# CADENCE 原理图与 PCB 设计说明

(第 1 版)

深圳市中兴通讯股份有限公司

ZTE CORPORATION

# 目 录

|                                    |           |

|------------------------------------|-----------|

| 序 言 .....                          | 1         |

| <b>第一章 系统简介 .....</b>              | <b>2</b>  |

| 1.1    系统组成.....                   | 2         |

| 1.1.1    库 .....                   | 2         |

| 1.1.2    原理图输入.....                | 2         |

| 1.1.3    设计转换和修改管理.....            | 2         |

| 1.1.4    物理设计与加工数据的生成.....         | 3         |

| 1.1.5    高速PCB规划设计环境 .....         | 3         |

| 1.2    Cadence设计流程.....            | 3         |

| <b>第二章    Cadence安装.....</b>       | <b>4</b>  |

| 2.1 安装步骤 .....                     | 4         |

| 2.2 LICENSE设置.....                 | 7         |

| 2.3 库映射 .....                      | 7         |

| 2.4 修改cds.lib文件, 设置原理图库: .....     | 8         |

| 2.5 编辑ENV文件, 设置PCB库: .....         | 9         |

| <b>第三章 CADENCE库管理.....</b>         | <b>11</b> |

| 3.1 中兴EDA库管理系统 .....               | 11        |

| 3.2 CADENCE库结构 .....               | 13        |

| 3.2.1 原理图 (Concept HDL) 库结构: ..... | 13        |

| 3.2.2 PCB库结构: .....                | 13        |

| <b>第四章    项目管理器 .....</b>          | <b>15</b> |

| 4.1 项目管理的概念 .....                  | 15        |

| 4.2 创建或打开一个项目 .....                | 15        |

| 4.3 原理图库的添加: .....                 | 16        |

| 4.4 填写设计 (Design) 名称.....          | 17        |

| 4.5 增加新的Design(设计) .....           | 18        |

|                                |           |

|--------------------------------|-----------|

| 4.6 项目的目录结构.....               | 18        |

| <b>第五章 原理图设计 .....</b>         | <b>20</b> |

| 5.1 图纸版面设置.....                | 20        |

| 5.1.1 图纸统一格式设置.....            | 20        |

| 5.1.2 栅格设置.....                | 22        |

| 5.2 Concept-HDL的启动 .....       | 23        |

| 5.3 添加元件 .....                 | 24        |

| 5.3.1 逻辑方式添加器件.....            | 24        |

| 5.3.2 物理方式添加器件.....            | 25        |

| 5.4 画线.....                    | 26        |

| 5.4.1 Draw方式 .....             | 26        |

| 5.4.2 Route方式.....             | 27        |

| 5.5 添加信号名 .....                | 27        |

| 5.6 画总线.....                   | 28        |

| 5.7 信号名命名规则.....               | 29        |

| 5.8 元件位号 .....                 | 31        |

| 5.8.1 元件位号手工标注 .....           | 31        |

| 5.8.2 元件位号的自动标注 .....          | 32        |

| 5.8.3 元件位号的自动排序.....           | 33        |

| 5.9 Cadence属性 .....            | 34        |

| 5.10 组操作 .....                 | 36        |

| 5.10.1 组定义:.....               | 36        |

| 5.10.2 组命名 .....               | 36        |

| 5.10.3 组操作 .....               | 37        |

| 5.11 常用命令 .....                | 38        |

| 5.11.1 常用的快捷键 .....            | 38        |

| 5.11.2 检查连接关系 .....            | 39        |

| 5.11.3 点画命令 .....              | 39        |

| 5.11.4 查找元件和网络 .....           | 39        |

| 5.11.5 两个不同网络名的网络连接的方法.....    | 40        |

| 5.11.6 错误检查 .....              | 40        |

| 5.11.7 检查Cadence原理图单个网络名 ..... | 40        |

|                                              |           |

|----------------------------------------------|-----------|

| 5.11.8 对隐藏了电源和地腿的器件定义电源和地信号.....             | 41        |

| 5.12 增加新的原理图页 .....                          | 41        |

| 5.13 原理图多页面操作 .....                          | 42        |

| 5.14 信号的页区位置交叉标注（Cross Reference） .....      | 42        |

| 5.14.1 信号的页区位置交叉标注（Cross Reference）的作用 ..... | 42        |

| 5.14.2 交叉标注需注意的几点： .....                     | 43        |

| 5.14.3 信号的交叉标注（Cross Reference）的方法.....      | 43        |

| 5.14.4 层次设计中出模块信号的交叉标注 .....                 | 43        |

| 5.14.5 出页信号的交叉标注的要求 .....                    | 44        |

| 5.15 在不同的project下实现原理图拷贝 .....               | 44        |

| 5.16 打印图纸 .....                              | 47        |

| 5.17 自动生成料单 .....                            | 48        |

| 5.18 原理图归档 .....                             | 50        |

| 5.19 原理图评审 .....                             | 51        |

| <b>第六章 从原理图到PCB .....</b>                    | <b>52</b> |

| 6.1 从原理图到PCB的实现.....                         | 52        |

| 6.1 .1 原理图到PCB的转换过程： .....                   | 52        |

| <b>第七章 PCB设计 .....</b>                       | <b>55</b> |

| 7.1 导入数据 .....                               | 55        |

| 7.2 Allegro用户界面 .....                        | 55        |

| 7.2.1 控制面板的作用 .....                          | 56        |

| 7.2.2 工具栏的显示.....                            | 57        |

| 7.3 Layout准备 .....                           | 58        |

| 7.3.1 创建PCB图的物理外形.....                       | 58        |

| 7.3.1.2 在Allegro界面下创建板外框： .....              | 61        |

| 7.3.2 设置板图尺寸参数 .....                         | 62        |

| 7.3.3 设置版图的栅格值： .....                        | 63        |

| 7.3.4 设置板图选项 .....                           | 63        |

| 7.3.5 设置PCB板的叠层.....                         | 64        |

| 7.3.6 设置约束条件 .....                           | 65        |

| 7.3.6.1 设置板的缺省间距： .....                      | 65        |

---

|                                          |           |

|------------------------------------------|-----------|

| 7.3.6.2 设置扩展的距离规则 .....                  | 66        |

| 7.3.6.3 设置扩展的物理规则 .....                  | 69        |

| 7.3.6.4 编辑属性 .....                       | 69        |

| 7.3.7 可视性和颜色设置 .....                     | 70        |

| 7.4 PCB布局 .....                          | 70        |

| 7.5 PCB布线: .....                         | 73        |

| 7.6 添加过孔和替换过孔 .....                      | 74        |

| 7.6.1 添加过孔 .....                         | 74        |

| 7.6.2 替换过孔 .....                         | 75        |

| 7.7 优化走线 .....                           | 76        |

| 7.8 覆铜处理 .....                           | 77        |

| 7.8.1 阴版覆铜 .....                         | 77        |

| 7.8.2 阳版覆铜 .....                         | 78        |

| 7.9 分割电源平面 .....                         | 80        |

| 7.10 位号标注 .....                          | 83        |

| 7.11 加测试点 .....                          | 83        |

| 7.12 DRC检查 .....                         | 83        |

| 7.13 生成报告文件 .....                        | 84        |

| 7.14 VALOR检查 .....                       | 85        |

| 7.15 生成光绘文件和钻孔文件 .....                   | 85        |

| 7.15.1 生成光圈文件 (art-aper.txt), 即D码表 ..... | 85        |

| 7.15.2 生成钻孔文件 .....                      | 86        |

| 7.15.3 生成光绘文件 .....                      | 86        |

| 7.15.3.1 在Artwork中加入所需的层 .....           | 86        |

| 7.15.3.2 生成光绘文件 .....                    | 90        |

| 7.16 PCB评审 .....                         | 93        |

| <b>第八章 公司的PCB设计规范 .....</b>              | <b>94</b> |

## 序 言

Cadence 软件是我们公司统一使用的原理图设计、PCB 设计、高速仿真的 EDA 工具。本篇设计说明针对硬件开发人员需要使用的原理图及 PCB 设计进行全面的阐述，是一个入门级的教材。通过这篇设计说明旨在让新进员工能掌握 CADENCE 的基本使用方法，能独立进行原理图及 PCB 的设计，并对公司的 PCB 流程有全面的了解。

# 第一章 系统简介

## 1.1 系统组成

Cadence 软件是一个功能强大的系统工具，包括很多功能模块，如原理图输入；数字、模拟及混合电路仿真；FPGA 可编程逻辑器件设计；自动布局、布线；印刷电路板图及生产制造数据输出；MCM 电路版图设计；以及针对高速 PCB 板 MCM 电路的信号完整性分析等，从前到后提供了完整的输入、分析、版图编辑和制造的全线 EDA 辅助设计工具。我们这里只说明与原理图及 PCB 设计有关的内容，对于其它功能，可以以后学习和提高。

Cadence 板级设计范畴，主要由以下几部份组成：

### 5.8.1 库

所有的 EDA 软件都离不开库的支持，库的丰富程度在一定程度上决定着 EDA 工具的实用性。Cadence 板级设计的库按调用它的软件工具可分为四类：

原理图库：Concept HDL 调用

信噪库：SPECCTRAQuest 工具调用。

逻辑功能库：Verilog -XL 工具调用

物理库：Allegro 工具调用。

### 5.8.2 原理图输入

在 Cadence 板级设计中的原理图输入工具为 Concept-HDL，它可以灵活高效地将原理图送入计算机，并生成后继工具能够处理的数据。

### 5.8.3 设计转换和修改管理

它实际是原理图与 PCB 之间的一个纽带，负责将原理图中所表述的器件连接关系及元件封装说明翻译成 PCB 所能接受的格式，并将 PCB 信息反馈到原理图中，以保证原理图与 PCB 的同步。这种由前到后和由后到前的设计数据的转换都是由这一环境完成的。

#### 5.8.4 物理设计与加工数据的生成

这一环境主要完成 PCB 图的设计（包括布局、布线）和生成后继制造与加工 PCB 板所需的各数据文件。

#### 5.8.5 高速 PCB 规划设计环境

在该环境中可以对 PCB 图进行信号完整性分析等高速仿真，并将分析结果传递到 Concept 和 Allegro，从不断修改和完善 PCB 图。这一工具在信号频率较高的 PCB 设计中尤为有用。

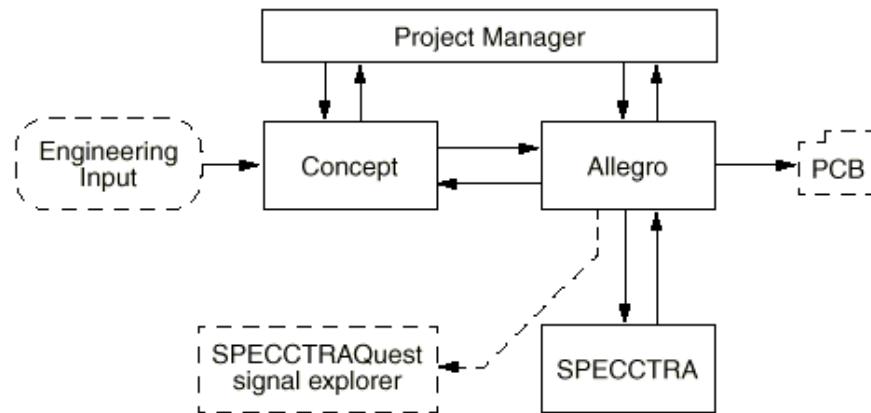

## 1.2 Cadence设计流程

Cadence 的原理图与 PCB 设计流程包括 Project 的生成、库的管理、输入原理图、生成网表、仿真分析、布局、布线和输出生产制造文档。流程如下：

- 1、使用 Project Manager 建立及管理 Project。

- 2、使用 Concept HDL 输入原理图。

- 3、使用 SPECCTRAQuest signal explorer (SigXP) 仿真分析并完成预布局。

- 4、设计转换和修改管理

- 5、使用 Allegro/SPECCTRA 布局、布线。

- 6、使用 Allegro 生成生产制造文档。

下图显示了使用 Cadence PCB 设计工具创建并完成一个 PCB 设计的过程：

## 第二章 Cadence安装

### 2.1 安装步骤

查找系统所在的计算机，

在安装目录下有 DISK1，选 SETUP 开始安装：

按确定：

NEXT

YES

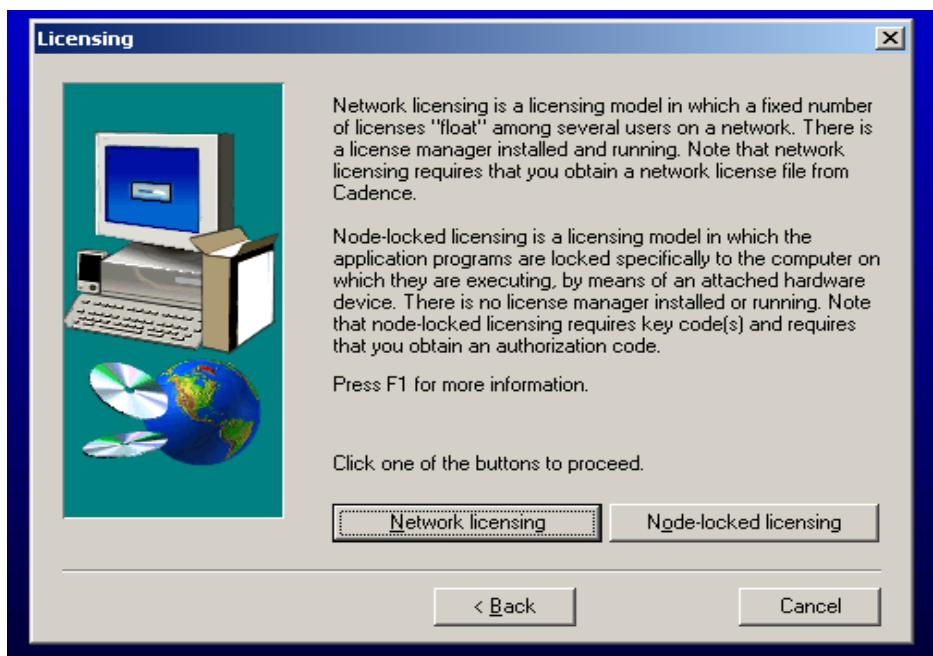

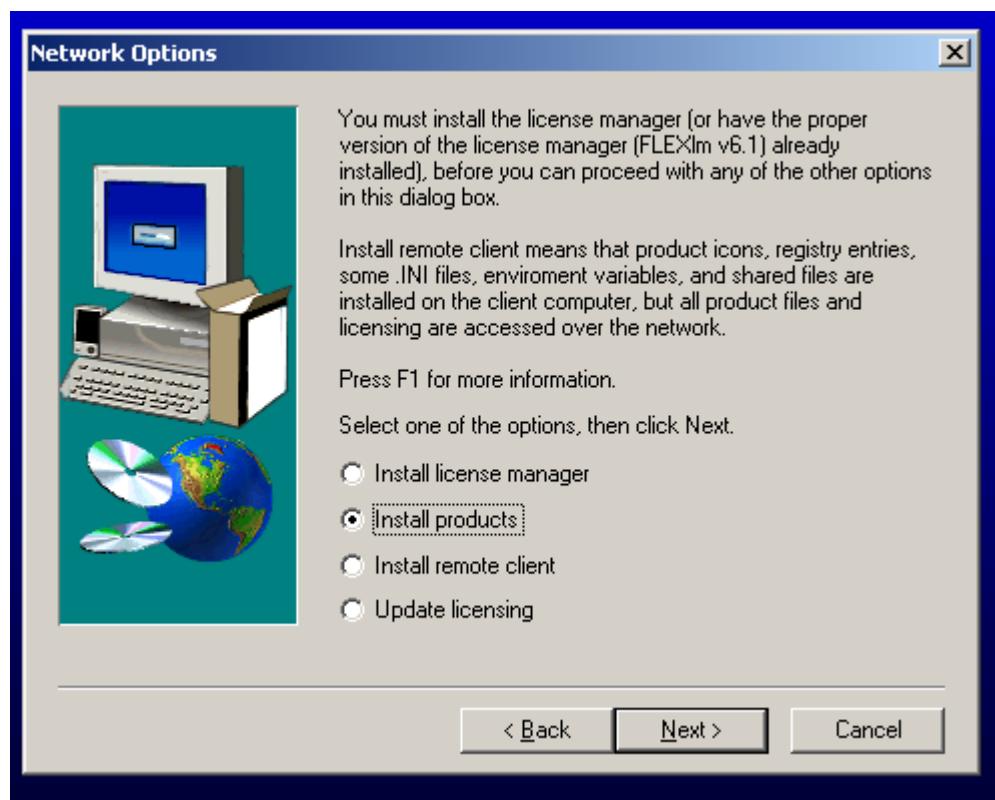

选 Network licensing

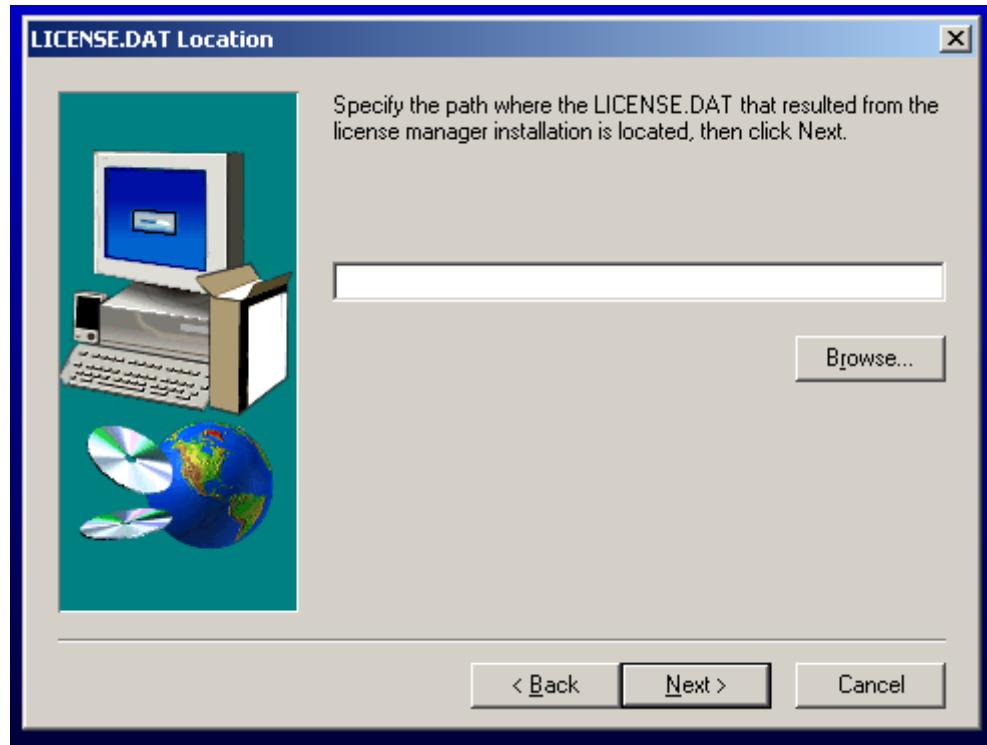

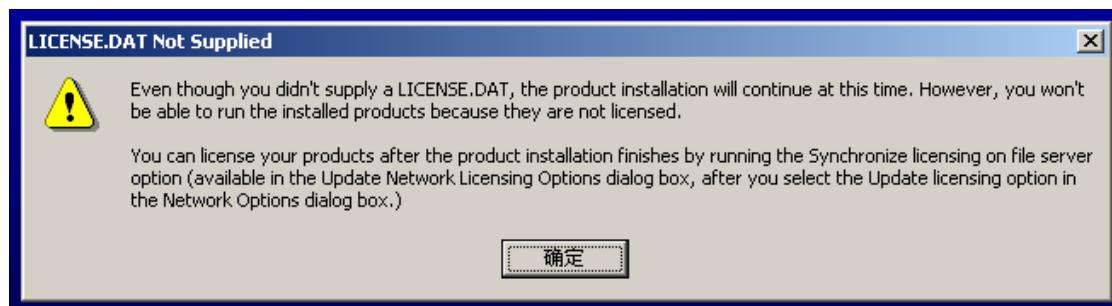

按 Next

按 Next

按确定

按 NEXT

按 YES

按确定

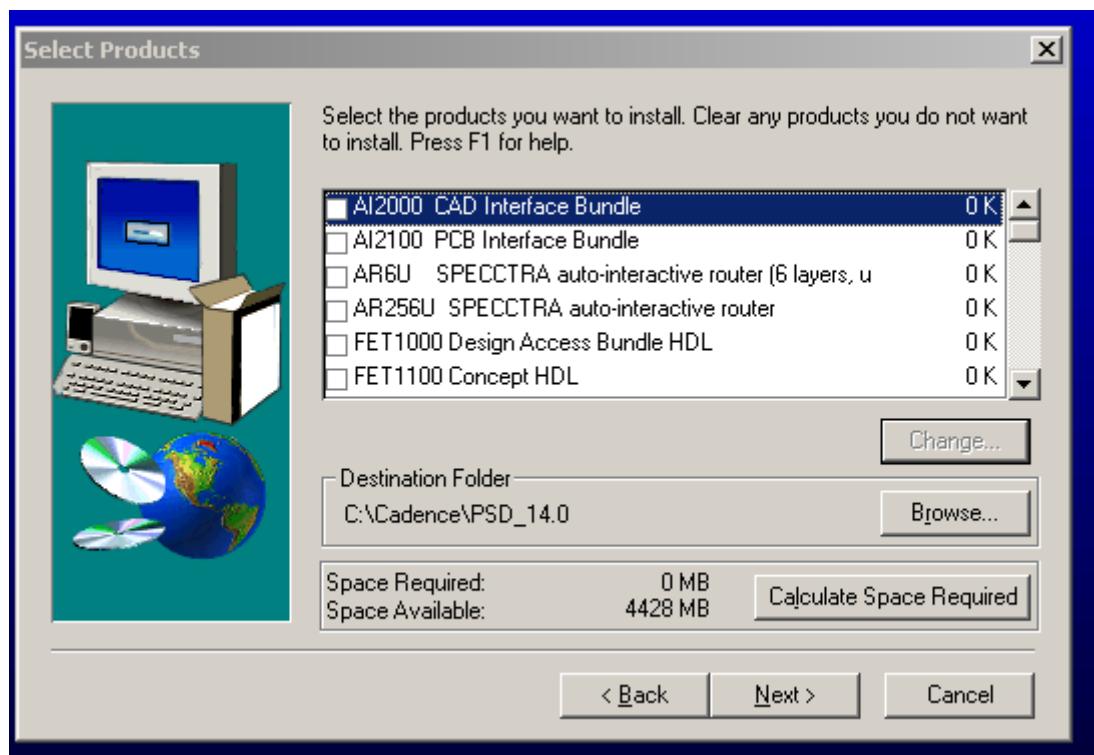

选 PX3700、VT1000、PX3100（这三个模块就是板级设计模块）。

同时可点选 Browse 改变目录。然后，按 NEXT 开始安装。

## 2.2 LICENSE设置

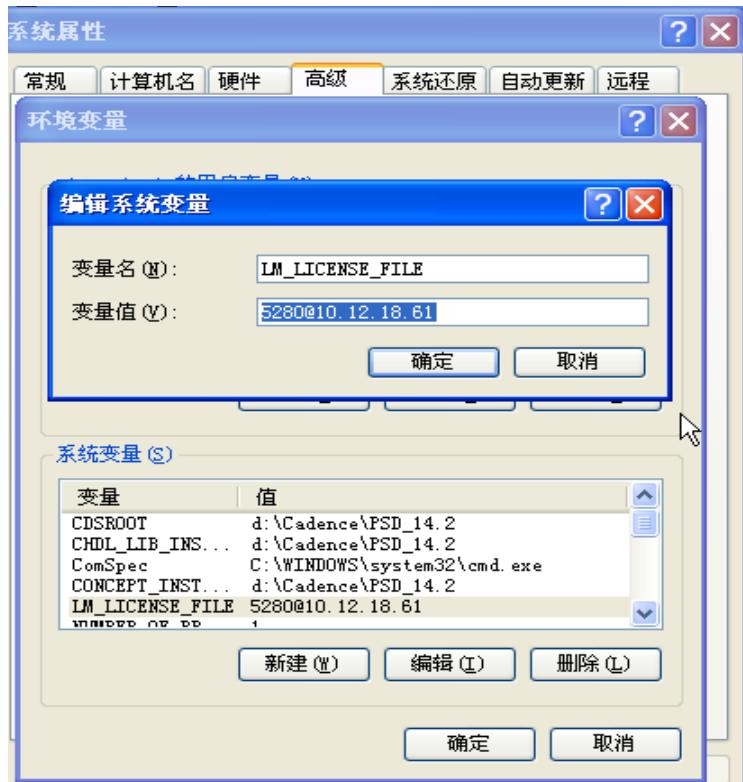

因为安装好的 Cadence 的 LICENSE 文件放在服务器上，所以需要将环境变量进行修改：

打开控制面板-----系统-----高级-----环境变量-----新建

按下图填写即可，变量值要根据 LICENSE 文件所在的位置进行修改：

## 2.3 库映射

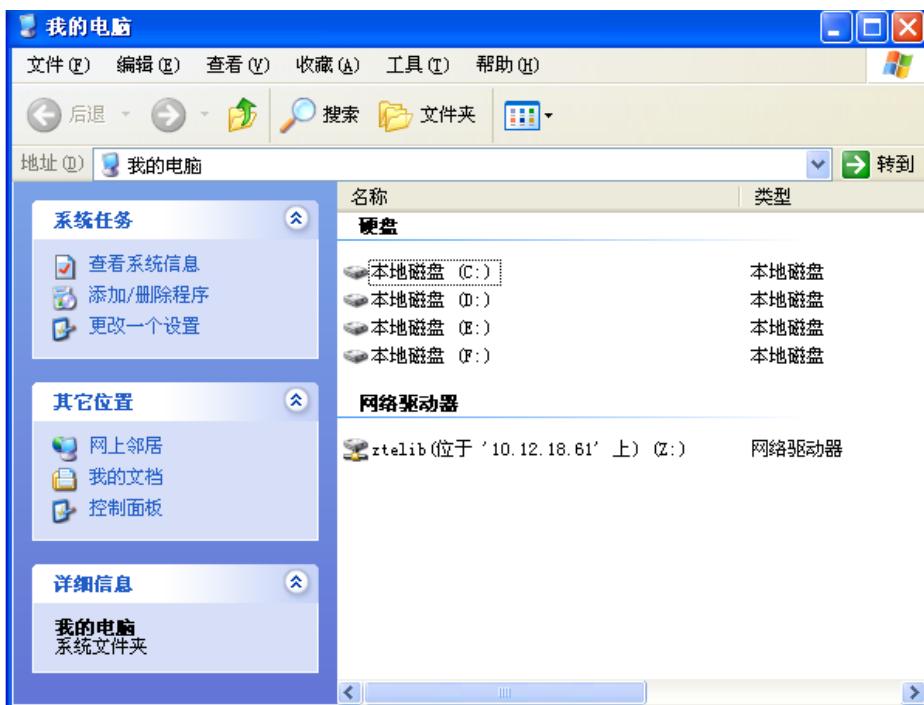

公司实行统一的 EDA 库管理，EDA 库都放在公司服务器上，当在本机运行 Cadence 时，需要将服务器上的 EDA 库映射到本机的虚拟盘上。映射驱动器 Z 到 EDA 库所在的文件夹，该文件夹为 [\10.61.24.22\ztelib](#)，要求映射驱动器名要统一为 Z。映射后如下图所示：

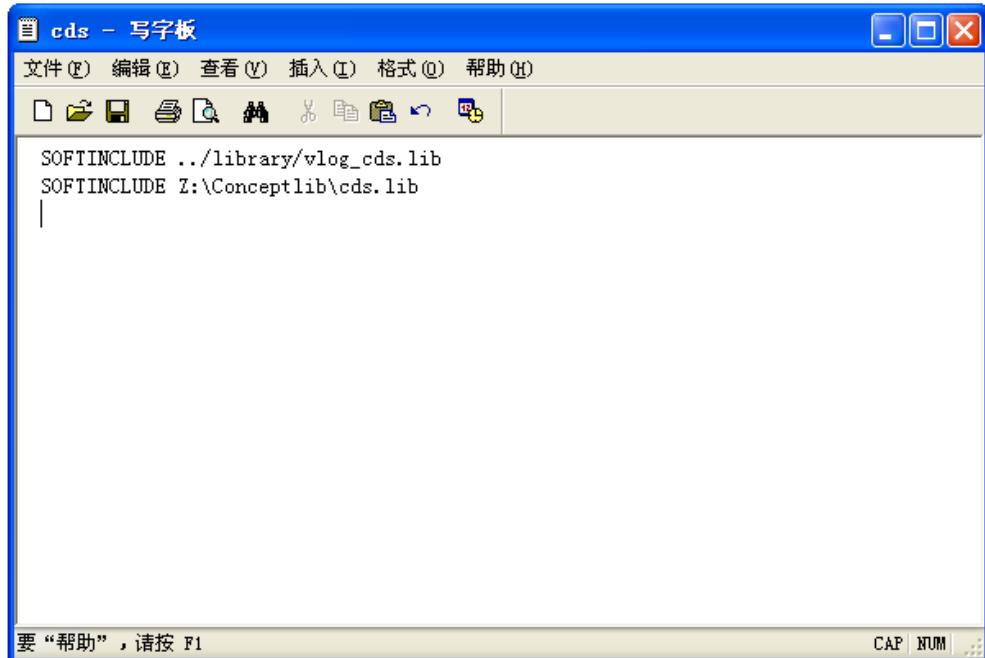

## 2.4 修改cds.lib文件，设置原理图库：

Cadence 中的 cds.lib 文件是一个原理图库索引文件，它是一个文本文件，允许你编辑修改。该文件的每一行都由 DEFINE 或 INCLUDE 关键词定义了一个元件库的索引指针，其中 DEFINE 定义了一个单一的元件库索引，而 INCLUDE 则定义了另一个库索引文件(cds.lib)的包含。

当安装好 Cadence 后，为了索引原理图库，需要修改系统的 cds.lib 文件，进入以下路径：

\$:\CADENCE\PSD\_14.2\SHARE\CDSSETUP\，打开未修改的 CDS.LIB 如下：

```

cds1 - 记事本

文件(F) 编辑(E) 格式(O) 帮助(H)

DEFINE standard ..\library\standard

SOFTINCLUDE ..\library\vlog_cds.lib

SOFTINCLUDE $CHDL_LIB_INST_DIR/share/library/cds.lib

```

将之编辑如下图，其中“SOFTINCLUDE Z: \Conceptlib\cds.lib”，表示包含了Z盘Concept目录下的cds.lib，然后通过它进一步引用所提供的所有原理图库。

保存退出，原理图库设置完成。

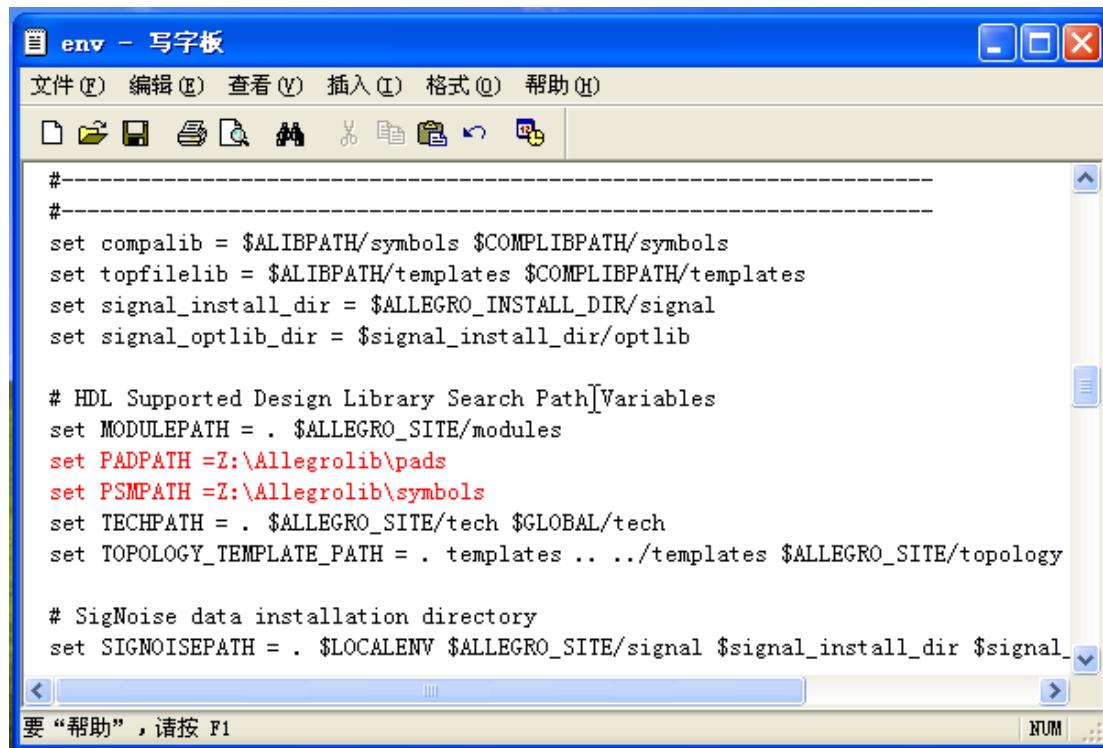

## 2.5 编辑ENV文件，设置PCB库：

ENV 文件中设置了 PCB 焊盘和封装库的路径，在\$:\CADENCE\PSD\_14.2\SHARE\PCB\TEXT 下打开 ENV 文件进行编辑，将 PAD\PSM 路径编辑成如下红色字体所示：

```

#-----

#-----

set compalib = $ALIBPATH/symbols $COMPLIBPATH/symbols

set topfilelib = $ALIBPATH/templates $COMPLIBPATH/templates

set signal_install_dir = $ALLEGRO_INSTALL_DIR	signal

set signal_optlib_dir = $signal_install_dir/optlib

# HDL Supported Design Library Search Path]Variables

set MODULEPATH = . $ALLEGRO_SITE/modules

set PADPATH =Z:\Allegrolib\pads

set PSMPATH =Z:\Allegrolib\symbols

set TECHPATH = . $ALLEGRO_SITE/tech $GLOBAL/tech

set TOPOLOGY_TEMPLATE_PATH = . templates .../templates $ALLEGRO_SITE/topology

# SigNoise data installation directory

set SIGNOISEPATH = . $LOCALENV $ALLEGRO_SITE/signal $signal_install_dir $signal_

要“帮助”，请按 F1

```

保存退出，PCB 库设置完成。

## 第三章 CADENCE库管理

### 3.1 中兴EDA库管理系统

公司的 EDA 库实行统一管理，所有 EDA 库（包括原理图库、封装库、VPL 库、IBIS 模型库）都要统一到工艺平台进行管理，通过流程建好的库都统一放在公司服务器上，一般不允许设计人员私自在本机建库。第三章已讲述了怎样将服务器上的库引用到本机的 Cadence 的设计环境中。

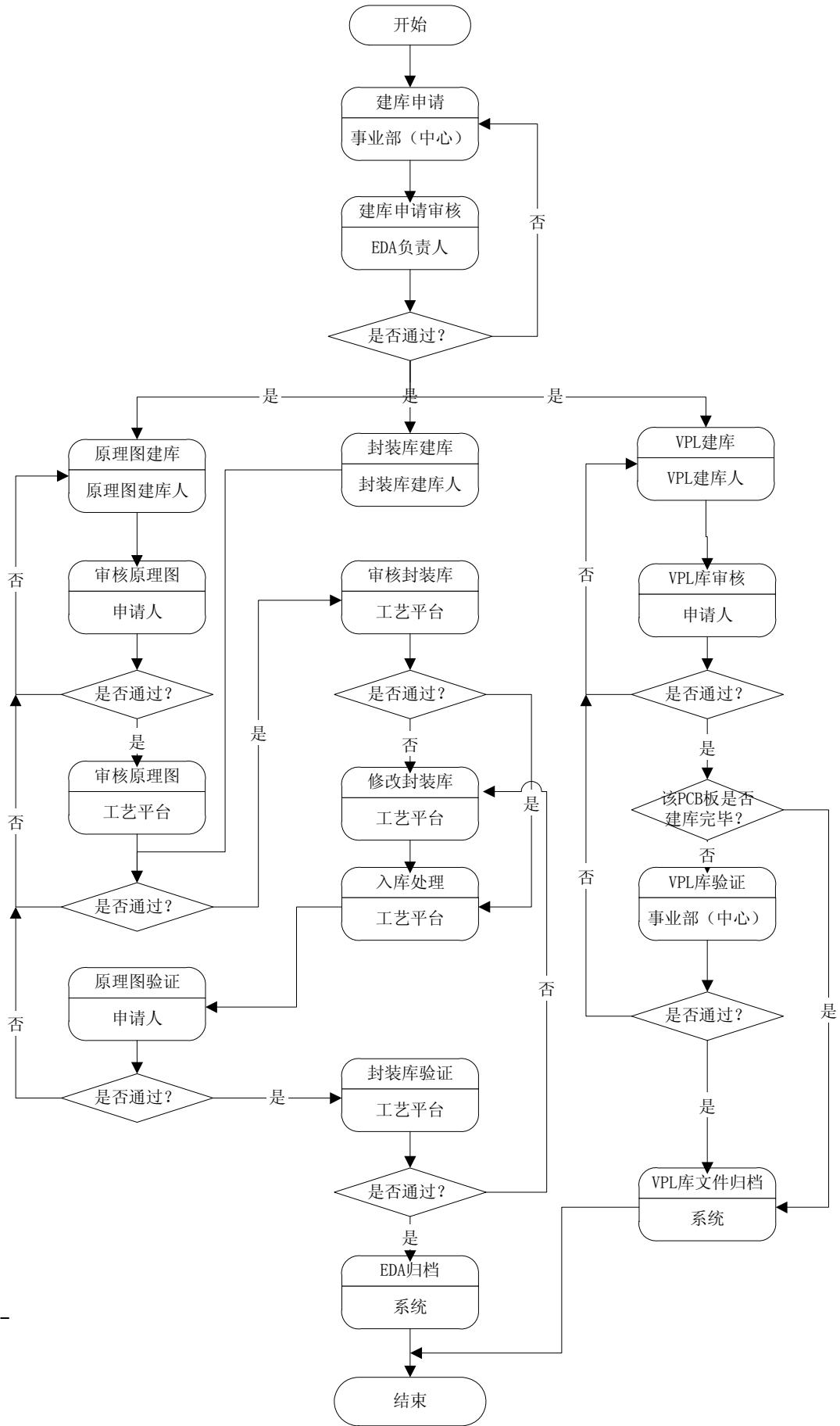

所有的 EDA 库申请、建库、审核等均要通过 **STEP2000 系统** 来执行。流程如下：（具体流程请参照 STEP2000V4.0 用户操作手册----工艺管理）。

## EDA/VPL建库流程图

## 3.2 CADENCE库结构 0

### 5.8.6 3.2.1 原理图 (Concept HDL) 库结构:

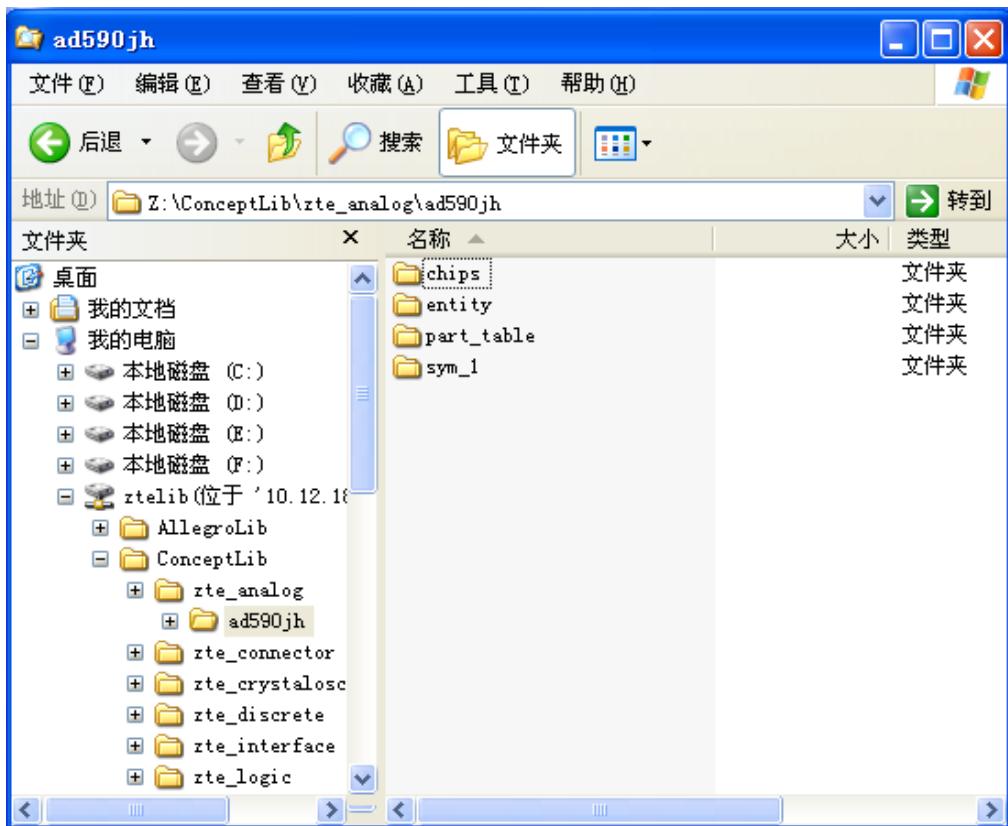

Cadence 的每个元件原理图库都用几个文件来描述，就是有多个 View，View 就是对器件从各个方面进行描述，系统默认的名字有 sym\_1、entity、chips、part\_table 等。Sym\_1 存放的文件用来描述元件符号；entity 存放的文件用来描述文件端口的高层语言描述；chips 目录的文件是对元件物理封装的说明和层次的描述；Part\_table 下存放的元件的附加属性，用于构造企业特定元件，建立和企业 ERP 系统的接口。

在 Z 盘打开一个具体的元件，可看到以下画面，可看出这个元件下就包括了上述的这四个文件：

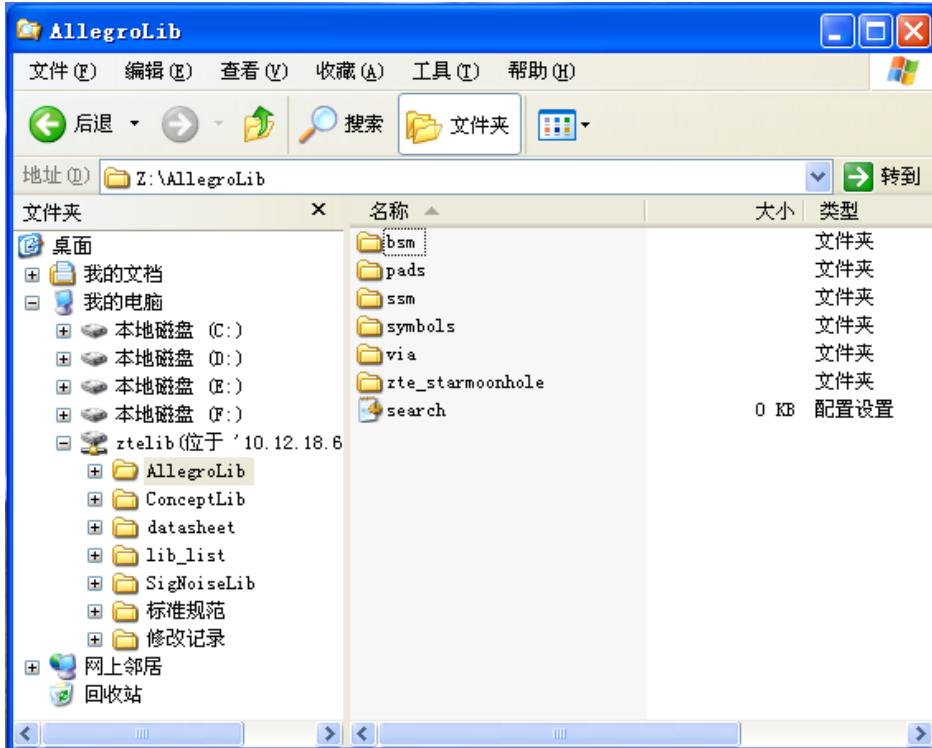

### 5.8.7 3.2.2 PCB库结构:

Cadence 的 PCB 库包括两个部份：焊盘和封装图形库，下图中 pads 文件夹中放焊盘库，symbols 文件夹中放封装图形库，路径由 ENV 文件指定。

因为现在公司实行统一的库管理流程，所以关于怎样建库在这里不作详细说明。

## 第四章 项目管理器

### 4.1 项目管理的概念

项目管理器是对用户的设计进行统一管理以及环境设计的工具，是板级设计工具的整合环境，Cadence 板级设计流程都在项目管理器下进行，通过项目管理器中可以方便地进入各个设计环节，如原理图设计、PCB 设计、高速仿真等，还可以进行原理图到 PCB 的转换、设计环境的设置等。

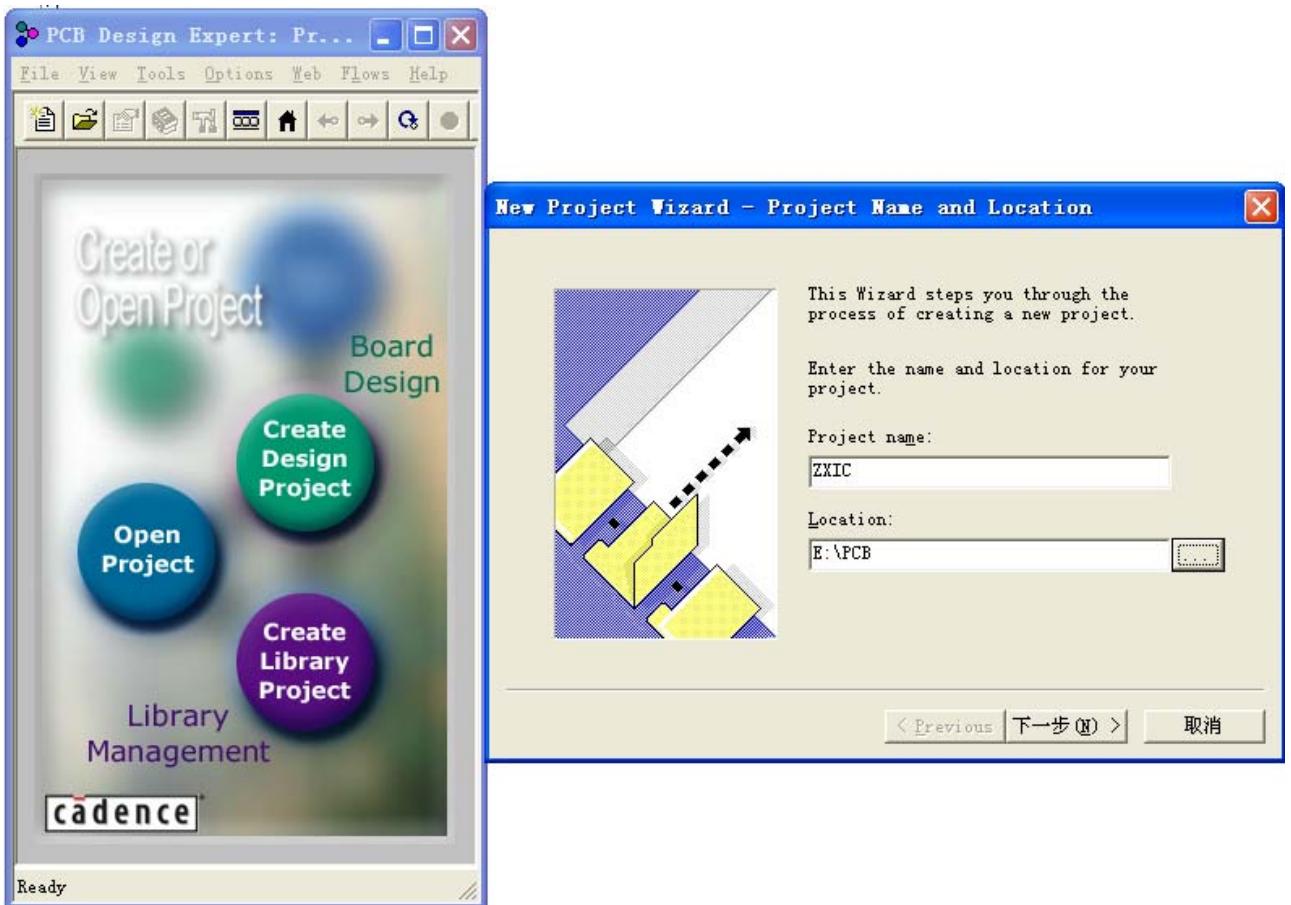

### 4.2 创建或打开一个项目

打开 Project Manager，然后“Create Design Project”，其中 Location 下的路径格式为“工作目录\产品名称”。（说明：工作目录可以为根目录，也可以为“根目录\PSD\_Data”，还可以是其它专门存放 PSD 工程文件的目录。）

产品名称格式为“ZX” + “设备简称代号”，其中 ZX 为公司名称“中兴”汉语拼音字首。设备简称代号不超过四个字符，例如 ZXIC。设备升级后可以用 Vx.x 区分，如 ZXIC 升级后可以表示为 ZXICV2.0。

Location 下的路径严禁包含任何中文字，否则输出网络表时可能会报告错误。

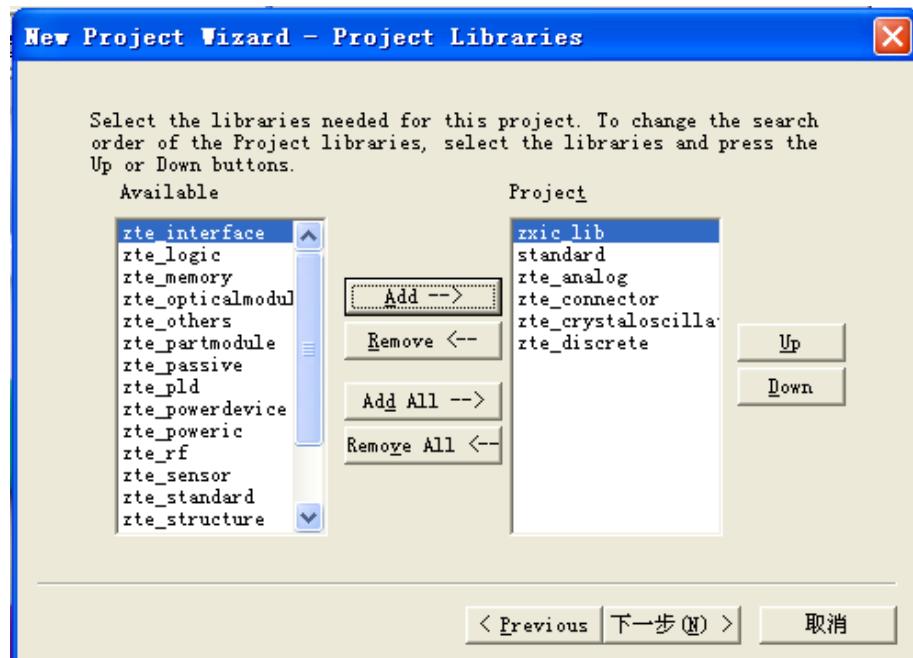

### 4.3 原理图库的添加:

点击“下一步”，进入以下界面进行原理图库的添加，由 cds.lib 索引的原理图库列出，选出需要的原理图库进行添加：

## 4.4 填写设计 (Design) 名称

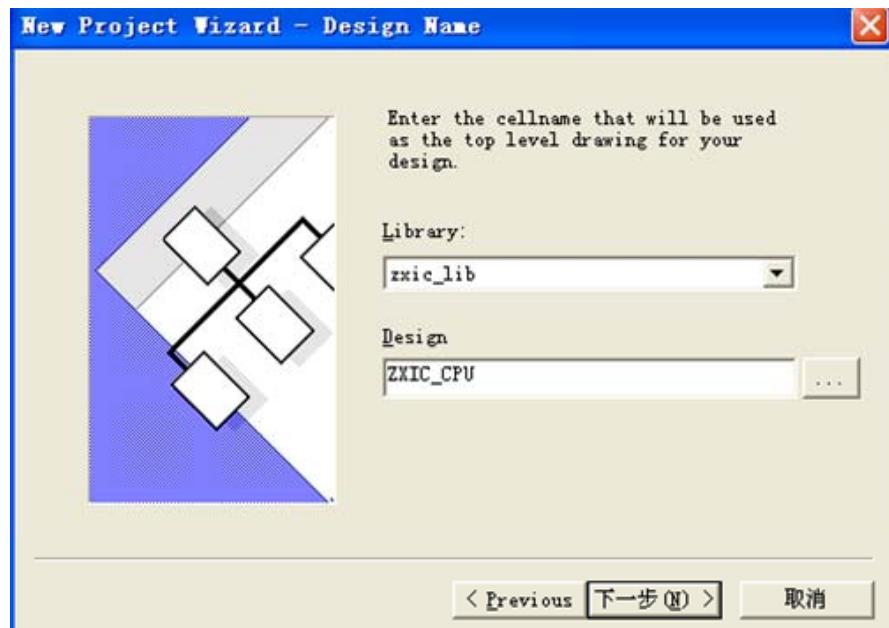

添加完原理图库后，再“进一步”，进入原理图设计 (Design) 界面，如下图所示。Design 名称格式为“产品名称\_单板名称”。

再点击“下一步”，则生成了一个新的项目。

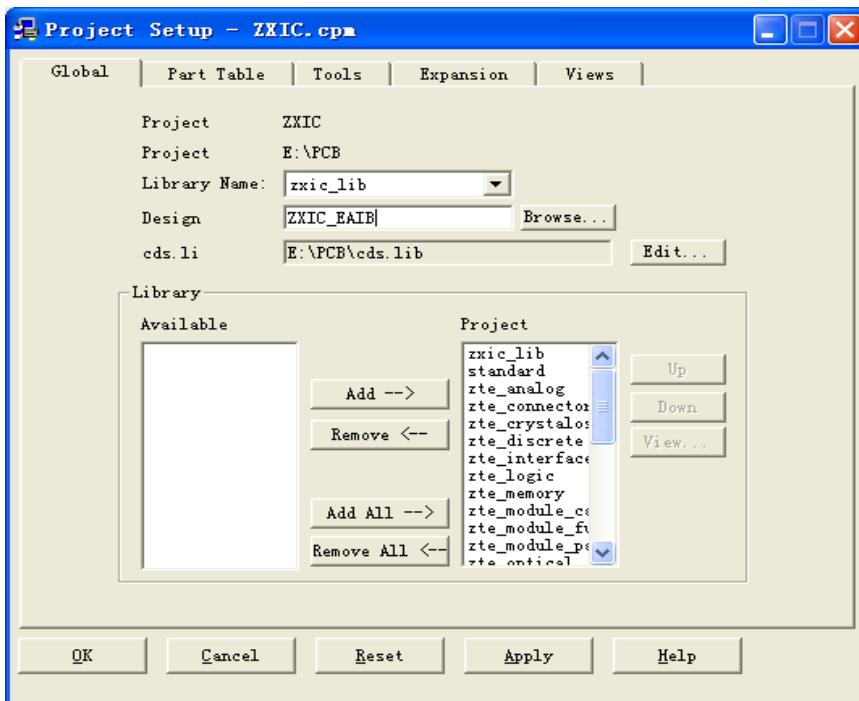

## 4.5 增加新的Design(设计)

如果你的工程包含多个单板，在 Project Manager 中的 Project Setup 的 Design 中输入新的设计(产品名称\_单板名称)名称，点击 OK，在 worklib 下即生成一个新的设计文件夹。如图所示，在工程 ZXIC 中增加设计 ZXIC\_EAIB，其中 ZXIC 为产品名称，EAIB 为单板名称：

在这个界面下，还可以进行 Design 的选择，通过“Browse”选择将要打开的 Design，然后通过 Project Manager 下的“Design Entry”就可以进入对应的 Design。

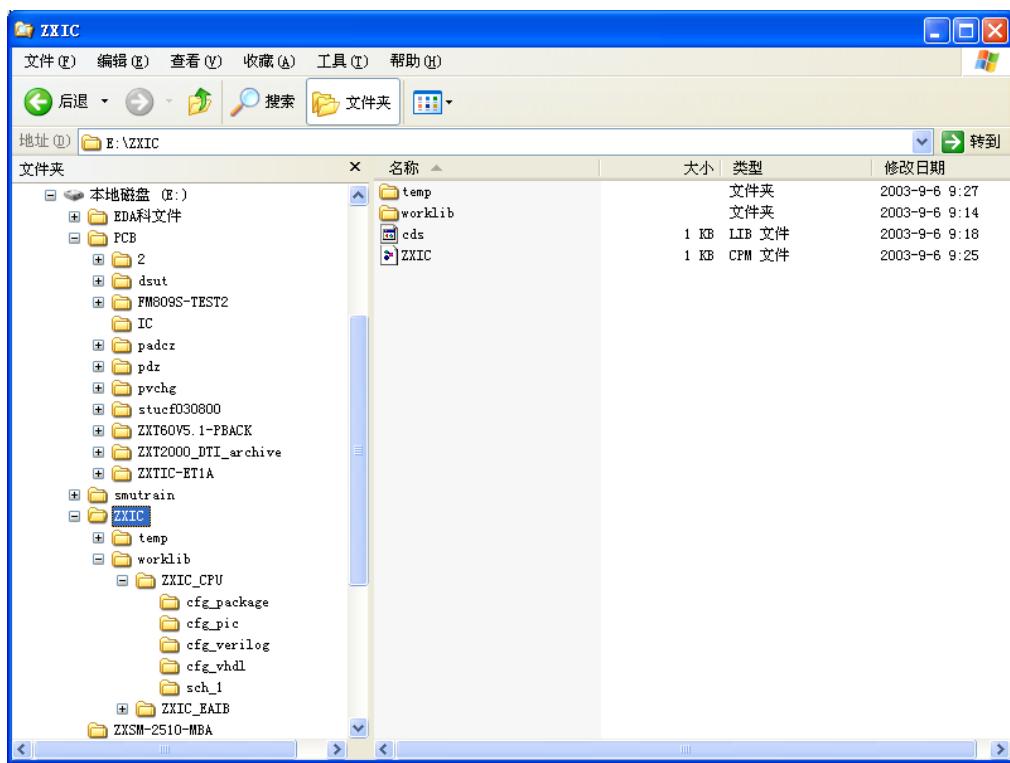

## 4.6 项目的目录结构

Cadence 的板级设计采用工程（Project）式的文件结构。通过上面的过程生成一个 Project 后，一个 Project 可以管理多个单板的设计，每个单板的设计又包含原理图、网络表、PCB 文件等。Cadence 文件目录结构如图：

其中 worklib 为工程库目录，下面又分为多个 design，cds.lib 为库索引文件。ZXIC.cpm 为项目管理文件。除了路径 E:\PCB\ZXIC 和项目管理文件 ZXIC.cpm 包含大写字母以外，其它文件夹和文件都不包含大写字母。

## 第五章 原理图设计

### 5.1 图纸版面设置

#### 5.8.8 5.1.1 图纸统一格式设置

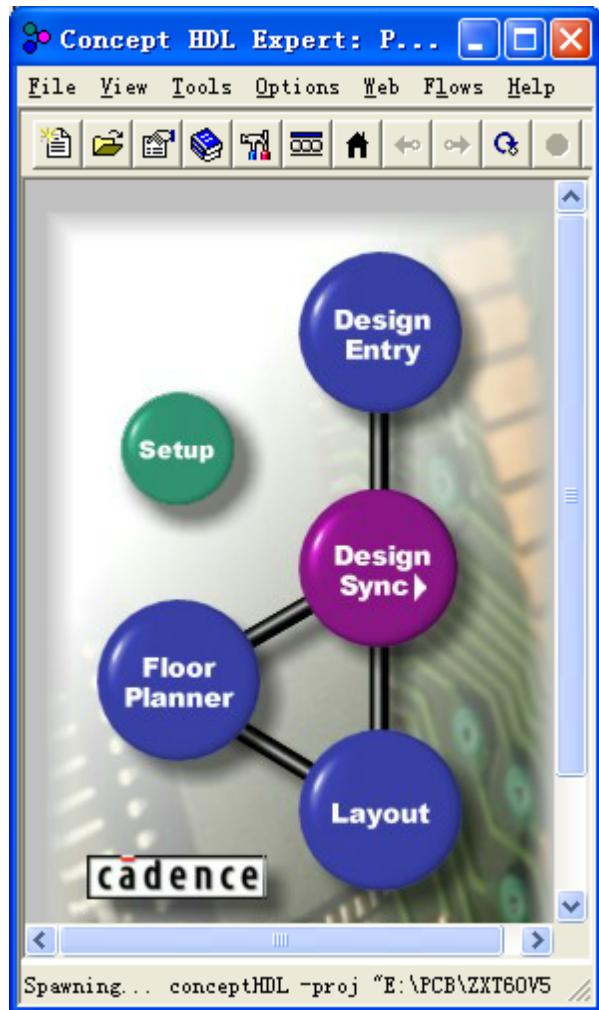

创建项目后，就进入以下界面：

在进入原理图设计之前，我们先需要进行原理图图纸格式设置和栅格设置：

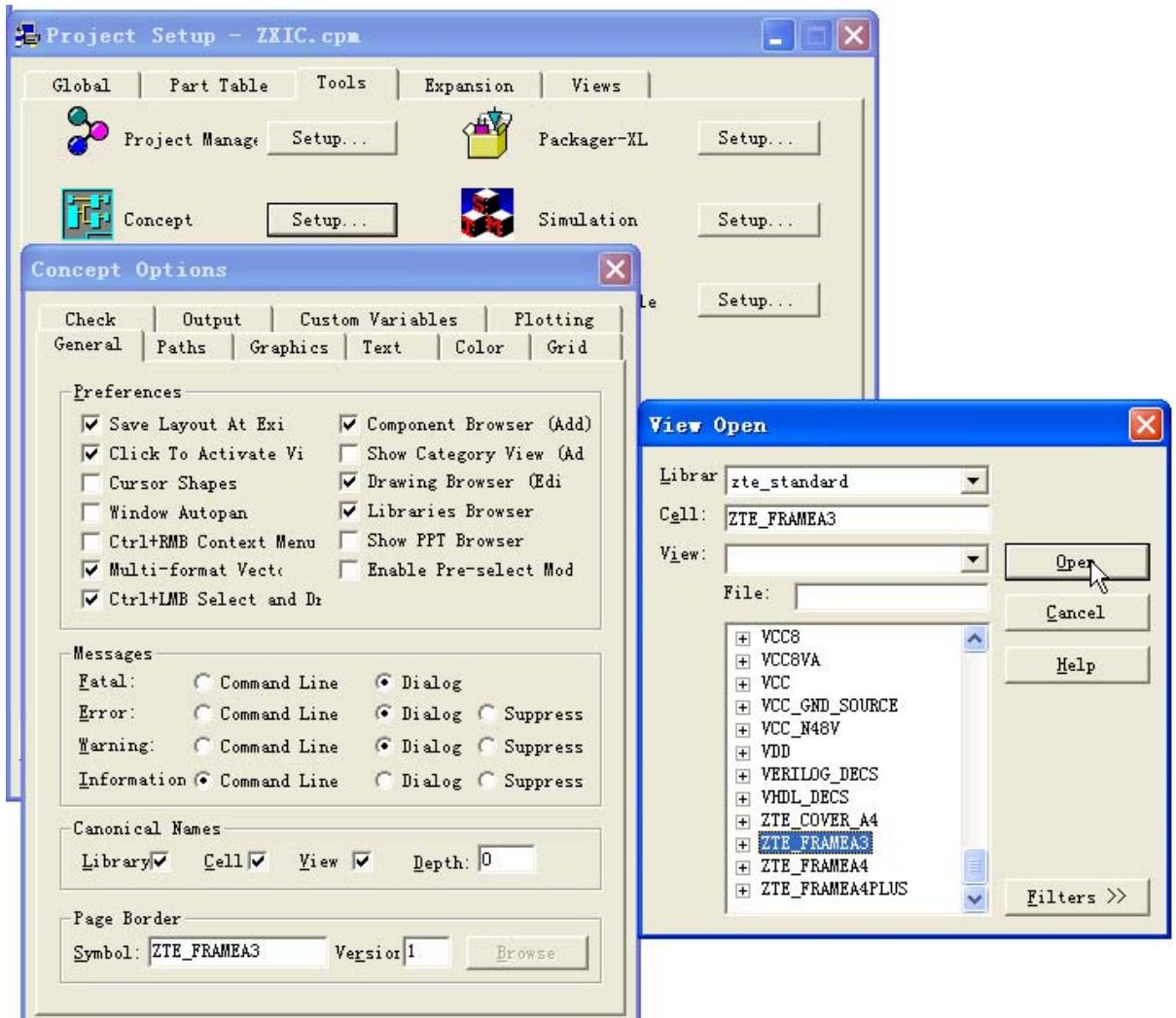

在上面的“Project Manager”中点击 Setup，接着选择 tools—concept setup，在图纸选择栏通过“Browse”选择 zte-standard 库中的图纸格式，如下图：

图框、目录表、会签表应该使用公司的统一格式的原理图库，见下表：

| 库 名             | 所在库          | 说 明        | 备 注                    |

|-----------------|--------------|------------|------------------------|

| Contents        | zte_standard | 目录表        | sym_2 为续表              |

| ZTE_COVER_A4    | zte_standard | 原理图封面      |                        |

| ZTE_FrameA4plus | zte_standard | 加大的 A4 纸图框 | 在 A4 纸上 Fit to Page 打印 |

|             |              |        |                        |

|-------------|--------------|--------|------------------------|

| ZTE_FrameA4 | zte_standard | A4 纸图框 | 在 A4 纸上 Fit to Page 打印 |

| ZTE_FrameA3 | zte_standard | A3 纸图框 | 在 A3 纸上 Fit to Page 打印 |

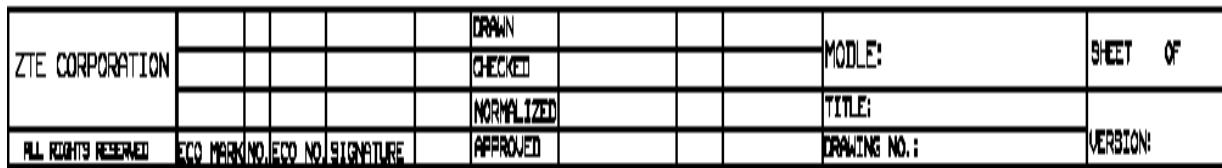

ZTE\_FrameA3 是统一的 A3 尺寸图纸格式。其标注栏如下，包括设计公司说明“ZTE CORPORATION”。原理图归档前，设计者、检查者、标准化者、更改者必须签名。标题，页码编号，版本等信息必须填写清楚。

### 5.8.9 5.1.2 栅格设置

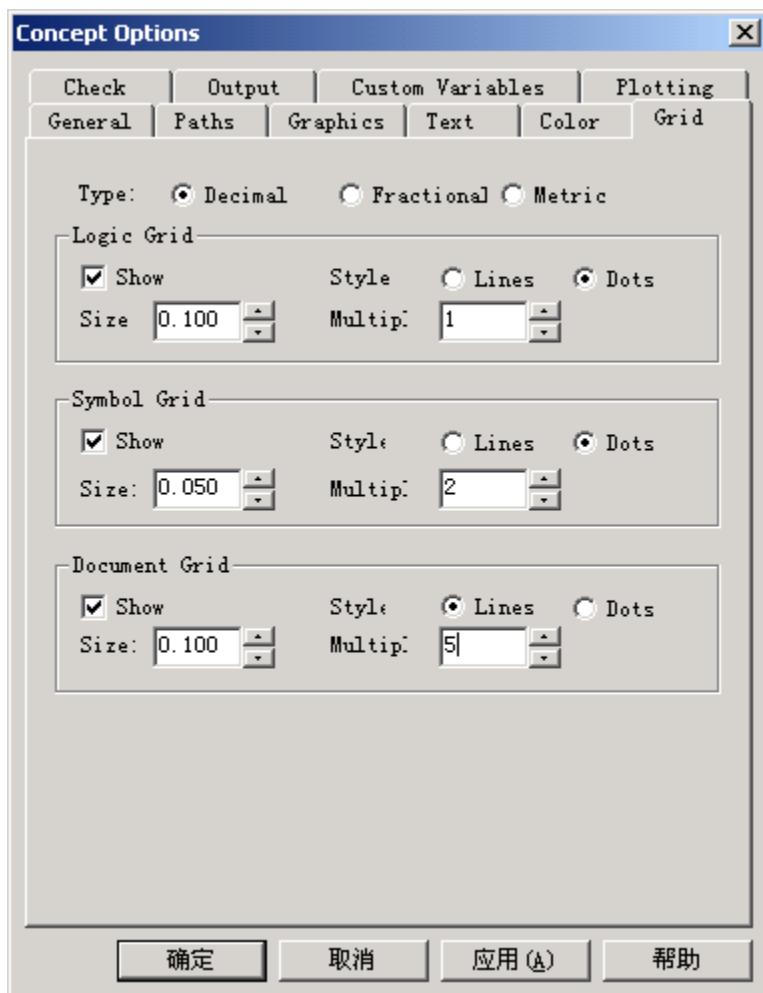

同样在上面 Project Manager 的 Concept Option 界面的 Grid 栏中设置原理图栅格，可以采用的值如下：

\*0.100 5 (跟踪 100mil 显示 500mil, 为默认值)

\*0.100 1 (跟踪 100mil 显示 100mil)

\*0.050 2(跟踪 50mil 显示 100mil)

\*0.010 10 (跟踪 10mil 显示 100mil)

因为原理图库的元件管脚间距为 100mil，为使得连线坐标直观且方便推荐采用 Logic Grid 采用 \*0.100 5 (跟踪 100mil 显示 500mil, 为默认值) 或者 0.100×1 格式。Symbols Grid 为设计原理图库时使用的栅格，不要修改它。即设置如下：

Concept Option 一旦设置好，以后就不要修改。每新建立一个 Cadence PSD 工程都必须经过上述流程。

## 5.2 Concept-HDL的启动

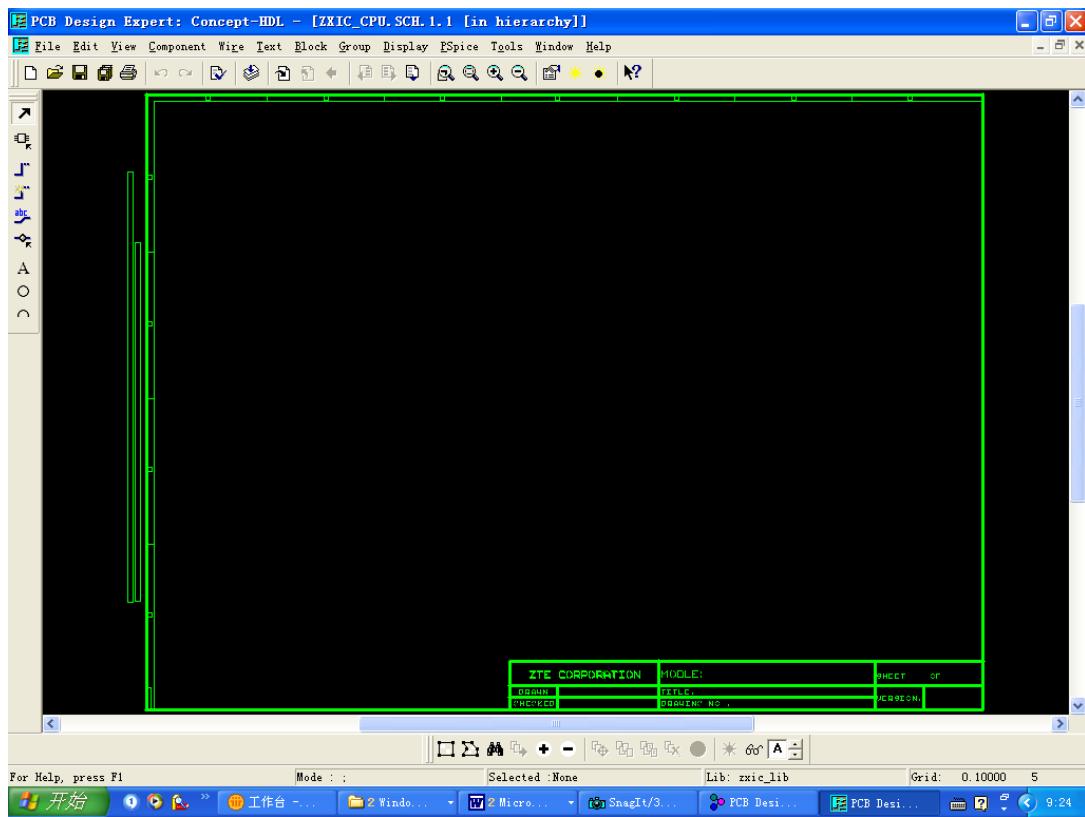

打开“Design Entry”，就进入原理图设计界面，如下图：(设置图纸版面后需退出 Project Manager，再重新进入)：

在标题栏中显示是将要编辑的原理图文件信息，即：ZXIC\_CPU.SCH.1.1。它的格式<Cell>.<View>.<Version>.<Page>。即是<设计>.<视图>.<版本>.<页码>。这里的 Version 并不是原理图多次修改的版本号，而是将该原理图作为一个单一的逻辑功能元件时，出现在原理图中的元件符号版本。

## 5.3 添加元件

Concept 通过元件浏览器将元件添加在原理图上。先选择元件所在库，再在浏览器的库元件清单中选择要添加的元件。一个元件可能有不同的版本（即 Version），系统默认为版本 1，在添加元件时你可以按鼠标右键，在弹出菜单中选择元件的其它 Version 且将元件旋转成合适的角度，然后放在原理图上。

### 5.8.10 5.3.1 逻辑方式添加器件

当你不点击 physical 而直接放置元件时，concept 仅将元件的符号视图以及与符号视图相关的信息放置在原理图上，例如符号图形、逻辑元件及管脚名、与元件符号相关的某些属性。这种方式我们称为“逻辑方式添加器件”。

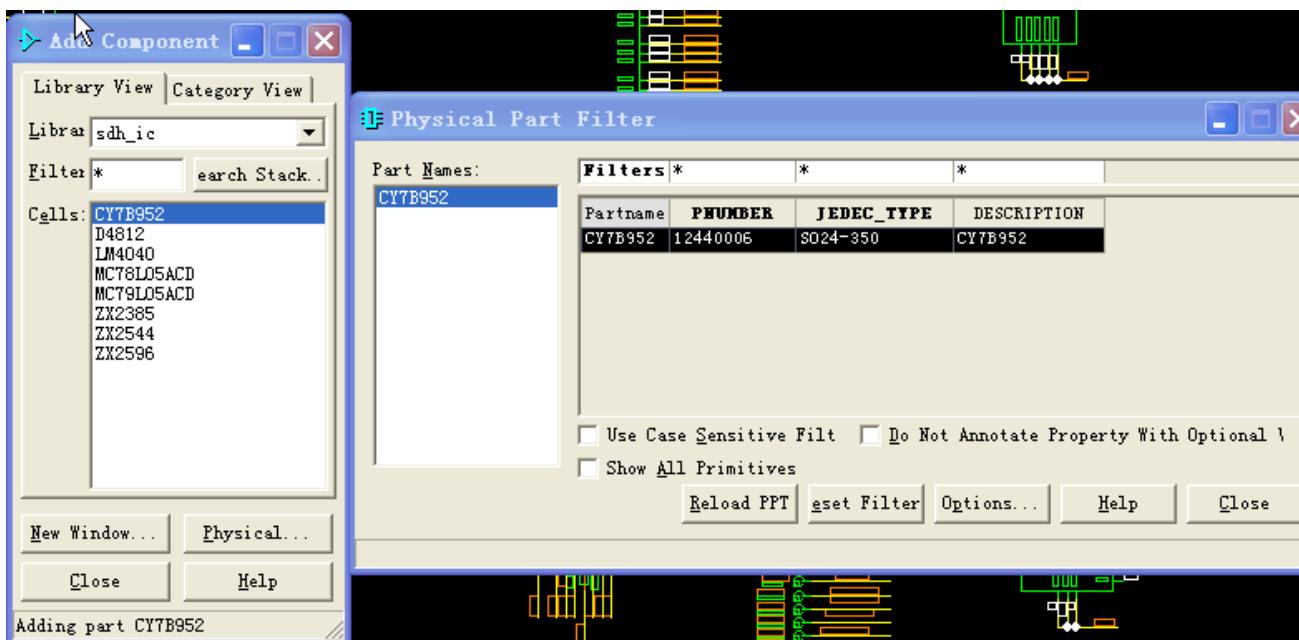

### 5.8.11 5.3.2 物理方式添加器件

为了将元件的物理封装形式调入，在放置元件时要点中 Physical。如果Physical Part Filter窗口为空，则直接放置该元件，如果Physical Part Filter 不为空，请从中选择合适的元件。

当你按照物理方式添加元件时，concept-HDL 除了放置逻辑符号有关属性外，还将 chips 和 Part\_table 两个文件中对该逻辑元件的物理封装说明信息同时放置在原理图上，这样你就能够选择该元件的物理封装方式。

Chips 是逻辑到物理的映射描述，一个元件可能对应多个物理封装，chips.prt 文件就是同样一个物理元件到各种封装的映射描述，放映在 conceptHDL 中就是 Add Part 窗口。Part\_Table 是元件的附加属性定义（例如封装、元件值、物料代码、价格、功能简介、规格型号、供应商等信息），反映在 concept HDL 中就是 Part Physical Filter。

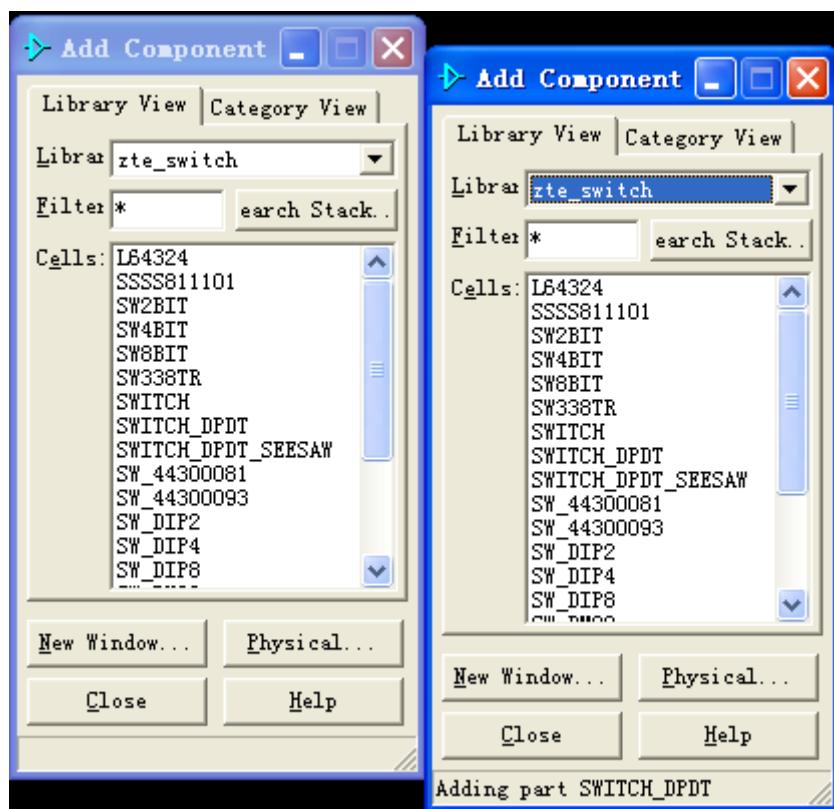

#### 5.3.3 多窗口添加元件

添加元件时，可以游览多个库：打开一个 Add Component 窗口后，点击其中的 New Windows，可以在新窗口中选择另一个库：

## 5.4 画线

Concept-HDL 有两种连线方式:

### 5.8.12 Draw方式

菜单操作 Wire-Draw，该方式允许你在连线的同时，对该线网络添加信号名。从管脚拉出一根线，再按鼠标右键从弹出菜单中选择“Signal name”可以添加网络名。也可以先画完需要引出的连线，再执行下拉菜单 Wire 中的 signal name，敲完所有的信号名，用鼠标逐个点击到相对的信号线上。

### 5.8.13 Route方式

菜单操作 Wire—Route，该方式能够自动完成点到点的连线。添加信号名需执行下拉菜单 Wire 中的 signal name…，敲完所有的信号名，用鼠标逐个点击到相对的信号线上。

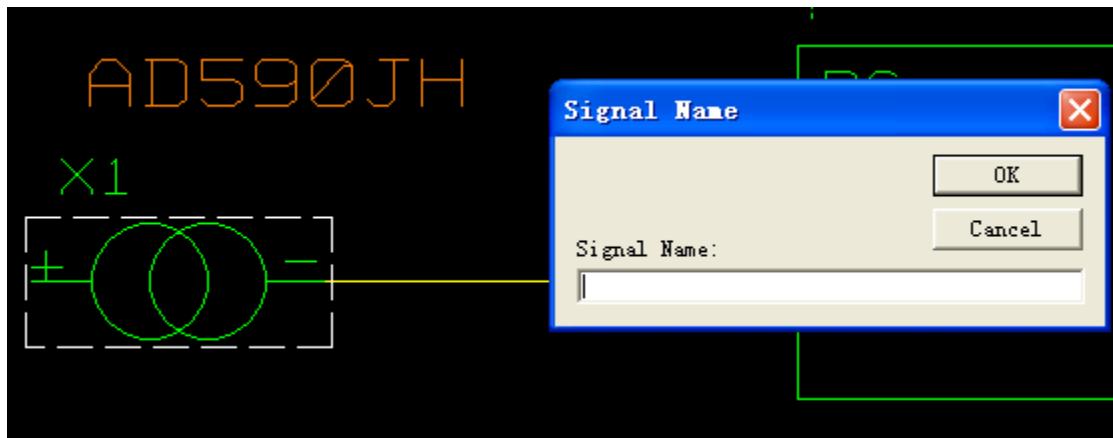

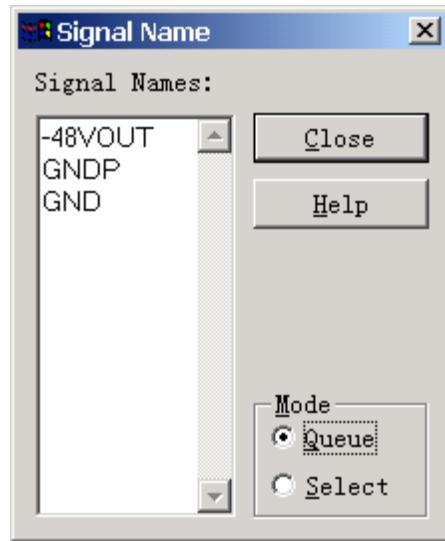

## 5.5 添加信号名

按 5.4 可知有两种方法添加信号名，一种是在画线过程中添加，一种是在画完线后添加。用 Route 方式画线则只能画完线后再执行下拉菜单 Wire 中的“signal name”定义信号名。执行下拉菜单 Wire 中的“signal name”弹出如下窗口：

有两种模式供选择，Queue 指依次方式，将会把 -48VOUT、GNDP、GND 依次附加给三根信号线，放完后 Signal Name 处为空；Select 模式指连续方式，选择该模式可以连续放置同一个信号名直至点击 Close 或者切换到 Queue 模式。

## 5.6 画总线

1、先用 5.4 的方法画一条线，再执行下拉菜单 Wire 中的 signal name，输入总线信号名，如 A<14.0>。

将信号名点击到信号线上，则这根连线自动变成总线形式。

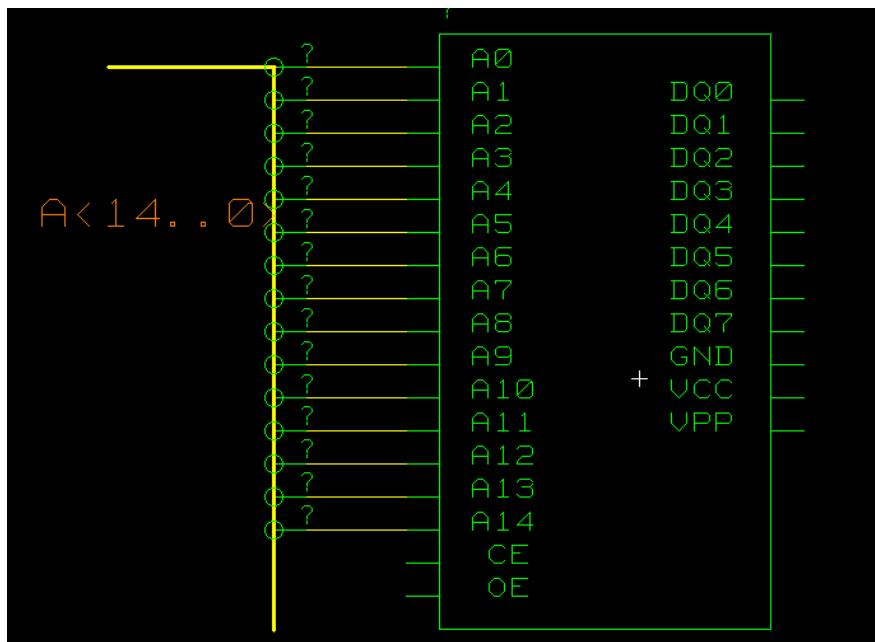

2、再选 Wire 菜单下的 Bus Tap，分别在总线上引出相应的支线，如图：

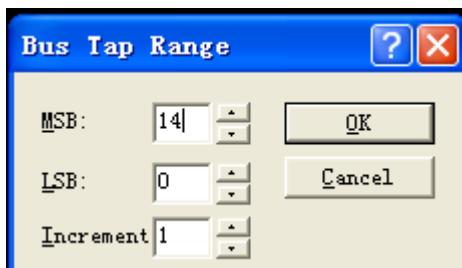

3、添加 Bus Tap value：从上图上可看出每条线上均有一个“？”，“？”是用来添加 BN（位号）属性的值。在 Wire 下选 Bus Tap Value，出现如下图所示的对话框。在 MSB（最高位）中填入 14，在 LSB（最低位）中填入 0，Increment（步进值）中填入 1。这是设定从支线到总线的值。

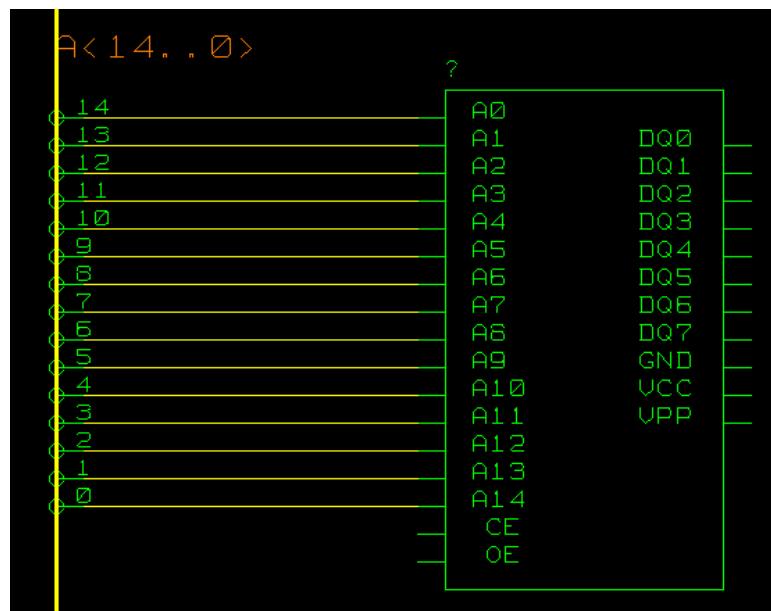

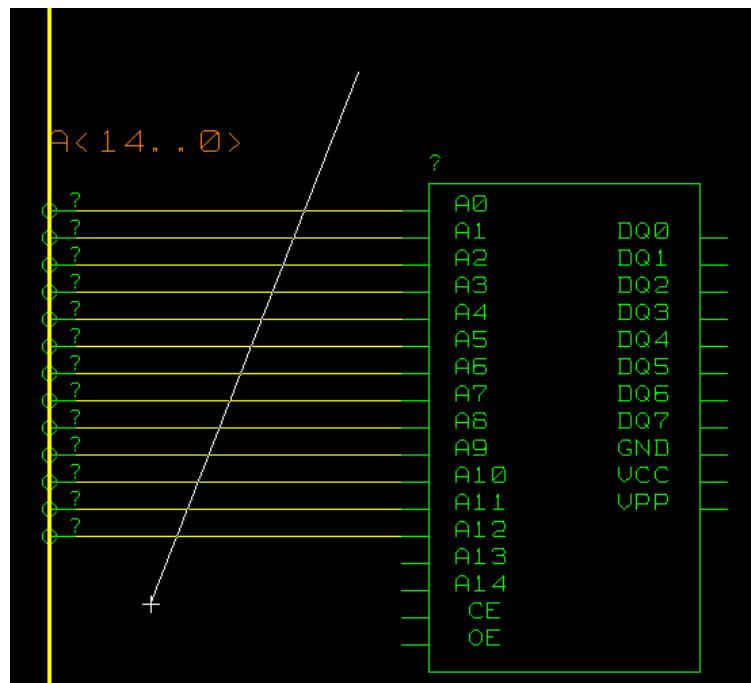

4、鼠标划一条线，穿过所有的支线，从高位到低位，如下图所示，松开鼠标后，“？”会自动变成位号。如下图所示：

## 5.7 信号名命名规则

下面规定一些信号名的命名规则，包括总线、差分线、逻辑低、双逻辑、电源信号线等命名方式。

## 1、电源信号命名规定：

设计时必须统一规定电源、地网络标号如下：

| 标号   | 含义           |

|------|--------------|

| VCC  | 数字正 5 伏      |

| VCCA | 模拟正 5 伏      |

| VCCN | 第 N 组专用正 5 伏 |

| +48V | 正 48 伏       |

| +12V | 正 12 伏       |

| +5V  | 正 5 伏        |

| +3V3 | 正 3.3V       |

| +2V5 | 正 2.5V       |

| +1V8 | 正 1.8V       |

| -5V  | 负 5 伏        |

| -12V | 负 12 伏       |

| -48V | 负 48 伏       |

| GND  | 数字地          |

| GNDD | 数字地          |

| GNDA | 模拟地          |

| GNDP | 保护地          |

电源和地的网络一律采用网络标号的方法实现电气连接。为保证电气连接正确，不准采用图形符号的方法实现连接。

## 2、差分信号命名规定：

差分信号的定义规定如下：正端定义为\*+，负端定义为\*-。不要采用\*A 和\*B 的方法区分正端和负端。局部信号命名打头字母规定：

局部信号命名的打头字符不能为： @ - ! # % & ( ) \* . / : ? [ ] ^ \_ `

+

= > 1 2 3 4 5 6 7 8 9

### 3、全局信号命名规定：

全局信号命名规定：在信号名后加上 “\G” 或在信号名前加上 “/” 或者 “!”，都表示该信号是一个全局有效的信号，在层次设计时，电源和地往往要定义成全局信号。

### 4、逻辑低和双逻辑信号命名规定：

如果信号为负逻辑有效请在信号名后加后缀\_N 表示，例如 INTD\_N；也可以用\*表示，例如 INTD\*。推荐采用\*表示负逻辑。

如果为双逻辑，表示方法：正逻辑信号名/负逻辑信号名，正逻辑在前，负逻辑在后，中间用/隔开，例如 C/BE7\_N（或者按推荐表示为 C/BE7\*）。

### 5、总线信号命名规定：

对用一根线表示多位信号的总线，其信号名的格式为<MSB..LSB>其中 MSB 和 LSB 分别表示信号的最高和最低位，不要采用[MSB..LSB]表示总线。总线的分支用信号名<bit>表示，不要用[BIT]表示。

## 5.8 元件位号

公司对元件位号都有相应的规定，如插头、插座规定用 X? 表示，集成电路规定用 D? 表示。具体请参照公司标准 Q/ZX 04.100.1 《印制电路板设计规范——工艺性要求》中的规定。

### 5.8.14 元件位号手工标注

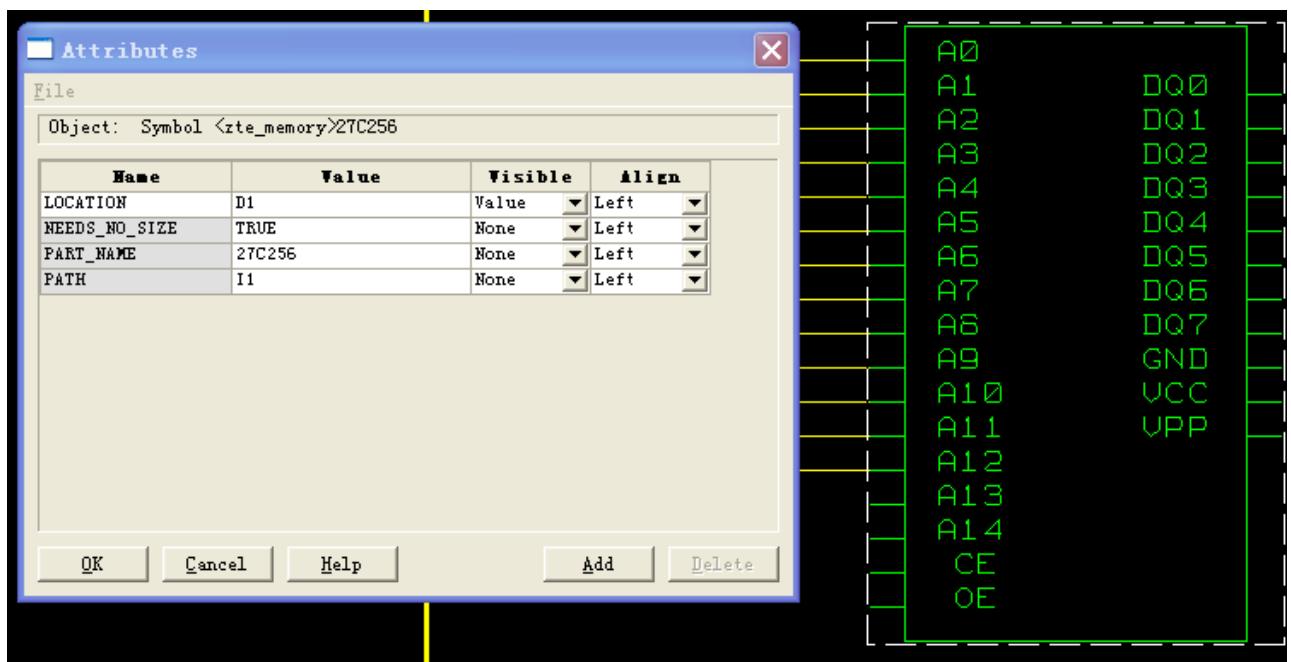

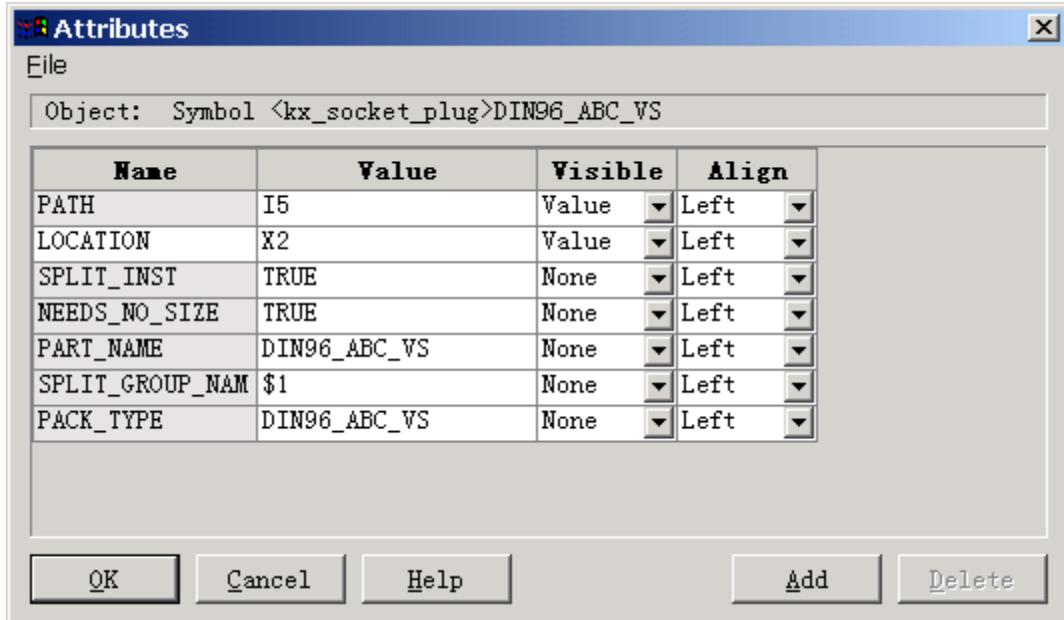

按鼠标左键选中元件，再按鼠标左键选择“Attribute”，如下图，将“\$LOCATION”的“?”改为指定的位号。

### 5.8.15 元件位号的自动标注

如想进行元件自动标注，建议器件位号采用 Cadence 软件自动分配的 \$Location（位号的软属性），即在放置器件后不需要对器件位号进行手工定义，一旦手工修改或者定义器件位号，则系统自动将\$Location 属性变为 Location 属性，自动保护你的修改结果，在重新封装过程中，Packager 能自动辨认和维护用户指定的 LOCATION，保证用户定义的位号不被修改。

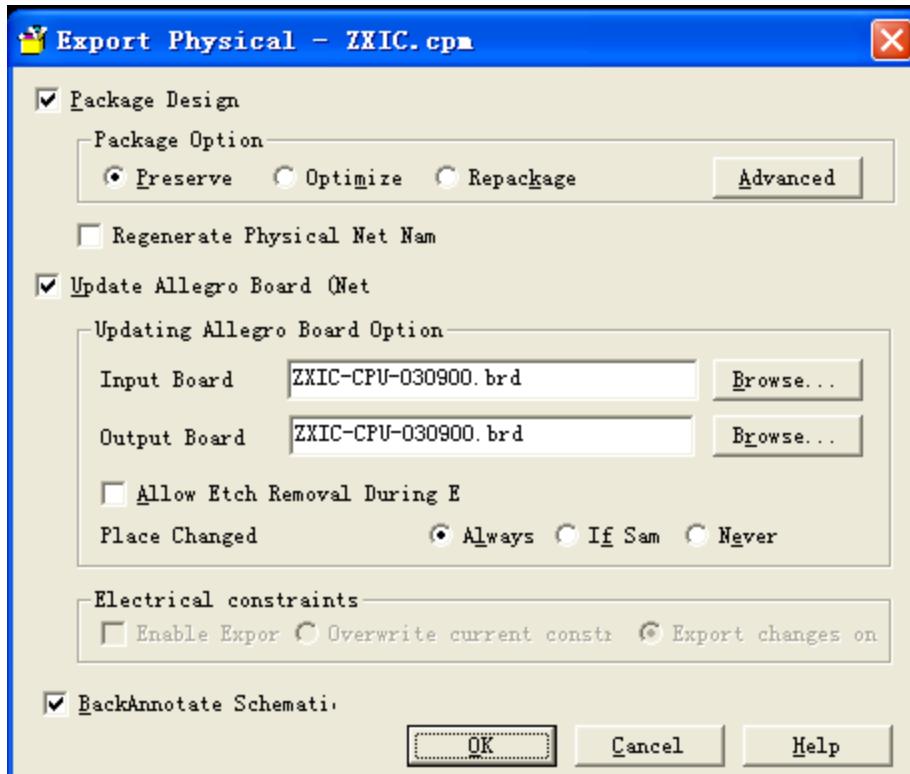

自动标注元件位号时，在 **file---export physical** 下，选择 **BackAnnotate Schematic**，则软件会自动标注位号，如下图。

这个界面是很重要的界面，从原理图转换到 PCB、生成网表都是通过它。

### 5.8.16 5.8.3 元件位号的自动排序

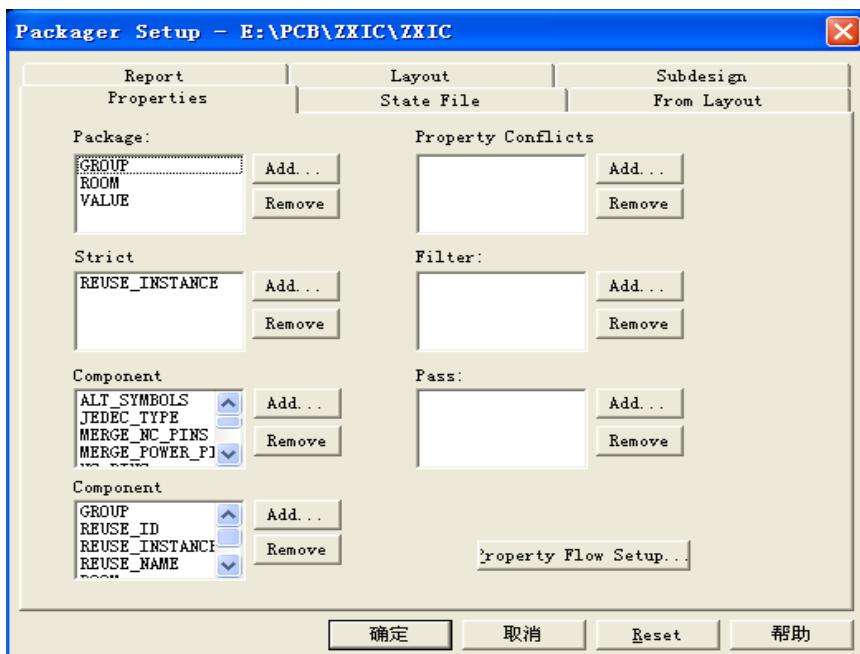

在原理图PCB设计过程中，为了使生成的料单整齐以及在焊接时不易产生人为的错误，通常我们要将分立器件-特别是阻容器件需要按照其值的大小来分配位号，同样大小的值的位号按序号连在一起。在CADNECE电原理图工具CONCEPT-HDL中我们可以采用以下方法来让系统自动按值的大小分配位号。

在上面的界面上，点击advanced按钮，出现如下对话框：

在properties对话框中的package栏内点击ADD按钮，输入VALUE属性，后点击确定，回到上一个生成网表的对话框。选择OK生成网表，最后再选择tools-back annotate命令反标原理图后，大家将得到一个按值的大小来排列位号的原理图。

## 5.9 Cadence属性

Cadence 的属性中有四种类型：

System Properties—是由系统所指定的，分配给 Wire (Net) 或者 Pin。

Schematic Properties—是由用户所指定的原理图属性，分配给 Component 或者 Wire (Net) 或者 Pin。

Symbols Properties—是在元件库中指定的封装属性。

Occurrence Properties—由用户指定的当前属性，可以对同一属性指定不同的值。

以下是几种常用的属性名称：

**PATH:** 器件在原理图中的标号，放置元件时自动添加，如 I12

**SIG\_NAME:**信号名，添加信号时系统自动生成，或者画线时用户定义。也可以作为属性添加。

**LOCATION:** 用户指定的元件所属的物理器件的位号，如 D2。

JEDEC\_TYPE:元件的物理封装，可以在制作原理图元件库时指定，也可以在原理图上用户自己指定。

点击 Text—Property 出现属性对话框，填入属性的名称和值，点击 OK，鼠标指针变成十字，点击想要添加属性的器件、管脚或者网络完成一次添加。如果要添加多个器件，选择 Text—Attribute 再点击想要添加属性的器件、管脚或者网络，出现属性添加列表，如下图：

填入想要添加的属性名称和值，然后在 Visible 中选择显示类型，是名称和值都显示（Both），还是都不显示（None）或只显示一种（Name 或者 Value），在 Align 中选择对齐方式，点击 OK，完成添加，如果不点击 OK，选择另一个想定义属性的对象，询问你是否保当前定义的属性，点击 Yes，接着可以继续定义属性。在 Name 和 Value 一栏中可以用快捷键 Ctrl+C 和 CTRL+V 实现复制和拷贝。

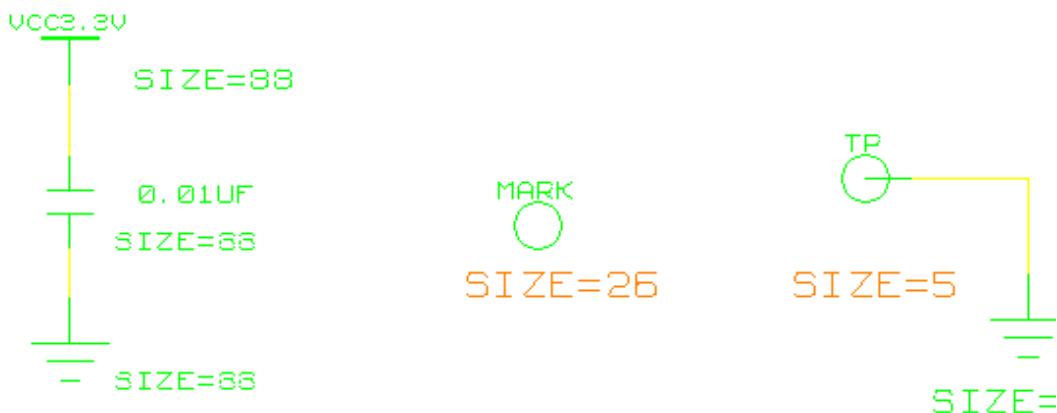

下面介绍一种特殊属性 Size 的作用：当加了一个 Size 属性时，用 Size 属性可以使一个器件符号表示 n 个器件，对去耦电容等的设计特别有意义。如下图，对 0.01uf 电容以及与其相连的电源和地分别加 Size=88 的属性，即表示在 VCC3.3V 和 GND 端加了 88 个电容，类似的用法还可以对需从原理图带入 PCB 中的光学定位点、地的测试针等需要多次重复的器件。

## 5.10 组操作

### 5.8.17 5.10.1 组定义:

组是原理图中某些元素的组合，这些元素可以是器件、网络、属性、注释等，但不能是管脚。定义了组以后，用户就可以对组元素一起操作。

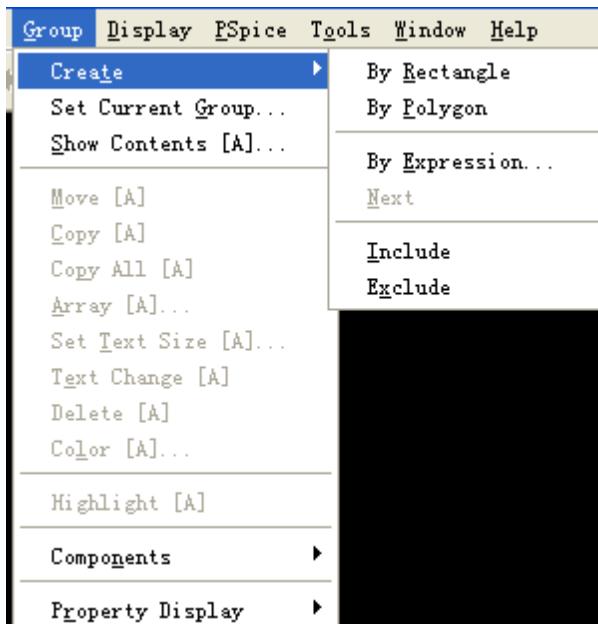

定义组有三种方法：矩形框、多边形框、表达式，这三种方法都可以在 Group 菜单中找到，如

下图所示：

### 5.8.18 5.10.2 组命名

创建组时，用户应用一个字母先给组命名，否则下次定义的组会覆盖本次的结果。名称选择可以点击 Group->Set Current Group，也可从 Group 工具栏中选择，如下图选择“B”作为组命名。

### 5.8.19 5.10.3 组操作

定义了组以后，用户可以对组进行 Move、Delete、Copy、Replace、Display 等各种操作，在成组复制时可以用 Group—Copy All 命令保持对元件和线网所添加的属性不变。但再次操作之前必须设定当前要进行操作的组。方法和定义组时的操作一样。

例如可以用该方式一起隐藏掉单前页的 PATH 属性。执行 GROUP BY EXPRESSION ...

在 Pattern 中的 Pattern 中填入属性名 PATH，当前页的所用的 PATH 属性名和属性值高亮，再执行 PROPERTIES Display — Invisible 隐藏掉所有的当前页的所用的 PATH 属性名和属性值。

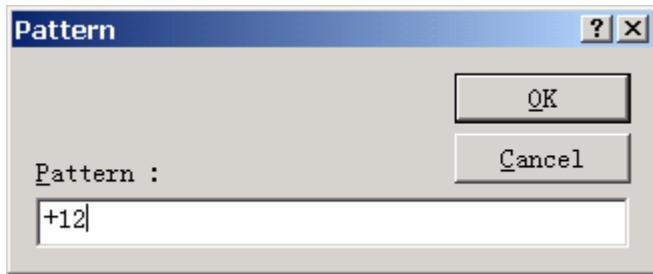

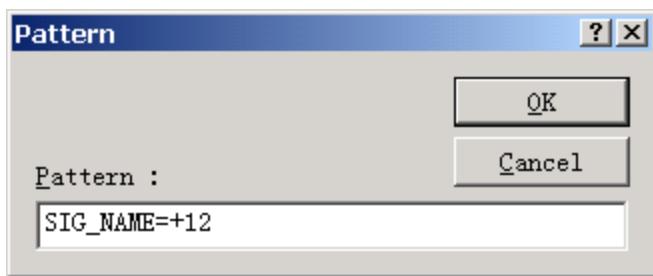

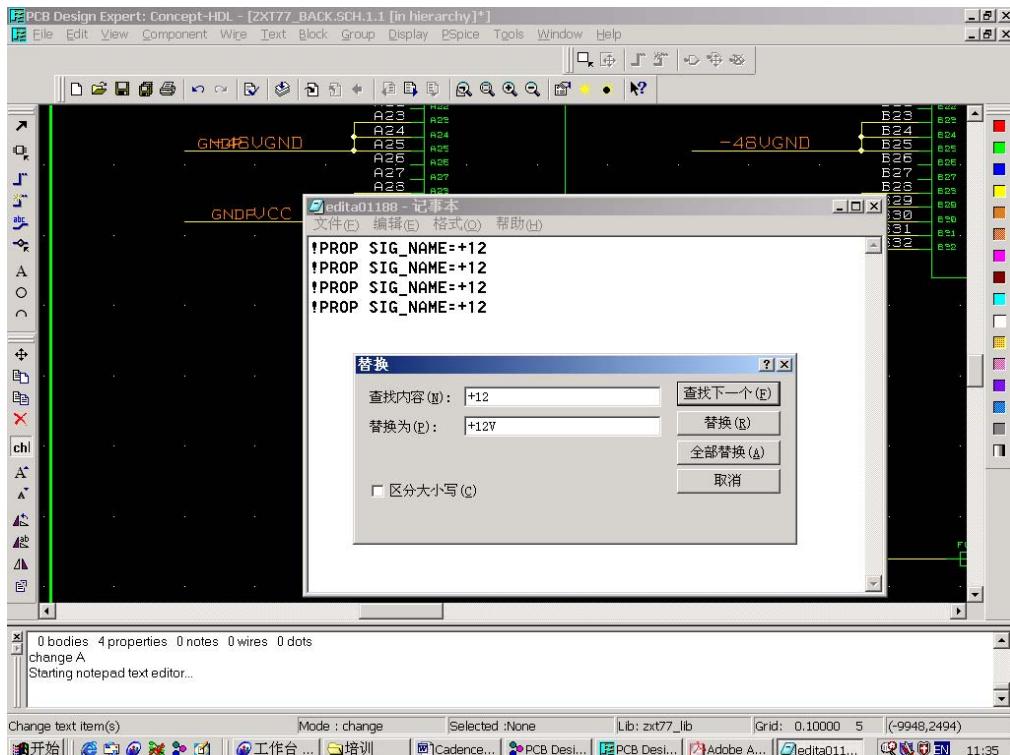

如果想把当前页的网络 +12 改为 +12V，执行 GROUP BY EXPRESSION ...

在 Pattern 中的 Pattern 中填入等式 SIG\_NAME=+12 或者 +12，当前页的所用的 SIG\_NAME=+12 的属性值高亮，再执行 GROUP—TEXT CHANGE，电解鼠标右键，选择 EDIT，从文本编辑窗口中通过替换操作，可以把当前页的所有 +12V 网络名换成 +12V。

## 5.11 常用命令

在 Concept HDL 中对元件的常规操作，如 move、copy、delete 等都在 Edit 菜单下，也可以通过 View->Toolbars 将这些命令选择放在主界面下。这些命令与一般的软件类似，就不再一一阐述。

### 5.8.20 5.11.1 常用的快捷键

系统默认的一些快捷键有：

F1：帮助

F2：Windows Fit(全屏显示)

F3：Display Both (属性的 Value 和 Name 都显示)

F4：Display Attachment (显示连接关系)

F5：Refresh (刷新屏幕)

F6: Show Property (显示属性)

F11: Windows in (放大)

F12: Windows out (缩小)

Ctrl+方向键: 移动屏幕 (也可用鼠标右键)

Tools->Cusomize->Key 中可以自己定义快捷键。

### 5.8.21 5.11.2 检查连接关系

通过执行 Display - Attachments 命令可以显示所有元件和线网属性的连接关系，信号名总是连接在相关网络的中间，如果从属线指向了线网段的末端，则表示你错误的将该信号添加给了一个管脚。

也可以启动智能感应功能查看信号名，执行 View—Data Tip 可以启动该功能，此时，只需把鼠标放在信号线上，即可报告该信号名。鼠标放在元件其它属性上则报告其它属性。

### 5.8.22 5.11.3 点画命令

点画命令是 Cadence 独特的一种快捷方式，可以直接用鼠标在屏幕上写特定的笔划，不同的笔划表示不同的命令。例如，Z 表示放大，W 表示整体显示，M 表示移动，C 表示拷贝等。按下鼠标左键，并写字母 Z，则 concept 会自动将原理图放大到 Z 所包括的区域，用同样的方法画 W 则 concept 会自动满屏显示全图。

用户可根据自己的习惯来定义笔划，如何定义可以参看帮助。

### 5.8.23 5.11.4 查找元件和网络

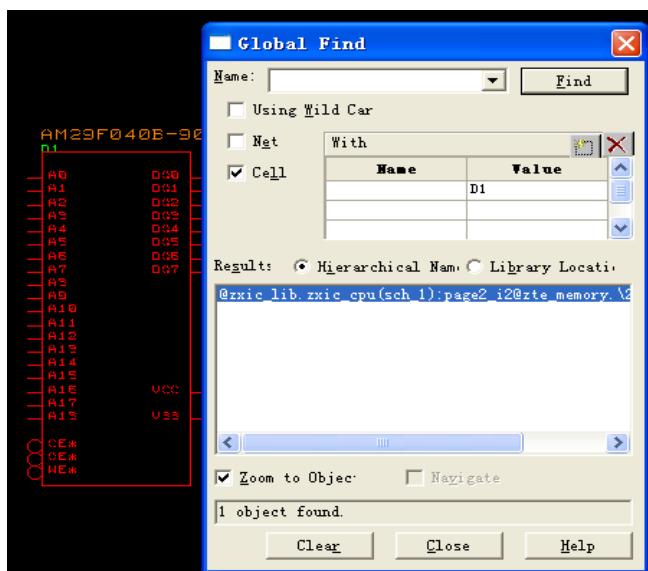

在多页原理图设计中，原理图的展开可以使用户深入到设计的每一层每一页，以便对设计进行全局的跟踪、查找。原理图展开后，用户的设计将成为一个整体保存在数据库中。展开的方法是 Tools->Expand Design。

原理图展开后，用户可以进行器件、网络的查找。方法是 Tools->Global Find，如下图所示，在 Name 中输入想要查找的网络和器件名，点击 Find，点击列表中的器件或网络，该器件或网络就会 Hightlight 显示，其中 Hierarchical Name 和 Library Location 是查看方式选项。

跟踪网络的方法是 Tools->Global Navigate，出现对话框后，点击任意 wire，则与该 wire 相连网络的会被加入列表，点击列表中的任意网络均会被 Highlight 显示。

#### **5.8.24 两个不同网络名的网络连接的方法**

需要将两个不同网络名的网络相连接时，使用 Standard 库中 Alias 将其相连，如下图：

#### **5.8.25 5.11.6 错误检查**

Concept-HDL 具有很强的的查错功能，默认情况下，系统会在每次存盘时对原理图进行错误检查。检查类型包括电连接检查、图符检查、名字检查、其它检查。用户可以在 Tools->Option->Check 标签下进行设定。用户也可点击 Tools->Check 进行实时检查。另外，Cadence 还提供更强大的查错工具----CheckPlus，它在 Project Manager->Tools 下，具体的设定和使用，用户可以查阅帮助文件（安装目录\doc\checkplus\checkplus.pdf）。

#### **5.8.26 5.11.7 检查Cadence原理图单个网络名**

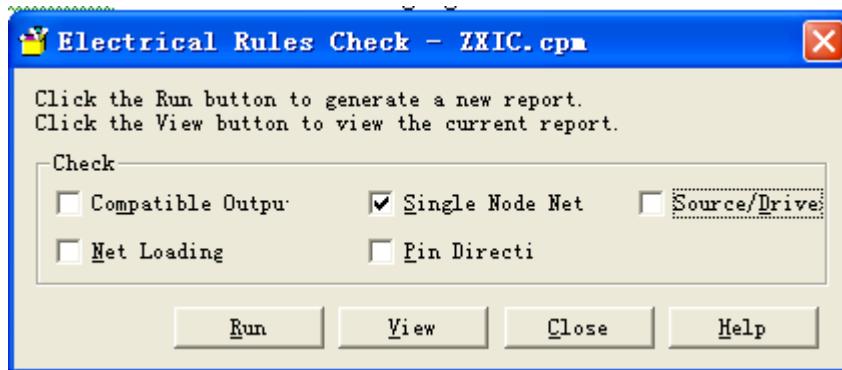

在制作电原理图经常会因为手误等原因会造成有单网络的出现，CADENCE软件同样可以进行单网络的检查。在Concept-HDL或者Project Manager界面下选择菜单Tools—Packager Utilities—Electrical rules Check:

选择single node net----Run执行后将产生一个单网络警告的报告，从报告中可知何处出现了单网络。需要注意的是：此命令是通过检查网表文件来执行的，所以在执行此命令前必须要先通过Exports physical产生输出网表。

### **5.8.27 5.11.8 对隐藏了电源和地腿的器件定义电源和地信号**

对隐藏了电源和地腿的 IC 来说，电源和地在 Chips 文件中做了详细说明。为了取代 Chips.prt 文件中定义的 POWER\_PINS 属性，通常在原理图上，给元件添加 POWER\_PINS 属性和 POWER\_GROUP 属性。**POWER\_PINS 属性必须对该元件的所有电源和地腿加以定义**，而不能只定义你想取代的那条管脚。**POWER\_GROUP 属性指一种电源或者地网络重新命名**。

检查你的原理图是否有隐含的电源管脚。如果有请给该元件定义电源管脚属性，同一电源网络的管脚用 “,” 隔开，不同电源网络用 “;” 隔开。例如：

Cadence74hc 库芯片 74HC253，POWER\_PINS=(+5V:16; GNDD:8)，等价于

POWER\_GROUP=VCC=+5V 和 POWER\_GROUP=VCC=GNDD。

芯片 74FCT16245 POWER\_PINS=(VCC:7, 18, 31, 42; GND:45, 4, 10, 15, 21, 28, 34, 39)。

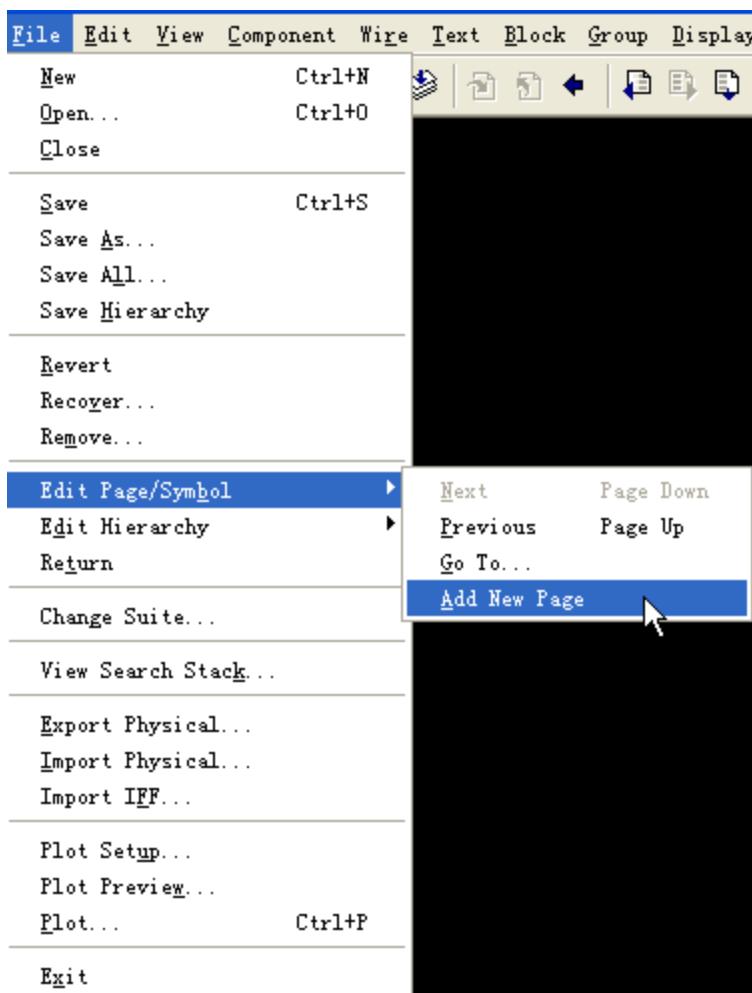

## **5.12 增加新的原理图页**

一般的原理图都有多页，当设计完第一页后，在 File->Edit Page/symbol->Add new page 下增加新的页，增加完后在标题栏中显示新的文件信息，如第一页是 ZXIC\_CPU.SCH.1.1，则标题栏现在会变成 ZXIC\_CPU.SCH.1.2。

## 5.13 原理图多页面操作

Concept-HDL 可以实现多页面间的内容交换和复制，通过 Copy 或 Move 等命令进行操作，在 Windoes --> New Window 切换不同的页面。多页面操作时，光标所在的窗口为当前活动窗口。

## 5.14 信号的页区位置交叉标注（Cross Reference）

### 5.8.28 5.14.1 信号的页区位置交叉标注（Cross Reference）的作用（交叉标准既是标明该信号出现在哪些页的哪个位置上，每页的特性是什么）

目前由于板级设计原理图页面往往超过 10 页，一个信号横跨多页，给阅读图纸造成很大的不便，所以需要标注信号在多页面中的页区位置，Concept-HDL 可以自动进行信号页面位置标注。

### 5.8.29 5.14.2 交叉标注需注意的几点:

- 1、必须加上图幅。否则无法标注。

- 2、缺省情况下，对于未加上出页符（OFFPAGE）的信号线是不标注，所以需要进行选项设置，在标注内容选项中选中“Cref Signals Not Connected to Flag Bodies”。

- 3、如果绘制原理图上未考虑留有足够的标注空间，会导致运行时间过长，可在绘制原理图时，考虑间隔大些。

- 4)、如果电源管脚是显性的，当在标注内容选项中选中“Cref Signals Not Connected to FlagBodies”后会对电源信号进行标注，因而建议对逻辑信号加上出页符，或对电源管脚采用隐性绘制方式（如我们库中的 POWER\_GROUP=POWER\_NAME=%POWER\_NAME）。

### 5.8.30 5.14.3 信号的交叉标注（Cross Reference）的方法

对于使用了出页符号或出模块符号的出页信号的交叉标注方法：当原理图绘制完毕并经规则检查无错误后，存盘并且 Export Physical 之后，在 Project Manager 中，Tools --> CRefer --> Options (设置) --> Run。标注结果如下图示：

图中对原理图中的出页信号加了出页符号，并交叉标注出信号的页区位置，其中：1C4<>表示本页的信号 SIGA 输出至第一页 C4 区，该信号所接的器件管脚属性为双向。

出页符号使用 OFFPG，(或用 STANDARD 库中的 OFFPAGE，每次安装 CADENCE 后都应将 OFFPG 的 SYM 覆盖 OFFPAGE 的 SYM。) 出页符号的六个 Version 见图 8，分别为输入、输出、双向。

出页符号 OFFPG 设置了五个交叉标注的位置，当交叉标注超过 5 个时，超过的部分将重叠在第五个的位置上，见下图。当图面位置允许时，建议设计者将其手工调整。

### 5.8.31 5.14.4 层次设计中出模块信号的交叉标注

层次设计中出模块信号的交叉标注要求，同出页信号的交叉标注。使用的符号为：

IOPORT (双向信号), IMPORT (输入信号), OUTPORT (输出信号), 符号见图 10。

### 5.8.32 5.14.5 出页信号的交叉标注的要求

各个产品事业部可以根据情况，针对各个单板的特点，采用以下三种出页信号的交叉标注的要求：

- 1、对图中所有的出页信号都要求采用交叉标注。

- 2、对图中部分主要的出页信号要求采用交叉标注。主要适用于大的背板。

- 3、不要求对图中的出页信号采用交叉标注。

## 5.15 在不同的project下实现原理图拷贝

Cadence PSD 的工程采用 Library/Cell/View 的层次结构存放，类似于原理图库。设计(cell)存放于工作库，原理图则存放于设计的视图(View)下。为保证数据的完整性，严禁在 Windwos 资源管理器中进行原理图页复制。原理图复制包含不同工程间的复制和同一工程内部的复制。下面只介绍不同工程间的复制：

例子：拷贝 F:\VXI\worklib\rclk\sch\_1 的 page4 到 F:\CPCI\worklib\lvds\sch\_1 的 page4。工程 VXI 为源工程，rclk 属于该工程的一个单板。CPCI 为目标工程，lvds 属于该工程的一个单板。

1、用文本编辑器打开目标工程 CPCI 的库索引文件 cds.lib。

2、在目标工程 cds.lib 中增加源工程工作库 worklib 的库索引语句：

```

DEFINE vxi_lib F:\VXI\worklib

```

说明：vxi\_lib 现在即代表源工程的工作库。

3、确保目标工程 cds.lib 包含了源工程的其它库的库索引语句。如果没有，就要加上。例如：

```

DEFINE vxi_buildlib F:\VXI\vxi_buildlib

```

说明：vxi\_buildlib 现在即代表源工程的临时原理图库。

4、保存目标工程的 cds.lib。

5、打开目标工程。

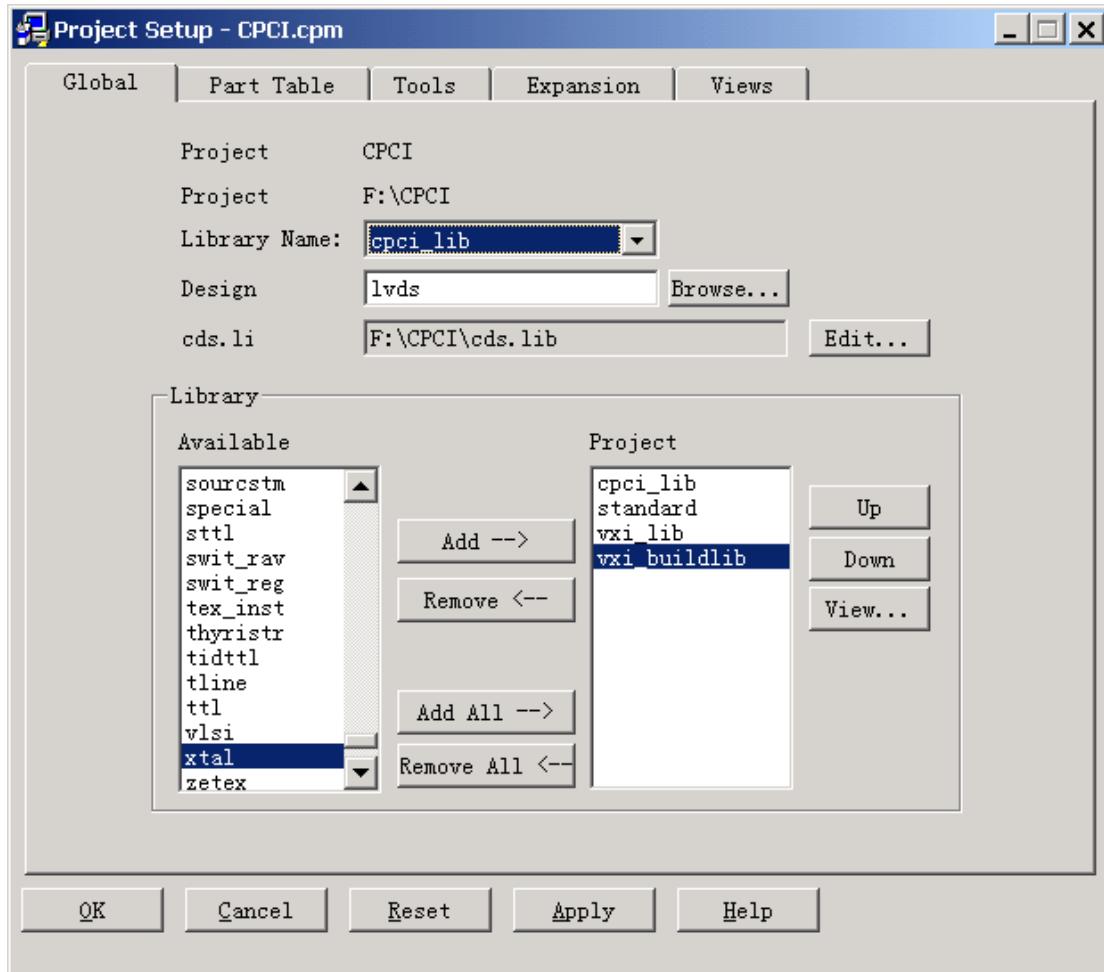

6、选择 Tools > Setup。

*Project Setup* 对话窗口显示。

7、选择 *Global tab*。

8、在 *Available Libraries list* 中选择在步骤 2 和步骤 3 中增加的库。

9、点击 *OK*。

10、在 project Manager 中选择 *Tools > Concept* 启动 concept。

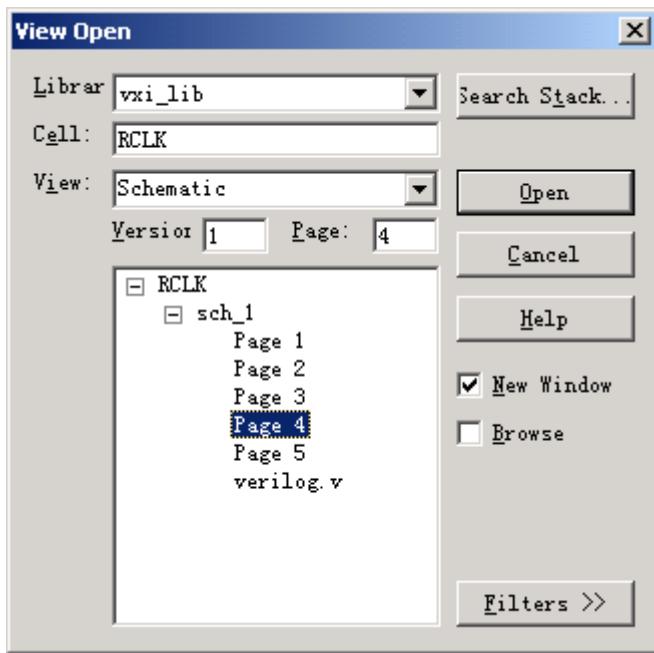

11、执行 *File > Open*。

12、从 *Library drop-down list* 中选择 RCLK\sch\_1\Page 4。

15、点击 *Open*。

Concept HDL 中显示该页原理图。Concept HDL 标题显示 RCLK.SCH.1.4。

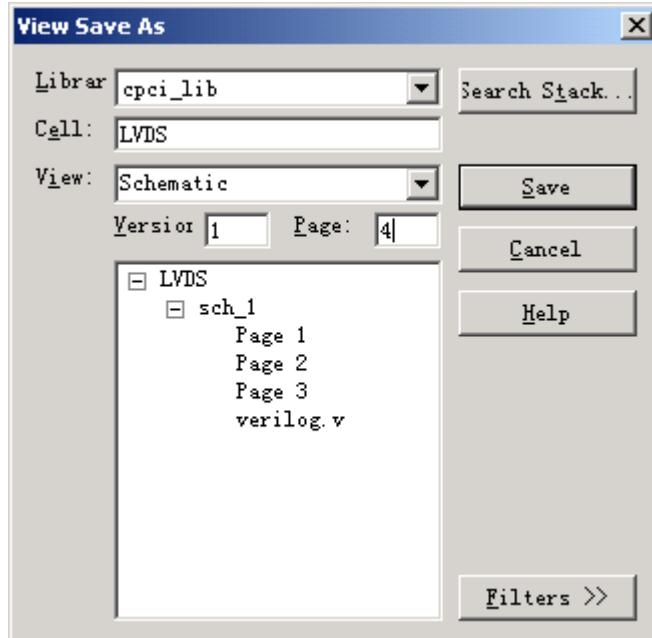

16、执行 *File > Save As*。

显示 *Save As* 对话框。

17、从 *Library* drop-down list 中选择 LVDS\sch\_1\Page 4，点击 *save*。

说明：点击 save 后，Concept HDL 标题显示 LVDS.SCH.1.10。这表明已经把源工程的原理图 F:\VXI\worklib\rclk\sch\_1 的 page4 存到 F:\CPCI\worklib\lvds\sch\_1 的 page 4。

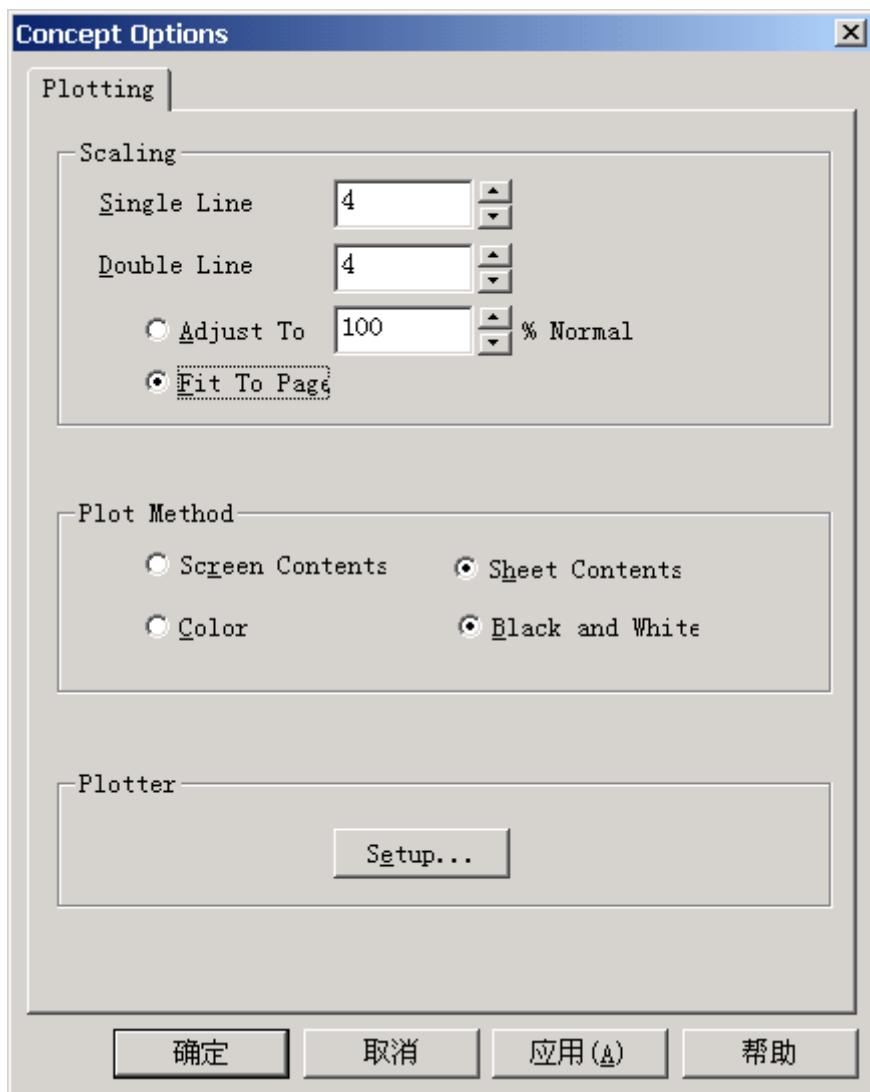

## 5.16 打印图纸

选择 File—Plot Setup，调出 Concept 的设置表格。

在 Plotting Section 中，选中如下选项：

\*Fit to page

\*Sheet Contents

\*Black and White

Single Line 填 4，Double Line 填 4。

点击 Setup。在打印设置表格中，按你的边框尺寸，选择方向。

选择好打印机型号。

点击 OK 退出打印设置表格。

选择 File—Plot Preview 预显示窗口中将显示实际要绘出的原理图，所见即所得。

点击 File-Plot ，选择打印范围，点击 Plot 打印。

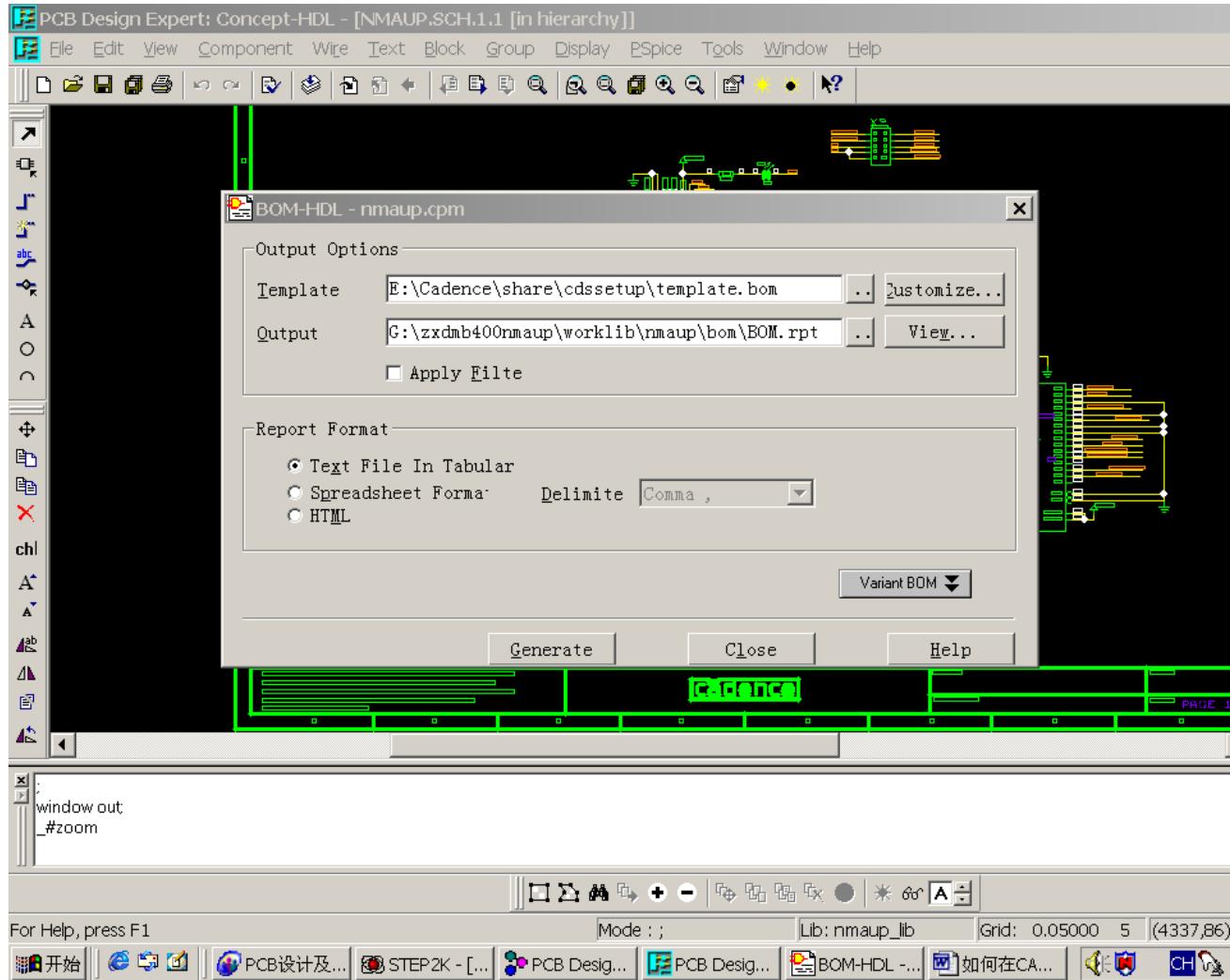

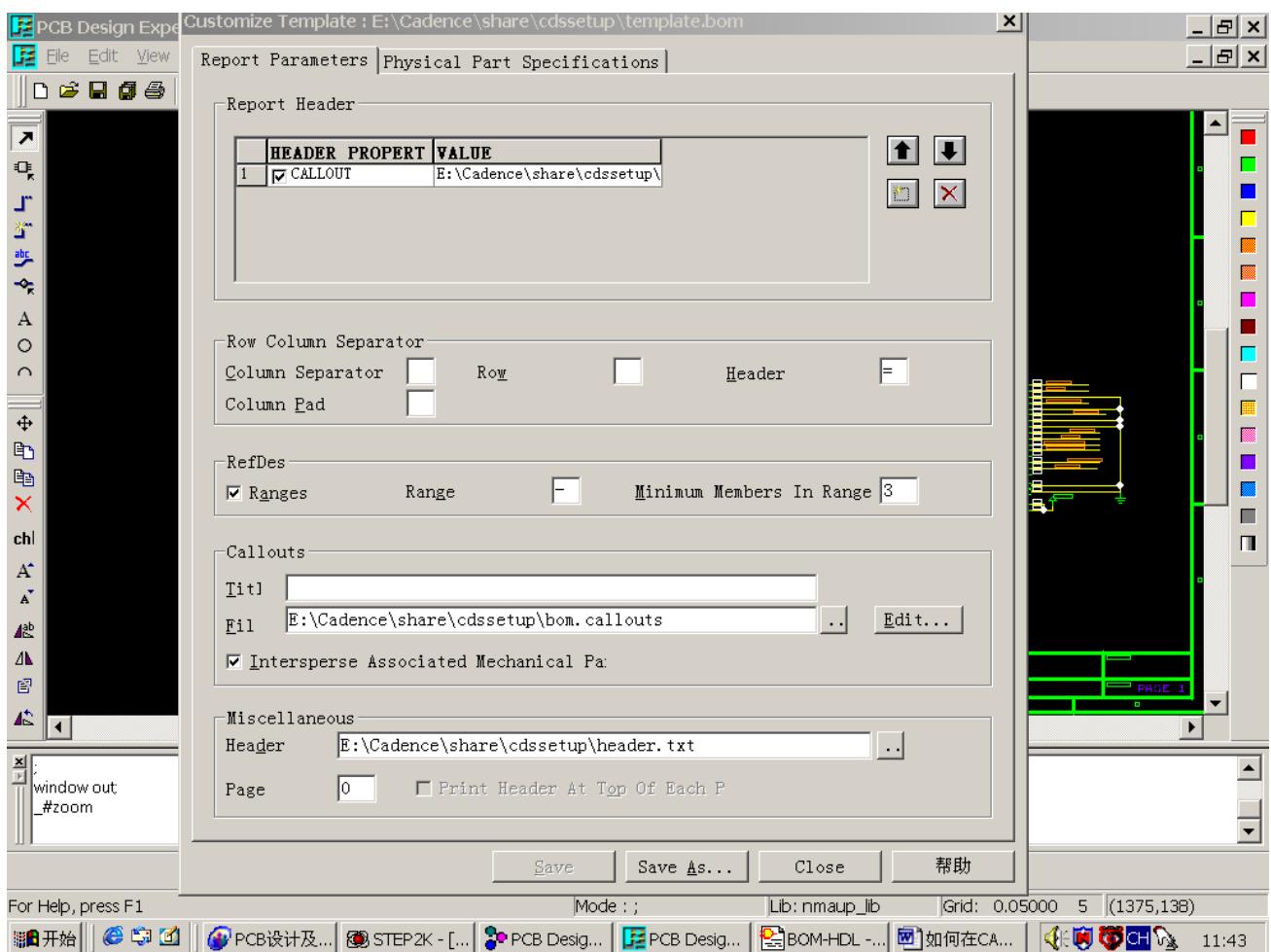

## 5.17 自动生成料单

在 Concept-HDL 中可以自动生成材料清单，执行 Tools-Packager Utilities-Bill OF Materials 即可。但现在一般要求生成在 STEP2000 可直接调用的料单，这需要两个文件 template.bom、header.txt，将这两个文件下载到 CADENCE 安装目录：\CADENCE\PSD\_14.2\share\cdssetup\ 下。

在 Concept-HDL 生成在 STEP2000 可直接调用的料单步骤如下：

1、打开原理图，执行 Tools-Packager Utilities-Bill Of Materials。

如下图，将 Template 指向上面拷贝的\*.BOM 模板文件：

2、执行 Customize，

使 Callouts file,Miscellaneous header 均指向正确的路径。如图所示：

3、返回到第一步，点击 Generate，生成料单，请注意：因为原理图没有包含辅料，所以还要对生成的料单进行一些必要的编辑，包括料单代码，特殊工艺，辅料添加到最后几行，文本格式如：

**BOM.RPT**

4、完成\*.RPT 文件的编辑,进入 STEP2000 料单管理系统中执行“文件生成料单”命令，即可自动生成料单。以后为了完成 VALOR 检查，还需要进行 AVL 料单的生成。

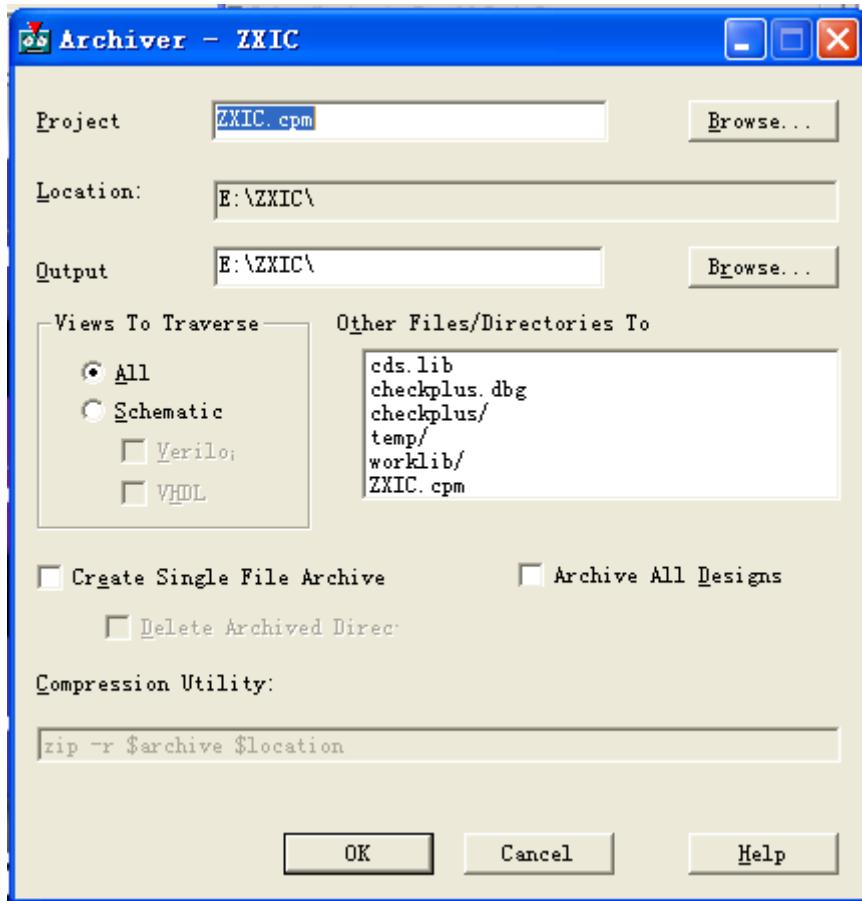

## 5.18 原理图归档

在完成一个设计项目之后，如果您需要将该项目存档，以提交 EDA 工程师设计 PCB 或报有关人员审核，您可以使用“归档”(Archive)功能。归档的意义在于使得库索引文件索引到的系统库以及设计人员放在工程文件夹外的库文件自动拷贝到工程文件内部新定义的文件夹，增加工程文件的可移植性，使得别人在打开原理图时软件不会报告找不到某个库。

在 Project Manager 中，执行 Tools -> Archive -> New Archive 便可调出归档定义窗口：

在这里，您可以根据需要对所有设计或指定原理图的 View 进行归档。归档工具将自动筛选该设计所使用到的库进行保存。

选择 **Create Single File Archive** 指对当前设计进行归档。当前设计指在 Project Setup 中指定的 Design。选择 **Archive All Designs** 指对整个工程归档。一个工程可以包含多个 Design，这里 Design 可以看作单板（或者一个子模块——底层设计），如果对各个设计单独归档，必须先在 Project Setup 中指定 Design，再执行 Tools -> Archive -> New Archive。每归档完一个设计，就重新进入 Project Setup 指定新的设计，再归档，如此重复，直至规完所有的设计。如果选择 **Archive All Designs**，则把整个工程文件归档在一起。

## 5.19 原理图评审

原理图设计完成后，应根据流程进行评审，通过后再开始进行 PCB 设计。具体评审流程每个事业部都有相关规定。

## 第六章 从原理图到PCB

### 6.1 从原理图到PCB的实现

原理图设计完后，需要将原理图的信息转移到 PCB 中，这个可以通过 Project Manager 中的“Design Sync”（设计同步）来实现，同样 PCB 的信息也可以通过“Design Sync”转移到原理图中。

#### 5.8.33 .1 原理图到PCB的转换过程:

1、打开 project，从 Project Manager 中，点击 Layout 图标，进入 Allegro (PCB 设计工具) 中，如图：

在 ALLEGRO 中，保存一板文件退出（如 ZXIC-CPU-030900.brd）。

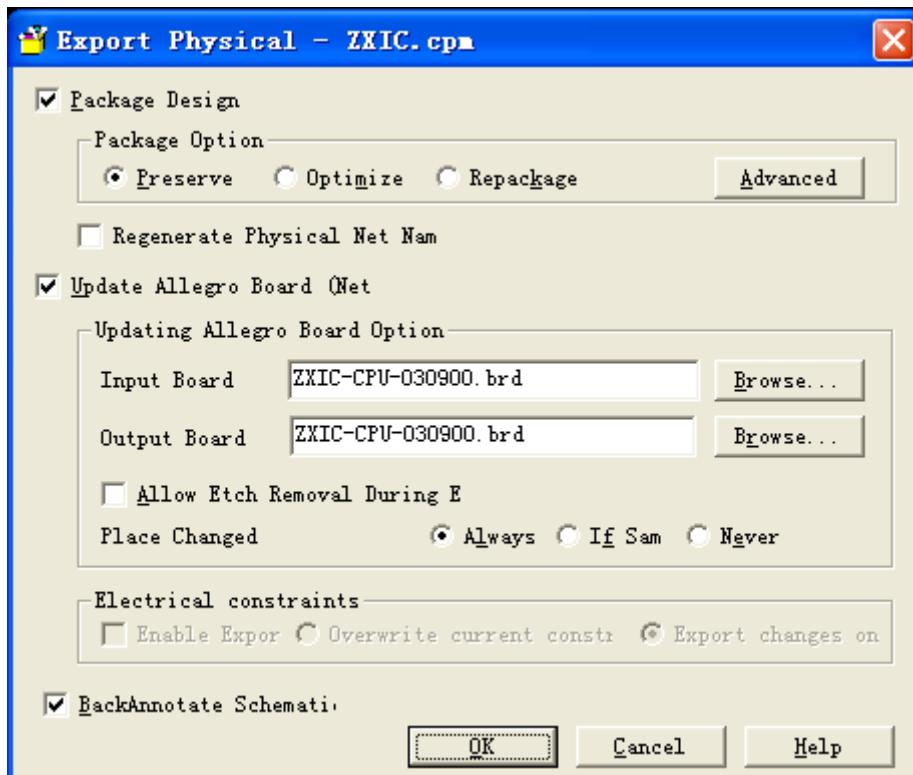

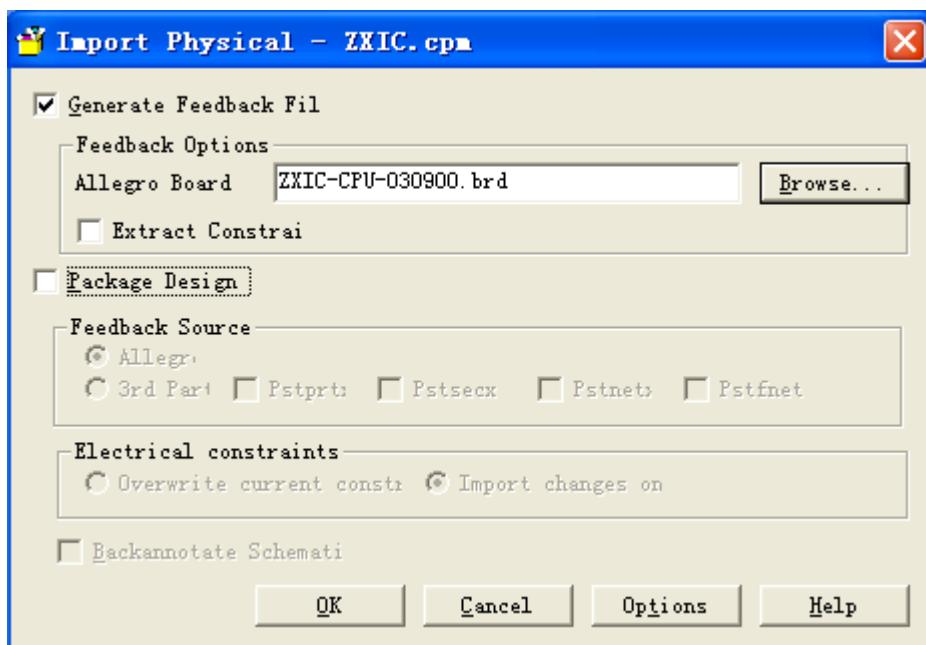

2、通过“Design Entry”打开原理图，在原理图中，点击 File-Export Physical，进入下面的界面。

注意：Input Board ,Output Board 均指向 ZXIC-CPU-030900.brd。

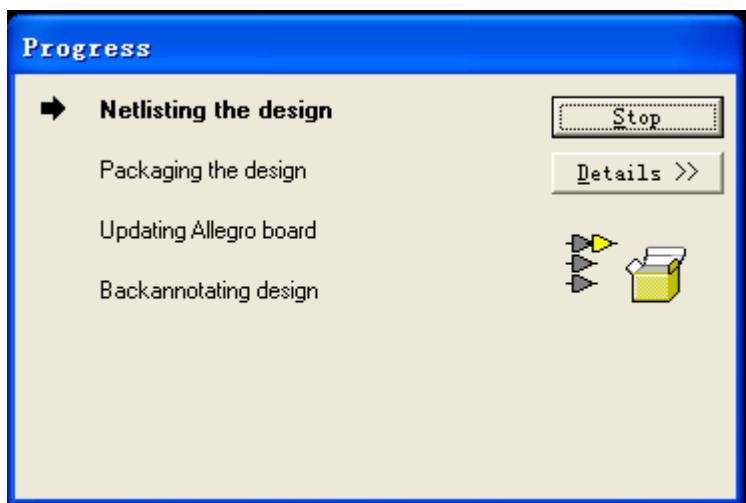

3、点击 OK 键，开始打包，如图：

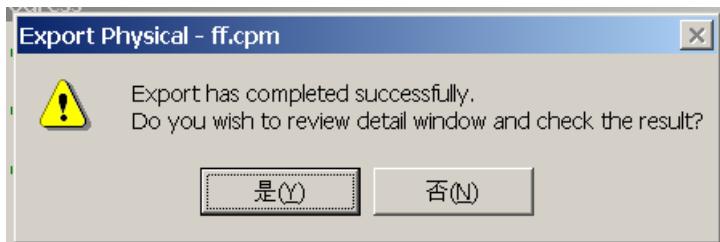

如能成功打包，则有如下提示：

完成了上述工作，则原理图的信息已成功地转移到 PCB 中。

## 第七章 PCB设计

### 7.1 导入数据

通过第六章从原理图到 PCB 的过程可以将原理图的数据，如网表、封装等导入到 PCB 中；或通过 Project Manager 的“Design sync”中 import physical 也可以导入数据，如图所示：

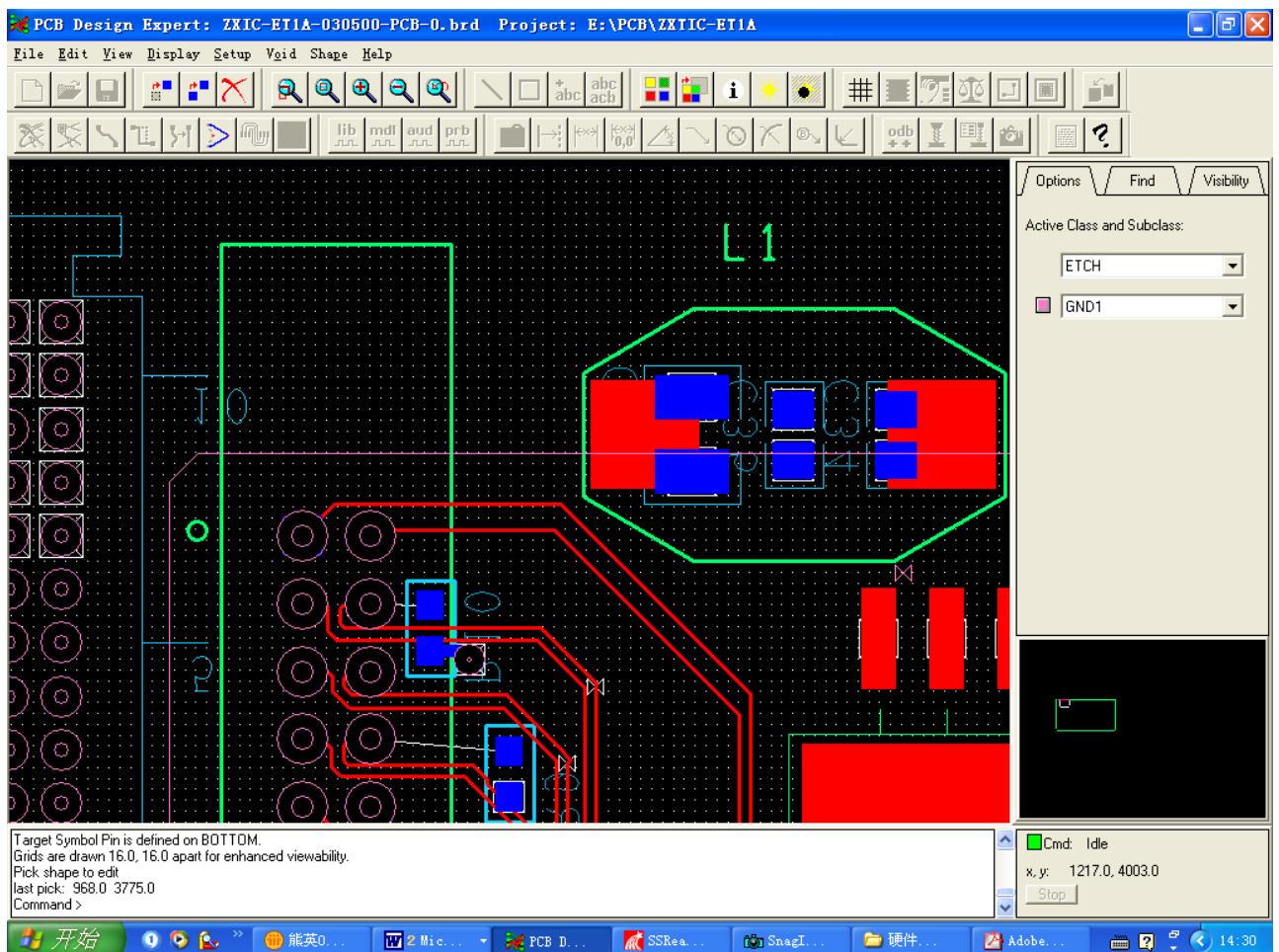

### 7.2 Allegro用户界面

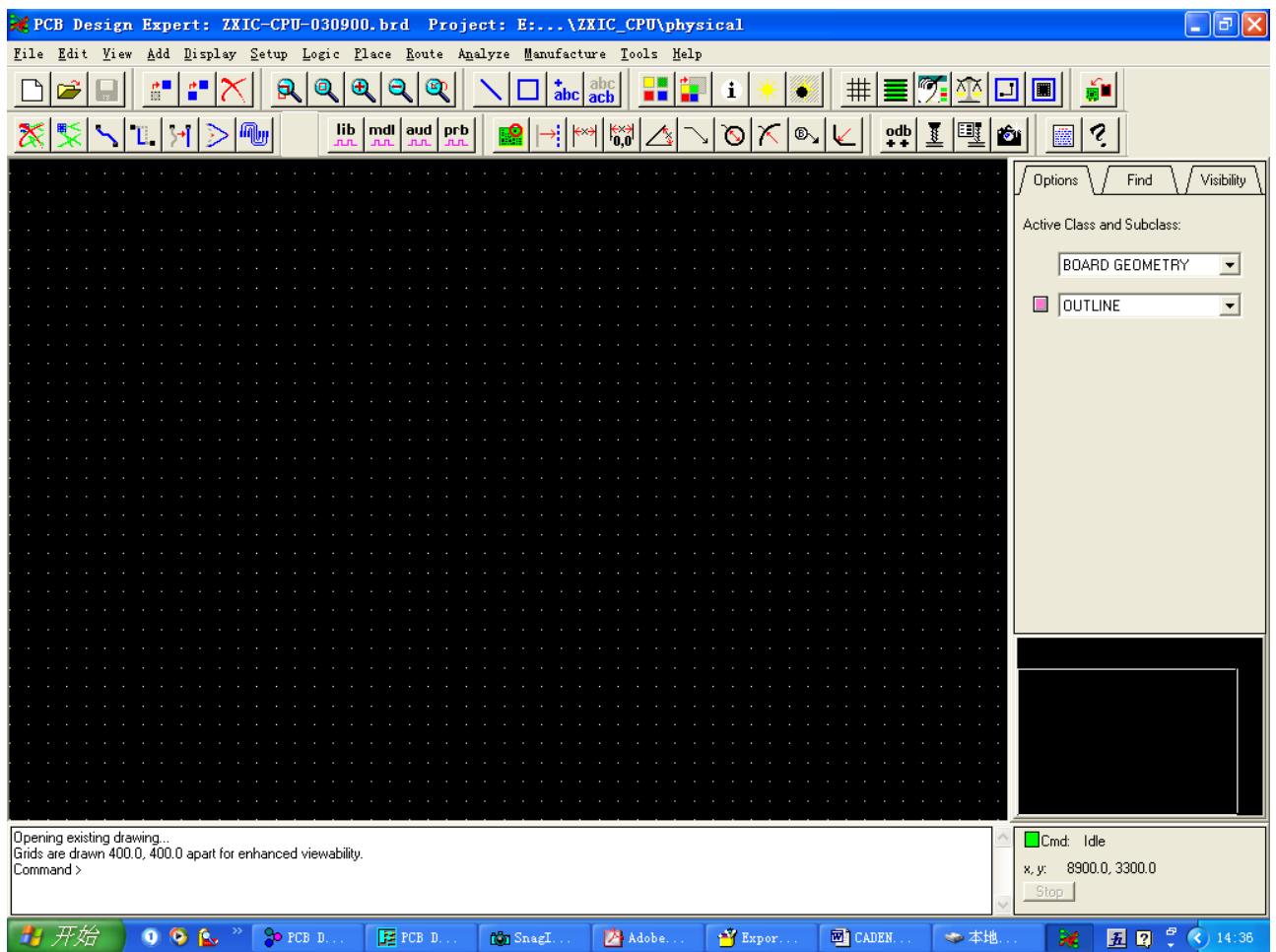

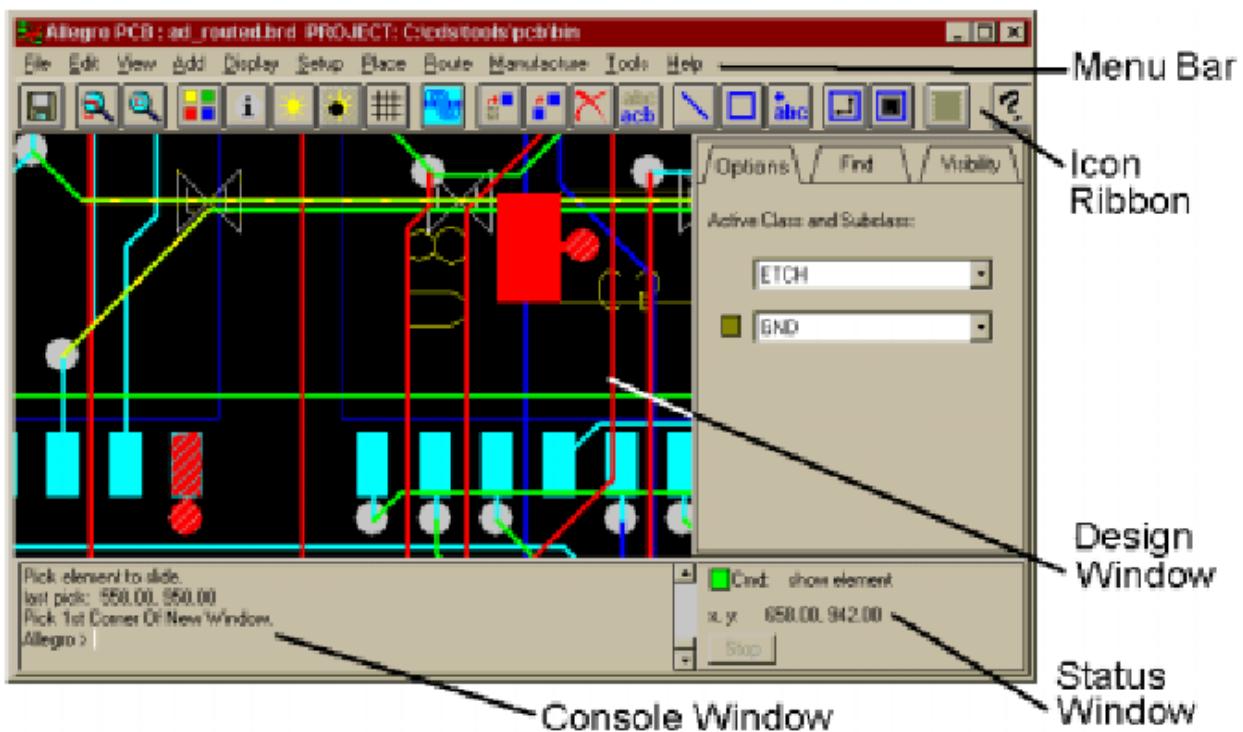

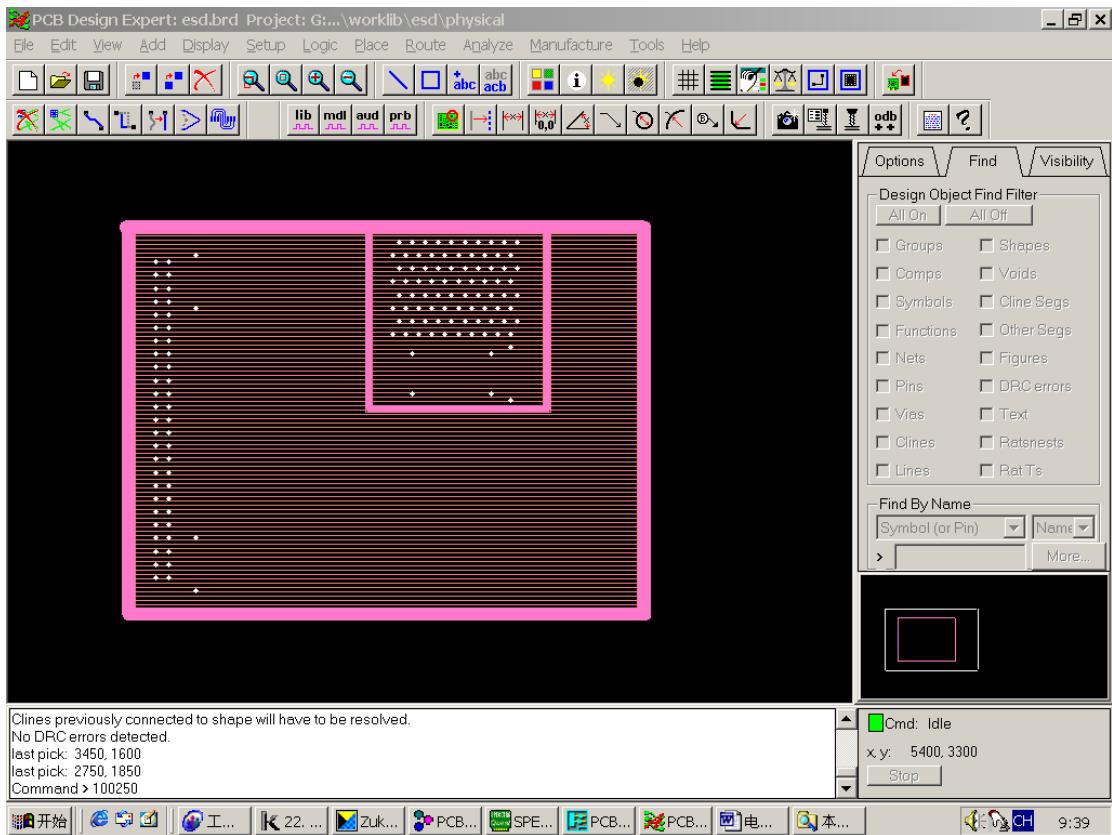

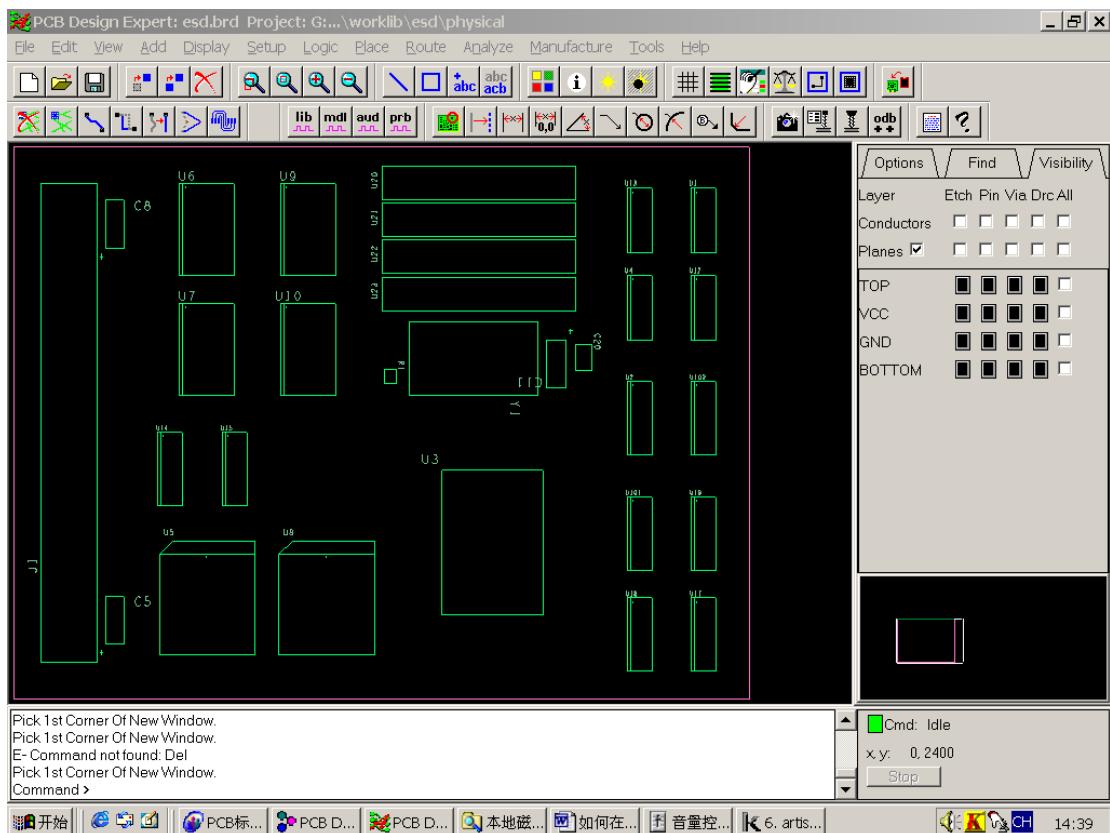

用 Layout 打开 brd 文件，进入 Allegro 用户界面，下图是 Allegro 用户界面，主要包括了菜单栏、图表栏、设计窗口、命令窗口、状态窗口和控制面板等：

### 5.8.34 7.2.1 控制面板的作用

控制面板如下图所示，包括三个可选按钮即：Option、Find 及 Visibility，还有一个全局视窗位于下方。

全局视窗允许你有选择的对图中的元素进行操作及快速定位，缩放图中的某个区域。

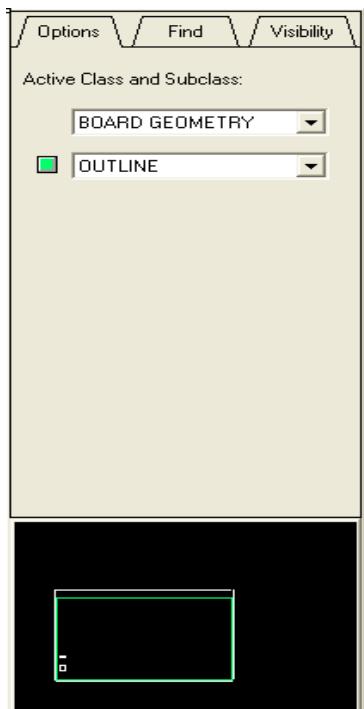

通过控制面板的 Option 标签可选择被激活的类或子类，在 Allegro 数据库中，所有元素都只有一个类属性（CLASS）或子类属性（SUBCLASS）。如下图所示，CLASS 为 BOARD GEOMETRY，SUBCLASS 包括 OUTLINE 等选项，相似的类构成组（GROUP），如 Etch 、Pin、 Via、 DRC 等都属于 Stack-up 组。

通过控制面板的 Find 标签，可以选择各种元素，如 Nets、Lines、Vias 等，当执行各种命令时，都需要在 Find 标签中选择好相应的元素。

通过控制面板的 Visibility 标签，可以选择 Etch 、Pin、 Via、 DRC 的各个子类的可视性。

控制面板可以移到屏幕的任何地方：在 View->Customization->display 下，可选择控制面板的位置。

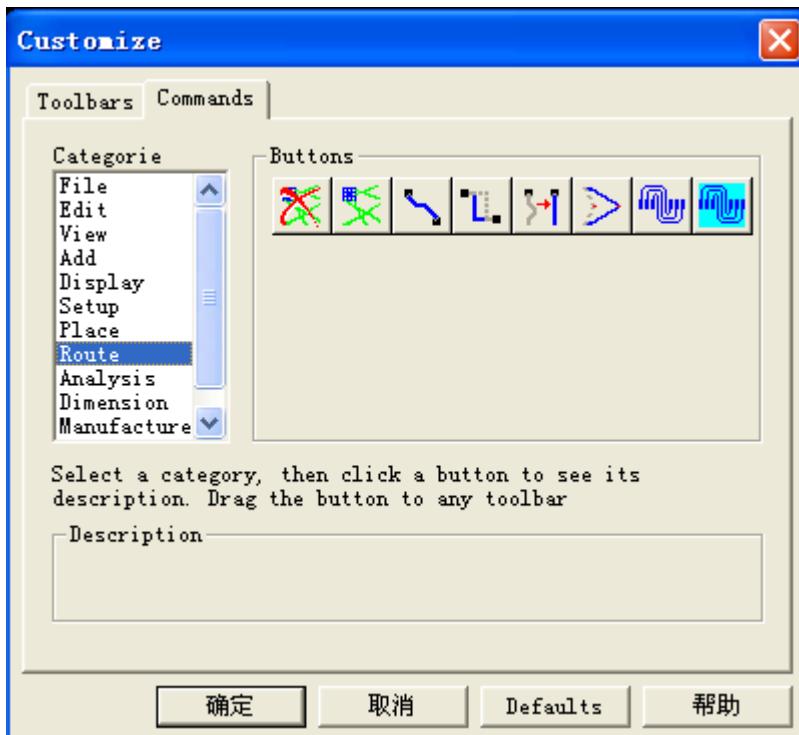

### 5.8.35 工具栏的显示

View->Customization->Toolbar 下可选择各种工具放在用户界面上，通过 commands 可以将单个按键放到用户界面上。

如果要查看某个元件的信息，可以通过 Display->Element，或单击图标 。

## 7.3 Layout准备

### 5.8.36 7.3.1 创建PCB图的物理外形

根据结构图，开始进行外形设计，有两种方法：

#### 7.3.1.1 通过创建封装符号的方法创建板物理外形

有些板外框应通过创建封装符号的方法创建，这样封装符号可以保存到库中，以后可以重用，特别适用于同一种规格、同一种类型的板图设计具有相同的物理板图条件。方法如下：

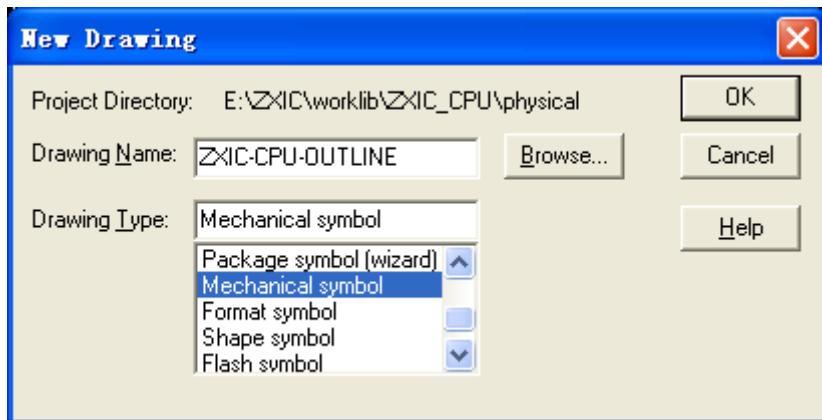

1、File->new，出现以下界面，选择“Mechanical symbol”，输入文件名：

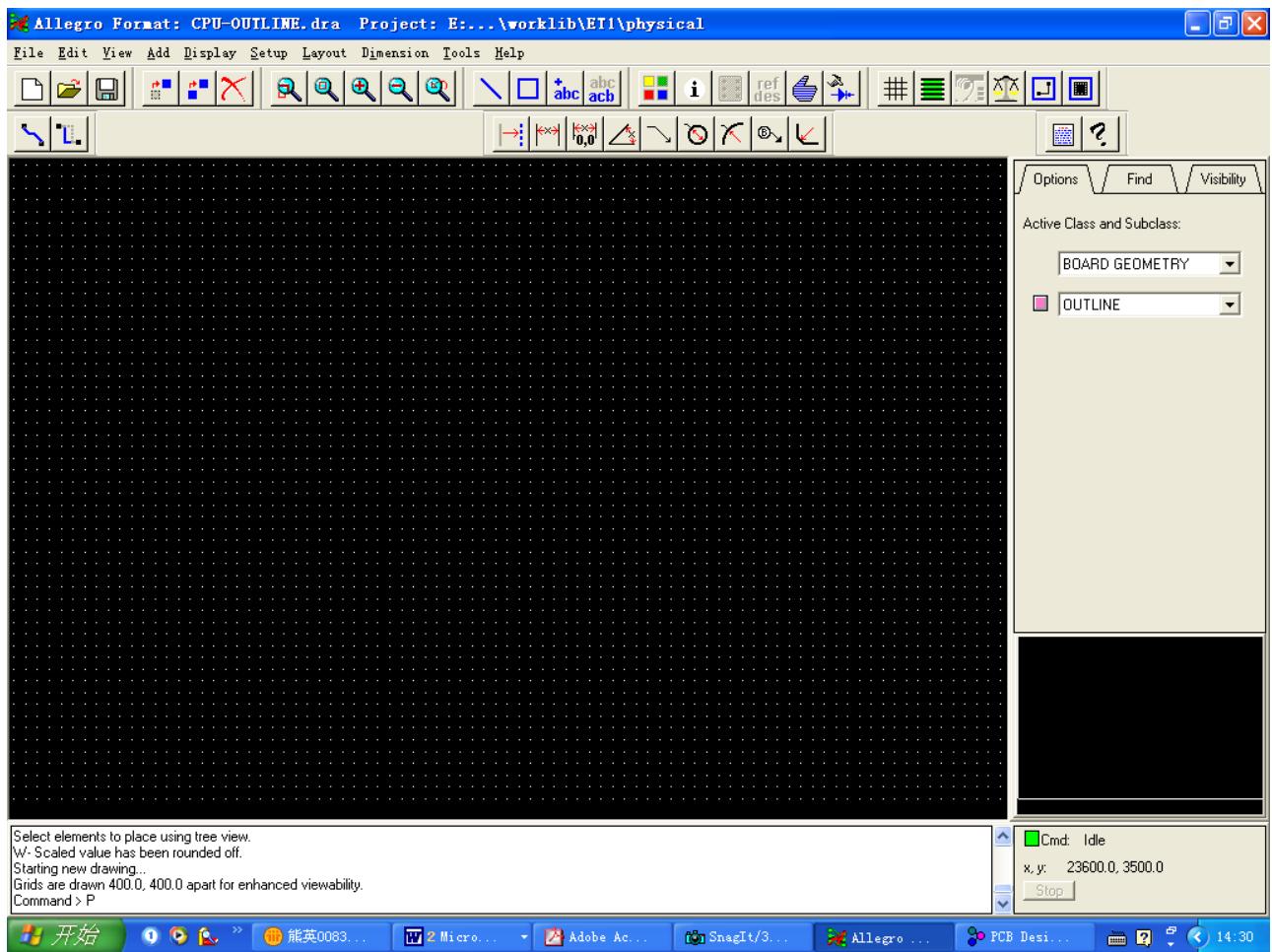

点击 OK 后进入以下界面：

2、打开 ADD->Line 或点击 ，在控制面板在 BOARD GEOMETRY 下选择 OUTLINE，画外框：

用 Allegro 的命令行以绝对尺寸方式输入 X、Y 座标(如: x 1900 1800)或增量座标(如: ix -900)，画出板外形。

3、如板外形需要倒角，在 Dimension/draft->Chamfer (倒斜角) or Fillet (倒圆角)，在控制面板的 Option 下选项角度或半径，再选择两条相交线进行倒角。

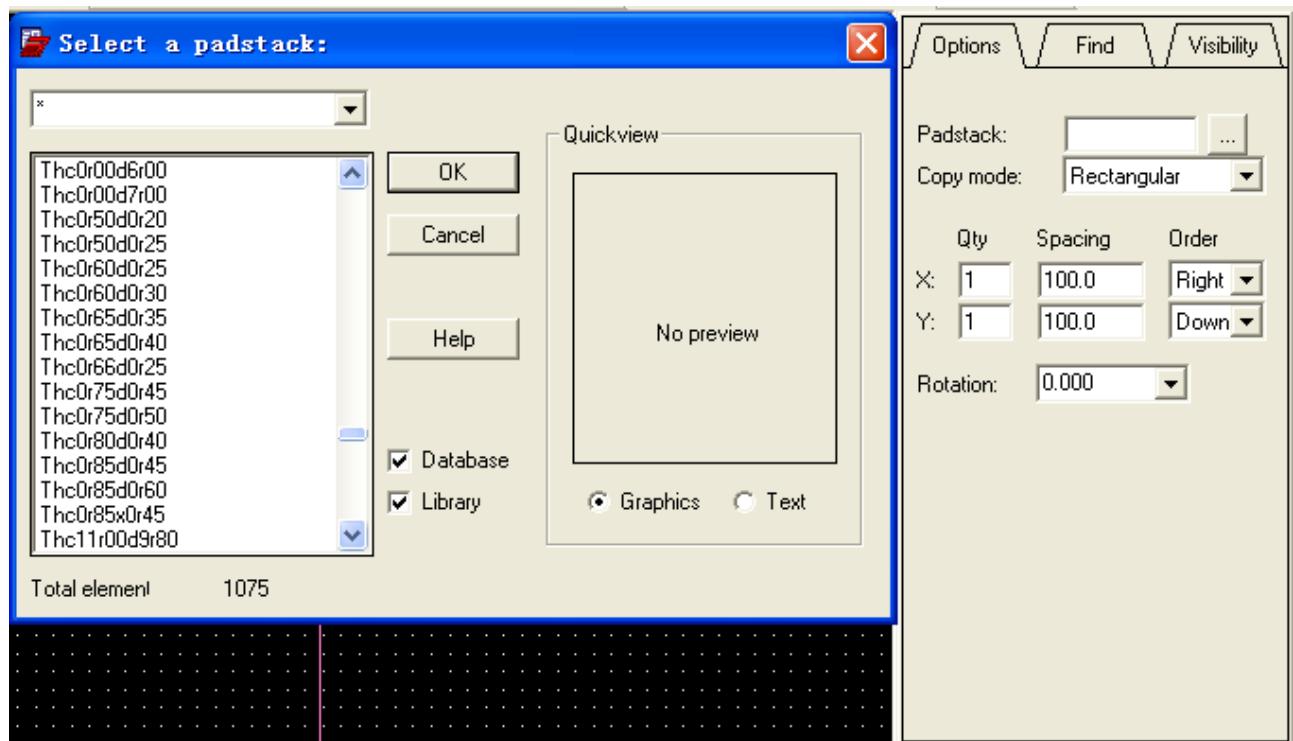

4、打开 Layout->Pins，控制面板如下图所示，点击选择 Padstack，并选择数量和间距来放置安装孔。

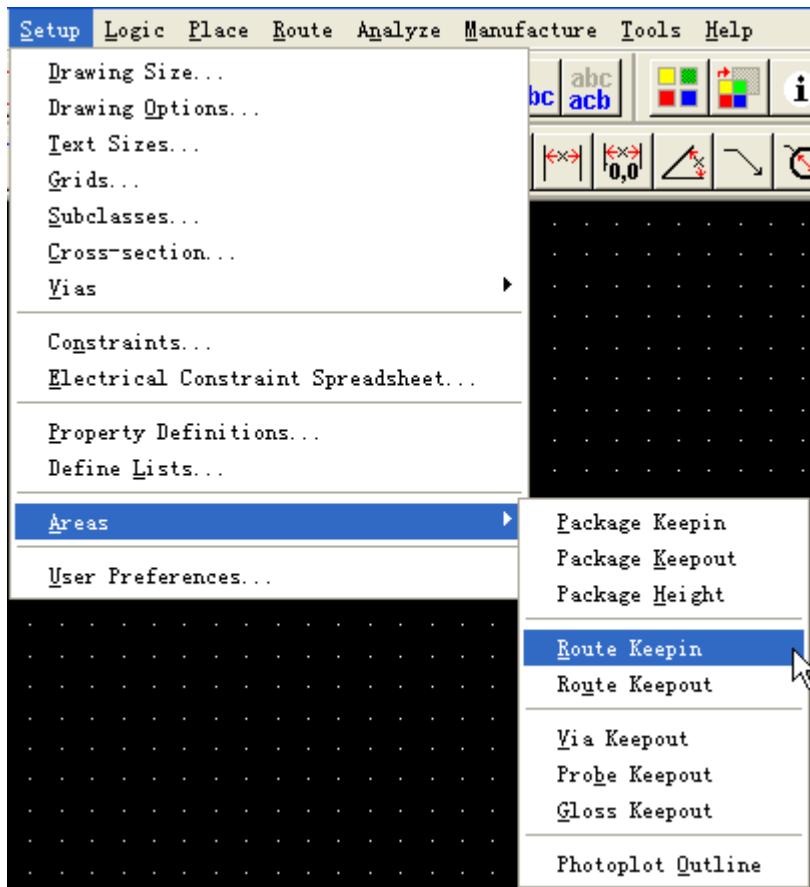

5、定义板区域：用 Setup->Areas 命令定义各种约束区域，如下图所示：

6、标注尺寸：点击 等命令来标注尺寸。

7、保存板图符号：先 File->Create symbol 保存板图封号，再通过 File->save as 保存成 dra 文件。将 bsm 和 dra 文件保存到封装符号库中，通过 2.5.1.1 的第 3 步的方法调用封装库时，板外形就会作为一个封装封号出现在 Mechanical symbols 下。

### 7.3.1.2 在Allegro界面下创建板外框：

对于一些简单、无须重用的板外形，可以直接在在 Allegro 界面下创建板外框：

1、 打开 ADD->Line 或点击 ，在控制面板在 BOARD GEOMETRY 下选择 OUTLINE，画外框。

用 Allegro 的命令行以绝对尺寸方式输入 X、Y 座标(如: x 1900 1800)或增量座标(如: ix -900)，画出板外形。

2)、如板外形需要倒角，在 Manufacture->Dimension/draft->Chamfer (倒斜角) or Fillet (倒圆角)，在控制面板的 Option 下选项角度或半径，再选择两条相交线进行倒角。

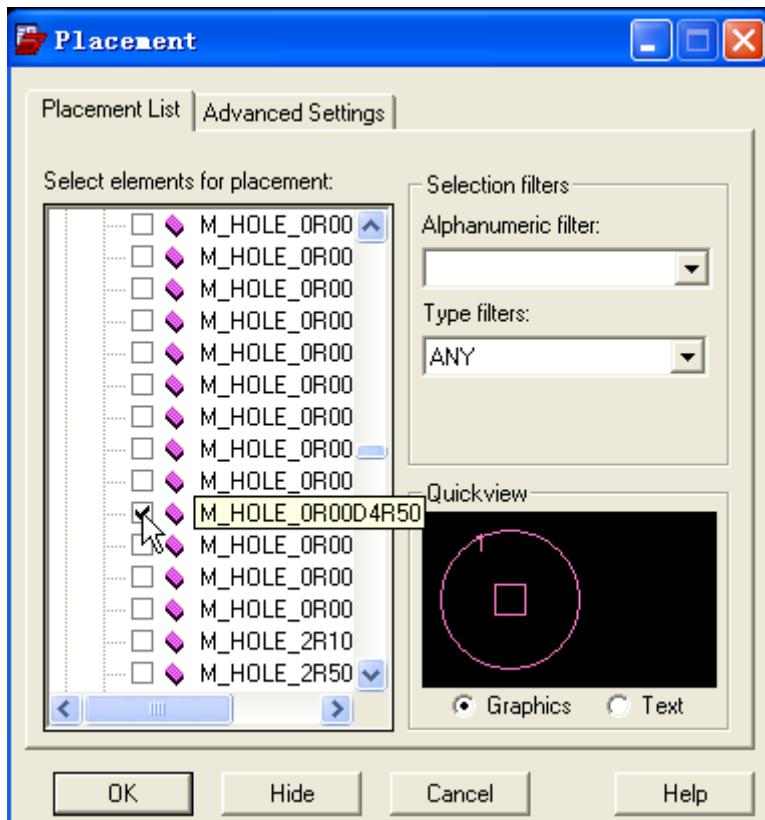

3)、加入安装孔：在 Place->manually 下，选择 Advanced Setting，再选择 Library，这是从封装库中调出所有的元件。然后点击 Placement List，选择合适的孔，放到相应的位置上，如下图所示：

(一些机械符号和格式符号（如光学定位符、EDS 符号等）也在封装库中，同样通过这个方法调出来。)

4、定义板区域：同样用 Setup->Areas 命令定义各种约束区域。

5、标注尺寸：点击  等命令来标注尺寸。

### 5.8.37 7.3.2 设置板图尺寸参数

创建了板外框后，开始进行板图尺寸参数设置：

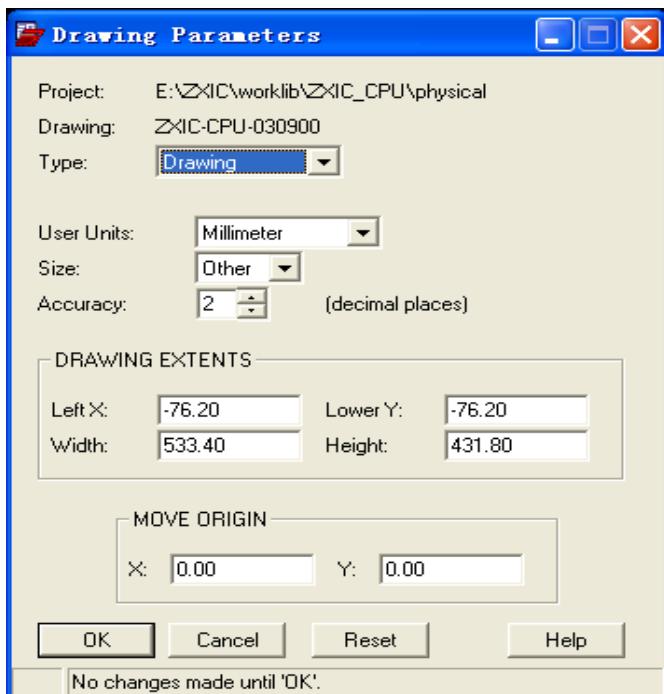

打开 Setup->Drawing Size 界面，设置板图尺寸参数，如原点、单位、精度、板图区域等。如下图：

### 5.8.38 7.3.3 设置版图的栅格值：

打开 Setup->Grid，布局时，栅格设为 100mil、50mil 或 25mi;，布线时，栅格可设为 1mil。

### 5.8.39 7.3.4 设置板图选项

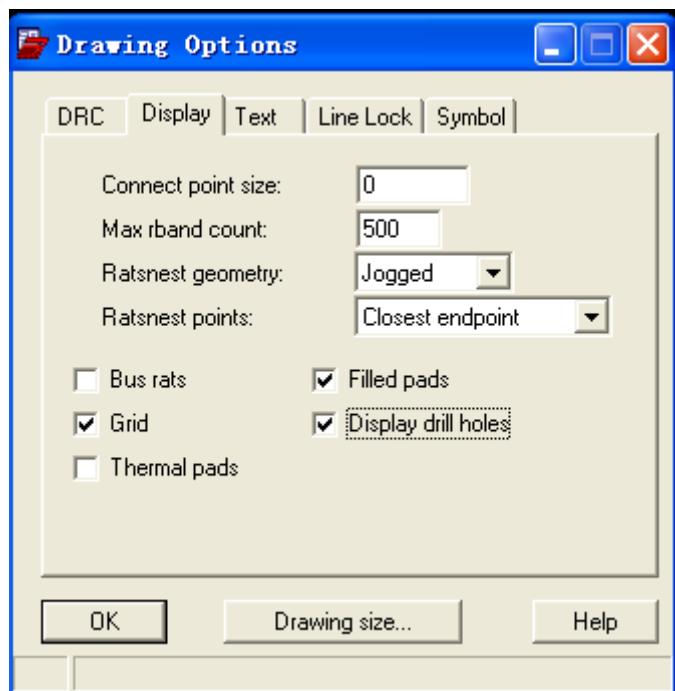

打开 Setup->Drawing，设置一些板图选项，如 DRC 的显示、焊盘的显示选择等：

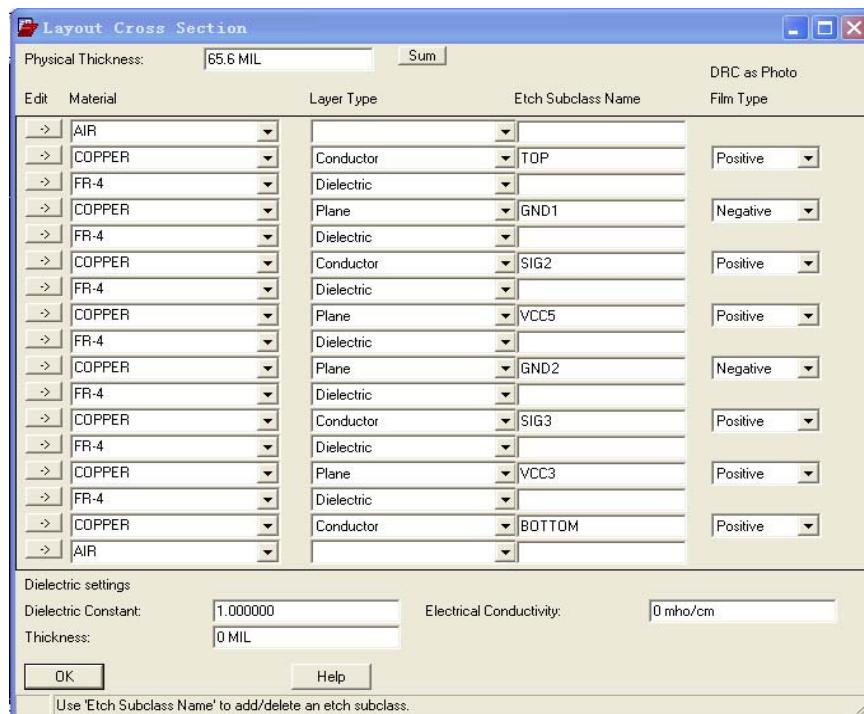

### 5.8.40 7.3.5 设置PCB板的叠层

点击图标或找开 Setup->Cross-section，可设置板叠层，通过界面左边的->按键可增加、删除、显示板层，再通过 Layer Type（板类型）和 Etch Subclass Name（板层名）对板层作相应的选择。

### 5.8.41 7.3.6 设置约束条件

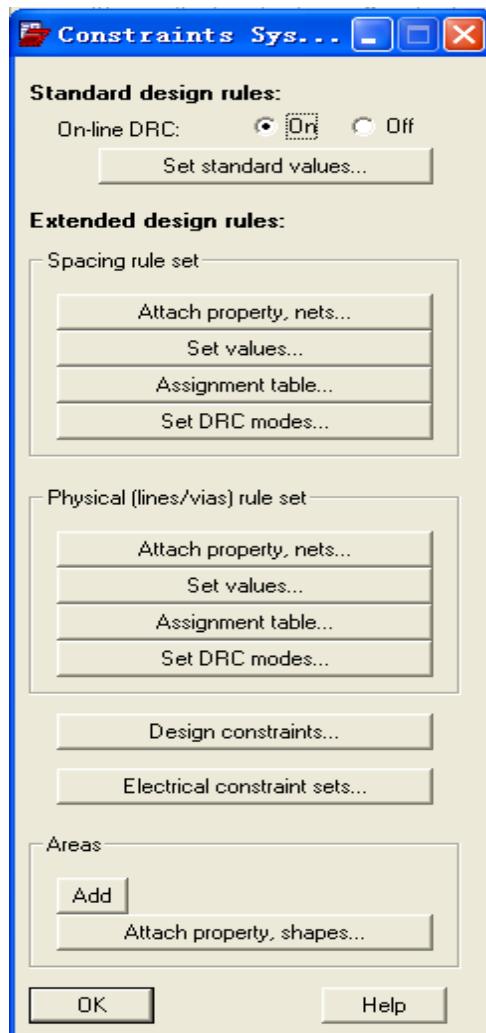

打开 Setup-> Constraints，如下图，设置约束条件：

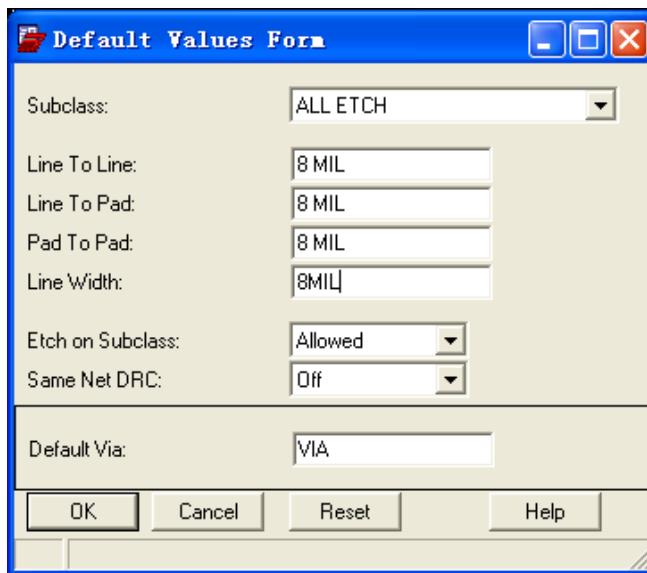

#### 7.3.6.1 设置板的缺省间距：

Set Standards Values... 进入板的缺省间距的设置。当表中显示 xx 时，表示规则集中有不同的值，如下图：

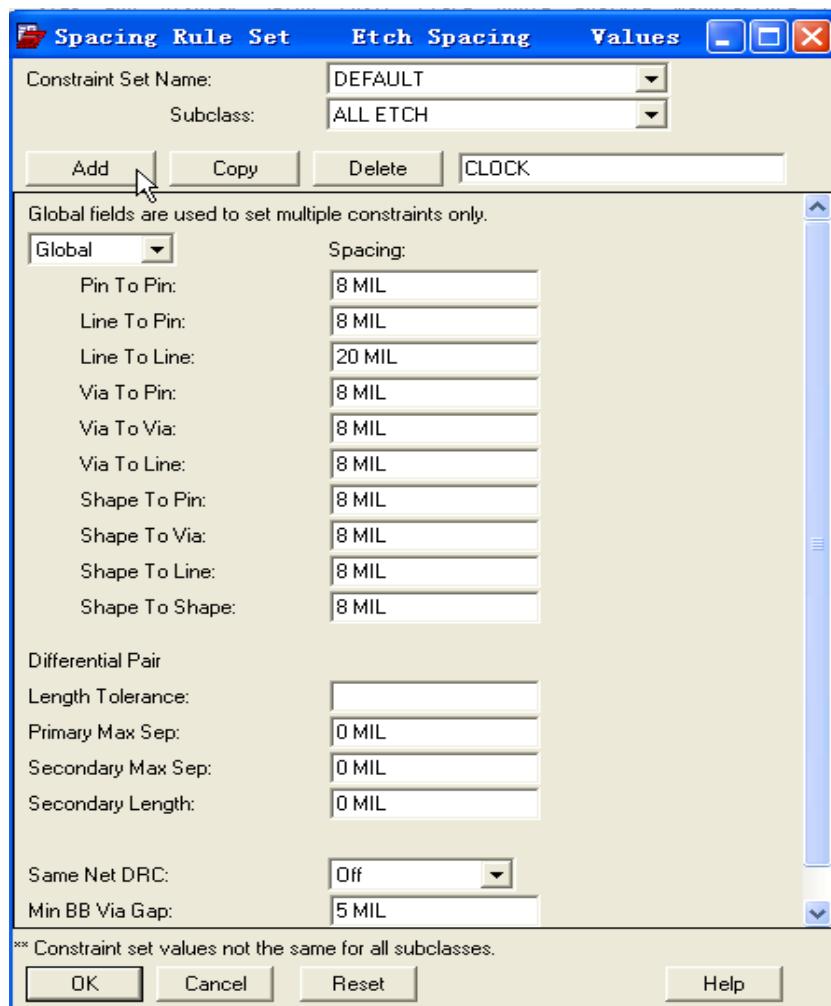

#### 5.8.42 7.3.6.2 设置扩展的距离规则

如果你的设计中某些网络或区域需要特殊的距离规则，就可以选择扩展的距离规则。例如，板上的线间距要求为 5mil，而时钟信号要求与其他信号距离至少为 10mil。扩展的距离规则设置方法与步骤如下：

- 1、设置一个新的约束规则值：打开 Extended desing rules 下的 Set value 进入以下界面，设置新的约束条件，然后 ADD 一个新的约束条件值，如图中将 LINE TO LINE 的值修改以后，ADD 一个新的值：CLOCK。

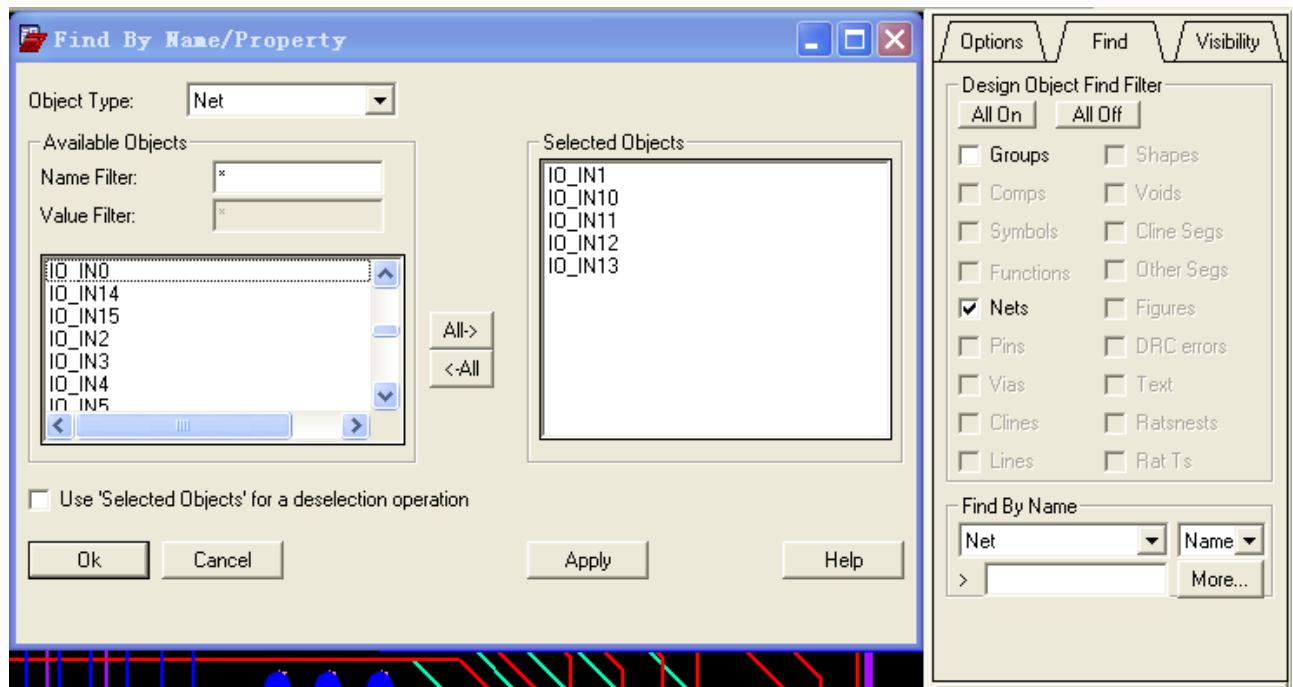

2、打开 Extended desing rules 下的 Attach Property,net..., 在控制面板的 Find 下通过 More 过滤出需要定义约束的网络:

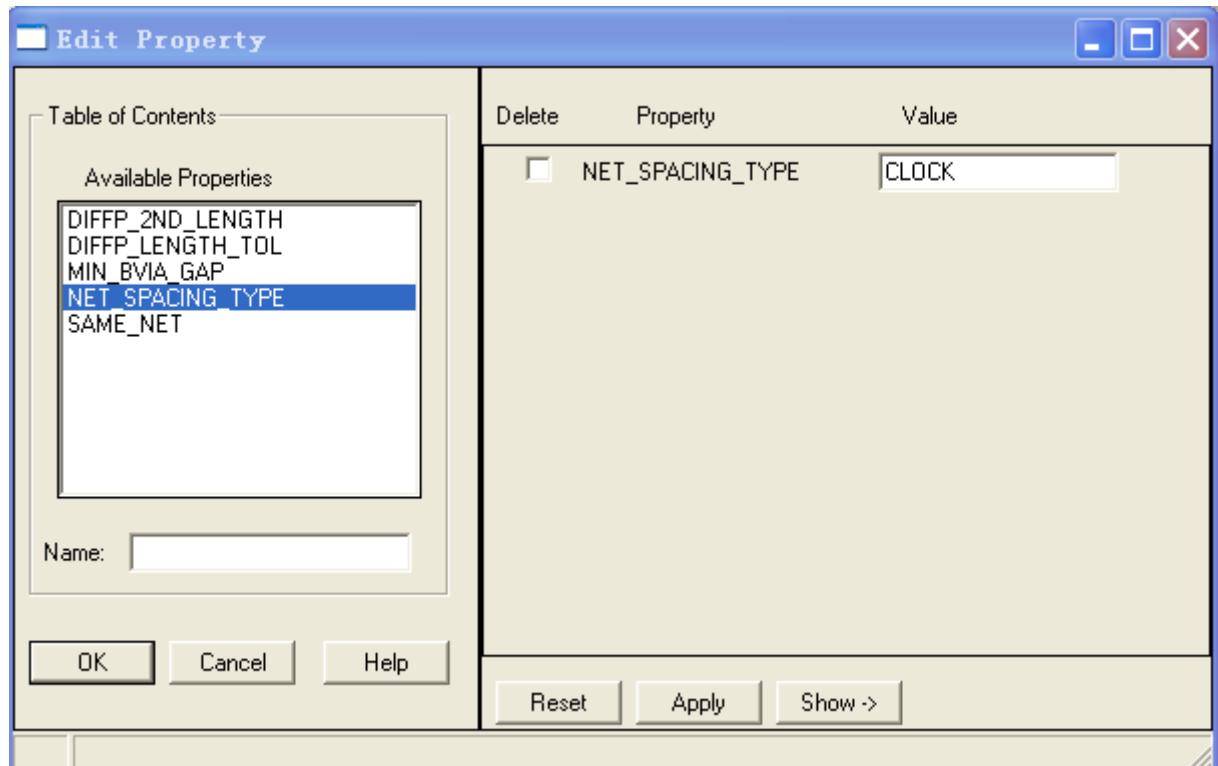

再点击 Apply，进行如下界面：点击 NET\_SPACING\_TYPE，取值 CLOCK。

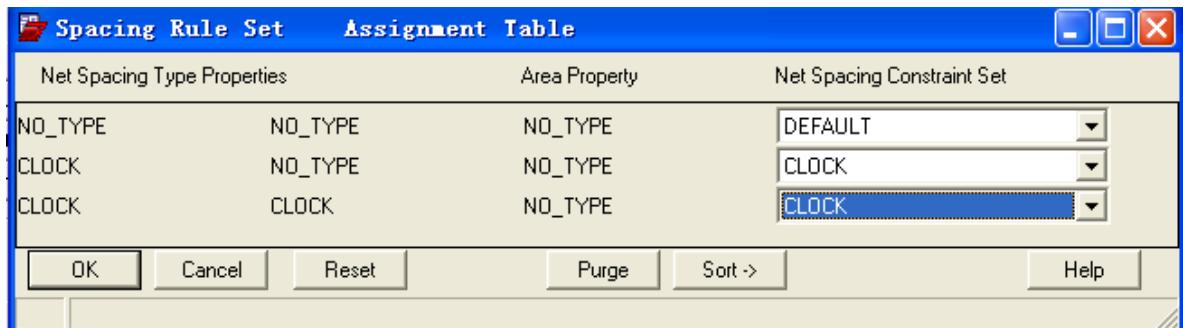

3、打开 Extended desing rules 下的 Assignment table...，进入以下界面，选择每两种之间所遵循的规则。

### 7.3.6.3 设置扩展的物理规则

如果你的设计中某些网络或区域需要特殊的物理规则，就可以选择扩展的物理规则。例如，板上的线宽要求为 8mil，而时钟信号要求至少为 10mil。扩展的物理规则设置方法与扩展的距离规则设置相似。

### 7.3.6.4 编辑属性

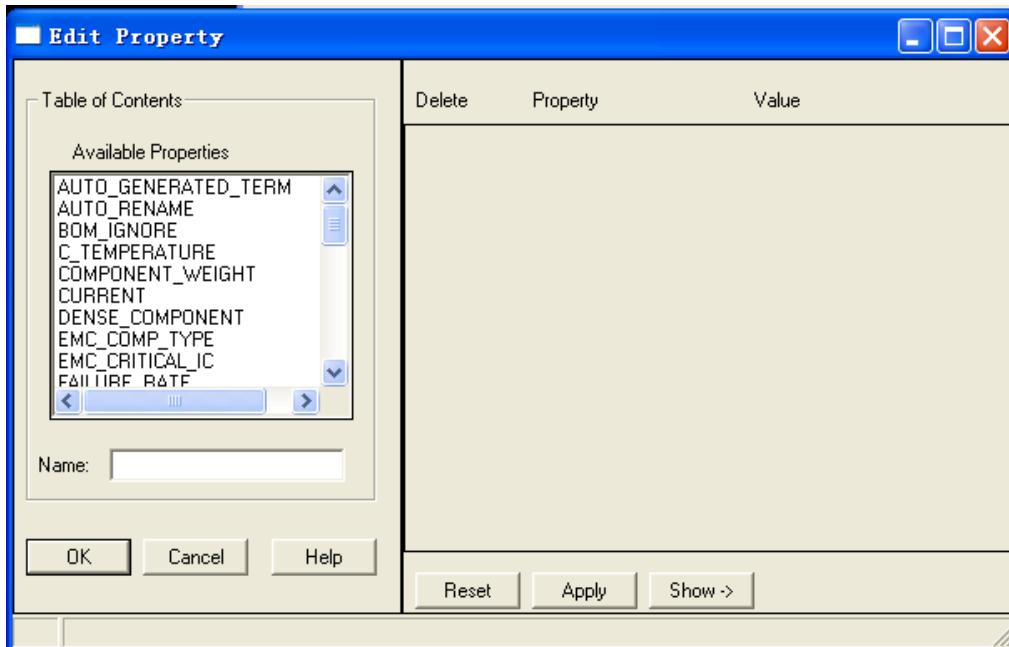

通过编辑属性命令可以对文件和线网定义约束，打开 Edit->Properties，选出你要约束的元素，进入如下界面：

可定义各种属性，如 FIXED 等，通过编辑属性定义的约束具有最高级别，并将替代前面所讲述的各种方法对相同元件和线网定义的同一类约束。

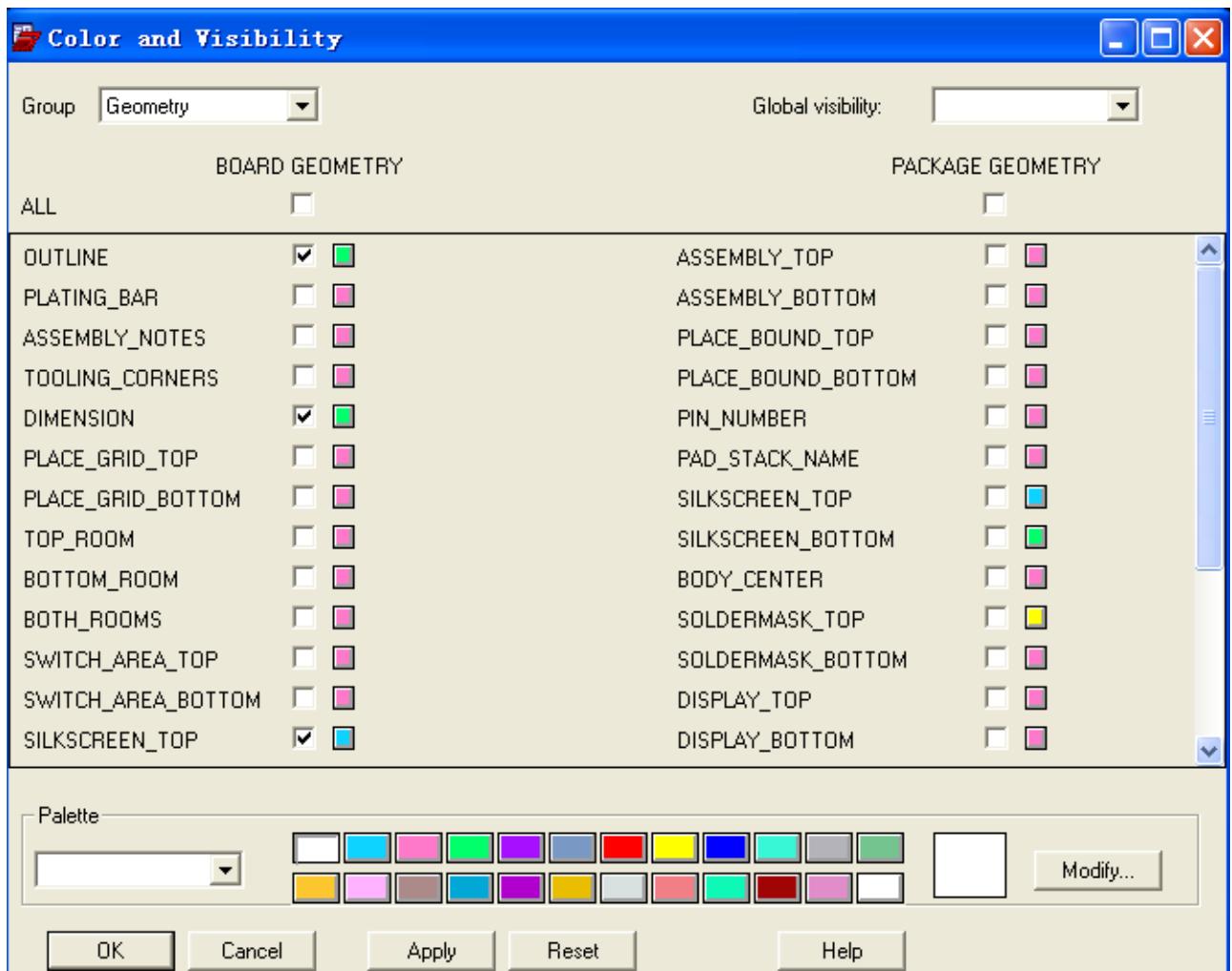

### 5.8.43 7.3.7 可视性和颜色设置

有些类或子类不能通过控制面板来进行可视性设置，可以通过选择 Display->Color/Visibility 或单击来确定所有组在各个类或各子类的可视性和颜色。如下图所示：

## 7.4 PCB布局

通过 Concept-HDL 的 Export physical 已导入网表和封装，设置好规则后，就可以进行布局了。

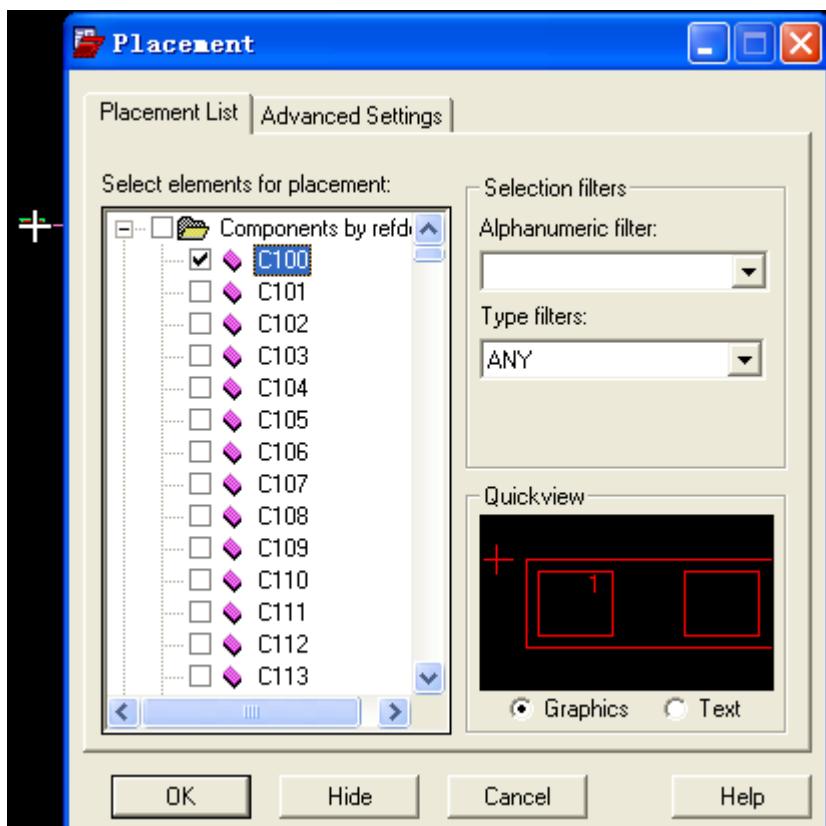

**手工布局：**打开 Place->manually，选择 Components by refdes 下的元件，就可以将此元件放置在 PCB 上。如下图所示：

在 Project Manager 中, 原理图与 PCB 是同步的, 手工布局时也可以利用这一点, 用 Concept-HDL 打开原理图, 同时在 Allegro 中打开 Place->manually, 然后点击原理图的器件, 切换到 Allegro 时, 此元件就被调出。

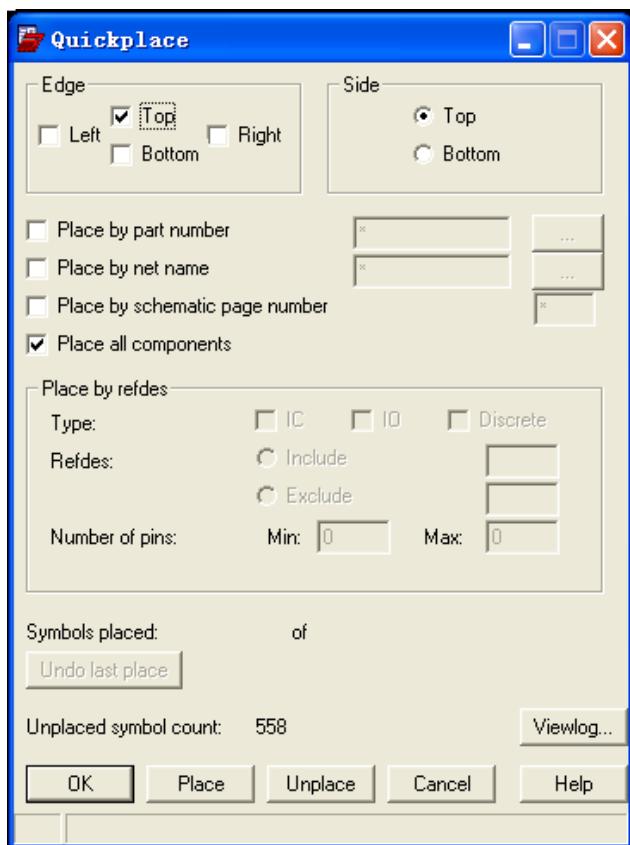

**快速布局:** 打开 Place->Quickplace, 出现下面的界面, 选择布放元件的边缘等, 点击 Place, 所有的元件都会放置在 PCB 上。这样放置后, 元件是堆在一起的, 也可以依照上面的方法, 通过原理图与 PCB 的同步, 将元件按原理图一一移动, 这时在 Allegro 中应打开 Edit->Move。

**自动布局:** 自动布局包括以下步骤:

1、 定义将要自动布局的元件:

选择 Edit->Property，将控制面板的 Find By Name 项选为 Comp(or pin)，点击 More，找到要设置 PLACE\_TAG 属性的元件，然后在 Edit Property 表格中选中 PLACE-TAG，点击 Apply。

2、 定义 ROOM: 选择 Add->Rectangle 或 shape unfilled，将 class/subclass 设置为

BOARD GEOMETRY/TOP\_ROOM ,BOTTOM\_ROOM，然后在板图中产生矩形框，用 Add-text 给 ROOM 添加名称。

3、 定义布局区域: 选择 setup->Area-> package keepin，定义布局区域。

4、 定义自动布局栅格: 选择 Place->Autoplace->Top Grid/Bottom Grid，定义栅格。

5、 调整布局参数表设置: 选择 Place->Autoplace->parameters，调整布局参数表。

6、 定义区域内选项: 选择 Place->Autoplace->insight，定义区域内选项。

7、 选择布局区域并启动布局: 选择 Place->Autoplace->Room，输入需自动布局的 Room 名，前面定义的元件就会自动布放在指定的区域内。

元件布局完成之后，可以调用 Allegro 的自动对换功能单元及管脚工具，进行合理对换，以减小信号长度，提高布通率。这个功能是通过 Place->swap 和 Place-> autoswap 来实现的。

通过 Place->Update symbols 命令可以更新改动过的封装。

## 7.5 PCB布线:

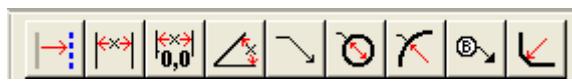

布线主要是用以下的按键完成： 。

Unrats all: 不显示所有飞线

Rats all: 显示所有飞线

Add Connect: 连线

Slide: 推挤

Custom Smooth: 线平滑化

Vertex: 编辑顶点

Auto-route: 自动布线

Specctra: CCT 自动布线

因自动布线还没有得到普及，现在一般还是用手工走线。

1、选择  进入布线方式，**检查选择控制面板中的各项设置是否正确，如层的设置、线宽设置、角度等。** 确定所有设置无误后，将线从起点走到终点。

2、用  对走线进行调整，用  对走线进行 45 度或圆弧化，用  对线的顶点进行编辑。

当要改变线所在的层或宽度，可以通过 Edit->change，在控制面板的 Option 中选择好 class 和 subclass，再点击需要改变的线，就进行了相应的修改。

3、当要删除线时，调用 Edit->Delete 或点击 ，在控制面板的 Option 和 Find 表格的内容同时变化，用这两个选项控制可以删除线的一部份。

## 7.6 添加过孔和替换过孔

### 5.8.44 7.6.1 添加过孔

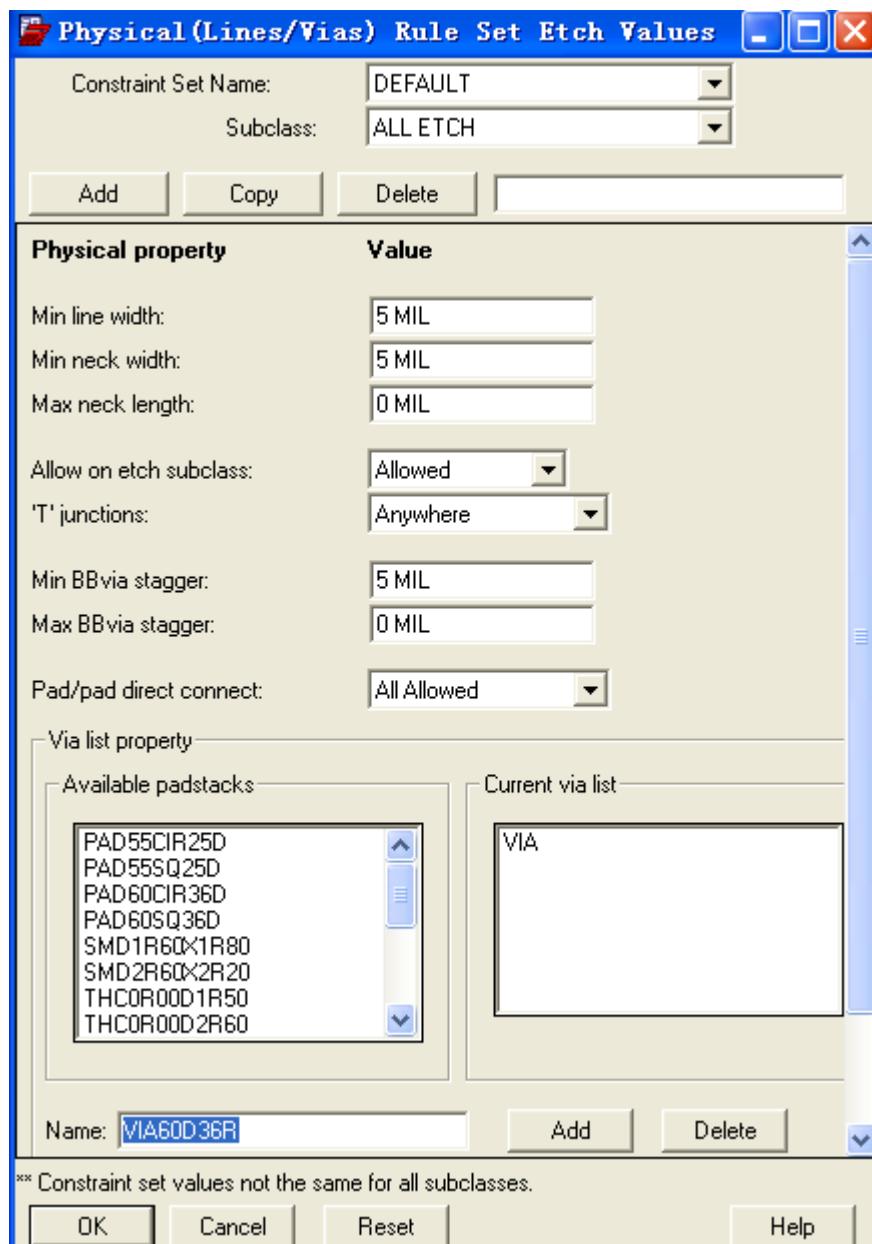

打开 Setup->constraints->physical rule sets->set rules 界面，如下图：在 Available padstacks 下输入一过孔名（必须是焊盘库中有的过孔名），点击 ADD。

走线换层时，双击鼠标左键，Allegro 自动添加过孔。或者走线时，点击鼠标右键，从弹出菜单中选择 Add Via，也可以添加过孔；如在 Setup->constraints->physical rule sets->set rules 界面里加入多种过孔，换层时在控制面板中需要选择相应的过孔。

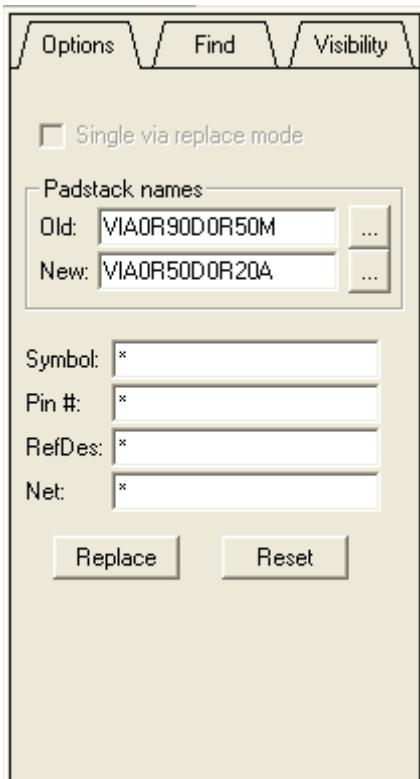

#### 5.8.45 7.6.2 替换过孔

当需要替换过孔时，打开 Tools->Padstack->Replace，控制面板如下图：

将以前的过孔和想要替换的过孔选出，点击 Replace 即可。

## 7.7 优化走线

当布线完成时，调用 Route->Gloss->Parameters 可优化走线，选择需要选化线的项目，点击 Gloss 就执行了此次功能，优化功能包括：

Line and via cleanup：清理线和过孔

Via Eliminate：消除过孔

Line Smoothing：线平滑

Center Lines Between Pads：线居中

Line Fattening：线加粗

Converting Corner to Arc：将拐角转换为弧

Pad and T Connection Fillet：将焊盘和 T 形接头进行泪滴处理

Dielectric Generation：绝缘层产生，用于 MCM 设计

在启动 Gloss 之前，如果有些线需要保护，不让优化布线工具进行处理，则需对该类线网添加两个属性：

\*No\_Gloss：不让 Gloss 工具处理

\*FIXED：不让所有自动布线工具处理

如果要定义一个区域进行保护，则用 Add->shape 或 Add-> Rectangle 命令，将 class/subclass 设置为 MANUFACTURING/NOGLOSS\_ALL，在板图上画出一个保护区域。

## 7.8 覆铜处理

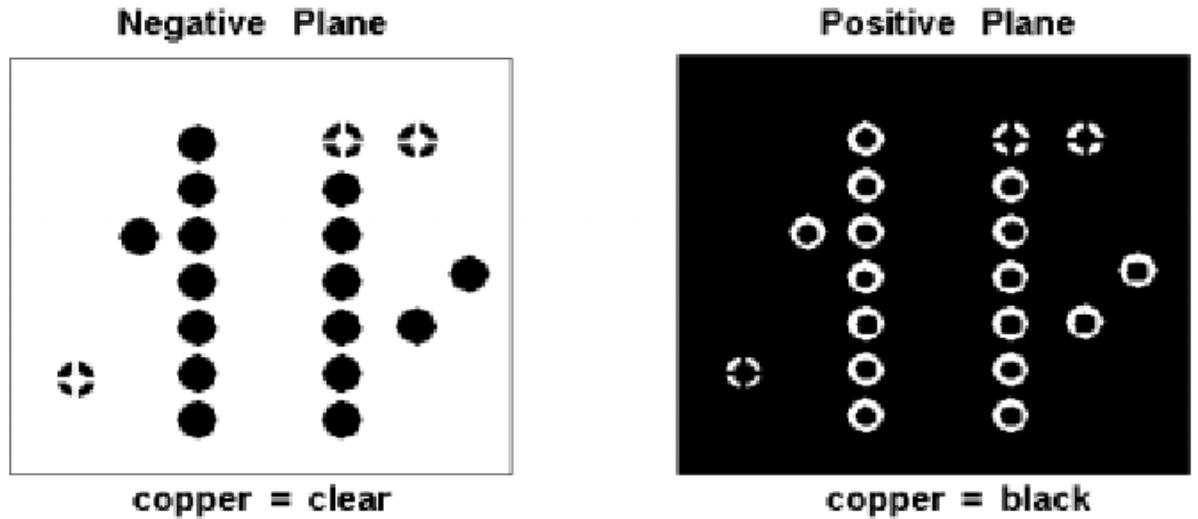

Allegro 的覆铜可分为“阳版”覆铜和“阴版”覆铜，二者各有特点：

阴版覆铜：生成的光绘数据量小，能自适应动态的布局、布线修改；但不直观。

阳版覆铜：直观；但生成的光绘数据量大，不能自适应动态的布局、布线修改。

在板叠层的设置中，就已经定义了电源与地是用阳版还是阴版。

### 5.8.46 7.8.1 阴版覆铜

1、用 Add Shape 命令在需要覆铜的区域添加一个封闭的 shape 区域（此区域可以选择三种方式：solid Fill、unFilled、Cross Hatch Fill），添加区域时，需检查控制面板的 Option 栏中 class/subclass 的设置是否是正确；Shape 区域必须处于布线区内。区域闭合后，点击右键，从弹出菜单中选择 Done，自动切换为编辑 shape 菜单。

2、用 **Edit->Change net** 命令给区域指定一个线网名，如 VCC，GND，+5V 等。

3、用 **Shape->Fill** 命令填充铜皮区域。

当填充完成后，Allegro 又回到主命令菜单。

#### **5.8.47 7.8.2 阳版覆铜**

生成阳版覆铜前两步与最后一步操作与生成阴版覆铜完全相同，不同的是，阳版覆铜需要你选择 Shape 的填充方式及避让处理，这些都是由 Shape 的参数表来控制。阳版覆铜的步骤分为五步：

- 1、 **Add->Shape->Solid Fill**：画出要覆铜的区域。

- 2、 **Edit->Change Net(name)**：为覆铜区选择一个网络名。

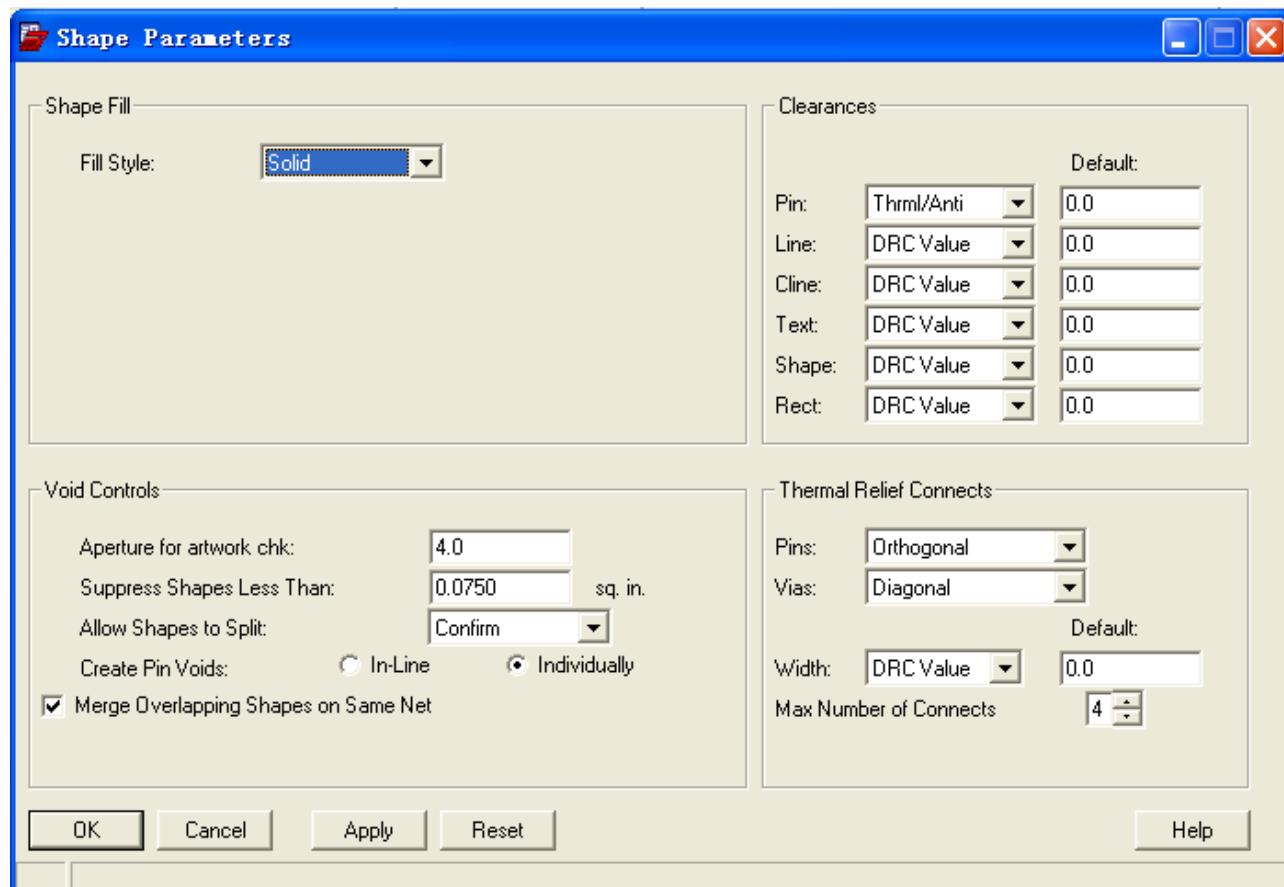

- 3、 **Shape->Parameters**：选择填充方式，调出参数表如下图：

Shape Fill: 选择填充方式

Clearances: 选择避让间距

Void Controls: 各种避让控制

Thermal Rellef Connects: 定义热漂移焊盘连接到铜皮的方式

4、 Void->Auto: 选择避让方式

5、 Shape->Fill: 覆铜

在添加了覆铜区域后，还可以对它进行编辑，如修改边界、在阳版上做特殊避让等。用 Edit->Shape，点击左键选择覆铜区域，再按右键选择 Done，就进入了 Shape 的编辑区域，如 2.7.1 的图示界面。

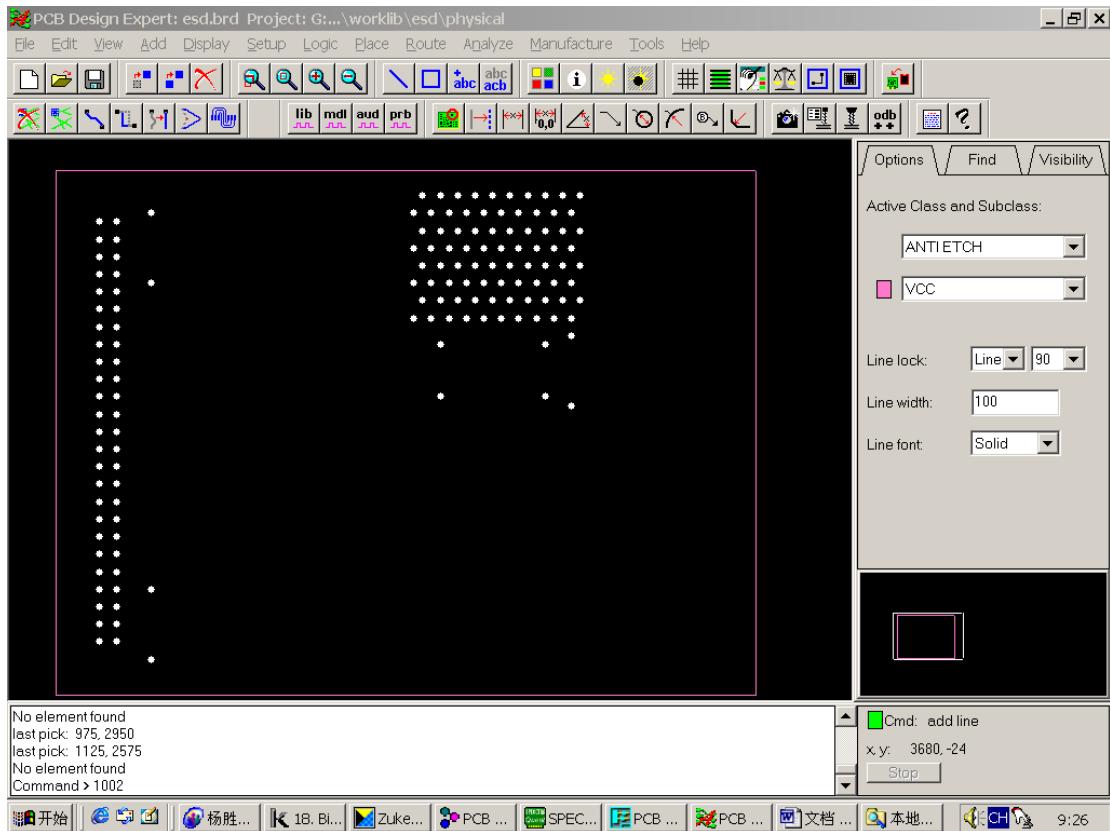

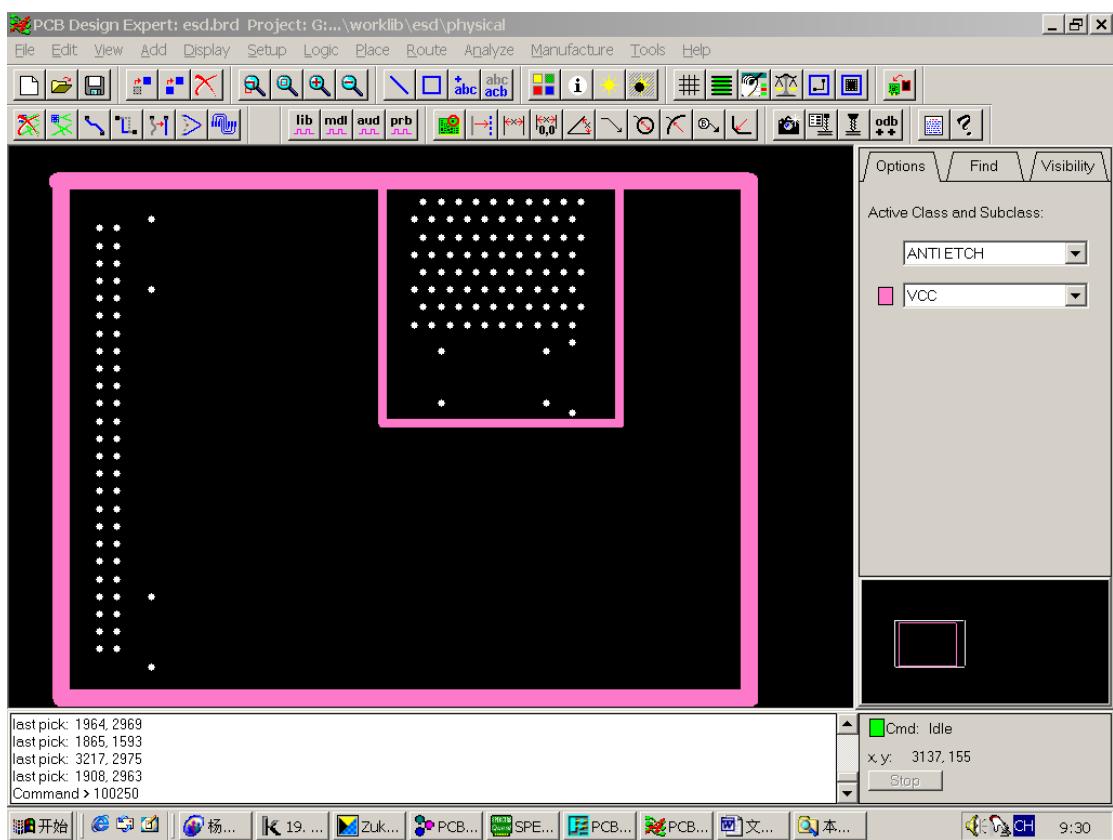

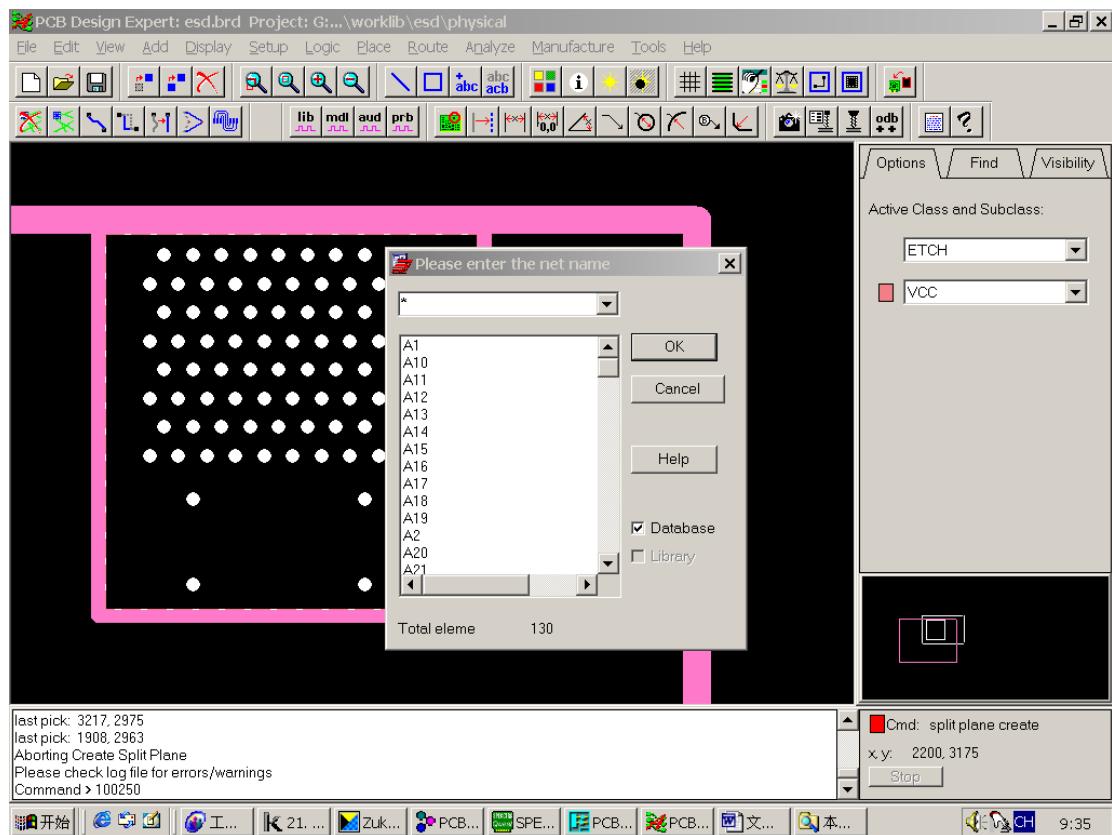

### 5.8.48 7.9 分割电源平面

有时一个电源层上分配有几个电压，必须对其进行分割。在分割电源面之前，需要先定义好布线区，用 Setup->Areas->Route keeping 来定义，然后再进行电源面的分割：

1、选 Add->Line 命令，控制面板的 class /subclass，选 ANTI ETCH 及要分割的层：

2、用适当的线宽将电源面分割成想要的区域如图：

3、将 class/subclass 改为 ETCH /VCC，选 Edit->Split plane->Create 如图：

执行该命令后，会依次提示为该区域选择所需网络，分割完成后如图：

### 5.8.49 7.10 位号标注

元件位号在 SILKSCREEN\_TOP/BOTTOM 层显示，通过可视性和颜色设置栏可以进行可视性和颜色进行控制，通过 Edit 下的命令对位号可以进行移动、删除等操作，通过 Edit->Change 可以对其进行编辑，编辑时注意控制面板中需选择相应的类、子类和 Text block。

## 7.11 加测试点

通过 Route->Testprep->Auto 命令，可以自动加在线测试点。

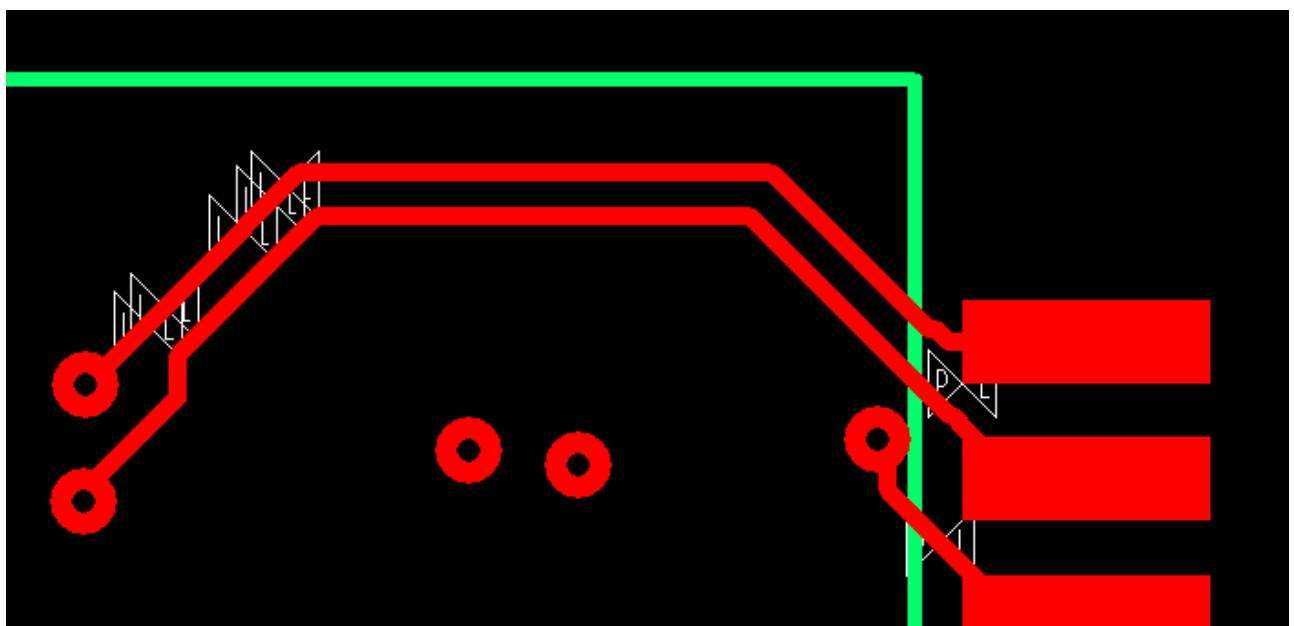

## 7.12 DRC检查

当设置了详细的规则后，用 Setup->Constraints->Set DRC modes 打开 DRC 在线检查，当某处违反了规则，就会出现 DRC 符号：如下所示：

我们可以通过  来查询具体的 DRC 的表示，然后对其进行修正，当错误修正后，DRC 符号自动消失。

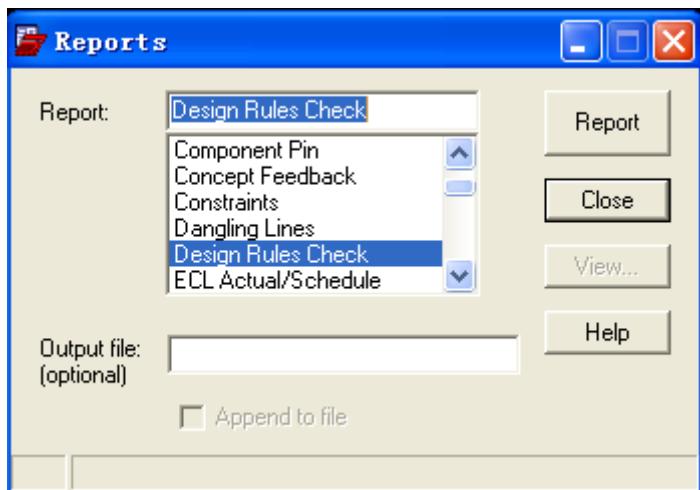

## 7.13 生成报告文件

Allegro 的文档工具能生成各种报告文件，例如：元器件清单、布通率、DRC、无连接管脚、没布局元件等。用 Tools->Reports，然后调出以下界面：

选择需要输出的报告，点击 Report，就可以生成报告文件。常用的选择有“Design Rules Check”(DRC)、

“Unconnected Pins”（未连管脚）等等，PCB 完成后，DRC 报告结果应该为 0。

## 7.14 VALOR 检查

当布局完成和 PCB 设计完成后，应该进行 VALOR 自动检查，VALOR 是一种进行 PCB 工艺检查的软件，可以有效地检查出元件封装错误等不满足 PCB 可加工性和可制造性方面的错误。

## 7.15 生成光绘文件和钻孔文件

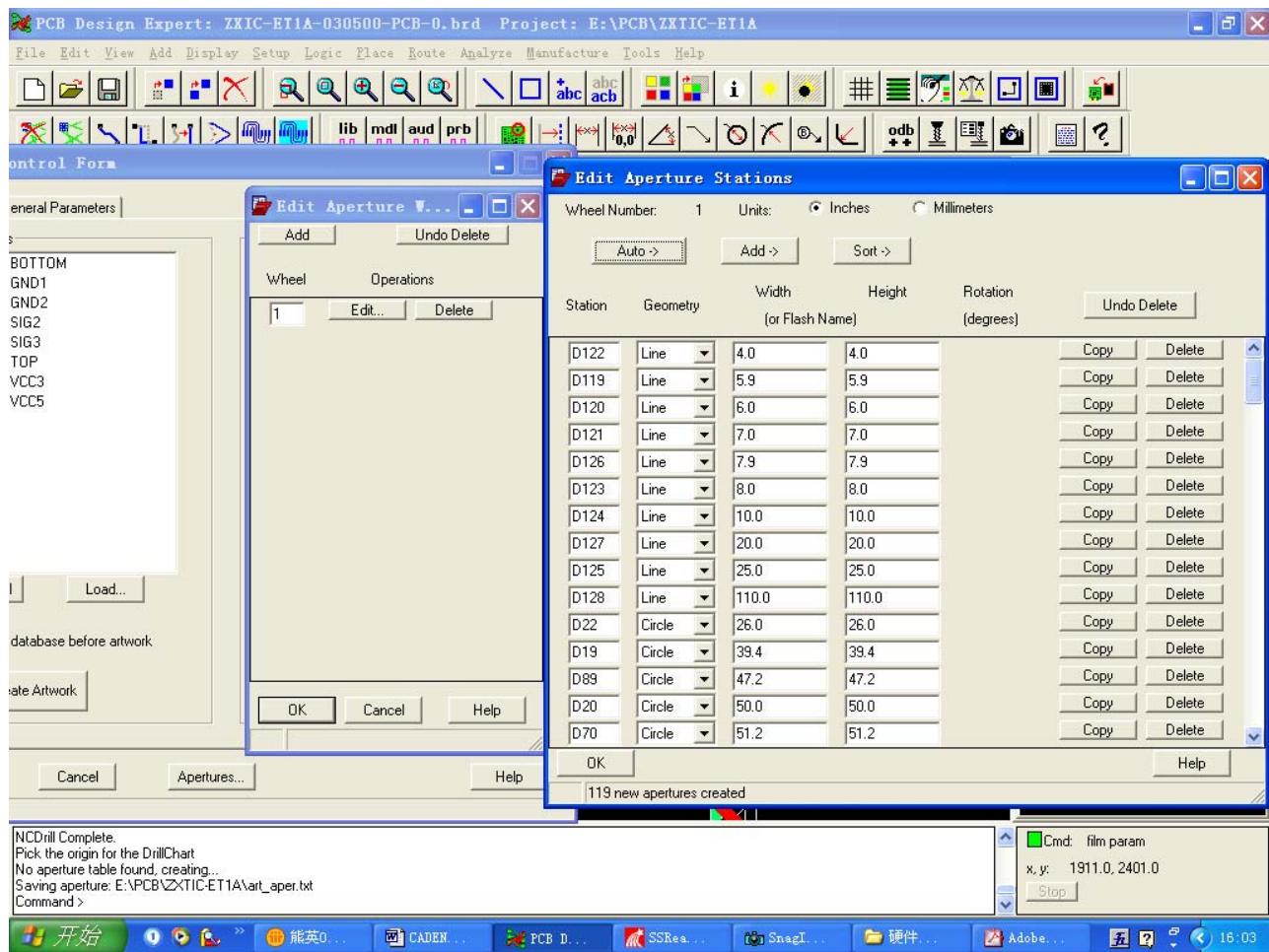

### 5.8.50 7.15.1 生成光圈文件 (art-aper.txt)，即 D 码表

选择 Manufacturing->Artwork->Apertures 命令，点击 Edit，再选择 Auto 下 Without Rotation 或 With Rotation，调出 D 码表格如下图，点击 OK 则生成了 D 码表。

### 5.8.51 7.15.2 生成钻孔文件

- 1、调用 Manufacture->NC->Drill Legend，生成钻孔图，将其与技术要求放在一起。

- 2、调用 Manufacture->NC->Drill Tape，启动数控钻程序，自动生成 NC 钻孔文件（ncdrill1.tap）和日志文件（nctap.log）。NC 钻孔文件包括板图中每种尺寸过孔的座标值，日志文件记录了所使用参数及孔的尺寸及数量、警告及错误信息。

### 5.8.52 7.15.3 生成光绘文件

#### 7.15.3.1 在Artwork中加入所需的层

举例讲述如何在光绘文件中加入 SILK-TOP 层：

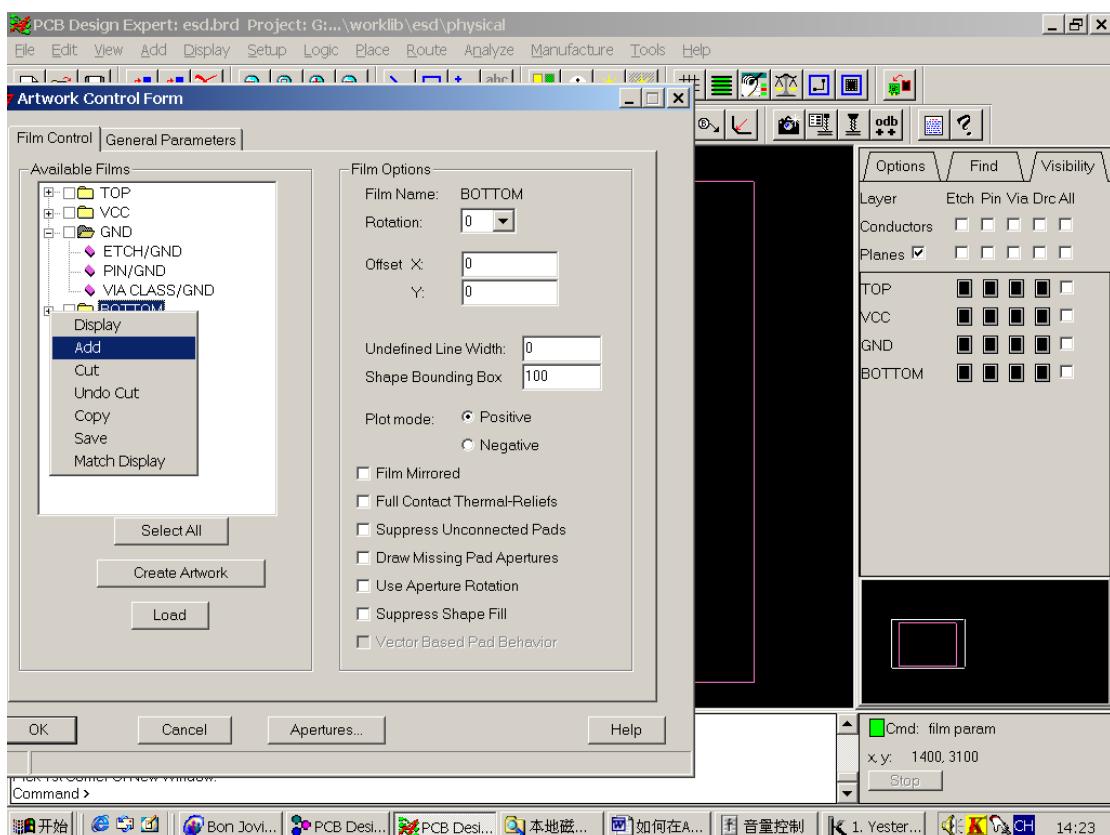

- 1、在 Allgero 中,选取 Manufacture->Artwork，将光标移到展开窗口右边的”+”号,按右键,如图:

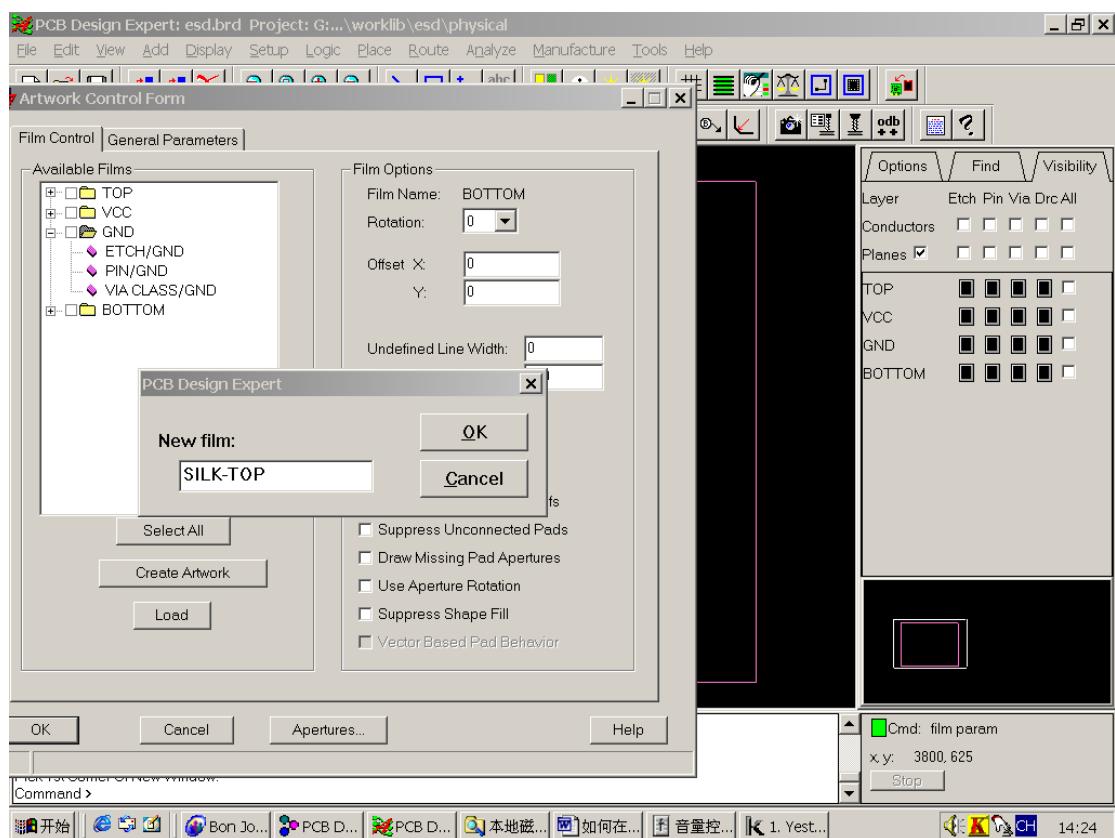

- 2、选 Add 命令，输入新的 Film 名，如图：

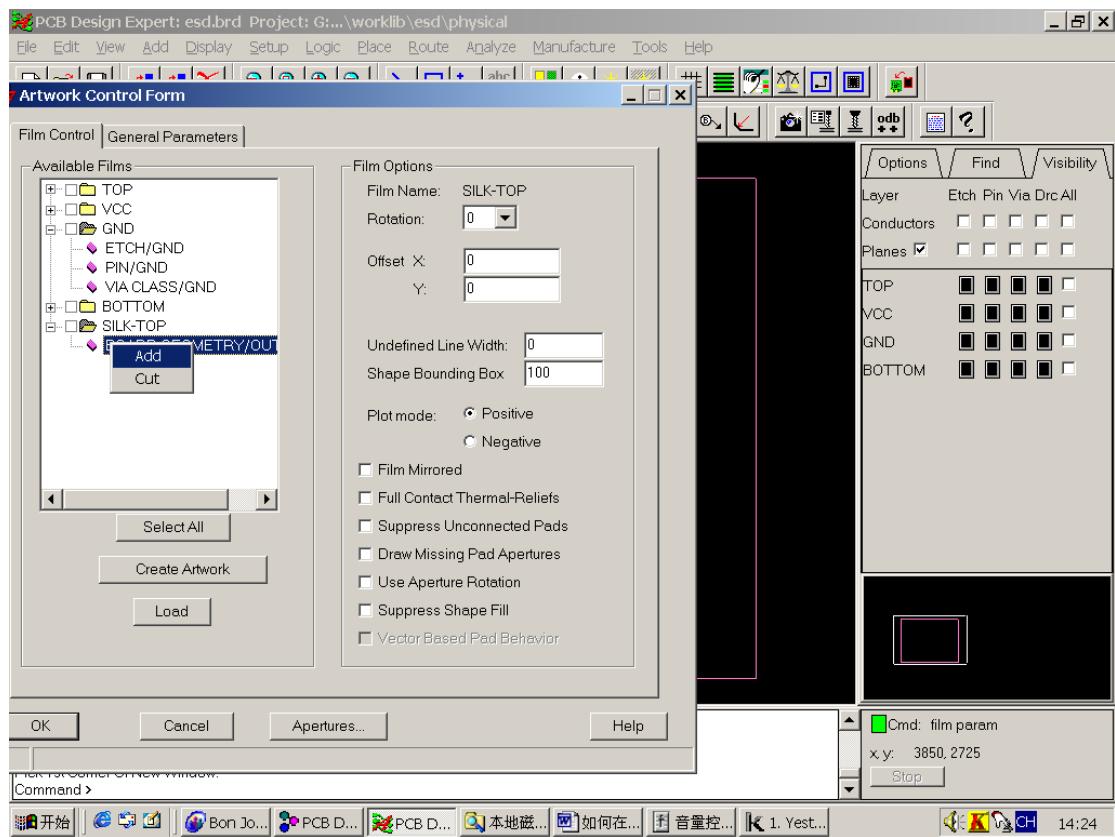

3、在 SILK-TOP 层下面，点右键，选 Add 命令，如图：

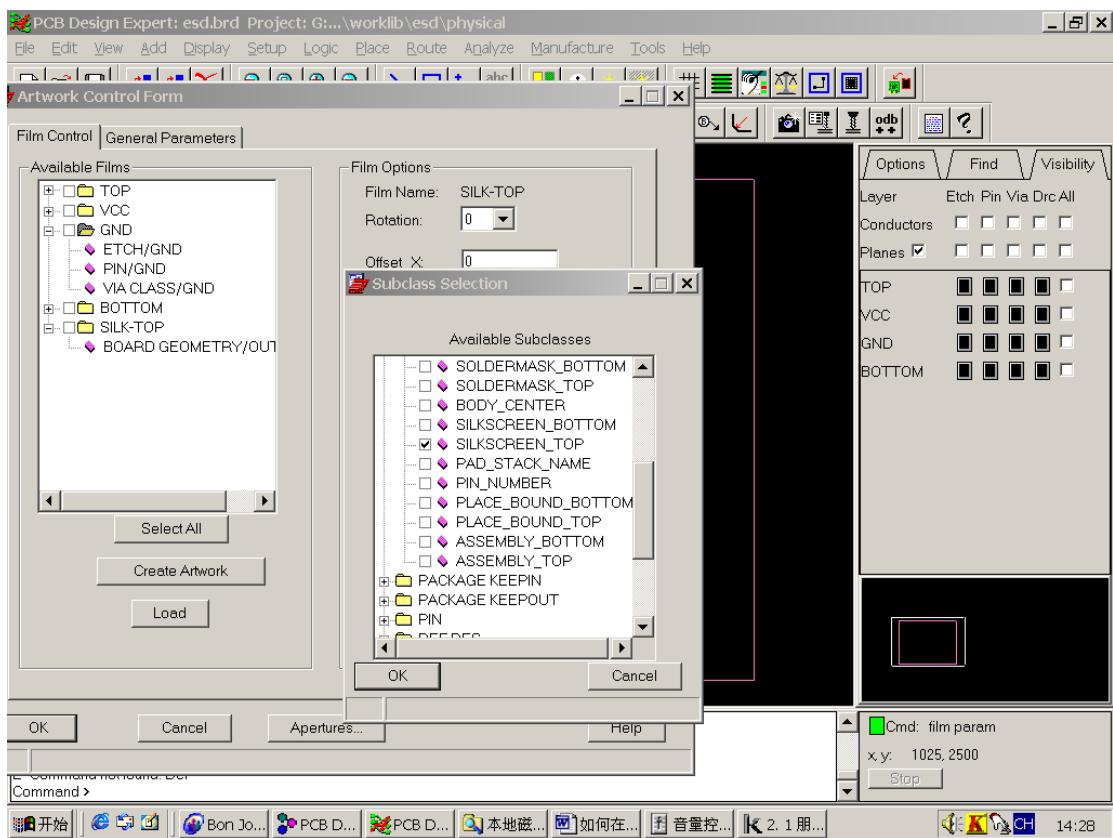

从展开的窗口中选所需的 SUBCLASS 如图：

依次加入所需的层，将光标移到 SILK-TOP 右边”+”处，点右键选 Display 命令，则所加的层显示在屏幕上，如图：

### 7.15.3.2 生成光绘文件

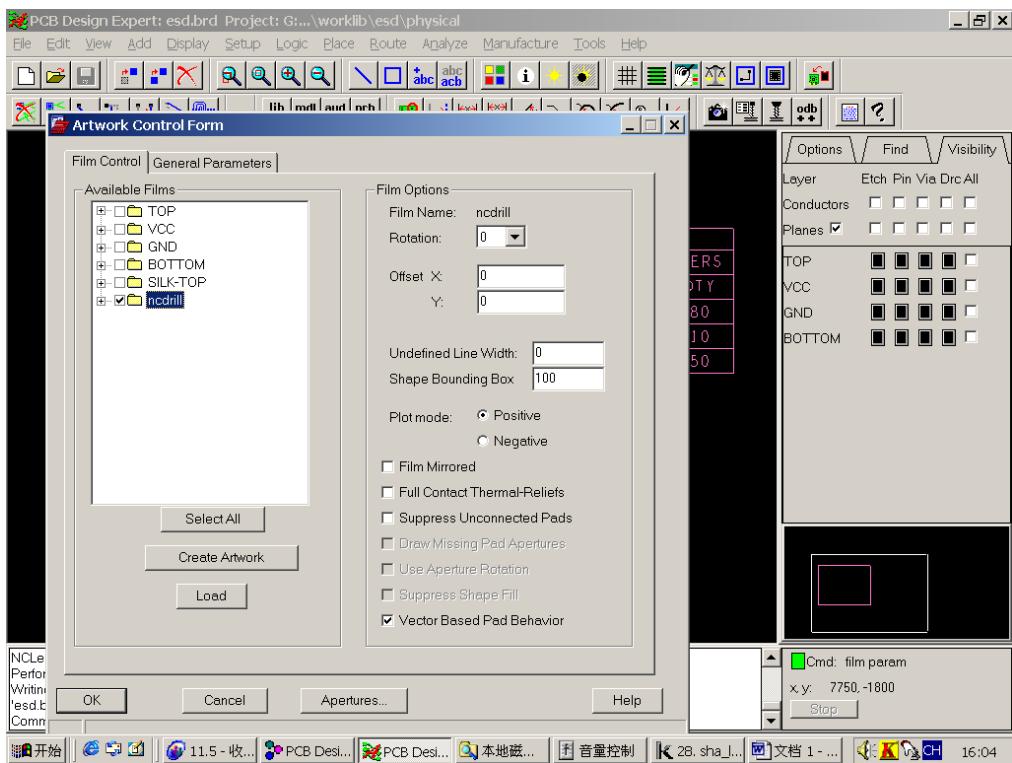

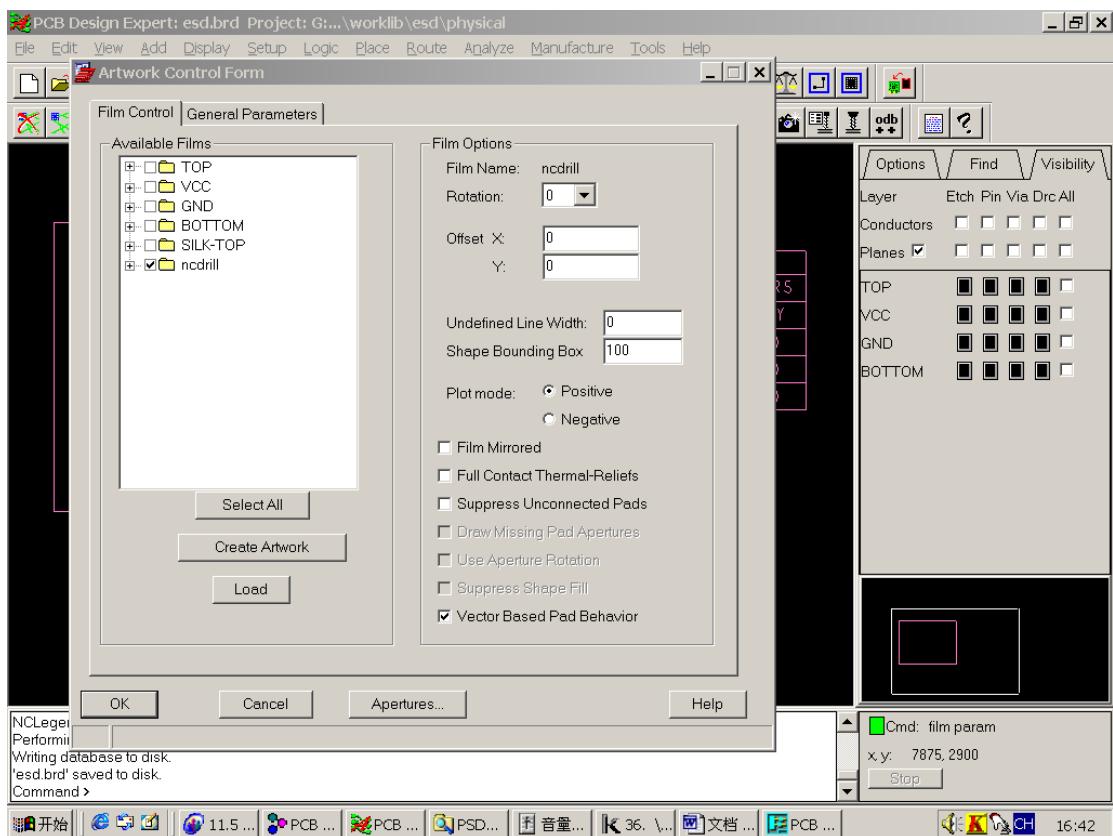

以 NCDRILL 为例：

1、选取 Manufacture->Artwork 命令, 选中 Ncdrill, Plot mode 设为 Positive(如为负片, 则选 Negative);

undefined Width 设为一指定值, 如图:

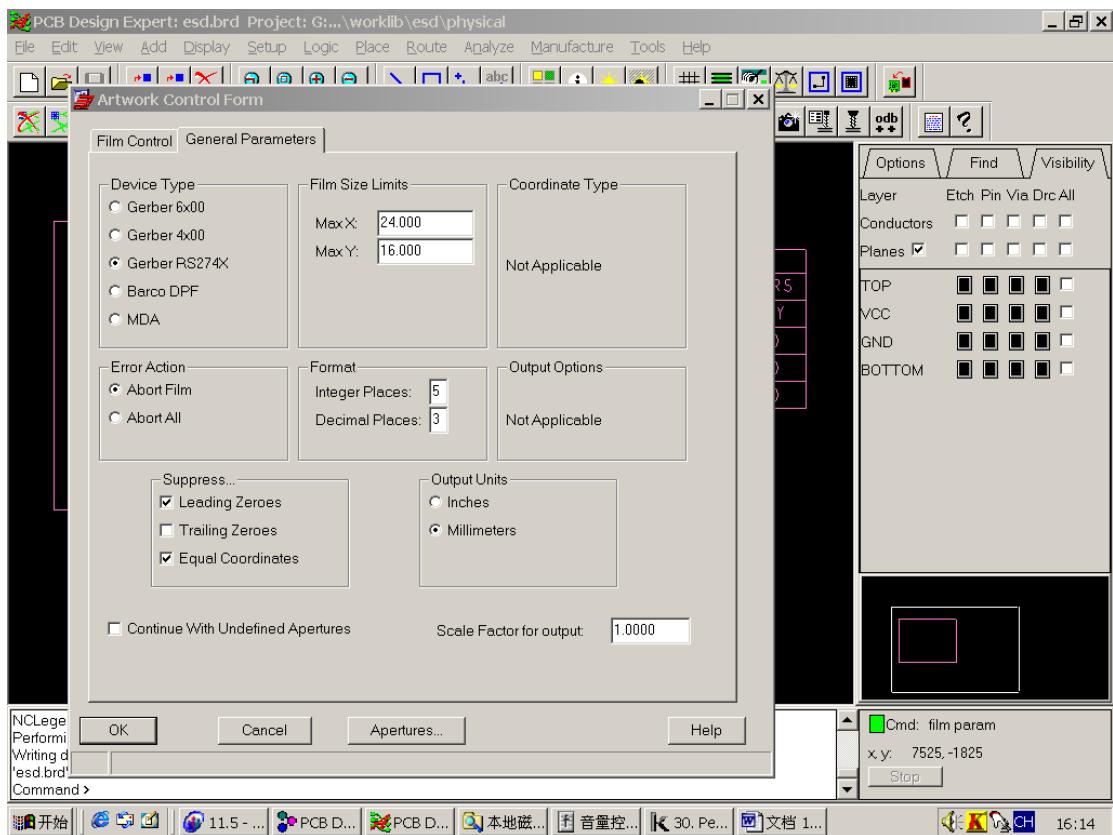

2、进入 Geneneral Parameters，将 Device Type 选为 Gerber RS274X(如所有的通孔都有 Flash，则可选第一种设备)，输出单位选为 mm。其他默认,如图：

2、再回到 Film Control，点击 Create Artwork，则 ncdrlil 光绘完成。（文件存于 Physical 目录下，后缀.art）：

库，10.61.24.22

其它层的光绘也是同样生成。

## 7.16 PCB评审

在 PCB 设计完成后，应提交给项目负责人、可靠性工程师和工艺工程师进行评审。每个事业部都有自己的具体的评审流程。

## 第八章 公司的PCB设计规范

上面是 Cadence 的原理图与 PCB 的设计说明，这只是一种设计工具。要成功地设计一块 PCB，需要熟悉公司许多的设计规范，这些规范在公司标准中都可以找到：

- 1、 Q/ZX 04.100.1-2003 印制电路板设计规范-----文档要求

- 2、 Q/ZX 04.100.2-2002 印制电路板设计规范-----工艺性要求

- 3、 Q/ZX 04.100.3-2003 印制电路板设计规范-----生产可测性要求

- 4、 Q/ZX 04.105-2002 基于 CADENCE 平台的 PCB 板级仿真流程

- 5、 Q/ZX 04.100.4-2001 印制电路板设计规范-----元器件封装库基本要求

- 6、 Q/ZX 04.100.6-2002 印制电路板设计规范——插件及连接器封装库尺寸要求（试行）

- 7、 Q/ZX 04.100.8 - 2002 印制电路板设计规范——PCB Check List

- 8、 Q/ZX 04.100.9-2003 印制电路板设计规范——版本和标识

- 9、 Q/ZX 04.100.10-2003 印制电路板设计规范——插板结构设计要求

- 10、 Q/ZX 04.104.1-2002 电路原理图设计规范——CADENCE元器件原理图库建库要求

- 11、 Q/ZX 04.104.2-2002 电路原理图设计规范——基于CADENCE平台的设计要求

- 12、 Q/ZX 04.106-2003 单板面板指示灯设计要求