## 特性

集成12位DAC和ADC的RF 2x2收发器

频段: 70 MHz至6.0 GHz

支持TDD和FDD

可调谐通道带宽: <200 kHz至56 MHz

双通道接收器: 6路差分或12路单端输入

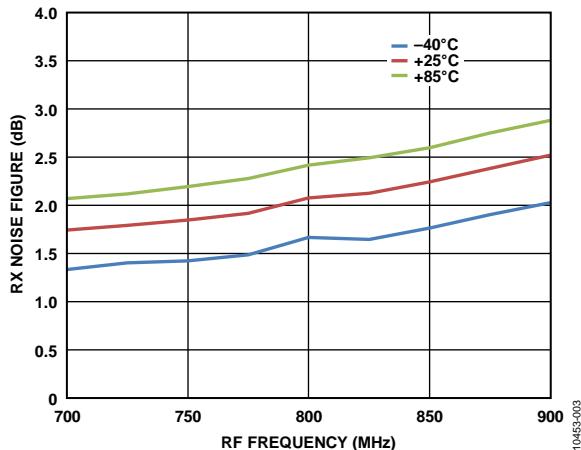

出色的接收器灵敏度, 噪声系数为2 dB(800 MHz, 本振(LO))

RX增益控制

实时监控和控制信号用于手动增益

独立的自动增益控制

双发射器: 4路差分输出

高线性度宽带发射器

TX EVM: ≤ -40 dB

TX噪声: ≤-157 dBm/Hz本底噪声

TX监控器: 动态范围≥66 dB, 精度=1 dB

集成小数N分频频率合成器

最大LO步长: 2.4 Hz

多器件同步

CMOS/LVDS数字接口

## 应用

点对点通信系统

毫微微蜂窝/微微蜂窝/微蜂窝基站

通用无线电系统

## 概述

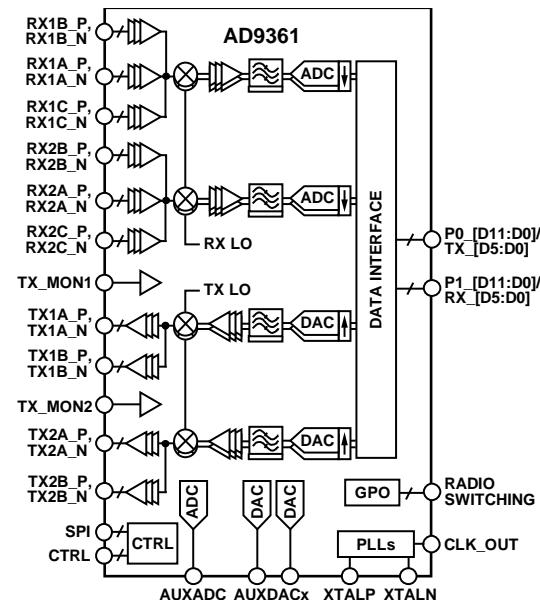

**AD9361**是一款面向3G和4G基站应用的高性能、高集成度的射频(RF)Agile Transceiver™捷变收发器。该器件的可编程性和宽带能力使其成为多种收发器应用的理想选择。该器件集RF前端与灵活的混合信号基带部分为一体，集成频率合成器，为处理器提供可配置数字接口，从而简化设计导入。**AD9361**工作频率范围为70 MHz至6.0 GHz，涵盖大部分特许执照和免执照频段，支持的通道带宽范围为不到200 kHz至56 MHz。

两个独立的直接变频接收器拥有首屈一指的噪声系数和线性度。每个接收(RX)子系统都拥有独立的自动增益控制(AGC)、直流失调校正、正交校正和数字滤波功能，从而消除了在数字基带中提供这些功能的必要性。**AD9361**还拥有灵活的手动增益模式，支持外部控制。每个通道搭载两个高动态范围ADC，先将收到的I信号和Q信号进行数字化处理，然后将其传过可配置抽取滤波器和128抽头有限脉冲响应(FIR)滤波器，结果以相应的采样率生成12位输出信号。

### Rev. D

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Trademarks and registered trademarks are the property of their respective owners.

### Document Feedback

## 功能框图

NOTES

1. SPI, CTRL, P0\_[D11:D0]/TX\_[D5:D0], P1\_[D11:D0]/RX\_[D5:D0],

AND RADIO SWITCHING CONTAIN MULTIPLE PINS.

10453-001

图1.

发射器采用直接变频架构，可实现较高的调制精度和超低的噪声。这种发射器设计带来了行业最佳的TX EVM，数值不到<-40 dB，可为外部功率放大器的选择留出可观的系统裕量。板载发射(TX)功率监控器可以用作功率检测器，从而实现高度精确的TX功率测量。

完全集成的锁相环(PLL)可针对所有接收和发射通道提供低功耗的小数N分频频率合成。设计中集成了频分双工(FDD)系统需要的通道隔离。还集成了所有VCO和环路滤波器器件。

**AD9361**的心核可以直接用1.3 V稳压器供电。IC通过一个标准四线式串行端口和四个实时I/O控制引脚进行控制。全面的省电模式可将正常使用情况下的功耗降至最低。

**AD9361**采用10 mm × 10 mm、144引脚芯片级球栅阵列封装(CSP\_BGA)。

## 目录

|                                             |    |                         |    |

|---------------------------------------------|----|-------------------------|----|

| 特性.....                                     | 1  | 工作原理.....               | 33 |

| 应用.....                                     | 1  | 一般特性.....               | 33 |

| 功能框图.....                                   | 1  | 接收器.....                | 33 |

| 概述.....                                     | 1  | 发射器.....                | 33 |

| 修订历史.....                                   | 2  | 时钟输入选项.....             | 33 |

| 技术规格.....                                   | 3  | 频率合成器.....              | 34 |

| 功耗—VDD接口.....                               | 8  | 数字数据接口.....             | 34 |

| 功耗—VDDD1P3_DIG和VDDAx<br>(全部1.3 V电源相结合)..... | 10 | 使能状态机.....              | 34 |

| 绝对最大额定值.....                                | 15 | SPI接口.....              | 35 |

| 回流温度曲线.....                                 | 15 | 控制引脚.....               | 35 |

| 热阻.....                                     | 15 | GPO引脚(GPO_3至GPO_0)..... | 35 |

| ESD警告.....                                  | 15 | 辅助转换器.....              | 35 |

| 引脚配置和功能描述.....                              | 16 | AD9361的供电.....          | 35 |

| 典型性能参数.....                                 | 20 | 封装和订购信息.....            | 36 |

| 800 MHz频段.....                              | 20 | 外形尺寸.....               | 36 |

| 2.4 GHz频段.....                              | 25 | 订购指南.....               | 36 |

| 5.5 GHz频段.....                              | 29 |                         |    |

## 修订历史

**2013年11月—修订版C至修订版D**

更改“订购指南”..... 36

**2013年9月—修订版C：初始版**

## 规格

除非另有说明，电气特性在VDD\_GPO = 3.3 V, VDD\_INTERFACE = 1.8 V, 所有其他VDDx引脚= 1.3 V, TA = 25°C下测得。

表1.

| 参数 <sup>1</sup>                                                                                                                                                                                                      | 符号                 | 最小值                     | 典型值                                                                                                                    | 最大值                                                                       | 件 | 测试条件/注释                                                                                        |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|-------------------------|------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------|---|------------------------------------------------------------------------------------------------|

| 接收器, 一般<br>中心频率<br>增益<br>最小值<br>最大值<br><br>增益步进<br>接收信号强度指示器<br>档位<br>准确度                                                                                                                                            | RSSI               | 70<br><br>65.5<br><br>1 | 6000<br><br>0<br><br>74.5<br><br>73.0<br><br>72.0<br><br>100<br><br>±2                                                 | MHz<br><br>dB<br><br>dB<br><br>dB<br><br>dB<br><br>dB<br><br>dB<br><br>dB |   | 800 MHz<br>2300 MHz (RX1A, RX2A)<br>2300 MHz (RX1B, RX1C, RX2B, RX2C)<br>5500 MHz (RX1A, RX2A) |

| 接收器, 800 MHz<br>噪声系数<br>三阶输入交调载点<br>二阶输入交调载点<br>本振(LO)泄漏<br>正交<br>增益误差<br>相位误差<br>调制精度(EVM)<br>输入S <sub>11</sub><br>RX1至RX2隔离<br>RX1A至RX2A, RX1C至RX2C<br>RX1B至RX2B<br>RX2至RX1隔离<br>RX2A至RX1A, RX2C至RX1C<br>RX2B至RX1B | NF<br>IIP3<br>IIP2 |                         | 2<br><br>-18<br><br>40<br><br>-122<br><br>0.2<br><br>0.2<br><br>-42<br><br>-10<br><br>70<br><br>55<br><br>70<br><br>55 | dB<br><br>dBm<br><br>dBm<br><br>dBm<br><br>%<br><br>度<br><br>dB<br><br>dB |   | 最大RX增益<br>最大RX增益<br>最大RX增益<br>RX前端输入<br><br>19.2 MHz参考时钟                                       |

| 接收器, 2.4 GHz<br>噪声系数<br>三阶输入交调载点<br>二阶输入交调载点<br>本振(LO)泄漏<br>正交<br>增益误差<br>相位误差<br>调制精度(EVM)<br>输入S <sub>11</sub><br>RX1至RX2隔离<br>RX1A至RX2A, RX1C至RX2C<br>RX1B至RX2B<br>RX2至RX1隔离<br>RX2A至RX1A, RX2C至RX1C<br>RX2B至RX1B | NF<br>IIP3<br>IIP2 |                         | 3<br><br>-14<br><br>45<br><br>-110<br><br>0.2<br><br>0.2<br><br>-42<br><br>-10<br><br>65<br><br>50<br><br>65<br><br>50 | dB<br><br>dBm<br><br>dBm<br><br>dBm<br><br>%<br><br>度<br><br>dB<br><br>dB |   | 最大RX增益<br>最大RX增益<br>最大RX增益<br>接收器前端输入<br><br>40 MHz参考时钟                                        |

# AD9361

| 参数 <sup>1</sup>   | 符号   | 最小值 | 典型值    | 最大值  | 件      | 测试条件/注释                           |

|-------------------|------|-----|--------|------|--------|-----------------------------------|

| 接收器, 5.5 GHz      |      |     |        |      |        |                                   |

| 噪声系数              | NF   |     | 3.8    |      | dB     | 最大RX增益                            |

| 三阶输入交调载点          | IIP3 |     | -17    |      | dBm    | 最大RX增益                            |

| 二阶输入交调载点          | IIP2 |     | 42     |      | dBm    | 最大RX增益                            |

| 本振(LO)泄漏          |      |     | -95    |      | dBm    | RX前端输入                            |

| 正交                |      |     |        |      |        |                                   |

| 增益误差              |      |     | 0.2    |      | %      |                                   |

| 相位误差              |      |     | 0.2    |      | 度      |                                   |

| 调制精度(EVM)         |      |     | -37    |      | dB     | 40 MHz参考时钟<br>(针对RF频率<br>合成器内部加倍) |

| 输入S <sub>11</sub> |      |     | -10    |      | dB     |                                   |

| RX1A至RX2A隔离       |      |     | 52     |      | dB     |                                   |

| RX2A至RX1A隔离       |      |     | 52     |      | dB     |                                   |

| 发射器——一般           |      | 70  |        | 6000 | MHz    |                                   |

| 中心频率              |      |     | 90     |      | dB     |                                   |

| 功率控制范围            |      |     | 0.25   |      | dB     |                                   |

| 功率控制分辨率           |      |     |        |      |        |                                   |

| 发射器, 800 MHz      |      |     |        |      |        |                                   |

| 输出S <sub>22</sub> |      |     | -10    |      | dB     |                                   |

| 最大输出功率            |      |     | 8      |      | dBm    | 1 MHz信号音(50 Ω负载)                  |

| 调制精度(EVM)         |      |     | -40    |      | dB     | 19.2 MHz参考时钟                      |

| 三阶输出交调载点          | OIP3 |     | 23     |      | dBm    |                                   |

| 载波泄漏              |      |     | -50    |      | dBc    | 0 dB衰减                            |

| 本底噪声              |      |     | -32    |      | dBc    | 40 dB衰减                           |

| 隔离                |      |     | -157   |      | dBm/Hz | 90 MHz偏移                          |

| TX1至TX2           |      |     | 50     |      | dB     |                                   |

| TX2至TX1           |      |     | 50     |      | dB     |                                   |

| 发射器, 2.4 GHz      |      |     |        |      |        |                                   |

| 输出S <sub>22</sub> |      |     | -10    |      | dB     |                                   |

| 最大输出功率            |      |     | 7.5    |      | dBm    | 1 MHz信号音(50 Ω负载)                  |

| 调制精度(EVM)         |      |     | -40    |      | dB     | 40 MHz参考时钟                        |

| 三阶输出交调载点          | OIP3 |     | 19     |      | dBm    |                                   |

| 载波泄漏              |      |     | -50    |      | dBc    | 0 dB衰减                            |

| 本底噪声              |      |     | -32    |      | dBc    | 40 dB衰减                           |

| 隔离                |      |     | -156   |      | dBm/Hz | 90 MHz偏移                          |

| TX1至TX2           |      |     | 50     |      | dB     |                                   |

| TX2至TX1           |      |     | 50     |      | dB     |                                   |

| 发射器, 5.5 GHz      |      |     |        |      |        |                                   |

| 输出S <sub>22</sub> |      |     | -10    |      | dB     |                                   |

| 最大输出功率            |      |     | 6.5    |      | dBm    | 7.7 MHz信号音(50 Ω负载)                |

| 调制精度(EVM)         |      |     | -36    |      | dB     | 40 MHz参考时钟<br>(针对RF频率<br>合成器内部加倍) |

| 三阶输出交调载点          | OIP3 |     | 17     |      | dBm    |                                   |

| 载波泄漏              |      |     | -50    |      | dBc    | 0 dB衰减                            |

| 本底噪声              |      |     | -30    |      | dBc    | 40 dB衰减                           |

| 隔离                |      |     | -151.5 |      | dBm/Hz | 90 MHz偏移                          |

| TX1至TX2           |      |     | 50     |      | dB     |                                   |

| TX2至TX1           |      |     | 50     |      | dB     |                                   |

| 参数 <sup>1</sup>           | 符号 | 最小值                 | 典型值               | 最大值                 | 单位    | 测试条件/注释                                       |

|---------------------------|----|---------------------|-------------------|---------------------|-------|-----------------------------------------------|

| TX监控器输入(TX_MON1, TX_MON2) |    |                     | 4                 |                     | dBm   |                                               |

| 最大输入电平                    |    |                     | 66                |                     | dB    |                                               |

| 动态范围                      |    |                     | 1                 |                     | dB    |                                               |

| 准确度                       |    |                     |                   |                     |       |                                               |

| LO频率合成器                   |    |                     | 2.4               |                     | Hz    | 2.4 GHz, 40 MHz 参考时钟                          |

| LO频率阶跃                    |    |                     |                   |                     |       |                                               |

| 积分相位噪声                    |    |                     | 0.13              |                     | ° rms | 100 Hz至100 MHz, 30.72 MHz参考时钟 (针对RF频率合成器内部加倍) |

| 800 MHz                   |    |                     |                   |                     |       |                                               |

| 2.4 GHz                   |    |                     | 0.37              |                     | ° rms | 100 Hz至100 MHz, 40 MHz参考时钟                    |

| 5.5 GHz                   |    |                     | 0.59              |                     | ° rms | 100 Hz至100 MHz, 40 MHz参考时钟 (针对RF频率合成器内部加倍)    |

| 参考时钟(REF_CLK)             |    |                     |                   |                     |       | REF_CLK要么为XTALP/XTALN引脚的输入, 要么为直接连接XTALN引脚的线路 |

| 输入                        |    |                     |                   |                     |       |                                               |

| 频率范围                      |    | 19                  |                   | 50                  | MHz   | 晶振输入                                          |

|                           |    | 10                  |                   | 80                  | MHz   | 外部振荡器                                         |

| 信号电平                      |    |                     | 1.3               |                     | V p-p | 交流耦合外部振荡器                                     |

| 辅助转换器                     |    |                     |                   |                     |       |                                               |

| ADC                       |    |                     | 12                |                     | 位     |                                               |

| 分辨率                       |    |                     |                   |                     |       |                                               |

| 输入电压                      |    |                     | 0.05              |                     | V     |                                               |

| 最小值                       |    |                     | VDDA1P3_BB - 0.05 |                     | V     |                                               |

| 最大值                       |    |                     |                   |                     |       |                                               |

| DAC                       |    |                     | 10                |                     | 位     |                                               |

| 分辨率                       |    |                     |                   |                     |       |                                               |

| 输出电压                      |    |                     | 0.5               |                     | V     |                                               |

| 最小值                       |    |                     | VDD_GPO - 0.3     |                     | V     |                                               |

| 最大值                       |    |                     |                   |                     |       |                                               |

| 输出电流                      |    |                     | 10                |                     | mA    |                                               |

| 数字规格(CMOS)                |    |                     |                   |                     |       |                                               |

| 逻辑输入                      |    |                     |                   |                     |       |                                               |

| 输入电压                      |    | VDD_INTERFACE × 0.8 |                   | VDD_INTERFACE       | V     |                                               |

| 高                         |    | 0                   |                   | VDD_INTERFACE × 0.2 | V     |                                               |

| 低                         |    |                     |                   |                     |       |                                               |

| 输入电流                      |    |                     |                   |                     |       |                                               |

| 高                         |    | -10                 | +10               |                     | μA    |                                               |

| 低                         |    | -10                 | +10               |                     | μA    |                                               |

| 逻辑输出                      |    |                     |                   |                     |       |                                               |

| 输出电压                      |    | VDD_INTERFACE × 0.8 |                   | VDD_INTERFACE × 0.2 | V     |                                               |

| 高                         |    |                     |                   |                     |       |                                               |

| 低                         |    |                     |                   |                     |       |                                               |

| 数字规格(LVDS)                |    |                     |                   |                     |       |                                               |

| 逻辑输入                      |    |                     |                   |                     |       |                                               |

| 输入电压范围                    |    | 825                 |                   | 1575                | mV    | 对中的各差分输入                                      |

| 输入差分电压阈值                  |    | -100                |                   | +100                | mV    |                                               |

| 接收机差分输入阻抗                 |    |                     | 100               |                     | Ω     |                                               |

**AD9361**

| 参数 <sup>1</sup>                        | 符号                   | 最小值                  | 典型值 | 最大值                  | 单位 | 测试条件/注释       |

|----------------------------------------|----------------------|----------------------|-----|----------------------|----|---------------|

| 数字数据时序(CMOS),<br>VDD_INTERFACE = 2.5 V |                      |                      |     |                      |    |               |

| DATA_CLK时钟周期                           | t <sub>CP</sub>      | 16.276               |     |                      | ns | 61.44 MHz     |

| DATA_CLK和FB_CLK脉冲宽度                    | t <sub>MP</sub>      | t <sub>CP</sub> 的45% |     | t <sub>CP</sub> 的55% | ns |               |

| TX数据                                   |                      |                      |     |                      |    |               |

| 建立至FB_CLK                              | t <sub>STX</sub>     | 1                    |     |                      | ns |               |

| 保持至FB_CLK                              | t <sub>HTX</sub>     | 0                    |     |                      | ns |               |

| DATA_CLK至数据总线输出延迟                      | t <sub>DDRX</sub>    | 0                    |     | 1.2                  | ns |               |

| DATA_CLK至RX_FRAME延迟                    | t <sub>DDDV</sub>    | 0                    |     | 1.0                  | ns |               |

| 脉冲宽度                                   |                      |                      |     |                      |    |               |

| 使能                                     | t <sub>ENPW</sub>    | t <sub>CP</sub>      |     |                      | ns |               |

| TXNRX                                  | t <sub>TXNRXPW</sub> | t <sub>CP</sub>      |     |                      | ns | FDD独立ENSM模式   |

| TXNRX建立至ENABLE                         | t <sub>TXNRXSU</sub> | 0                    |     |                      | ns | TDD ENSM模式    |

| 总线周转时间                                 |                      |                      |     |                      |    |               |

| RX前                                    | t <sub>RPRE</sub>    | 2 × t <sub>CP</sub>  |     |                      | ns | TDD模式         |

| RX后                                    | t <sub>RPST</sub>    | 2 × t <sub>CP</sub>  |     |                      | ns | TDD模式         |

| 容性负载                                   |                      |                      | 3   |                      | pF |               |

| 容性输入                                   |                      |                      | 3   |                      | pF |               |

| 数字数据时序(LVDS)                           |                      |                      |     |                      |    |               |

| DATA_CLK时钟周期                           | t <sub>CP</sub>      | 4.069                |     |                      | ns | 245.76 MHz    |

| DATA_CLK和FB_CLK脉冲宽度                    | t <sub>MP</sub>      | t <sub>CP</sub> 的45% |     | t <sub>CP</sub> 的55% | ns |               |

| TX数据                                   |                      |                      |     |                      |    |               |

| 建立至FB_CLK                              | t <sub>STX</sub>     | 1                    |     |                      | ns |               |

| 保持至FB_CLK                              | t <sub>HTX</sub>     | 0                    |     |                      | ns |               |

| DATA_CLK至数据总线输出延迟                      | t <sub>DDRX</sub>    | 0.25                 |     | 1.25                 | ns |               |

| DATA_CLK至RX_FRAME延迟                    | t <sub>DDDV</sub>    | 0.25                 |     | 1.25                 | ns |               |

| 脉冲宽度                                   |                      |                      |     |                      |    |               |

| 使能                                     | t <sub>ENPW</sub>    | t <sub>CP</sub>      |     |                      | ns |               |

| TXNRX                                  | t <sub>TXNRXPW</sub> | t <sub>CP</sub>      |     |                      | ns | FDD独立ENSM模式   |

| TXNRX建立至ENABLE                         | t <sub>TXNRXSU</sub> | 0                    |     |                      | ns | TDD ENSM模式    |

| 总线周转时间                                 |                      |                      |     |                      |    |               |

| RX前                                    | t <sub>RPRE</sub>    | 2 × t <sub>CP</sub>  |     |                      | ns |               |

| RX后                                    | t <sub>RPST</sub>    | 2 × t <sub>CP</sub>  |     |                      | ns |               |

| 容性负载                                   |                      |                      | 3   |                      | pF |               |

| 容性输入                                   |                      |                      | 3   |                      | pF |               |

| 电源特性                                   |                      |                      |     |                      |    |               |

| 1.3 V电源电压                              |                      | 1.267                | 1.3 | 1.33                 | V  |               |

| VDD_INTERFACE电源额定设置                    |                      |                      |     |                      |    |               |

| CMOS                                   |                      | 1.2                  |     | 2.5                  | V  |               |

| LVDS                                   |                      | 1.8                  |     | 2.5                  | V  |               |

| VDD_INTERFACE容差                        |                      | -5                   |     | +5                   | %  | 容差适用于任何电压设置   |

| VDD_GPO电源标称设置                          |                      | 1.3                  |     | 3.3                  | V  | 未用时，必须设为1.3 V |

| VDD_GPO容差                              |                      | -5                   |     | +5                   | %  | 容差适用于任何电压设置   |

| 电流消耗                                   |                      |                      |     |                      |    |               |

| VDDx, 休眠模式                             |                      |                      | 180 |                      | μA | 所有输入电流之和      |

| VDD_GPO                                |                      |                      | 50  |                      | μA | 无负载           |

<sup>1</sup> 指参数中多功能引脚的单个功能时，只会列出引脚名称中与规格相关的部分。要了解多功能引脚的全部引脚名称，请参见“引脚配置和功能描述”部分。

# AD9361

## 功耗——VDD\_INTERFACE

表2.VDD\_INTERFACE = 1.2 V

| 参数                                         | 最小值 | 典型值               | 最大值 | 件              | 测试条件/注释                                                        |

|--------------------------------------------|-----|-------------------|-----|----------------|----------------------------------------------------------------|

| 休眠模式                                       | 45  |                   |     | μA             | 加电, 器件禁用                                                       |

| 1RX, 1TX, DDR<br>LTE10<br>单端口<br>双端口       |     | 2.9<br>2.7        |     | mA<br>mA       | 30.72 MHz数据时钟, CMOS<br>15.36 MHz数据时钟, CMOS                     |

| LTE20<br>双端口                               |     | 5.2               |     | mA             | 30.72 MHz数据时钟, CMOS                                            |

| 2RX, 2TX, DDR<br>LTE3<br>双端口               |     | 1.3               |     | mA             | 7.68 MHz数据时钟, CMOS                                             |

| LTE10<br>单端口<br>双端口                        |     | 4.6<br>5.0        |     | mA<br>mA       | 61.44 MHz数据时钟, CMOS<br>30.72 MHz数据时钟, CMOS                     |

| LTE20<br>双端口                               |     | 8.2               |     | mA             | 61.44 MHz数据时钟, CMOS                                            |

| GSM<br>双端口                                 |     | 0.2               |     | mA             | 1.08 MHz数据时钟, CMOS                                             |

| WiMAX 8.75<br>双端口                          |     | 3.3               |     | mA             | 20 MHz数据时钟, CMOS                                               |

| WiMAX 10<br>单端口<br>TDD RX<br>TDD TX<br>FDD |     | 0.5<br>3.6<br>3.8 |     | mA<br>mA<br>mA | 22.4 MHz数据时钟, CMOS<br>22.4 MHz数据时钟, CMOS<br>44.8 MHz数据时钟, CMOS |

| WiMAX 20<br>双端口<br>FDD                     |     | 6.7               |     | mA             | 44.8 MHz数据时钟, CMOS                                             |

表3.VDD\_INTERFACE = 1.8 V

| 参数                                   | 最小值 | 典型值        | 最大值 | 件        | 测试条件/注释                                    |

|--------------------------------------|-----|------------|-----|----------|--------------------------------------------|

| 休眠模式                                 | 84  |            |     | μA       | 加电, 器件禁用                                   |

| 1RX, 1TX, DDR<br>LTE10<br>单端口<br>双端口 |     | 4.5<br>4.1 |     | mA<br>mA | 30.72 MHz数据时钟, CMOS<br>15.36 MHz数据时钟, CMOS |

| LTE20<br>双端口                         |     | 8.0        |     | mA       | 30.72 MHz数据时钟, CMOS                        |

| 2RX, 2TX, DDR<br>LTE3<br>双端口         |     | 2.0        |     | mA       | 7.68 MHz数据时钟, CMOS                         |

| LTE10<br>单端口<br>双端口                  |     | 8.0<br>7.5 |     | mA<br>mA | 61.44 MHz数据时钟, CMOS<br>30.72 MHz数据时钟, CMOS |

| LTE20<br>双端口                         |     | 14.0       |     | mA       | 61.44 MHz数据时钟, CMOS                        |

| GSM<br>双端口                           |     | 0.3        |     | mA       | 1.08 MHz数据时钟, CMOS                         |

| WiMAX 8.75<br>双端口                    |     | 5.0        |     | mA       | 20 MHz数据时钟, CMOS                           |

| 参数                        | 最小值  | 典型值 | 最大值 | 件  | 测试条件/注释            |

|---------------------------|------|-----|-----|----|--------------------|

| WiMAX 10<br>单端口<br>TDD RX | 0.7  |     |     | mA | 22.4 MHz数据时钟, CMOS |

| TDD TX                    | 5.6  |     |     | mA | 22.4 MHz数据时钟, CMOS |

| FDD                       | 6.0  |     |     | mA | 44.8 MHz数据时钟, CMOS |

| WiMAX 20<br>双端口<br>FDD    | 10.7 |     |     | mA | 44.8 MHz数据时钟, CMOS |

| P-P56<br>75 mV差分输出        | 14.0 |     |     | mA | 240 MHz数据时钟, LVDS  |

| 300 mV差分输出                | 35.0 |     |     | mA | 240 MHz数据时钟, LVDS  |

| 450 mV差分输出                | 47.0 |     |     | mA | 240 MHz数据时钟, LVDS  |

表4.VDD\_INTERFACE = 2.5 V

| 参数                           | 最小值  | 典型值 | 最大值 | 件  | 测试条件/注释             |

|------------------------------|------|-----|-----|----|---------------------|

| 休眠模式<br>1RX, 1TX, DDR        | 150  |     |     | μA | 加电, 器件禁用            |

| LTE10<br>单端口                 | 6.5  |     |     | mA | 30.72 MHz数据时钟, CMOS |

| 双端口                          | 6.0  |     |     | mA | 15.36 MHz数据时钟, CMOS |

| LTE20<br>双端口                 | 11.5 |     |     | mA | 30.72 MHz数据时钟, CMOS |

| 2RX, 2TX, DDR<br>LTE3<br>双端口 | 3.0  |     |     | mA | 7.68 MHz数据时钟, CMOS  |

| LTE10<br>单端口                 | 11.5 |     |     | mA | 61.44 MHz数据时钟, CMOS |

| 双端口                          | 10.0 |     |     | mA | 30.72 MHz数据时钟, CMOS |

| LTE20<br>双端口                 | 20.0 |     |     | mA | 61.44 MHz数据时钟, CMOS |

| GSM<br>双端口                   | 0.5  |     |     | mA | 1.08 MHz数据时钟, CMOS  |

| WiMAX 8.75<br>双端口            | 7.3  |     |     | mA | 20 MHz数据时钟, CMOS    |

| WiMAX 10<br>单端口<br>TDD RX    | 1.3  |     |     | mA | 22.4 MHz数据时钟, CMOS  |

| TDD TX                       | 8.0  |     |     | mA | 22.4 MHz数据时钟, CMOS  |

| FDD                          | 8.7  |     |     | mA | 44.8 MHz数据时钟, CMOS  |

| WiMAX 20<br>双端口<br>FDD       | 15.3 |     |     | mA | 44.8 MHz数据时钟, CMOS  |

| P-P56<br>75 mV差分输出           | 26.0 |     |     | mA | 240 MHz数据时钟, LVDS   |

| 300 mV差分输出                   | 45.0 |     |     | mA | 240 MHz数据时钟, LVDS   |

| 450 mV差分输出                   | 58.0 |     |     | mA | 240 MHz数据时钟, LVDS   |

# AD9361

功耗——VDDD1P3\_DIG和VDDAx(全部1.3 V电源组合)

表5.800 MHz, TDD模式

| 参数       | 最小值 | 典型值 | 最大值 | 件    | 测试条件/注释 |

|----------|-----|-----|-----|------|---------|

| 1RX      |     |     |     |      |         |

| 5 MHz带宽  | 180 |     | mA  | 连续RX |         |

| 10 MHz带宽 | 210 |     | mA  | 连续RX |         |

| 20 MHz带宽 | 260 |     | mA  | 连续RX |         |

| 2RX      |     |     |     |      |         |

| 5 MHz带宽  | 265 |     | mA  | 连续RX |         |

| 10 MHz带宽 | 315 |     | mA  | 连续RX |         |

| 20 MHz带宽 | 405 |     | mA  | 连续RX |         |

| 1TX      |     |     |     |      |         |

| 5 MHz带宽  |     | 340 | mA  | 连续TX |         |

| 7 dBm    | 190 |     | mA  | 连续TX |         |

| -27 dBm  |     |     |     |      |         |

| 10 MHz带宽 |     | 360 | mA  | 连续TX |         |

| 7 dBm    | 220 |     | mA  | 连续TX |         |

| -27 dBm  |     |     |     |      |         |

| 20 MHz带宽 |     | 400 | mA  | 连续TX |         |

| 7 dBm    | 250 |     | mA  | 连续TX |         |

| -27 dBm  |     |     |     |      |         |

| 2TX      |     |     |     |      |         |

| 5 MHz带宽  |     | 550 | mA  | 连续TX |         |

| 7 dBm    | 260 |     | mA  | 连续TX |         |

| -27 dBm  |     |     |     |      |         |

| 10 MHz带宽 |     | 600 | mA  | 连续TX |         |

| 7 dBm    | 310 |     | mA  | 连续TX |         |

| -27 dBm  |     |     |     |      |         |

| 20 MHz带宽 |     | 660 | mA  | 连续TX |         |

| 7 dBm    | 370 |     | mA  | 连续TX |         |

| -27 dBm  |     |     |     |      |         |

表6.TDD模式，2.4 GHz

| 参数       | 最小值 | 典型值 | 最大值 | 件  | 测试条件/注释 |

|----------|-----|-----|-----|----|---------|

| 1RX      |     |     |     |    |         |

| 5 MHz带宽  |     | 175 |     | mA | 连续RX    |

| 10 MHz带宽 |     | 200 |     | mA | 连续RX    |

| 20 MHz带宽 |     | 240 |     | mA | 连续RX    |

| 2RX      |     |     |     |    |         |

| 5 MHz带宽  |     | 260 |     | mA | 连续RX    |

| 10 MHz带宽 |     | 305 |     | mA | 连续RX    |

| 20 MHz带宽 |     | 390 |     | mA | 连续RX    |

| 1TX      |     |     |     |    |         |

| 5 MHz带宽  |     | 350 |     | mA | 连续TX    |

| 7 dBm    |     | 160 |     | mA | 连续TX    |

| -27 dBm  |     |     |     |    |         |

| 10 MHz带宽 |     | 380 |     | mA | 连续TX    |

| 7 dBm    |     | 220 |     | mA | 连续TX    |

| -27 dBm  |     |     |     |    |         |

| 20 MHz带宽 |     | 410 |     | mA | 连续TX    |

| 7 dBm    |     | 260 |     | mA | 连续TX    |

| -27 dBm  |     |     |     |    |         |

| 2TX      |     |     |     |    |         |

| 5 MHz带宽  |     | 580 |     | mA | 连续TX    |

| 7 dBm    |     | 280 |     | mA | 连续TX    |

| -27 dBm  |     |     |     |    |         |

| 10 MHz带宽 |     | 635 |     | mA | 连续TX    |

| 7 dBm    |     | 330 |     | mA | 连续TX    |

| -27 dBm  |     |     |     |    |         |

| 20 MHz带宽 |     | 690 |     | mA | 连续TX    |

| 7 dBm    |     | 390 |     | mA | 连续TX    |

|          |     |     |     |    |         |

表7.TDD模式，5.5 GHz

| 参数       | 最小值 | 典型值 | 最大值 | 件  | 测试条件/注释 |

|----------|-----|-----|-----|----|---------|

| 1RX      |     |     |     |    |         |

| 5 MHz带宽  |     | 175 |     | mA | 连续RX    |

| 40 MHz带宽 |     | 275 |     | mA | 连续RX    |

| 2RX      |     |     |     |    |         |

| 5 MHz带宽  |     | 270 |     | mA | 连续RX    |

| 40 MHz带宽 |     | 445 |     | mA | 连续RX    |

| 1TX      |     |     |     |    |         |

| 5 MHz带宽  |     | 400 |     | mA | 连续TX    |

| 7 dBm    |     | 240 |     | mA | 连续TX    |

| -27 dBm  |     |     |     |    |         |

| 40 MHz带宽 |     | 490 |     | mA | 连续TX    |

| 7 dBm    |     | 385 |     | mA | 连续TX    |

| 2TX      |     |     |     |    |         |

| 5 MHz带宽  |     | 650 |     | mA | 连续TX    |

| 7 dBm    |     | 335 |     | mA | 连续TX    |

| -27 dBm  |     |     |     |    |         |

| 40 MHz带宽 |     | 820 |     | mA | 连续TX    |

| 7 dBm    |     | 500 |     | mA | 连续TX    |

|          |     |     |     |    |         |

# AD9361

表8.FDD模式，800 MHz

| 参数                                                                                                      | 最小值 | 典型值                                     | 最大值 | 件                                | 测试条件/注释 |

|---------------------------------------------------------------------------------------------------------|-----|-----------------------------------------|-----|----------------------------------|---------|

| 1RX, 1TX<br>5 MHz带宽<br>7 dBm<br>–27 dBm<br>10 MHz带宽<br>7 dBm<br>–27 dBm<br>20 MHz带宽<br>7 dBm<br>–27 dBm |     | 490<br>345<br>540<br>395<br>615<br>470  |     | mA<br>mA<br>mA<br>mA<br>mA<br>mA |         |

| 2RX, 1TX<br>5 MHz带宽<br>7 dBm<br>–27 dBm<br>10 MHz带宽<br>7 dBm<br>–27 dBm<br>20 MHz带宽<br>7 dBm<br>–27 dBm |     | 555<br>410<br>625<br>480<br>740<br>600  |     | mA<br>mA<br>mA<br>mA<br>mA<br>mA |         |

| 1RX, 2TX<br>5 MHz带宽<br>7 dBm<br>–27 dBm<br>10 MHz带宽<br>7 dBm<br>–27 dBm<br>20 MHz带宽<br>7 dBm<br>–27 dBm |     | 685<br>395<br>755<br>465<br>850<br>570  |     | mA<br>mA<br>mA<br>mA<br>mA<br>mA |         |

| 2RX, 2TX<br>5 MHz带宽<br>7 dBm<br>–27 dBm<br>10 MHz带宽<br>7 dBm<br>–27 dBm<br>20 MHz带宽<br>7 dBm<br>–27 dBm |     | 790<br>495<br>885<br>590<br>1020<br>730 |     | mA<br>mA<br>mA<br>mA<br>mA<br>mA |         |

表9.FDD模式，2.4 GHz

| 参数       | 最小值 | 典型值  | 最大值 | 件  | 测试条件/注释 |

|----------|-----|------|-----|----|---------|

| 1RX, 1TX |     |      |     |    |         |

| 5 MHz带宽  |     |      |     |    |         |

| 7 dBm    |     | 500  |     | mA |         |

| −27 dBm  |     | 350  |     | mA |         |

| 10 MHz带宽 |     |      |     |    |         |

| 7 dBm    |     | 540  |     | mA |         |

| −27 dBm  |     | 390  |     | mA |         |

| 20 MHz带宽 |     |      |     |    |         |

| 7 dBm    |     | 620  |     | mA |         |

| −27 dBm  |     | 475  |     | mA |         |

| 2RX, 1TX |     |      |     |    |         |

| 5 MHz带宽  |     |      |     |    |         |

| 7 dBm    |     | 590  |     | mA |         |

| −27 dBm  |     | 435  |     | mA |         |

| 10 MHz带宽 |     |      |     |    |         |

| 7 dBm    |     | 660  |     | mA |         |

| −27 dBm  |     | 510  |     | mA |         |

| 20 MHz带宽 |     |      |     |    |         |

| 7 dBm    |     | 770  |     | mA |         |

| −27 dBm  |     | 620  |     | mA |         |

| 1RX, 2TX |     |      |     | mA |         |

| 5 MHz带宽  |     |      |     |    |         |

| 7 dBm    |     | 730  |     | mA |         |

| −27 dBm  |     | 425  |     | mA |         |

| 10 MHz带宽 |     |      |     |    |         |

| 7 dBm    |     | 800  |     | mA |         |

| −27 dBm  |     | 500  |     | mA |         |

| 20 MHz带宽 |     |      |     |    |         |

| 7 dBm    |     | 900  |     | mA |         |

| −27 dBm  |     | 600  |     | mA |         |

| 2RX, 2TX |     |      |     | mA |         |

| 5 MHz带宽  |     |      |     |    |         |

| 7 dBm    |     | 820  |     | mA |         |

| −27 dBm  |     | 515  |     | mA |         |

| 10 MHz带宽 |     |      |     |    |         |

| 7 dBm    |     | 900  |     | mA |         |

| −27 dBm  |     | 595  |     | mA |         |

| 20 MHz带宽 |     |      |     |    |         |

| 7 dBm    |     | 1050 |     | mA |         |

| −27 dBm  |     | 740  |     | mA |         |

# AD9361

表10.FDD模式，5.5 GHz

| 参数                                      | 最小值 | 典型值        | 最大值 | 件        | 测试条件/注释 |

|-----------------------------------------|-----|------------|-----|----------|---------|

| 1RX, 1TX<br>5 MHz带宽<br>7 dBm<br>-27 dBm |     | 550<br>385 |     | mA<br>mA |         |

| 2RX, 1TX<br>5 MHz带宽<br>7 dBm<br>-27 dBm |     | 645<br>480 |     | mA<br>mA |         |

| 1RX, 2TX<br>5 MHz带宽<br>7 dBm<br>-27 dBm |     | 805<br>480 |     | mA<br>mA |         |

| 2RX, 2TX<br>5 MHz带宽<br>7 dBm<br>-27 dBm |     | 895<br>575 |     | mA<br>mA |         |

## 绝对最大额定值

表11.

| 参数                  | 评分                             |

|---------------------|--------------------------------|

| VDDx至VSSx           | -0.3 V至+1.4 V                  |

| VDD_INTERFACE至VSSx  | -0.3 V至+3.0 V                  |

| VDD_GPO至VSSx        | -0.3 V至+3.9 V                  |

| 逻辑输入和输出至VSSx        | -0.3 V至VDD_INTERFACE + 0.3 V   |

| 输入电流至除电源引脚外的任何引脚    | $\pm 10 \text{ mA}$            |

| RF输入(峰值功率)          | 2.5 dBm                        |

| TX监控器输入功率<br>(峰值功率) | 9 dBm                          |

| 封装功耗                | $(T_{JMAX} - T_A)/\theta_{JA}$ |

| 最大结温( $T_{JMAX}$ )  | 110°C                          |

| 工作温度范围              | -40°C至+85°C                    |

| 存储温度范围              | -65°C至+150°C                   |

注意，超出上述绝对最大额定值可能会导致器件永久性损坏。这只是额定最值，并不能以这些条件或者在任何其它超出本技术规范操作章节中所示规格的条件下，推断器件能否正常工作。长期在绝对最大额定值条件下工作会影响器件的可靠性。

## 回流温度曲线

AD9361回流温度曲线依据的是JEDEC JESD20无铅器件标准。

最大回流温度为260°C。

## 热阻

$\theta_{JA}$ 针对最差条件，即器件焊接在电路板上实现表贴封装。

表12.热阻

| 封装类型    | 气流速度<br>(m/s) | $\theta_{JA}^{1,2}$ | $\theta_{JC}^{1,3}$ | $\theta_{JB}^{1,4}$ | $\Psi_{JT}^{1,2}$ | 件    |

|---------|---------------|---------------------|---------------------|---------------------|-------------------|------|

| 144引脚   | 0             | 32.3                | 9.6                 | 20.2                | 0.27              | °C/W |

| CSP_BGA | 1.0           | 29.6                |                     |                     | 0.43              | °C/W |

|         | 2.5           | 27.8                |                     |                     | 0.57              | °C/W |

<sup>1</sup> 按照JEDEC JESD51-7，加上JEDEC JESD51-5 2S2P测试板。

<sup>2</sup> 按照JEDEC JESD51-2(静止空气)或JEDEC JESD51-6(流动空气)。

<sup>3</sup> 按照MIL-STD 883、方法1012.1。

<sup>4</sup> 按照JEDEC JESD51-8(静止空气)。

## ESD警告

### ESD(静电放电)敏感器件。

带电器件和电路板可能会在没有察觉的情况下放电。尽管本产品具有专利或专有保护电路，但在遇到高能量ESD时，器件可能会损坏。因此，应当采取适当的ESD防范措施，以避免器件性能下降或功能丧失。

## 引脚配置和功能描述

|   | 1            | 2                  | 3                    | 4           | 5         | 6         | 7              | 8              | 9             | 10                 | 11             | 12            |

|---|--------------|--------------------|----------------------|-------------|-----------|-----------|----------------|----------------|---------------|--------------------|----------------|---------------|

| A | RX2A_N       | RX2A_P             | NC                   | VSSA        | TX_MON2   | VSSA      | TX2A_N         | TX2A_P         | TX2B_N        | TX2B_P             | VDDA1P1_TX_VCO | TX_EXT_LO_IN  |

| B | VSSA         | VSSA               | AUXDAC1              | GPO_3       | GPO_2     | GPO_1     | GPO_0          | VDD_GPO        | VDDA1P3_TX_LO | VDDA1P3_TX_VCO_LDO | TX_VCO_LDO_OUT | VSSA          |

| C | RX2C_P       | VSSA               | AUXDAC2              | TEST/ENABLE | CTRL_IN0  | CTRL_IN1  | VSSA           | VSSA           | VSSA          | VSSA               | VSSA           | VSSA          |

| D | RX2C_N       | VDDA1P3_RX_RF      | VDDA1P3_RX_TX        | CTRL_OUT0   | CTRL_IN3  | CTRL_IN2  | P0_D9/TX_D4_P  | P0_D7/TX_D3_P  | P0_D5/TX_D2_P | P0_D3/TX_D1_P      | P0_D1/TX_D0_P  | VSSD          |

| E | RX2B_P       | VDDA1P3_RX_LO      | VDDA1P3_RX_LO_BUFFER | CTRL_OUT1   | CTRL_OUT2 | CTRL_OUT3 | P0_D11/TX_D5_P | P0_D8/TX_D4_N  | P0_D6/TX_D3_N | P0_D4/TX_D2_N      | P0_D2/TX_D1_N  | P0_D0/TX_D0_N |

| F | RX2B_N       | VDDA1P3_RX_VCO_LDO | VSSA                 | CTRL_OUT6   | CTRL_OUT5 | CTRL_OUT4 | VSSD           | P0_D10/TX_D5_N | VSSD          | FB_CLK_P           | VSSD           | VDDD1P3_DIG   |

| G | RX_EXT_LO_IN | RX_VCO_LDO_OUT     | VDDA1P1_RX_VCO       | CTRL_OUT7   | EN_AGC    | ENABLE    | RX_FRAME_N     | RX_FRAME_P     | TX_FRAME_P    | FB_CLK_N           | DATA_CLK_P     | VSSD          |

| H | RX1B_P       | VSSA               | VSSA                 | TXNRX       | SYNC_IN   | VSSA      | VSSD           | P1_D11/RX_D5_P | TX_FRAME_N    | VSSD               | DATA_CLK_N     | VDD_INTERFACE |

| J | RX1B_N       | VSSA               | VDDA1P3_RX_SYNTH     | SPI_DI      | SPI_CLK   | CLK_OUT   | P1_D10/RX_D5_N | P1_D9/RX_D4_P  | P1_D7/RX_D3_P | P1_D5/RX_D2_P      | P1_D3/RX_D1_P  | P1_D1/RX_D0_P |

| K | RX1C_P       | VSSA               | VDDA1P3_TX_SYNTH     | VDDA1P3_BB  | RESETB    | SPI_ENB   | P1_D8/RX_D4_N  | P1_D6/RX_D3_N  | P1_D4/RX_D2_N | P1_D2/RX_D1_N      | P1_D0/RX_D0_N  | VSSD          |

| L | RX1C_N       | VSSA               | VSSA                 | RBIAS       | AUXADC    | SPI_DO    | VSSA           | VSSA           | VSSA          | VSSA               | VSSA           | VSSA          |

| M | RX1A_P       | RX1A_N             | NC                   | VSSA        | TX_MON1   | VSSA      | TX1A_P         | TX1A_N         | TX1B_P        | TX1B_N             | XTALP          | XTALN         |

ANALOG I/O     DC POWER

DIGITAL I/O     GROUND

NO CONNECT

10453-002

图2.引脚配置(顶视图)

表13.引脚功能描述

| 引脚编号                                                                                  | 类型 <sup>1</sup> | 引脚名称               | 说明                                                             |

|---------------------------------------------------------------------------------------|-----------------|--------------------|----------------------------------------------------------------|

| A1, A2                                                                                | I               | RX2A_N, RX2A_P     | 接收通道2差分输入A。或者，每个引脚都可作为单端输入或者结合形成差分对。将未使用的引脚接地。                 |

| A3, M3                                                                                | NC              | NC                 | 不连接。请勿连接到这些引脚。                                                 |

| A4, A6, B1, B2, B12, C2, C7 to C12, F3, H2, H3, H6, J2, K2, L2, L3, L7 to L12, M4, M6 | I               | VSSA               | 模拟地。将这些引脚直接连接至印刷电路板上的VSSD数字地(一个接地层)。                           |

| A5                                                                                    | I               | TX_MON2            | 发射通道2功率监控输入。若未使用此引脚，则将其接地。                                     |

| A7, A8                                                                                | O               | TX2A_N, TX2A_P     | 发射通道2差分输出A。将未使用的引脚连接至1.3 V。                                    |

| A9, A10                                                                               | O               | TX2B_N, TX2B_P     | 发射通道2差分输出B。将未使用的引脚连接至1.3 V。                                    |

| A11                                                                                   | I               | VDDA1P1_TX_VCO     | 发射VCO电源输入。连接至B11。                                              |

| A12                                                                                   | I               | TX_EXT_LO_IN       | 外部发射LO输入。若未使用此引脚，则将其接地。                                        |

| B3                                                                                    | O               | AUXDAC1            | 辅助DAC 1输出。                                                     |

| B4至B7                                                                                 | O               | GPO_3 to GPO_0     | 支持3.3 V的通用输出。                                                  |

| B8                                                                                    | I               | VDD_GPO            | 2.5 V至3.3 V电源，支持AUXDAC和通用输出引脚。不使用VDD_GPO电源时，必须将该电源设为1.3 V。     |

| B9                                                                                    | I               | VDDA1P3_TX_LO      | 发射LO 1.3 V电源输入。                                                |

| B10                                                                                   | I               | VDDA1P3_TX_VCO_LDO | 发射VCO LDO 1.3 V电源输入。连接至B9。                                     |

| B11                                                                                   | O               | TX_VCO_LDO_OUT     | 发射VCO LDO输出。连接至A11，将一个1 μF旁路电容与一个1 Ω电阻串联接地。                    |

| C1, D1                                                                                | I               | RX2C_P, RX2C_N     | 接收通道2差分输入C。每个引脚都可作为单端输入或者结合形成差分对。这些输入在3 GHz以上时性能会下降。将未使用的引脚接地。 |

| 引脚编号                                      | 类型 <sup>1</sup> | 引脚名称                                                                   | 说明                                                                                                              |

|-------------------------------------------|-----------------|------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------|

| C3                                        | O               | AUXDAC2                                                                | 辅助DAC 2输出。                                                                                                      |

| C4                                        | I               | 测试/使能                                                                  | 测试输入。正常工作时，将该引脚接地。                                                                                              |

| C5, C6, D5, D6                            | I               | CTRL_IN0至CTRL_IN3                                                      | 控制输入。用于手动RX增益和TX衰减控制。                                                                                           |

| D2                                        | I               | VDDA1P3_RX_RF                                                          | 接收器1.3 V电源输入。连接至D3。                                                                                             |

| D3                                        | I               | VDDA1P3_RX_TX                                                          | 1.3 V电源输入。                                                                                                      |

| D4, E4至E6,<br>F4至F6, G4                   | O               | CTRL_OUT0, CTRL_OUT1至<br>CTRL_OUT3, CTRL_OUT6至<br>CTRL_OUT4, CTRL_OUT7 | 控制输出。这些引脚是多功能输出，具有可编程功能。                                                                                        |

| D7                                        | I/O             | P0_D9/TX_D4_P                                                          | 数字数据端口P0/发射差分输入总线。这是双功能引脚。对于P0_D9，它充当12位双向并行CMOS电平数据端口0的一部分。或者，该引脚(TX_D4_P)也可作为LVDS 6位TX差分输入总线(带内部LVDS端子)的一部分。  |

| D8                                        | I/O             | P0_D7/TX_D3_P                                                          | 数字数据端口P0/发射差分输入总线。这是双功能引脚。对于P0_D7，它充当12位双向并行CMOS电平数据端口0的一部分。或者，该引脚(TX_D3_P)也可作为LVDS 6位TX差分输入总线(带内部LVDS端子)的一部分。  |

| D9                                        | I/O             | P0_D5/TX_D2_P                                                          | 数字数据端口P0/发射差分输入总线。这是双功能引脚。对于P0_D5，它充当12位双向并行CMOS电平数据端口0的一部分。或者，该引脚(TX_D2_P)也可作为LVDS 6位TX差分输入总线(带内部LVDS端子)的一部分。  |

| D10                                       | I/O             | P0_D3/TX_D1_P                                                          | 数字数据端口P0/发射差分输入总线。这是双功能引脚。对于P0_D3，它充当12位双向并行CMOS电平数据端口0的一部分。或者，该引脚(TX_D1_P)也可作为LVDS 6位TX差分输入总线(带内部LVDS端子)的一部分。  |

| D11                                       | I/O             | P0_D1/TX_D0_P                                                          | 数字数据端口P0/发射差分输入总线。这是双功能引脚。对于P0_D1，它充当12位双向并行CMOS电平数据端口0的一部分。或者，该引脚(TX_D0_P)也可作为LVDS 6位TX差分输入总线(带内部LVDS端子)的一部分。  |

| D12, F7, F9,<br>F11, G12, H7,<br>H10, K12 | I               | VSSD                                                                   | 数字地。将这些引脚直接连接至印刷电路板上的VSSA模拟地(一个接地层)。                                                                            |

| E1, F1                                    | I               | RX2B_P, RX2B_N                                                         | 接收通道2差分输入B。每个引脚都可作为单端输入或者相结合从而形成差分对。这些输入在3 GHz以上时性能会下降。将未使用的引脚接地。                                               |

| E2                                        | I               | VDDA1P3_RX_LO                                                          | 接收LO 1.3 V电源输入。                                                                                                 |

| E3                                        | I               | VDDA1P3_TX_LO_BUFFER                                                   | 1.3 V电源输入。                                                                                                      |

| E7                                        | I/O             | P0_D11/TX_D5_P                                                         | 数字数据端口P0/发射差分输入总线。这是双功能引脚。对于P0_D11，它充当12位双向并行CMOS电平数据端口0的一部分。或者，该引脚(TX_D5_P)也可作为LVDS 6位TX差分输入总线(带内部LVDS端子)的一部分。 |

| E8                                        | I/O             | P0_D8/TX_D4_N                                                          | 数字数据端口P0/发射差分输入总线。这是双功能引脚。对于P0_D8，它充当12位双向并行CMOS电平数据端口0的一部分。或者，该引脚(TX_D4_N)也可作为LVDS 6位TX差分输入总线(带内部LVDS端子)的一部分。  |

| E9                                        | I/O             | P0_D6/TX_D3_N                                                          | 数字数据端口P0/发射差分输入总线。这是双功能引脚。对于P0_D6，它充当12位双向并行CMOS电平数据端口0的一部分。或者，该引脚(TX_D3_N)也可作为LVDS 6位TX差分输入总线(带内部LVDS端子)的一部分。  |

| E10                                       | I/O             | P0_D4/TX_D2_N                                                          | 数字数据端口P0/发射差分输入总线。这是双功能引脚。对于P0_D4，它充当12位双向并行CMOS电平数据端口0的一部分。或者，该引脚(TX_D2_N)也可作为LVDS 6位TX差分输入总线(带内部LVDS端子)的一部分。  |

| E11                                       | I/O             | P0_D2/TX_D1_N                                                          | 数字数据端口P0/发射差分输入总线。这是双功能引脚。对于P0_D2，它充当12位双向并行CMOS电平数据端口0的一部分。或者，该引脚(TX_D1_N)也可作为LVDS 6位TX差分输入总线(带内部LVDS端子)的一部分。  |

| E12                                       | I/O             | P0_D0/TX_D0_N                                                          | 数字数据端口P0/发射差分输入总线。这是双功能引脚。对于P0_D0，它充当12位双向并行CMOS电平数据端口0的一部分。或者，该引脚(TX_D0_N)也可作为LVDS 6位TX差分输入总线(带内部LVDS端子)的一部分。  |

# AD9361

| 引脚编号     | 类型 <sup>1</sup> | 引脚名称                   | 说明                                                                                                              |

|----------|-----------------|------------------------|-----------------------------------------------------------------------------------------------------------------|

| F2       | I               | VDDA1P3_RX_VCO_LDO     | 接收VCO LDO 1.3 V电源输入。连接至E2。                                                                                      |

| F8       | I/O             | P0_D10/TX_D5_N         | 数字数据端口P0/发射差分输入总线。这是双功能引脚。对于P0_D10，它充当12位双向并行CMOS电平数据端口0的一部分。或者，该引脚(TX_D5_N)也可作为LVDS 6位TX差分输入总线(带内部LVDS端子)的一部分。 |

| F10, G10 | I               | FB_CLK_P, FB_CLK_N     | 反馈时钟。这些引脚接收作为TX数据时钟的FB_CLK信号。在CMOS模式中，以FB_CLK_P为输入，将FB_CLK_N接地。                                                 |

| F12      | I               | VDDD1P3_DIG            | 1.3 V数字电源输入。                                                                                                    |

| G1       | I               | RX_EXT_LO_IN           | 外部接收LO输入。若未使用此引脚，则将其接地。                                                                                         |

| G2       | O               | RX_VCO_LDO_OUT         | 接收VCO LDO输出。将该引脚直接连至G3，将一个1 μF旁路电容与一个1 Ω电阻串联接地。                                                                 |

| G3       | I               | VDDA1P1_RX_VCO         | 接收VCO电源输入。将该引脚只直接连至G2。                                                                                          |

| G5       | I               | EN_AGC                 | 用于自动增益控制(AGC)的手动控制输入。                                                                                           |

| G6       | I               | 使能                     | 使能控制输入。该引脚使器件在各种运行状态之间移动。                                                                                       |

| G7, G8   | O               | RX_FRAME_N, RX_FRAME_P | 接收数字数据帧输出信号。这些引脚发射RX_FRAME信号，用于指示RX输出数据是否有效。在CMOS模式下，以RX_FRAME_P为输出，使RX_FRAME_N保持断开状态。                          |

| G9, H9   | I               | TX_FRAME_P, TX_FRAME_N | 发射数字数据帧输入信号。这些引脚接收用于指示TX数据何时有效的TX_FRAME信号。在CMOS模式中，以TX_FRAME_P为输入，将TX_FRAME_N接地。                                |

| G11, H11 | O               | DATA_CLK_P, DATA_CLK_N | 接收数据时钟输出。这些引脚发射DATA_CLK信号，BBP用这些信号为RX数据提供时钟。在CMOS模式下，以DATA_CLK_P为输出，使DATA_CLK_N保持断开状态。                          |

| H1, J1   | I               | RX1B_P, RX1B_N         | 接收通道1差分输入B。另外，每个引脚均可用作单端输入。这些输入在3 GHz以上时性能会下降。将未使用的引脚接地。                                                        |

| H4       | I               | TXNRX                  | 使能状态机控制信号。该引脚控制数据端口总线方向。逻辑低电平选择RX方向，逻辑高电平选择TX方向。                                                                |

| H5       | I               | SYNC_IN                | 用于同步多个AD9361器件之间数字时钟的输入。若未使用此引脚，则将其接地。                                                                          |

| H8       | I/O             | P1_D11/RX_D5_P         | 数字数据端口P1/接收差分输出总线。这是双功能引脚。对于P1_D11，它充当12位双向并行CMOS电平数据端口1的一部分。或者，该引脚(RX_D5_P)也可作为LVDS 6位RX差分输出总线(带内部LVDS端子)的一部分。 |

| H12      | I               | VDD_INTERFACE          | 数字I/O引脚，1.2 V至2.5 V电源(LVDS模式下为1.8 V至2.5 V)。                                                                     |

| J3       | I               | VDDA1P3_RX_SYNTH       | 1.3 V电源输入。                                                                                                      |

| J4       | I               | SPI_DI                 | SPI串行数据输入。                                                                                                      |

| J5       | I               | SPI_CLK                | SPI时钟输入。                                                                                                        |

| J6       | O               | CLK_OUT                | 输出时钟。可将该引脚配置为输出缓冲版外部输入时钟DCXO，或者输出分频版内部ADC_CLK。                                                                  |

| J7       | I/O             | P1_D10/RX_D5_N         | 数字数据端口P1/接收差分输出总线。这是双功能引脚。对于P1_D10，它充当12位双向并行CMOS电平数据端口1的一部分。或者，该引脚(RX_D5_N)也可作为LVDS 6位RX差分输出总线(带内部LVDS端子)的一部分。 |

| J8       | I/O             | P1_D9/RX_D4_P          | 数字数据端口P1/接收差分输出总线。这是双功能引脚。对于P1_D9，它充当12位双向并行CMOS电平数据端口1的一部分。或者，该引脚(RX_D4_P)也可作为LVDS 6位RX差分输出总线(带内部LVDS端子)的一部分。  |

| J9       | I/O             | P1_D7/RX_D3_P          | 数字数据端口P1/接收差分输出总线。这是双功能引脚。对于P1_D7，它充当12位双向并行CMOS电平数据端口1的一部分。或者，该引脚(RX_D3_P)也可作为LVDS 6位RX差分输出总线(带内部LVDS端子)的一部分。  |

| J10      | I/O             | P1_D5/RX_D2_P          | 数字数据端口P1/接收差分输出总线。这是双功能引脚。对于P1_D5，它充当12位双向并行CMOS电平数据端口1的一部分。或者，该引脚(RX_D2_P)也可作为LVDS 6位RX差分输出总线(带内部LVDS端子)的一部分。  |

| 引脚编号     | 类型 <sup>1</sup> | 引脚名称             | 说明                                                                                                             |

|----------|-----------------|------------------|----------------------------------------------------------------------------------------------------------------|

| J11      | I/O             | P1_D3/RX_D1_P    | 数字数据端口P1/接收差分输出总线。这是双功能引脚。对于P1_D3，它充当12位双向并行CMOS电平数据端口1的一部分。或者，该引脚(RX_D1_P)也可作为LVDS 6位RX差分输出总线(带内部LVDS端子)的一部分。 |

| J12      | I/O             | P1_D1/RX_D0_P    | 数字数据端口P1/接收差分输出总线。这是双功能引脚。对于P1_D1，它充当12位双向并行CMOS电平数据端口1的一部分。或者，该引脚(RX_D0_P)也可作为LVDS 6位RX差分输出总线(带内部LVDS端子)的一部分。 |

| K1, L1   | I               | RX1C_P, RX1C_N   | 接收通道1差分输入C。另外，每个引脚均可用作单端输入。这些输入在3 GHz以上时性能会下降。将未使用的引脚接地。                                                       |

| K3       | I               | VDDA1P3_TX_SYNTH | 1.3 V电源输入。                                                                                                     |

| K4       | I               | VDDA1P3_BB       | 1.3 V电源输入。                                                                                                     |

| K5       | I               | RESETB           | 异步复位。逻辑低电平复位器件。                                                                                                |

| K6       | I               | SPI_ENB          | SPI使能输入。将该引脚设为逻辑低电平，以使能SPI总线。                                                                                  |

| K7       | I/O             | P1_D8/RX_D4_N    | 数字数据端口P1/接收差分输出总线。这是双功能引脚。对于P1_D8，它充当12位双向并行CMOS电平数据端口1的一部分。或者，该引脚(RX_D4_N)也可作为LVDS 6位RX差分输出总线(带内部LVDS端子)的一部分。 |

| K8       | I/O             | P1_D6/RX_D3_N    | 数字数据端口P1/接收差分输出总线。这是双功能引脚。对于P1_D6，它充当12位双向并行CMOS电平数据端口1的一部分。或者，该引脚(RX_D3_N)也可作为LVDS 6位RX差分输出总线(带内部LVDS端子)的一部分。 |

| K9       | I/O             | P1_D4/RX_D2_N    | 数字数据端口P1/接收差分输出总线。这是双功能引脚。对于P1_D4，它充当12位双向并行CMOS电平数据端口1的一部分。或者，该引脚(RX_D2_N)也可作为LVDS 6位RX差分输出总线(带内部LVDS端子)的一部分。 |

| K10      | I/O             | P1_D2/RX_D1_N    | 数字数据端口P1/接收差分输出总线。这是双功能引脚。对于P1_D2，它充当12位双向并行CMOS电平数据端口1的一部分。或者，该引脚(RX_D1_N)也可作为LVDS 6位RX差分输出总线(带内部LVDS端子)的一部分。 |

| K11      | I/O             | P1_D0/RX_D0_N    | 数字数据端口P1/接收差分输出总线。这是双功能引脚。对于P1_D0，它充当12位双向并行CMOS电平数据端口1的一部分。或者，该引脚(RX_D0_N)也可作为LVDS 6位RX差分输出总线(带内部LVDS端子)的一部分。 |

| L4       | I               | RBIAS            | 偏置输入参考。通过一个14.3 kΩ (1%容差)电阻将此引脚接地。                                                                             |

| L5       | I               | AUXADC           | 辅助ADC输入。若未使用此引脚，则将其接地。                                                                                         |

| L6       | O               | SPI_DO           | 4线模式的SPI串行数据输出，或者3线模式下的高Z。                                                                                     |

| M1, M2   | I               | RX1A_P, RX1A_N   | 接收通道1差分输入A。另外，每个引脚均可用作单端输入。将未使用的引脚接地。                                                                          |

| M5       | I               | TX_MON1          | 发射通道1功率监控输入。未使用此引脚时，将其接地。                                                                                      |

| M7, M8   | O               | TX1A_P, TX1A_N   | 发射通道1差分输出A。将未使用的引脚连接至1.3 V。                                                                                    |

| M9, M10  | O               | TX1B_P, TX1B_N   | 发射通道1差分输出B。将未使用的引脚连接至1.3 V。                                                                                    |

| M11, M12 | I               | XTALP, XTALN     | 参考频率晶振连接。使用晶振时，将其连接于这两个引脚之间。使用外部时钟源时，将其连接至XTALN，使XTALP保持断开。                                                    |

<sup>1</sup> I为输入，O为输出，I/O为输入/输出，NC为未连接。

## 典型性能参数

### 800 MHz频段

图3.RX噪声系数与RF频率的关系

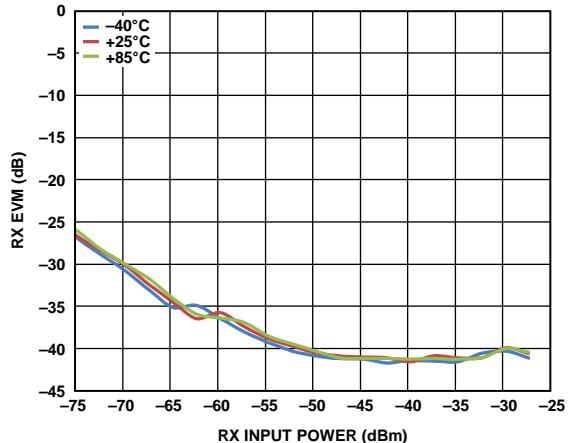

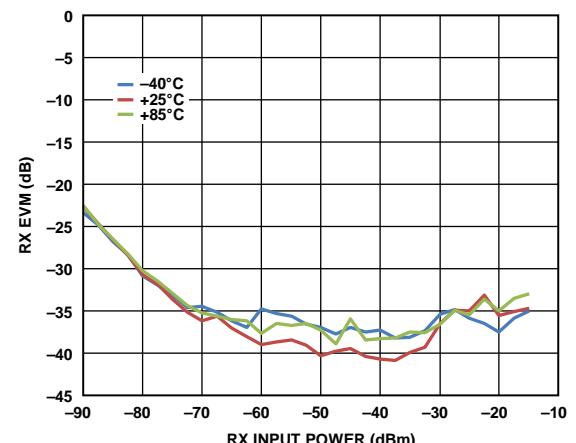

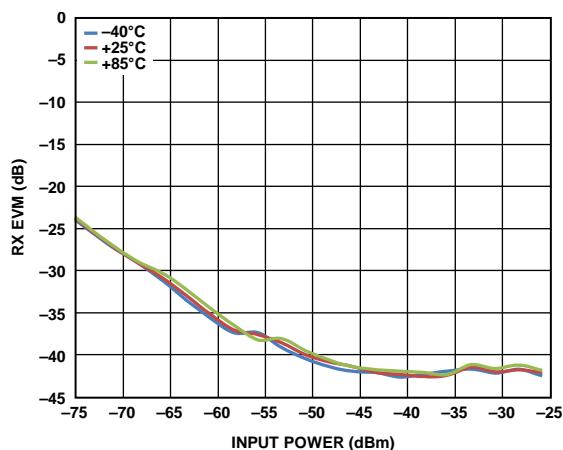

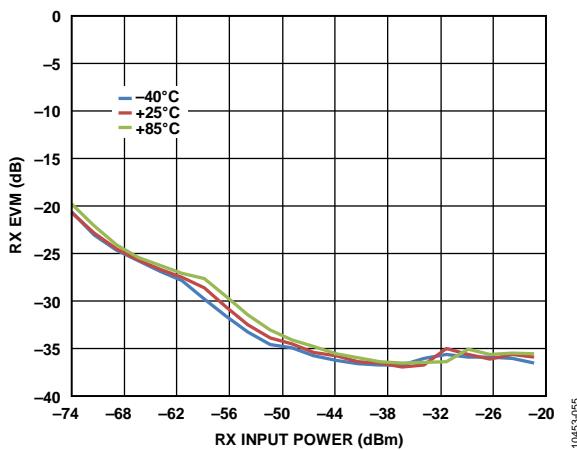

图6.RX EVM与RX输入功率的关系

(64 QAM LTE 10 MHz模式, 19.2 MHz REF\_CLK)

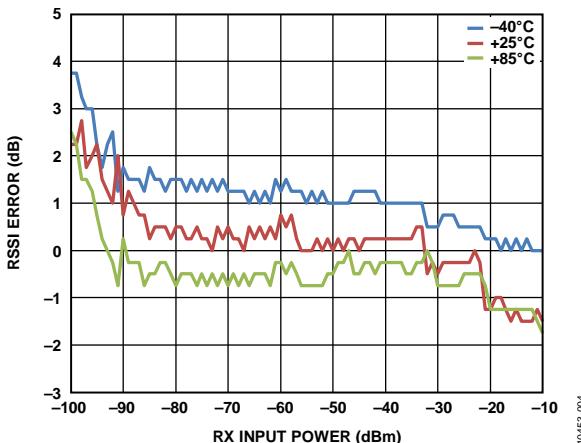

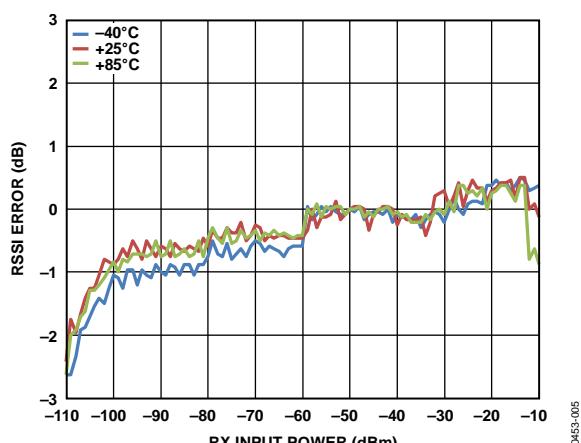

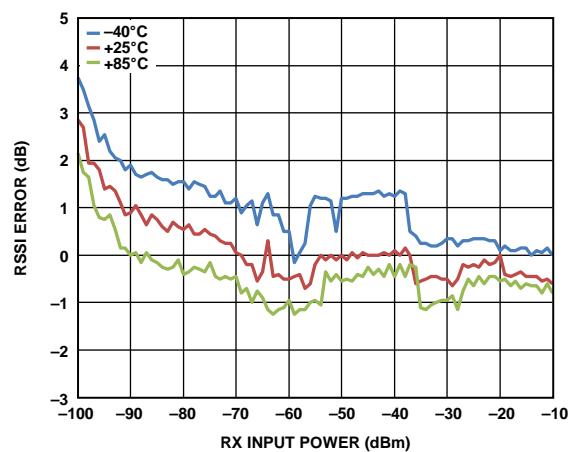

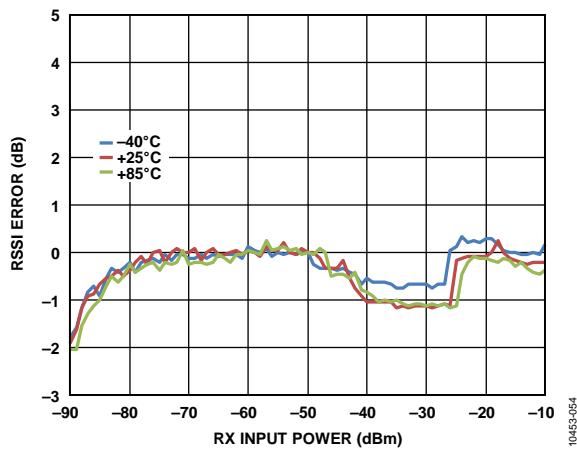

图4.RSSI误差与RX输入功率的关系

(LTE 10 MHz调制, 折合至-50 dBm输入功率, 800 MHz)

图7.RX EVM与RX输入功率的关系

(GSM模式, 30.72 MHz REF\_CLK, RF频率合成器内部加倍)

图5.RSSI误差与RX输入功率的关系

(Edge调制, 折合至-50 dBm输入功率, 800 MHz)

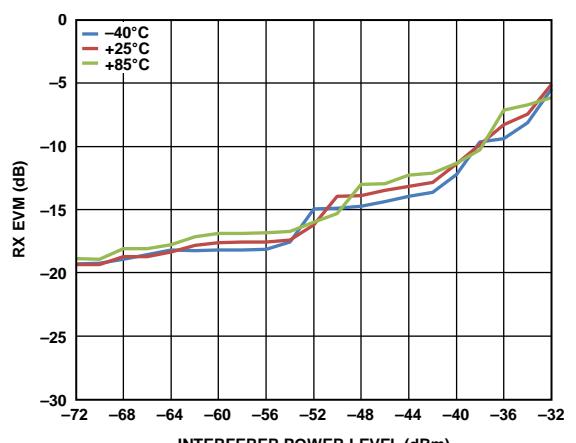

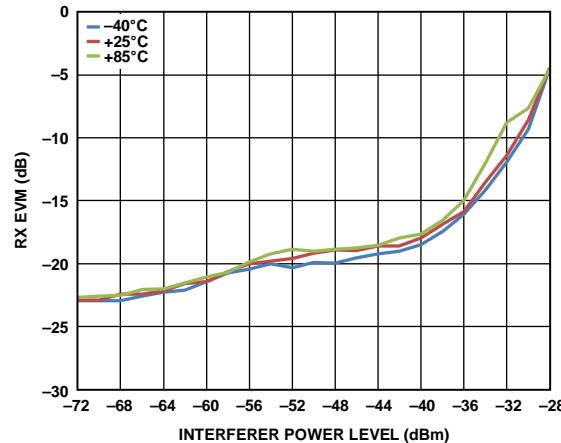

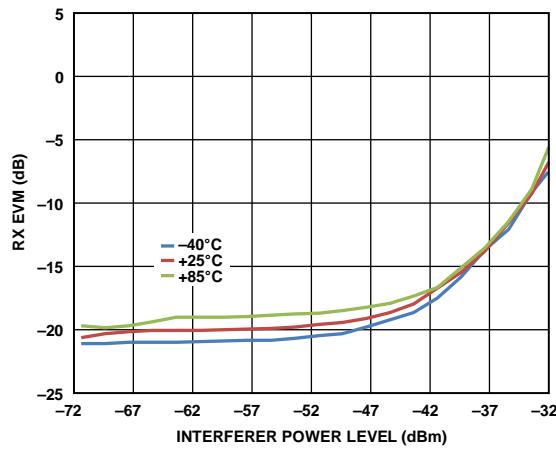

图8.RX EVM与干扰功率水平的关系

(LTE 10 MHz目标信号, PIN = -82 dBm,

5 MHz OFDM阻塞, 7.5 MHz失调)

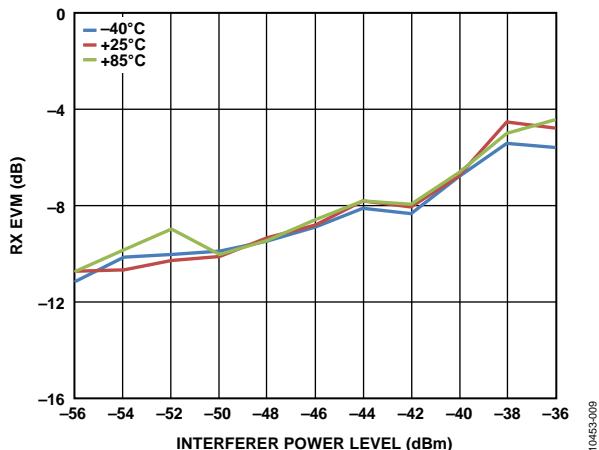

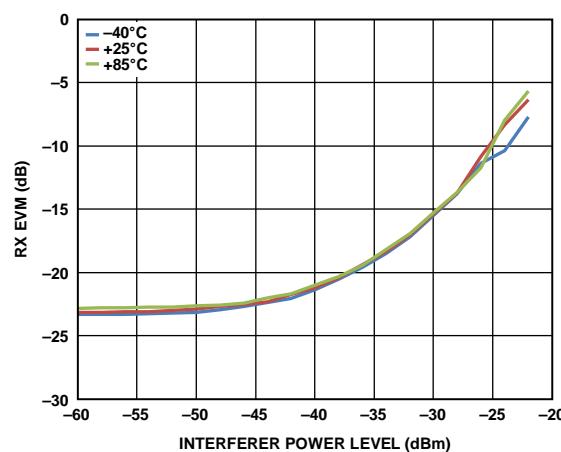

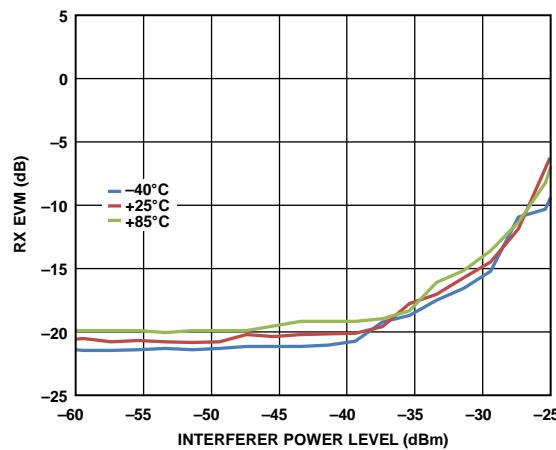

图9.RX EVM与干扰功率水平的关系

(LTE 10 MHz目标信号, PIN = -90 dBm, 5 MHz OFDM阻塞, 17.5 MHz失调)

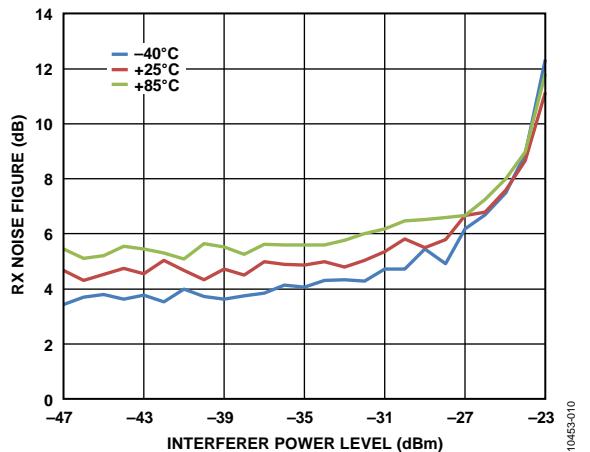

图10.RX噪声系数与干扰功率水平的关系

(Edge目标信号, PIN = -90 dBm, CW阻塞、3 MHz失调, 增益指数 = 64)

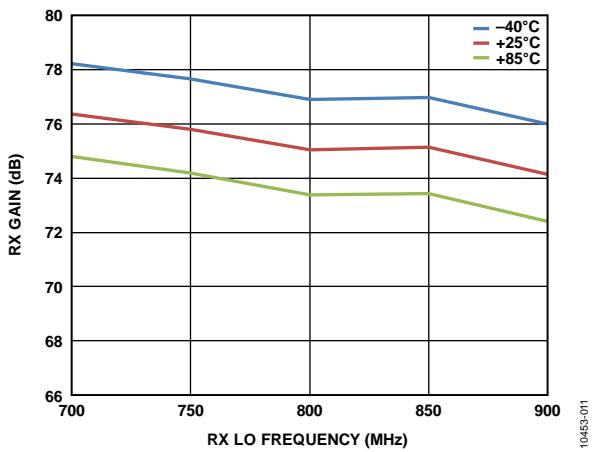

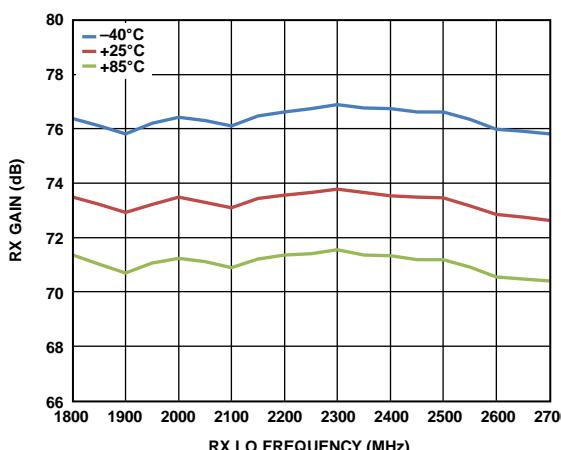

图11.RX增益与RX LO频率的关系(增益指数 = 76, 最大设置)

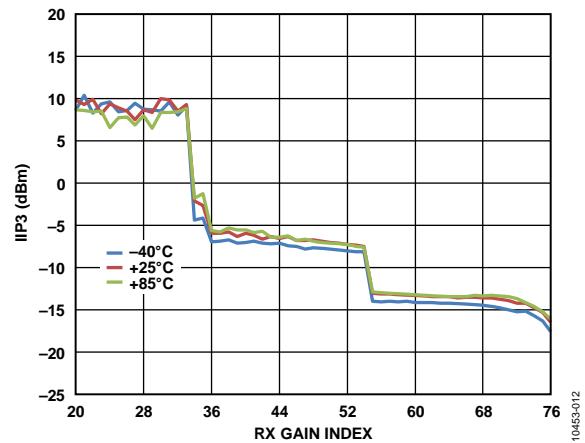

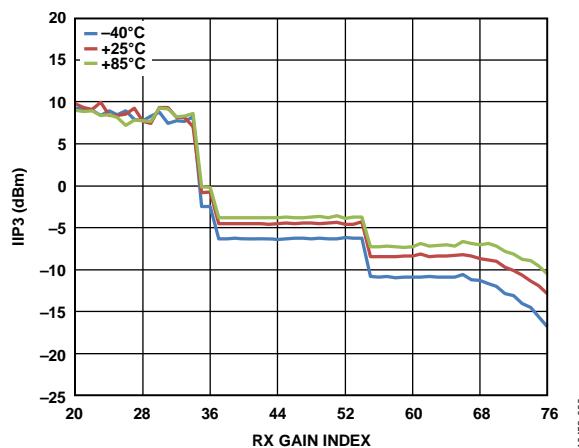

图12.三阶输入交调截点(IIP3)与增益指数的关系

(f1 = 1.45 MHz, f2 = 2.89 MHz, GSM模式)

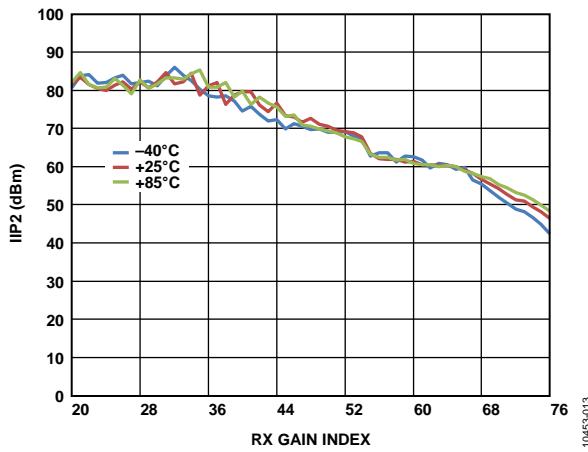

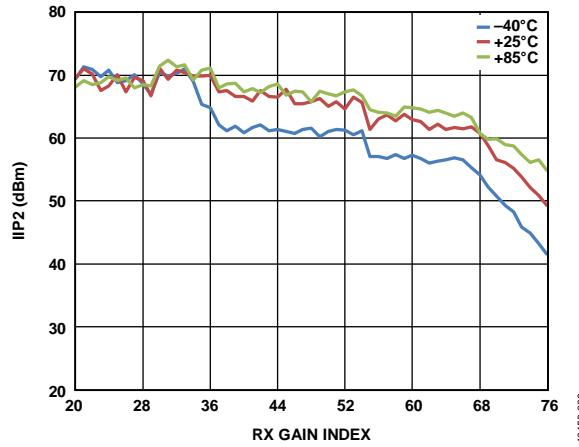

图13.二阶输入交调截点(IIP2)与增益指数的关系

(f1 = 2.00 MHz, f2 = 2.01 MHz, GSM模式)

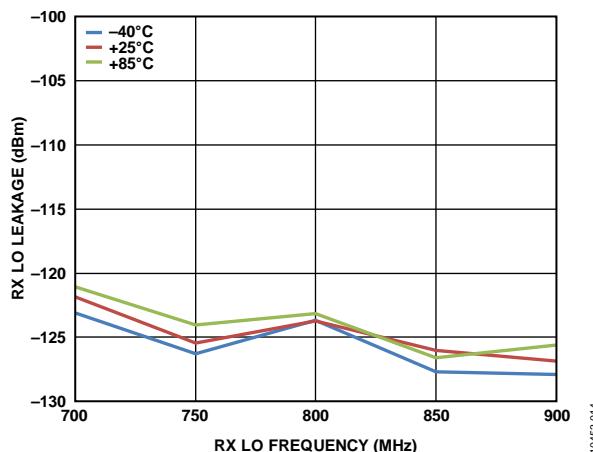

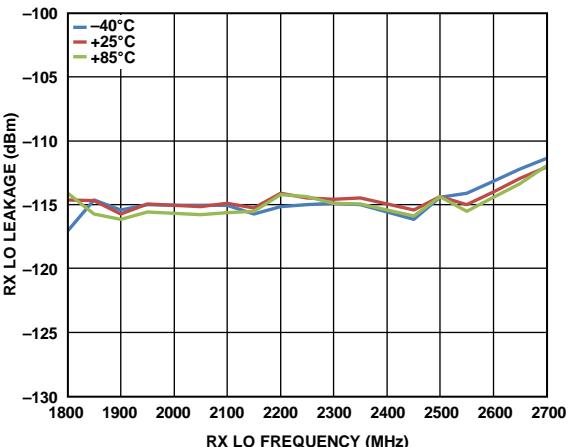

图14.RX本振(LO)泄漏与RX LO频率的关系

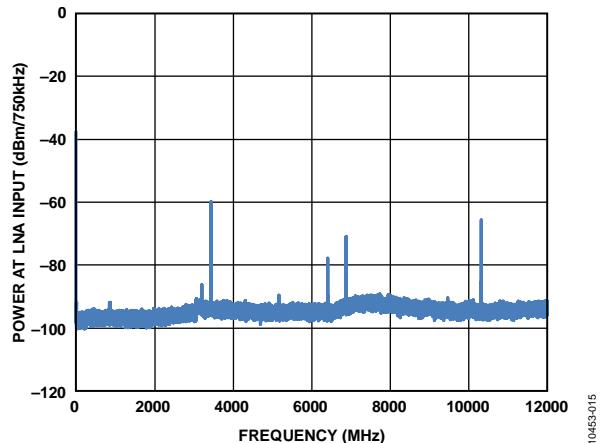

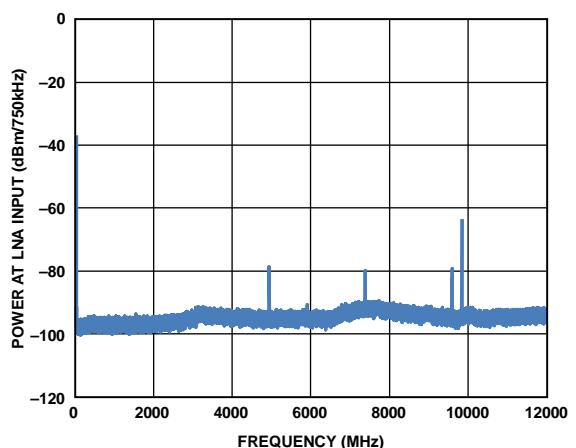

图15.LNA输入端的RX发射(直流至12 GHz,  $f_{LO_RX} = 800$  MHz,

$LTE 10$  MHz,  $f_{LO_TX} = 860$  MHz)

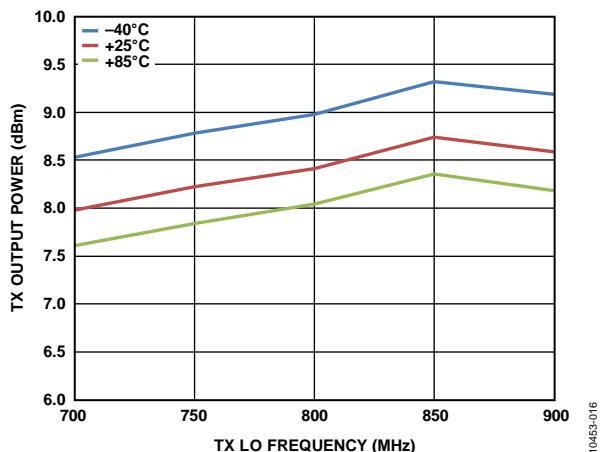

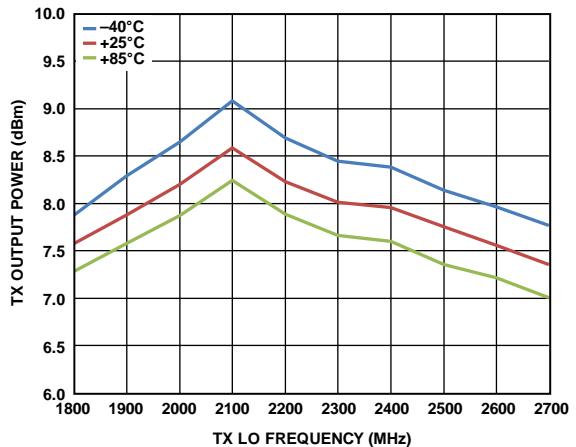

图16.TX输出功率与TX LO频率的关系(衰减设置 = 0 dB, 单音输出)

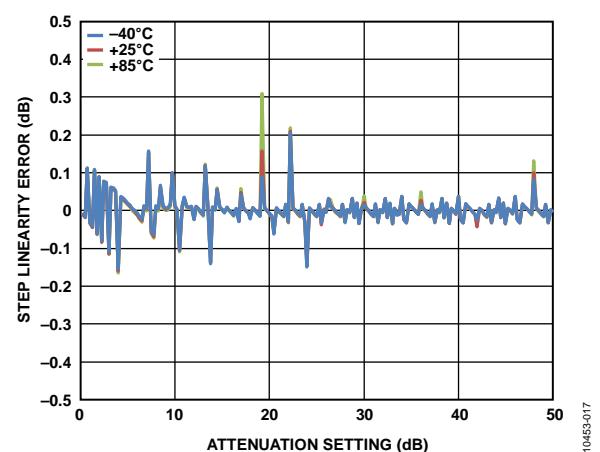

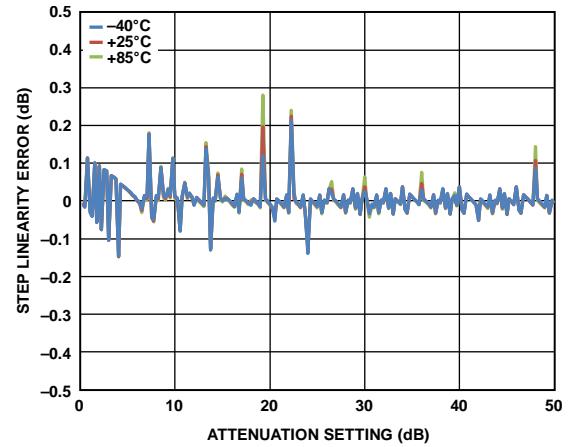

图17.TX功率控制线性度误差与衰减设置的关系

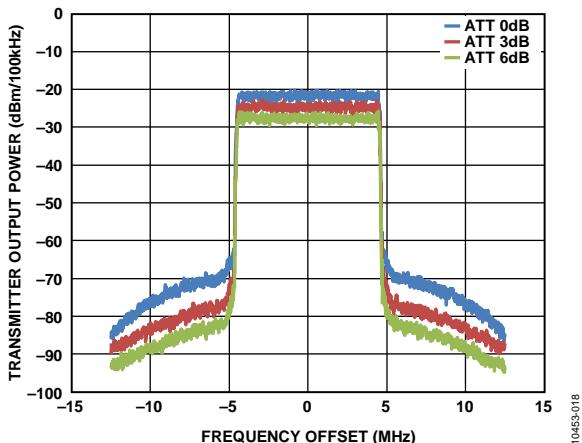

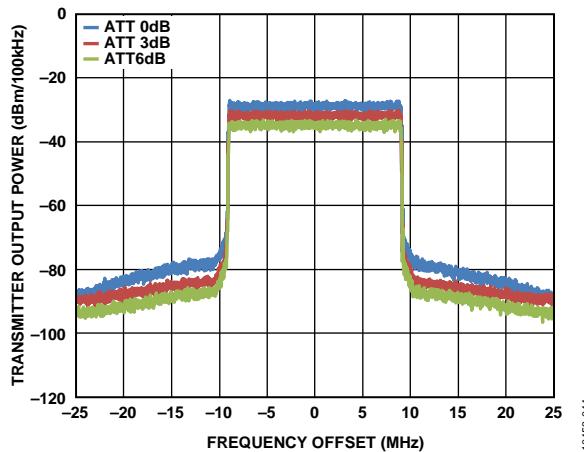

图18.TX频谱与相对载波频率的频率失调的关系

( $f_{LO_TX} = 800$  MHz, LTE 10 MHz下行链路, 展示的是数字衰减变化)

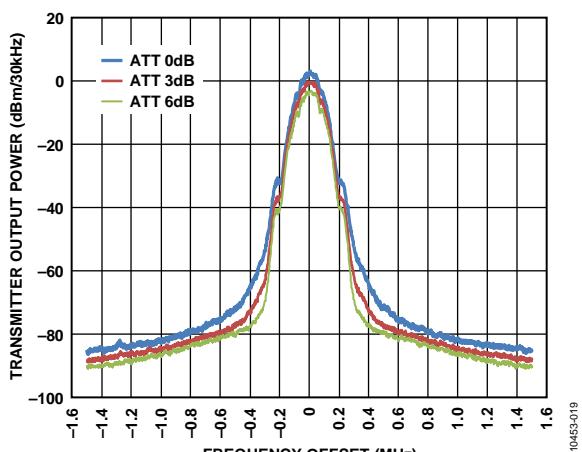

图19.TX频谱与相对载波频率的频率失调的关系

( $f_{LO_TX} = 800$  MHz, GSM 下行链路, 展示的是数字衰减变化, 3 MHz范围)

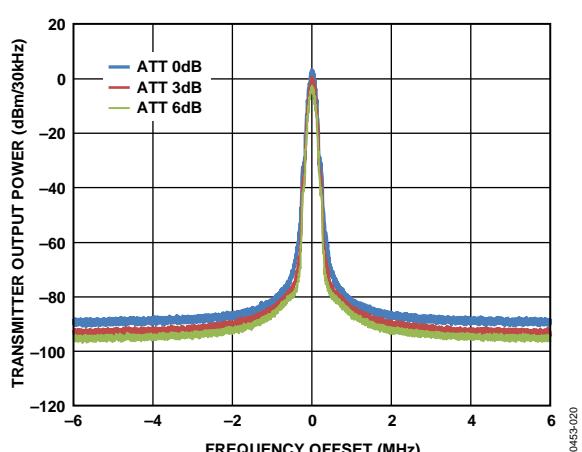

图20.TX频谱与相对载波频率的频率失调的关系

( $f_{LO_TX} = 800$  MHz, GSM 下行链路, 展示的是数字衰减变化, 12 MHz范围)

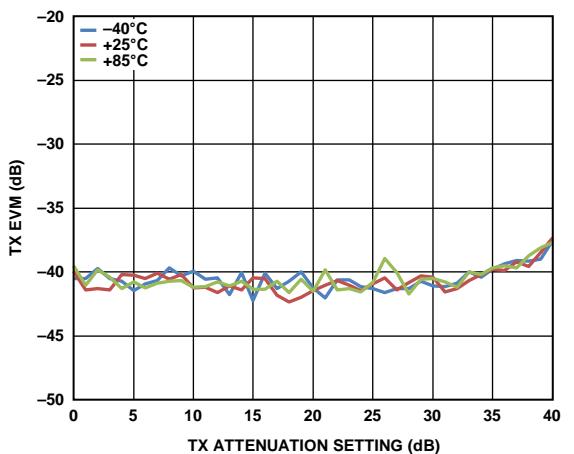

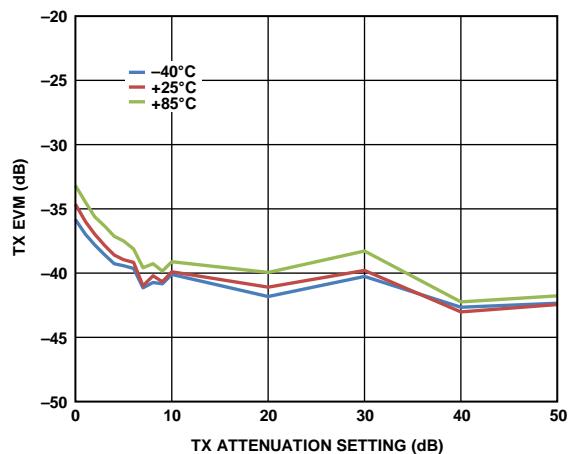

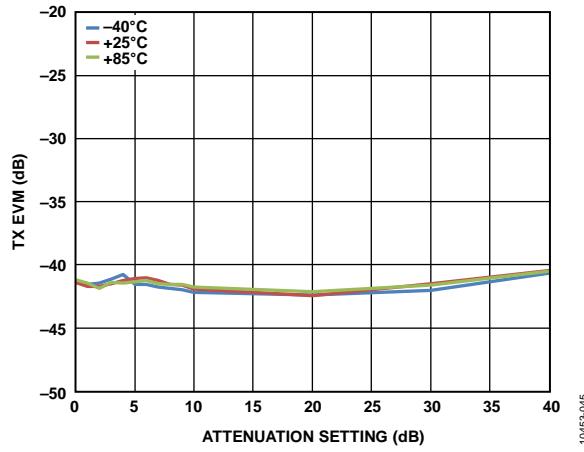

图21.TX EVM与TX衰减设置的关系( $f_{LO,TX} = 800$  MHz,

LTE 10 MHz, 64 QAM调制, 19.2 MHz REF\_CLK)

图22.TX EVM与TX衰减设置的关系( $f_{LO,TX} = 800$  MHz,

GSM调制, 30.72 MHz REF\_CLK, RF频率合成器内部加倍)

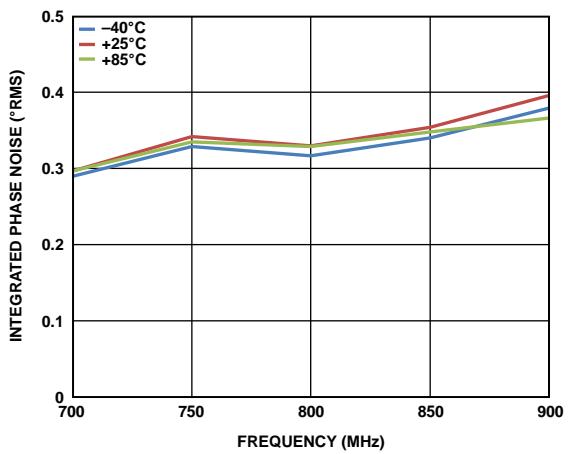

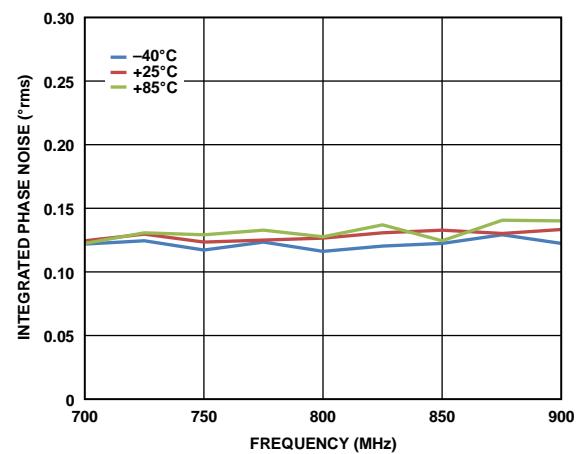

图23.集成TX LO相位噪声与频率的关系(19.2 MHz REF\_CLK)

图24.集成TX LO相位噪声与频率的关系

(30.72 MHz REF\_CLK, RF频率合成器内部加倍)

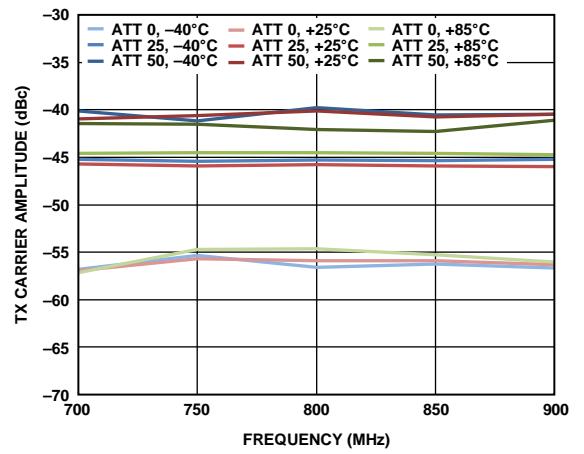

图25.TX载波抑制与频率的关系

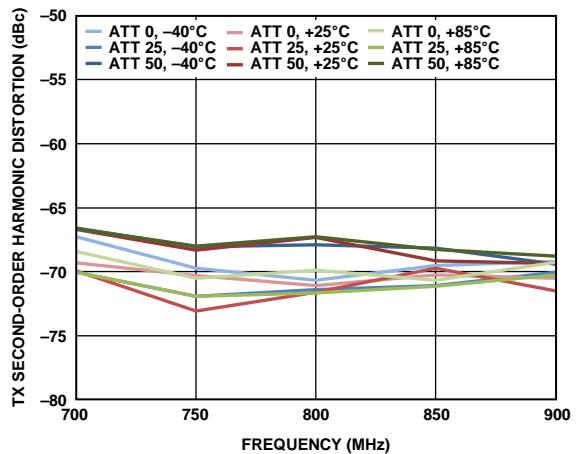

图26.TX二次谐波失真(HD2)与频率的关系

图27.TX三次谐波失真(HD3)与频率的关系

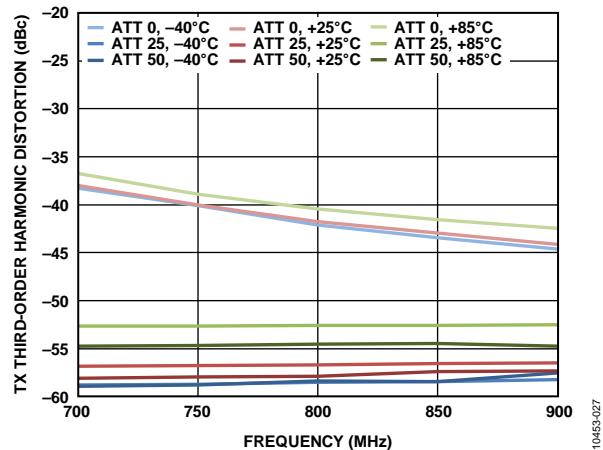

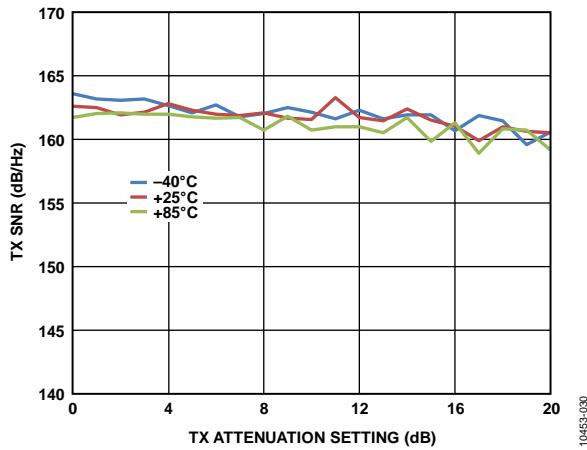

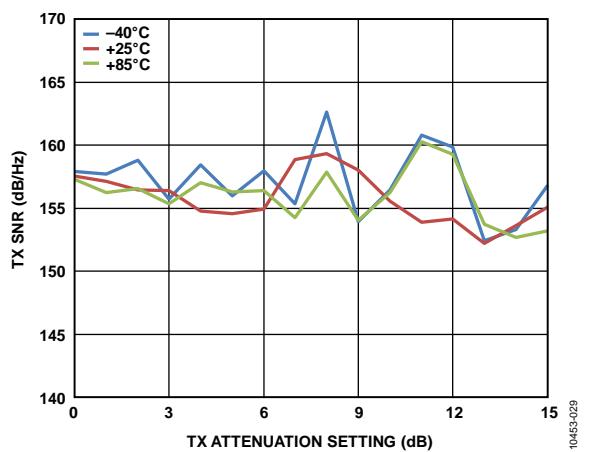

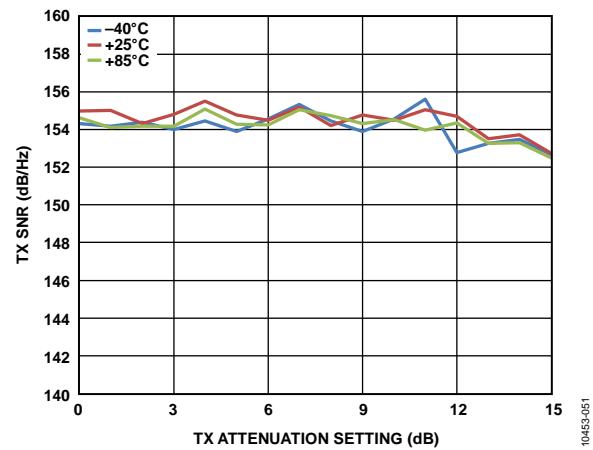

图30.TX信噪比(SNR)与TX衰减设置的关系

(GSM目标信号, 噪声于20 MHz失调条件下测量)

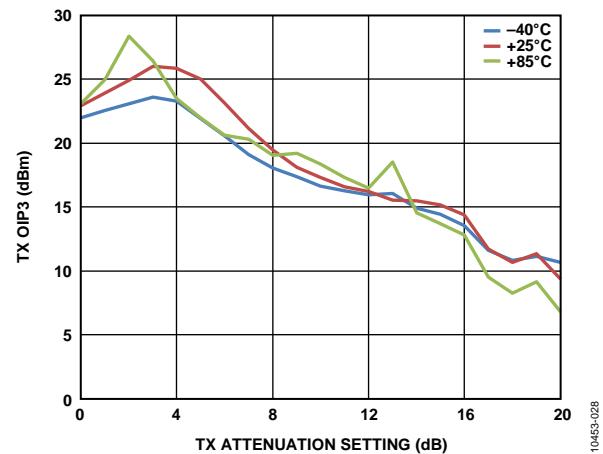

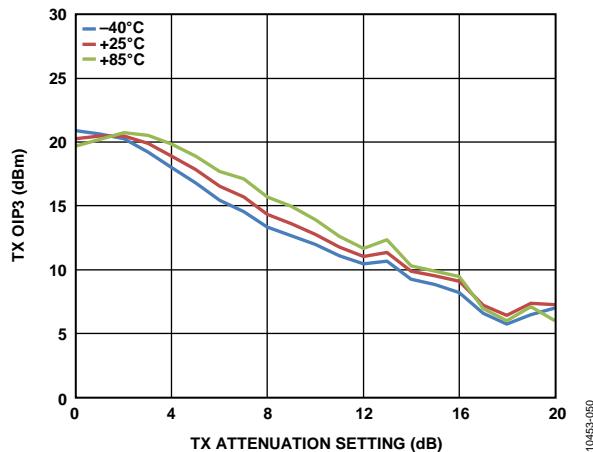

图28.TX三阶输出交调截点(OIP3)与TX衰减设置的关系

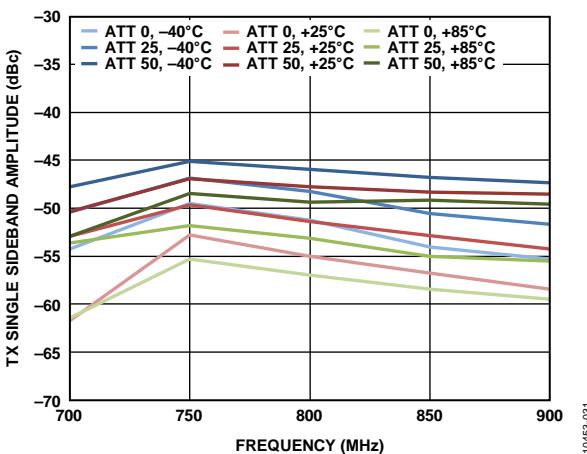

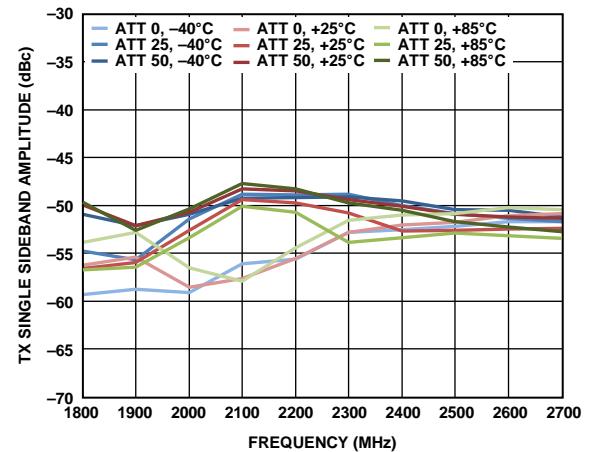

图31.TX单边带(SSB)抑制与频率的关系

(1.5375 MHz失调)

图29.TX信噪比(SNR)与TX衰减设置的关系

(LTE 10 MHz目标信号, 噪声于90 MHz失调条件下测量)

## 2.4 GHz频段

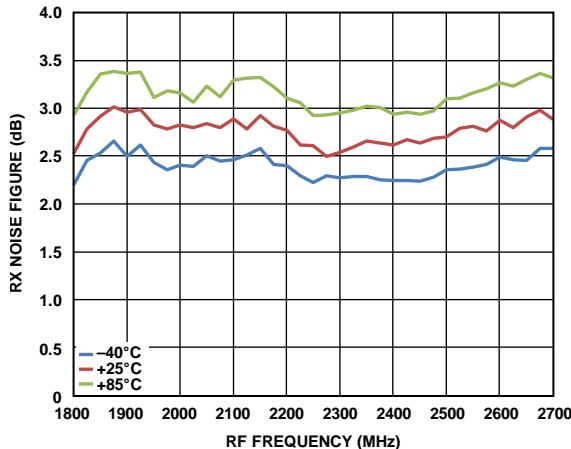

图32.RX噪声系数与RF频率的关系

10453-032

图33.RSSI误差与RX输入功率的关系

(折合至-50 dBm输入功率, 2.4 GHz)

10453-033

图34.RX EVM与输入功率的关系

(64 QAM LTE 20 MHz模式, 40 MHz REF\_CLK)

10453-034

图35.RX EVM与干扰功率水平的关系(LTE 20 MHz目标信号,

$P_{IN} = -75 \text{ dBm}$ , LTE 20 MHz阻塞, 20 MHz失调)

10453-035

图36.RX EVM与干扰功率水平的关系(LTE 20 MHz目标信号,

$P_{IN} = -75 \text{ dBm}$ , LTE 20 MHz阻塞, 40 MHz失调)

10453-036

图37.RX增益与RX LO频率的关系(增益指数 = 76, 最大设置)

10453-037

# AD9361

图38.三阶输入交调截点(IIP3)与增益指数的关系

( $f_1 = 30 \text{ MHz}$ ,  $f_2 = 61 \text{ MHz}$ )

图39.二阶输入交调截点(IIP2)与增益指数的关系

( $f_1 = 60 \text{ MHz}$ ,  $f_2 = 61 \text{ MHz}$ )

图40.RX本振(LO)泄漏与RX LO频率的关系

图41.LNA输入端的RX发射(直流至12 GHz,  $f_{LO\_RX} = 2.4 \text{ GHz}$ ,

LTE 20 MHz,  $f_{LO\_TX} = 2.46 \text{ GHz}$ )

图42.TX输出功率与TX LO频率的关系(衰减设置 = 0 dB, 单音输出)

图43.TX功率控制线性度误差与衰减设置的关系

图44.TX频谱与相对载波频率于的频率失调的关系

( $f_{LO\_TX} = 2.3$  GHz, LTE 20 MHz下行链路, 展示的是数字衰减变化)

图45.TX EVM与发射器衰减设置的关系

(40 MHz REF\_CLK, LTE 20 MHz, 64 QAM调制)

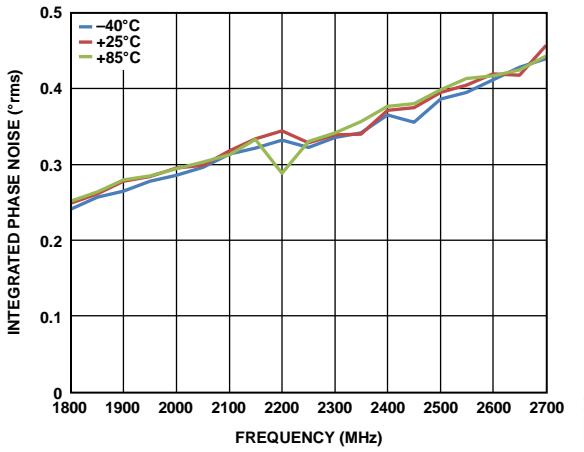

图46.集成TX LO相位噪声与频率的关系(40 MHz REF\_CLK)

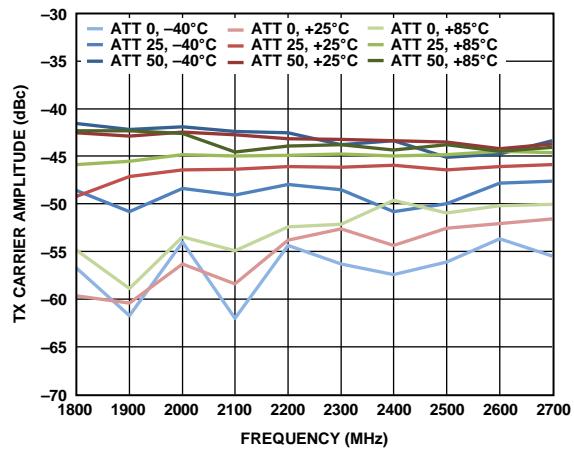

图47.TX载波抑制与频率的关系

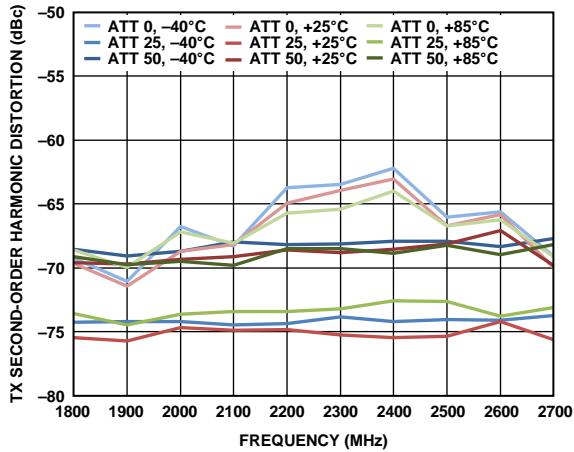

图48.TX二次谐波失真(HD2)与频率的关系

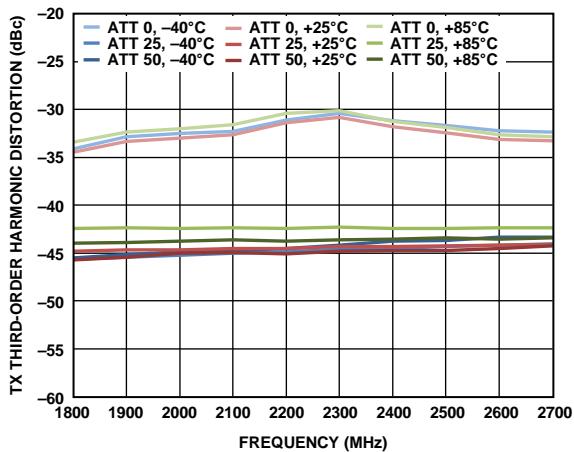

图49.TX三次谐波失真(HD3)与频率的关系

# AD9361

图50.TX三阶输出交调截点(OIP3)与TX衰减设置的关系

图52.TX单边带(SSB)抑制与频率的关系(3.075 MHz失调)

图51.TX信噪比(SNR)与TX衰减设置的关系

(LTE 20 MHz目标信号, 噪声于90 MHz失调条件下测量)

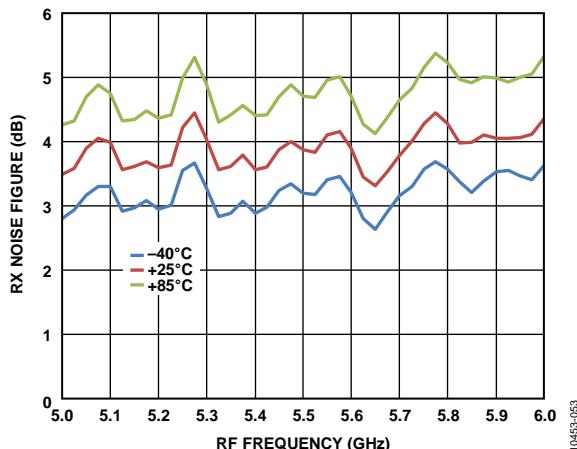

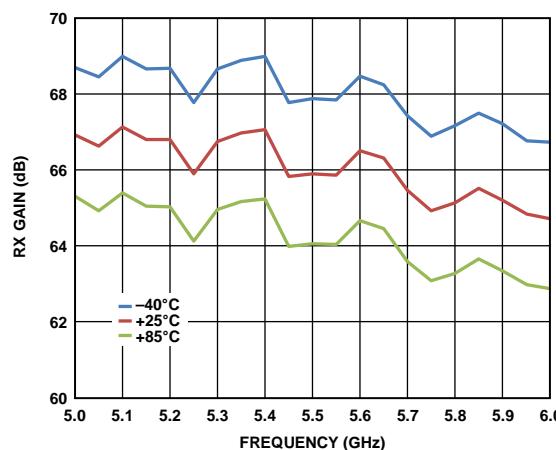

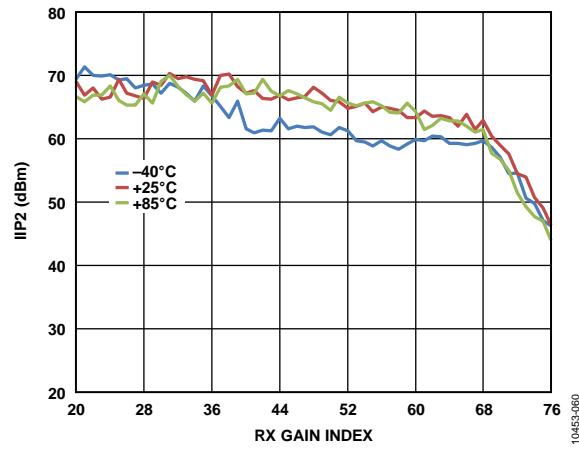

## 5.5 GHz频段

图53.RX噪声系数与RF频率的关系

图56.RX EVM与干扰功率水平的关系(WiMAX 40 MHz目标信号,

$P_{IN} = -74 \text{ dBm}$ , WiMAX 40 MHz阻塞, 40 MHz失调)

图54.RSSI误差与RX输入功率的关系(折合至-50 dBm输入功率, 5.8 GHz)

图57.RX EVM与干扰功率水平的关系(WiMAX 40 MHz目标信号,

$P_{IN} = -74 \text{ dBm}$ , WiMAX 40 MHz阻塞, 80 MHz失调)图55.RX EVM与RX输入功率的关系(64 QAM WiMAX 40 MHz模式,

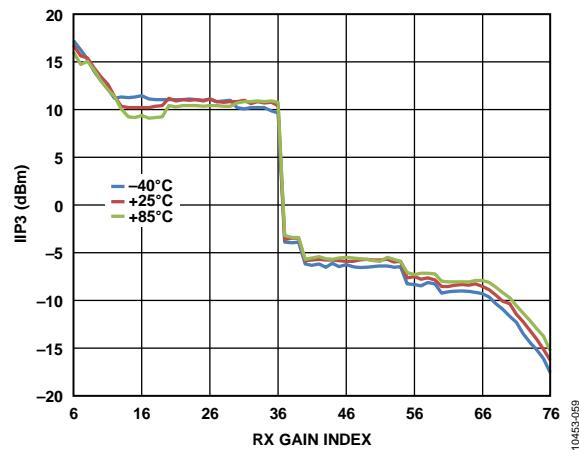

40 MHz REF\_CLK, RF频率合成器内部加倍)

图58.RX增益与频率的关系(增益指数 = 76, 最大设置)

图59.三阶输入交调截点(IIP3)与增益指数的关系

( $f_1 = 50 \text{ MHz}$ ,  $f_2 = 101 \text{ MHz}$ )

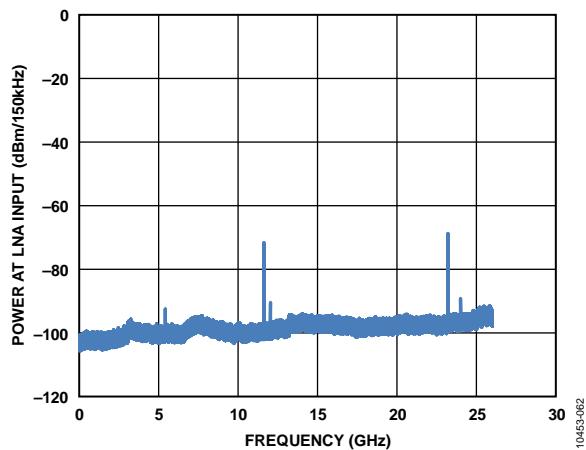

图62.LNA输入端的RX发射(直流至26 GHz,

$f_{LO\_RX} = 5.8 \text{ GHz}$ , WiMAX 40 MHz)

图60.二阶输入交调截点(IIP2)与增益指数的关系

( $f_1 = 70 \text{ MHz}$ ,  $f_2 = 71 \text{ MHz}$ )

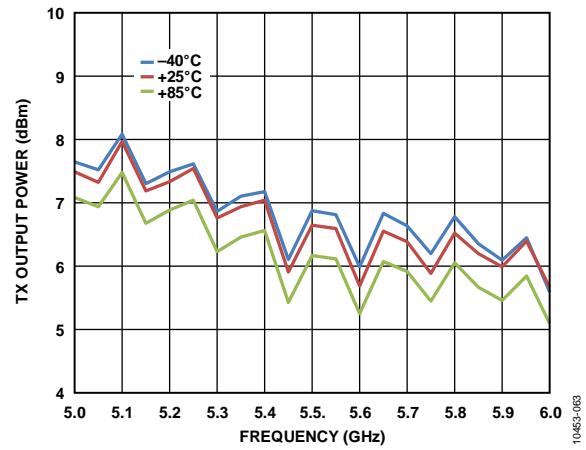

图63.TX输出功率与频率的关系(衰减设置 = 0 dB, 单音)

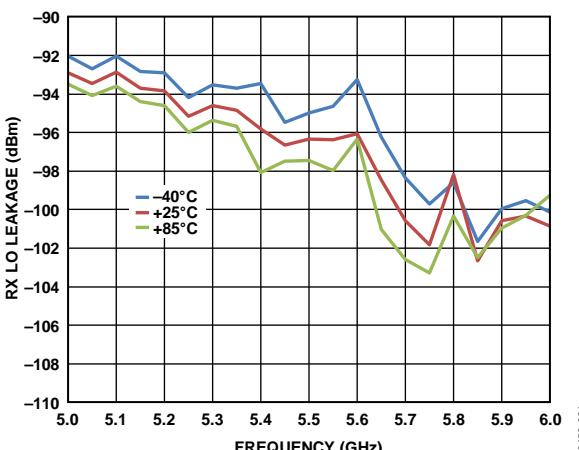

图61.RX本振(LO)泄漏与频率的关系

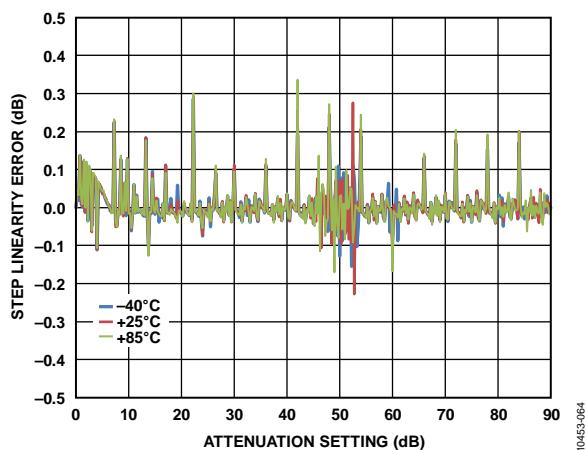

图64.TX功率控制线性度误差与衰减设置的关系

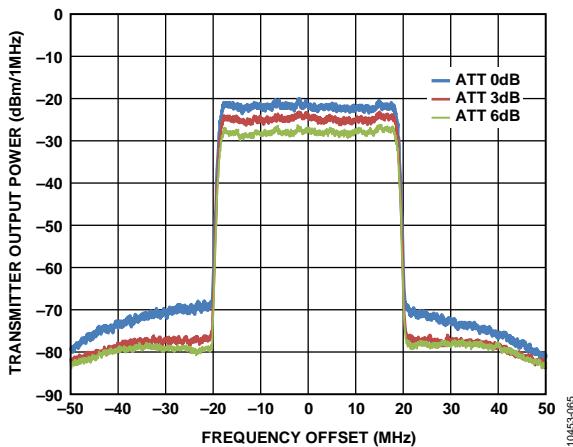

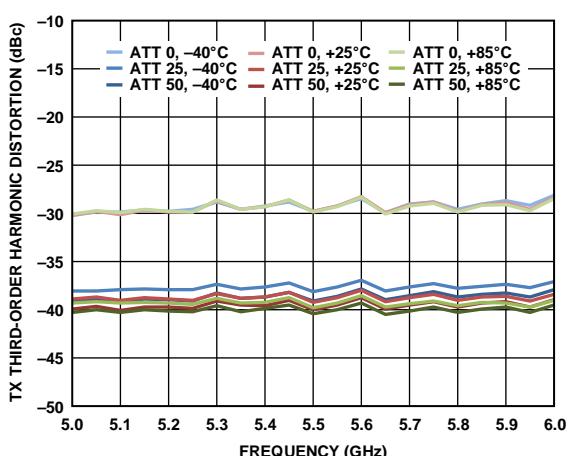

图65.TX频谱与相对载波频率于的频率失调的关系

( $f_{LO\_TX} = 5.8 \text{ GHz}$ , WiMAX 40 MHz下行链路, 展示的是数字衰减变化)

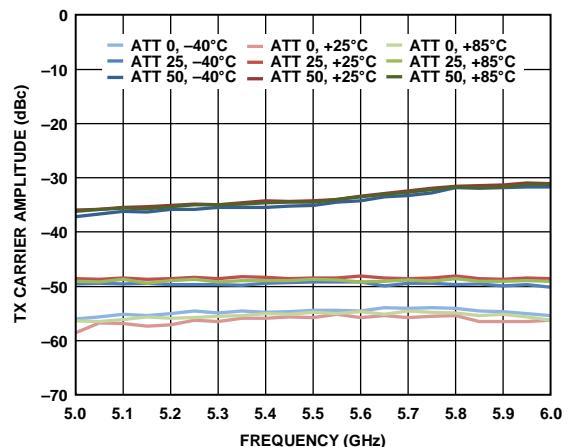

图68.TX载波抑制与频率的关系

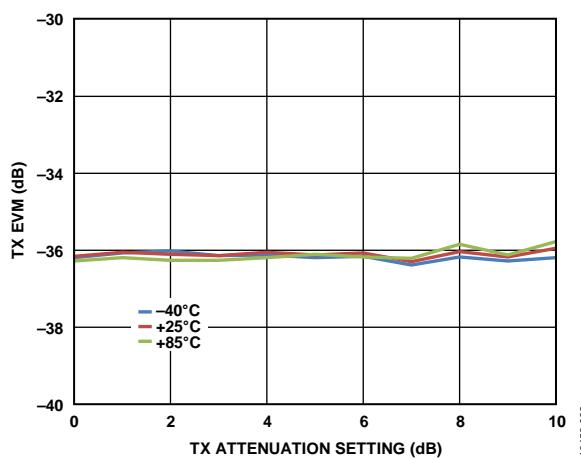

图66.TX EVM与TX衰减设置的关系(WiMAX 40 MHz, 64 QAM调制,

$f_{LO\_TX} = 5.495 \text{ GHz}$ , 40 MHz REF\_CLK, RF频率合成器内部加倍)

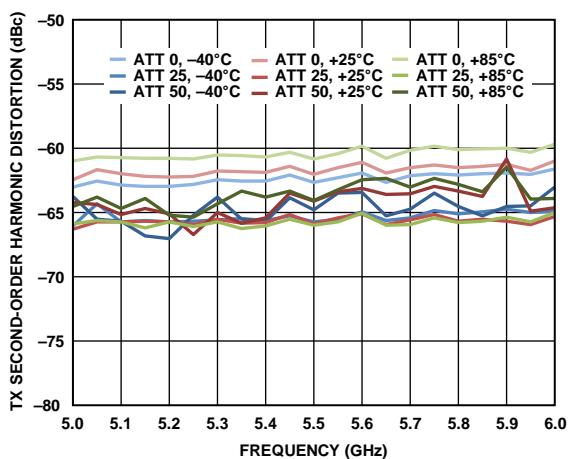

图69.TX二次谐波失真(HD2)与频率的关系

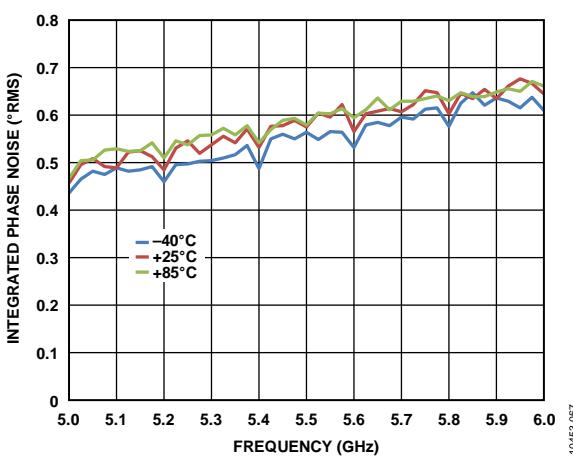

图67.集成TX LO相位噪声与频率的关系

(40 MHz REF\_CLK, RF频率合成器内部加倍)

图70.TX三次谐波失真(HD3)与频率的关系

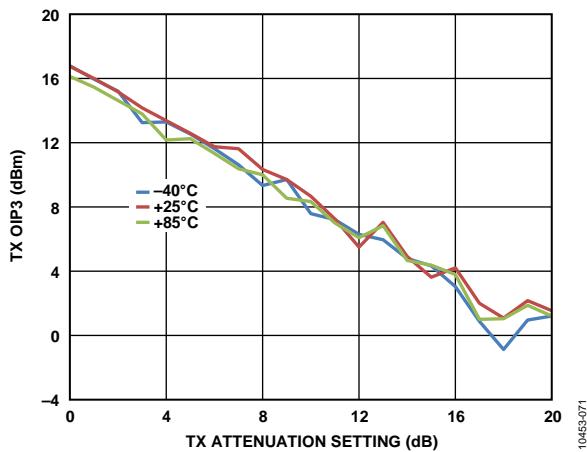

图71.TX三阶输出交调截点(OIP3)与TX衰减设置的关系

( $f_{LO\_TX} = 5.8 \text{ GHz}$ )

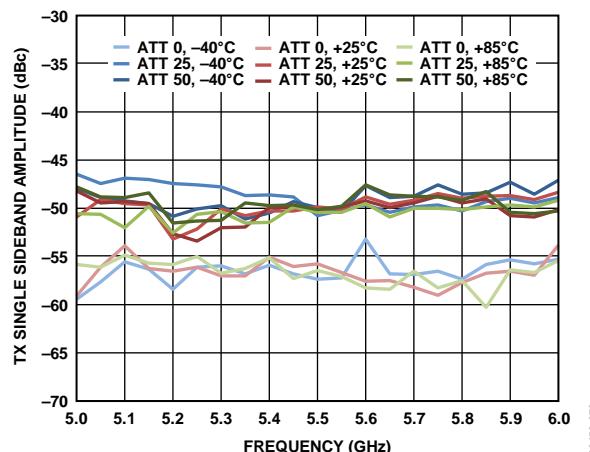

图73.TX单边带(SSB)抑制与频率的关系(7 MHz失调)

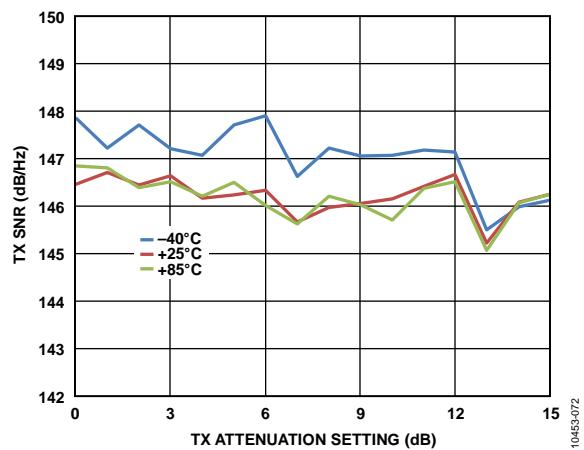

图72.TX信噪比(SNR)与TX衰减设置的关系

(WiMAX 40 MHz目标信号, 噪声于90 MHz失调条件下测量,

$f_{LO\_TX} = 5.745 \text{ GHz}$ )

# 工作原理

## 一般特性

[AD9361](#)是一款高集成度的射频(RF)收发器，能够配置用于广泛应用，在单个器件中集成了提供所有收发器功能的所有必要RF、混合信号和数字模块。可编程能力使这款宽带收发器可以适用于多种通信标准，包括频分双工(FDD)和时分双工(TDD)系统。此外，这种可编程能力还允许通过单通道12位并行数据端口、双通道12位并行数据端口或12位低电压差分信令(LVDS)接口，与各种基带处理器(BBP)相连接。

[AD9361](#)还提供了自我校准和自动增益控制(AGC)系统，可以在多种温度和输入信号条件下维持高性能水平。另外，器件还包括几种测试模式，允许系统设计师插入测试音，创建内部回送模式，以便用于在原型制作过程中对设计进行调试，并针对具体应用优化无线电配置。

## 接收器

接收器部分含有所有必要模块，用于接收RF信号并将其转换成可供BBP使用的数字数据。有两个独立控制的通道，可以接收来自不同源的信号，使器件可以用于多输入、多输出(MIMO)系统，同时还可共享一个通用频率合成器。

每个通道都有三个输入，可以多路复用至信号链，使[AD9361](#)可以用于搭载多个天线输入的分集系统。接收器是一个直接变频系统，含有一个低噪声放大器(LNA)，其后是匹配相内(I)和正交(Q)放大器、混频器和频带整形滤波器，该滤波器可以将接收到的信号下变频为基带，以便进行数字化。外部LNA也可连接至该器件，给设计师带来了极大的灵活性，使其可以针对具体应用定制接收器前端。

依据预编程增益指数映射，可实现增益控制，该映射将增益分配于各模块之间，从而实现各电平下的性能优化。这可以通过在快速或慢速模式下使能内部AGC来实现，也可通过手动增益控制来实现，使BBP可以根据需要调整增益。此外，各个通道还拥有独立的RSSI测量功能、直流失调跟踪功能和进行自我校准的所有必要电路。

接收器包括12位、 $\Sigma\Delta$  ADC和可调采样速率，可以从收到的信号产生数据流。数字化信号可以通过一系列抽取滤波器和一个完全可编程的128抽头FIR滤波器(带有额外的抽取设置)进一步调理。各个数字滤波器模块的采样速率可以通过更改抽取系数来进行调整，从而产生需要的输出数据速率。

## 发射器

发射器部分含有两个相同的、独立控制的通道，提供了所有必要的数字处理、混合信号和RF模块，可以实现一个直接变频系统，同时共用一个通用型频率合成器。从BBP收到的数字数据通过一个不带插值选项的完全可编程128抽头FIR滤波器。FIR输出被发送到一系列插值滤波器，在输出到达DAC之前，提供额外的滤波和数据速率插值处理。每个12位DAC都拥有可调的采样速率。I和Q通道都馈入RF模块以进行上变频。

当转换为基带模拟信号时，I和Q信号将进行滤波，以移除采样伪像，然后馈入上变频混频器。这里，I和Q信号将重新组合起来，并在载波频率下进行调制，以便传输到输出级。组合信号还会通过模拟滤波器，由它们提供额外的频带整形处理，然后再将信号传输至输出放大器。每个发射通道都提供了较宽的细粒度衰减调整范围，以帮助设计师优化信噪比(SNR)。

每个发射通道内置自我校准电路，以支持自动实时调整。发射器模块同时为每个通道提供一个TX监控器模块。该模块监控发射器输出，并通过一个未使用的接收器通道将其送回BBP，以实现信号监控。TX监控器模块仅在接收器空闲的TDD模式下可用。

## 时钟输入选项

[AD9361](#)运行时使用的参考时钟可由两个不同时钟源提供。第一个选择是使用一个专门的晶振，其频率在19 MHz和50 MHz之前，连接于XTALP和XTALN引脚之间。第二个选择是将一个外部振荡器或时钟分配器件(如[AD9548](#))连接至XTALN引脚(其中，XTALP引脚保持断开状态)。如果使用外部振荡器，则频率可在10 MHz和80 MHz之间变化。该参考时钟用于为频率合成器模块提供电源，这些模块在器件内部生成所有数据时钟、采样时钟和本振。

利用数字可编程、数字控制晶振(DCXO)功能来调节片内可变电容，则可消除晶振频率误差。该电容可以调谐系统中的晶振频率变化，结果产生精度更高的参考时钟，而所有其他频率就是从这些时钟生成的。该功能也可配合片内温度检测功能使用，以便在正常运行中提供振荡器频率温度补偿。

## 频率合成器

### RF PLL

AD9361含有两个完全相同的频率合成器，用于为RF信号路径生成需要的LO信号：一个用于接收器，一个用于发射器。锁相环(PLL)频率合成器采用小数N设计，融入了完全集成式电压控制振荡器(VCO)和环路滤波器。在TDD运行模式下，频率合成器会根据RX和TX帧的需要开启和关闭。在FDD模式下，TX PLL和RX PLL可以同时激活。这些PLL不需要外部元件。

### BB PLL

AD9361还含有一个基带PLL频率合成器，用于生成所有基带相关时钟信号。这些包括ADC和DAC采样时钟、DATA\_CLK信号(见“数字数据接口”部分)和所有数据帧信号。该PLL的编程频率范围为700 MHz至1400 MHz，具体取决于系统的数据速率和采样速率要求。

## 数字数据接口

AD9361数据接口采用并行数据端口(P0和P1)来在器件和BBP之间传输数据。数据端口可以配置为单端CMOS格式或差分LVDS格式。这两种格式都可以配置为多种方式，以满足数据排序和数据端口连接的系统需求。其中包括单端口数据总线、双端口数据总线、单数据速率、双数据速率和各种数据排序组合，以在适当的时间将来自不同通道的数据传过总线。

总线传输是通过简单的硬件握手信令来控制的。两个端口可以工作于双向(TDD)模式或全双工(FDD)模式，在后一种模式下，一半位数用于发射数据、一半用于接收数据。接口也可配置为，只将其中一个数据端口用于不需要高数据速率而且倾向于使用较少接口引脚的应用。

### DATA\_CLK信号

RX数据提供DATA\_CLK信号，BBP可以在接收数据时使用后者。DATA\_CLK可以设为提供单数据速率(SDR)时序的速率(其中，数据在各上升时钟沿采样)，也可设为提供双数据速率(DDR)时序(其中，同时在上升沿和下降沿捕获数据)。该时序适用于使用单端口或两个端口的运行模式。

### FB\_CLK信号

对于发射数据，接口以FB\_CLK信号作为时序参考。对于突发控制信号，FB\_CLK允许源与上升沿捕获时序同步，而对于发射信号突发，则允许与上升沿(SDR模式)或双沿捕获(DDR模式)时序同步。FB\_CLK信号必须具有与DATA\_CLK的频率和占空比。

### RX\_FRAME信号

每当接收器输出有效数据时，器件都会生成一个RX\_FRAME输出信号。该信号有两个模式：电平模式(RX\_FRAME在数据有效期间保持高电平)和脉冲模式(RX\_FRAME以50%的占空比脉动)。类似地，BBP必须提供一个TX\_FRAME信号，以上升沿来指示有效数据传输的开始。与RX\_FRAME相似，TX\_FRAME信号可能在整个突发过程中保持高电平，或者，可能以50%的占空比脉动。

### 使能状态机

AD9361收发器包括一个使能状态机(ENSM)，允许对器件的当前状态进行实时控制。在正常运行过程中，器件可以置于多种不同状态，包括

- 待机—节能，频率合成器被禁用

- 休眠—待机，所有时钟/BB PLL被禁用

- TX—TX信号链被使能

- RX—RX信号链被使能

- FDD—TX和RX信号链被使能

- 报警—频率合成器被使能

ENSM有两种可能的控制方法：SPI控制和引脚控制。

### SPI控制模式

在SPI控制模式下，通过写SPI寄存器，从当前状态进入下一状态，从而实现对ENSM的异步控制。SPI控制被认为与DATA\_CLK异步，因为SPI\_CLK可能派生自一个不同的参考时钟，而且仍然能正常工作。当不需要对频率合成器进行实时控制时，推荐采用SPI控制ENSM法。只要BBIC能够精确执行SPI写操作，SPI控制就可以用于实时控制。

### 引脚控制模式

在引脚控制模式下，ENABLE引脚和TXNRX引脚的使能功能允许对当前状态进行实时控制。ENSM支持TDD或FDD运行模式，具体取决于相应SPI寄存器的配置。如果BBIC有可以实时控制的额外控制输出，允许用一个简单的双线接口来控制器件状态，则建议使用ENABLE和TXNRX引脚控制方法。为了使ENSM的当前状态进入下一状态，可以通过一个脉冲(边沿在内部检测)或电平来鸡翅ENABLE引脚的使能功能。

使用脉冲时，其最小脉冲宽度必须为一个FB\_CLK周期。在电平模式下，ENABLE和TXNRX引脚同样由AD9361检测其边沿，而且必须符合相同的最小脉冲宽度要求，即一个FB\_CLK周期。

在FDD模式下，ENABLE和TXNRX引脚必须重新映射，作为实时RX和TX数据传输控制信号。在该模式下，ENABLE引脚使能或禁用接收信号路径，TXNRX引脚使能或禁用发射信号路径。在该模式下，ENSM将从系统中移除，以便由这些引脚控制所有数据流。

## SPI接口

AD9361通过一个串行外设接口(SPI)与BBP通信。该接口可以配置为4线接口，带有专门的接收和发射端口，也可以配置为3线接口，带一个双向数据通信端口。该总线允许BBP通过一种简单地址数据串行总线协议，设置所有器件控制参数。

写命令遵循一种24位格式。前6位用于设置总线方向和需要传输的字节数。接下来的10位数据的写入地址。最后8位是将被传输至指定寄存器地址(MSB至LSB)的数据。

AD9361还支持LSB优先格式，允许命令以LSB至MSB格式写入。在该模式下，对于多字节写命令，寄存器地址将递增。

读命令遵循相似的格式，区别在于，前16位在SPI\_DI引脚上传输，最后8位从AD9361中读取，如果是4线模式，则在SPI\_DO引脚上完成，如果是3线模式，则在SPI\_DI引脚上完成。

## 控制引脚

### 控制输出(CTRL\_OUT[7:0])

AD9361提供8个同步实时输出信号，用作BBP的中断。这些输出可以配置为输出一些内部设置和测量值，BBP在监控收发器在不同情况下的性能时可以使用这些设置和测量值。控制输出指针寄存器选择将哪些信息输出到这些引脚，而控制输出使能寄存器则决定BBP将激活哪些信号以便监控。用于手动增益模式的信号、校准标志、状态机状态和ADC输出都是可以在这些引脚上监控的部分输出。

### 控制输入(CTRL\_IN[3:0])

AD9361提供4个边沿检测控制输入引脚。在手动增益模式下，BBP可以用这些引脚来实时更改增益表索引。在发射模式下，BBP可以使用两个这些引脚来实时更改发射增益。

### GPO引脚(GPO\_3至GPO\_0)

AD9361提供4个支持3.3 V的通用逻辑输出引脚：GPO\_3、GPO\_2、GPO\_1和GPO\_0。这些引脚可以用于通过AD9361 SPI总线控制其他外设器件，比如稳压器、开关等，或者，也可充当内部AD9361状态机的从机。

## 辅助转换器

### AUXADC

AD9361含有一个辅助ADC，可以用来监控温度、功率输出等系统功能。转换器为12位宽，输入范围为0 V至1.25 V。使能时，ADC处于自由运行状态。SPI读操作提供在ADC输出端锁存的最后值。借助位于ADC之前的一个多路复用器，用户可以在AUXADC输入引脚与内置温度传感器之间进行选择。

### AUXDAC1和AUXDAC2

AD9361含有两个完全相同的辅助DAC，可以提供功率放大器(PA)偏置或其他系统功能。辅助DAC为10位宽，输出电压范围为0.5 V至VDD\_GPO - 0.3 V，电流驱动为10 mA，可以通过内部使能状态机直接控制。

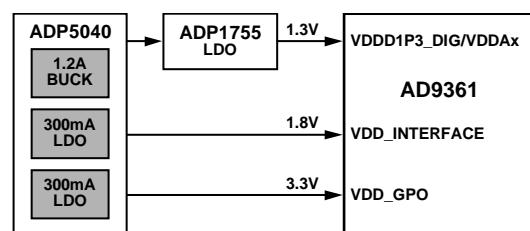

## AD9361的供电

AD9361必须通过以下三种电源供电：模拟电源(VDDD1P3\_DIG/VDDAx = 1.3 V)、接口电源(VDD\_INTERFACE = 1.8 V)和GPO电源(VDD\_GPO = 3.3 V)。

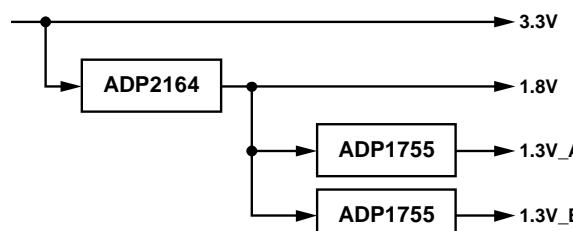

对于要求优化噪声性能的应用，建议用低噪声、低压差(LDO)稳压器分离和提供1.3 V电源。图74展示的是建议方法。

图74.面向AD9361的低噪声电源解决方案

对于注重电路板空间并且最佳噪声性能不构成绝对要求的应用，1.3 V模块电轨可以直接由一个开关提供，并且可以采取一种集成程度更高的电源管理装置(PMU)。图75显示了这种方法。

图75.面向AD9361的空间优化型电源解决方案

## 封装和订购信息

### 外形尺寸

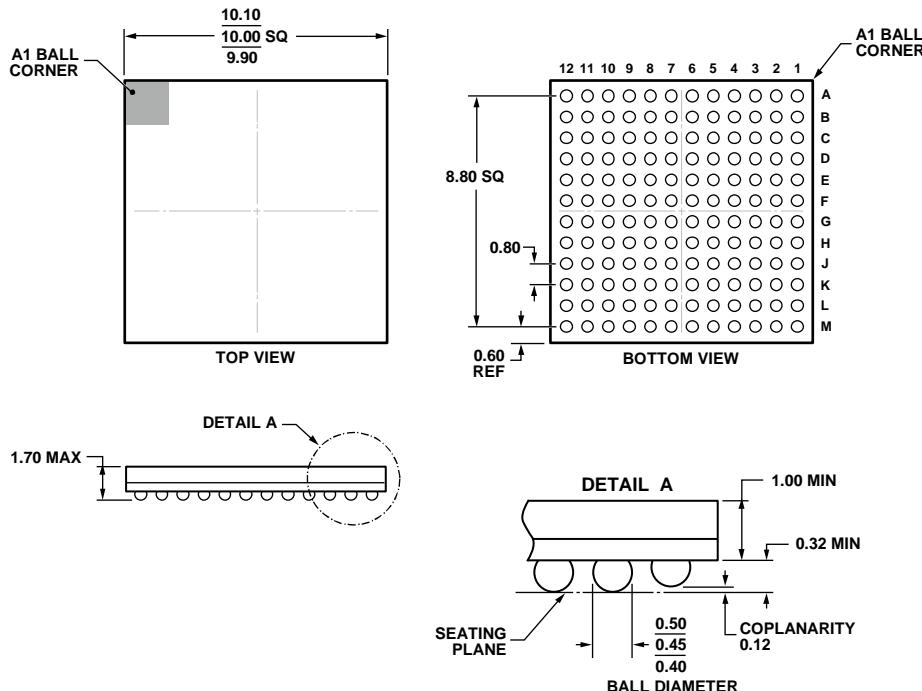

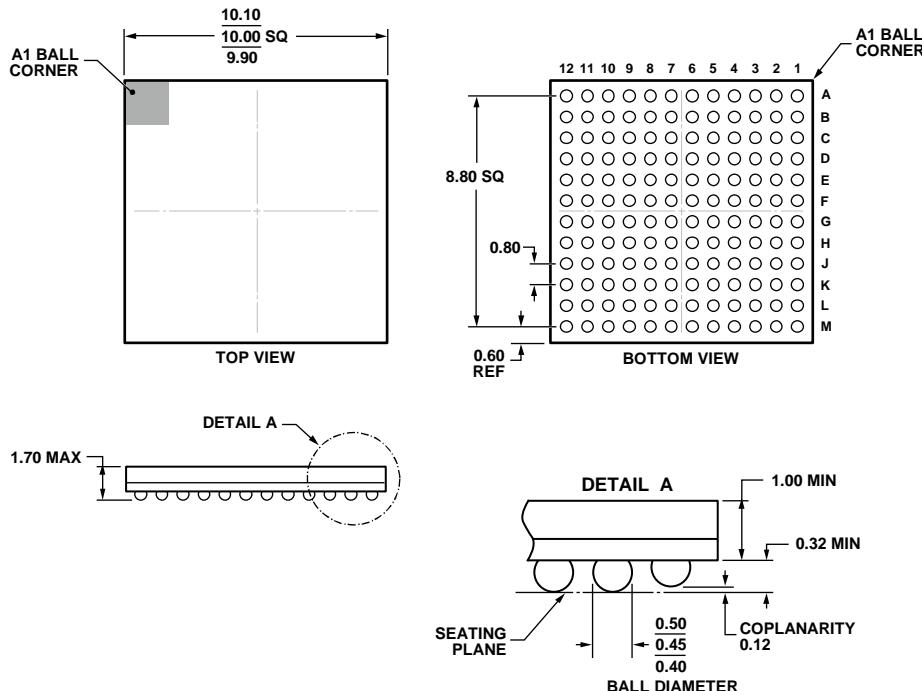

COMPLIANT TO JEDEC STANDARDS MO-275-EEAB-1.

11-8-2011A

图76.144引脚芯片级封装球栅阵列[CSP\_BGA]

(BC-144-7)

图示尺寸单位：毫米

### 订购指南

| 型号 <sup>1</sup> | 温度范围        | 封装描述           | 封装选项     |

|-----------------|-------------|----------------|----------|

| AD9361BBCZ      | -40°C至+85°C | 144引脚CSP_BGA封装 | BC-144-7 |

| AD9361BBCZ-REEL | -40°C至+85°C | 144引脚CSP_BGA封装 | BC-144-7 |

<sup>1</sup> Z = 符合RoHS标准的器件。

## 封装和订购信息

### 外形尺寸

COMPLIANT TO JEDEC STANDARDS MO-275-EEAB-1.

11-18-2011A

图76.144引脚芯片级封装球栅阵列[CSP\_BGA]

(BC-144-7)

图示尺寸单位：毫米

### 订购指南

| 型号 <sup>1</sup> | 温度范围        | 封装描述           | 封装选项     |

|-----------------|-------------|----------------|----------|

| AD9361BBCZ      | -40°C至+85°C | 144引脚CSP_BGA封装 | BC-144-7 |

| AD9361BBCZ-REEL | -40°C至+85°C | 144引脚CSP_BGA封装 | BC-144-7 |

<sup>1</sup> Z = 符合RoHS标准的器件。

## 封装和订购信息

### 外形尺寸

COMPLIANT TO JEDEC STANDARDS MO-275-EEAB-1.

11-18-2011A

图76.144引脚芯片级封装球栅阵列[CSP\_BGA]

(BC-144-7)

图示尺寸单位：毫米

### 订购指南

| 型号 <sup>1</sup> | 温度范围        | 封装描述           | 封装选项     |

|-----------------|-------------|----------------|----------|

| AD9361BBCZ      | -40°C至+85°C | 144引脚CSP_BGA封装 | BC-144-7 |

| AD9361BBCZ-REEL | -40°C至+85°C | 144引脚CSP_BGA封装 | BC-144-7 |

<sup>1</sup> Z = 符合RoHS标准的器件。