**Tronlong®**

# **TL665xFI-EasyEVM**

## 开发板规格书

**广州创龙电子科技有限公司**

© 2013 Guangzhou Tronlong Electronic Technology Co.,Ltd.

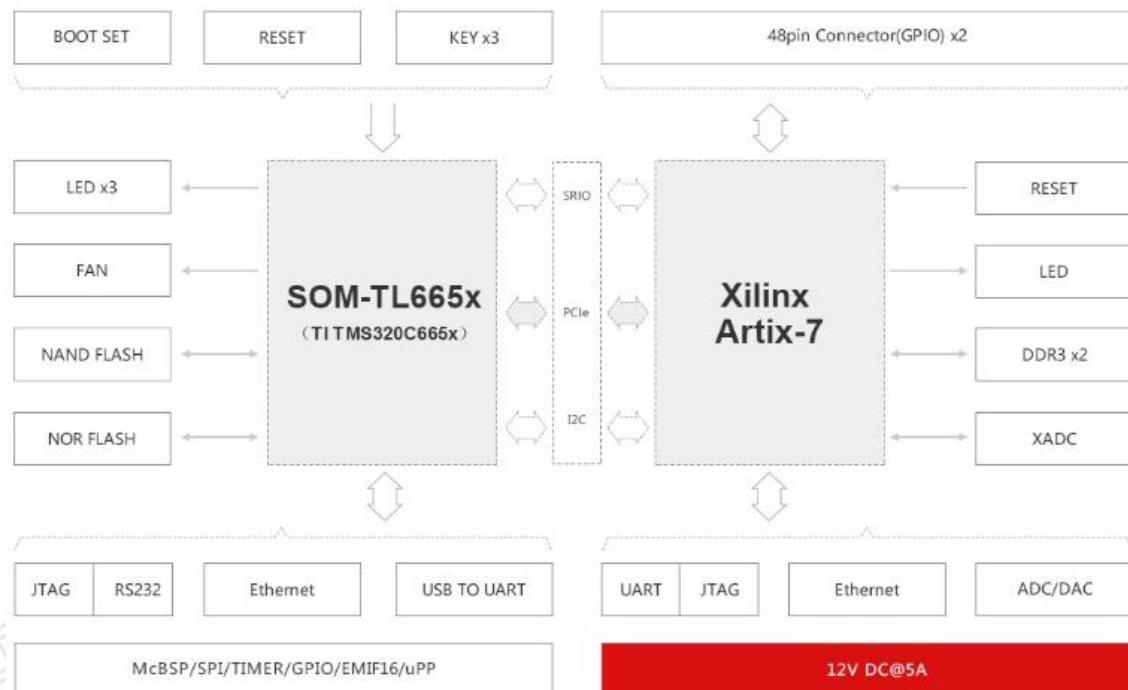

通信原理基于创龙 DSP+FPGA TMS320C665x, FPGA 端基于 Xilinx Artix-7 处理器简介

## 1 DSP+FPGA TMS320C665x + Xilinx Artix-7 开发板简介

- 集成 TL665x-EasyEVM 开发板 (DSP 端) + TL-A7HSAD 采集卡 (FPGA 端);

- DSP 端基于 TI KeyStone C66x 多核定点/浮点 DSP TMS320C665x, 单核 TMS320C6655 和双核 TMS320C6657 管脚 pin to pin 兼容, FPGA 端基于 Xilinx Artix-7 处理器;

- TMS320C665x 主频为 1.0/1.25GHz, 单核运算能力高达 40GMACS 和 20GFLOPS, 包含 2 个 Viterbi 协处理器和 1 个 Turbo 协处理解码器, 每核心 32KByte L1P、32KByte L1D、1MByte L2, 1MByte 多核共享内存, 8192 个多用途硬件队列, 支持 DMA 传输;

- FPGA 芯片为 XC7A100T-2FGG484I, 逻辑单元 101K 个, DSP Slice 240 个;

- FPGA 采集卡支持双通道 250MSPS\*12Bit 高速高精度 ADC, 一路 175MSPS\*12Bit 高速高精度 DAC, 满足多种数据采集需求, 同时支持 CameraLink 输入输出、VGA 输出等拓展模块;

- DSP 开发板支持千兆网口, 可接工业网络摄像机, 同时支持 uPP、EMIF16、I2C、SPI、UART、McBSP 等常见接口;

- 开发板 DSP 端与 FPGA 端通过 I2C、PCIe、SRIO 等通讯接口连接, 其中 PCIe、SRIO 每路传输速度最高可达到 5GBaud。

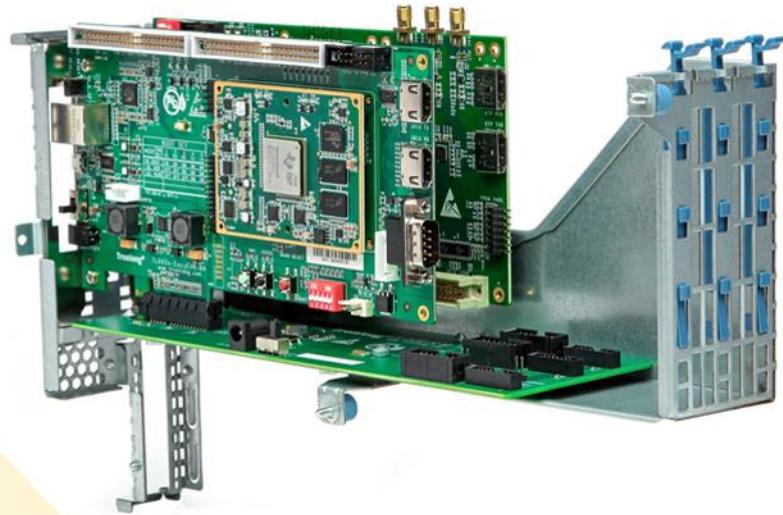

图 1 开发板正面图

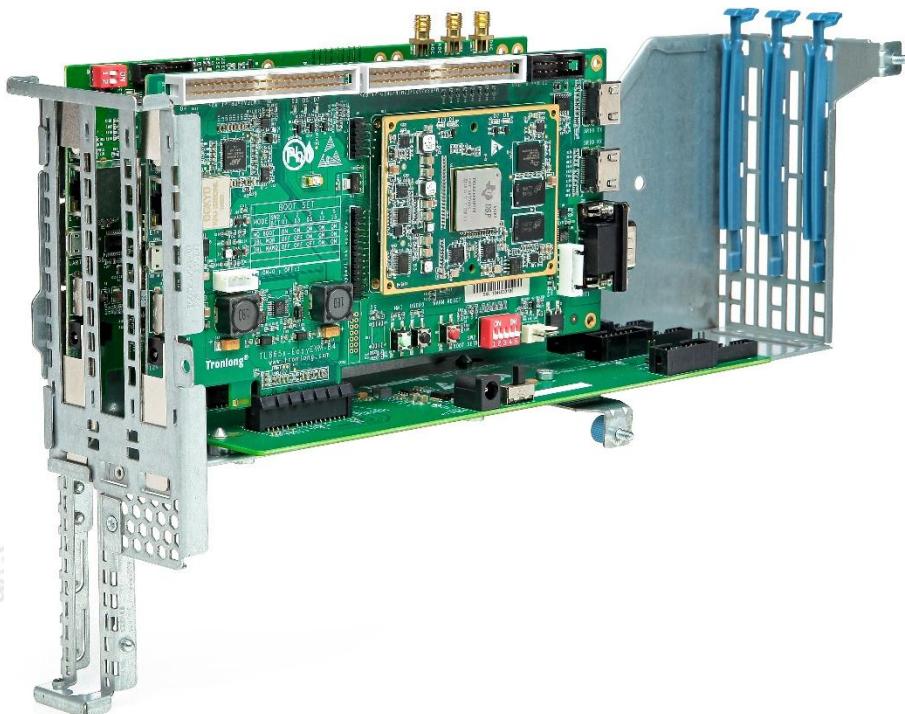

图 2 开发板斜视图 1

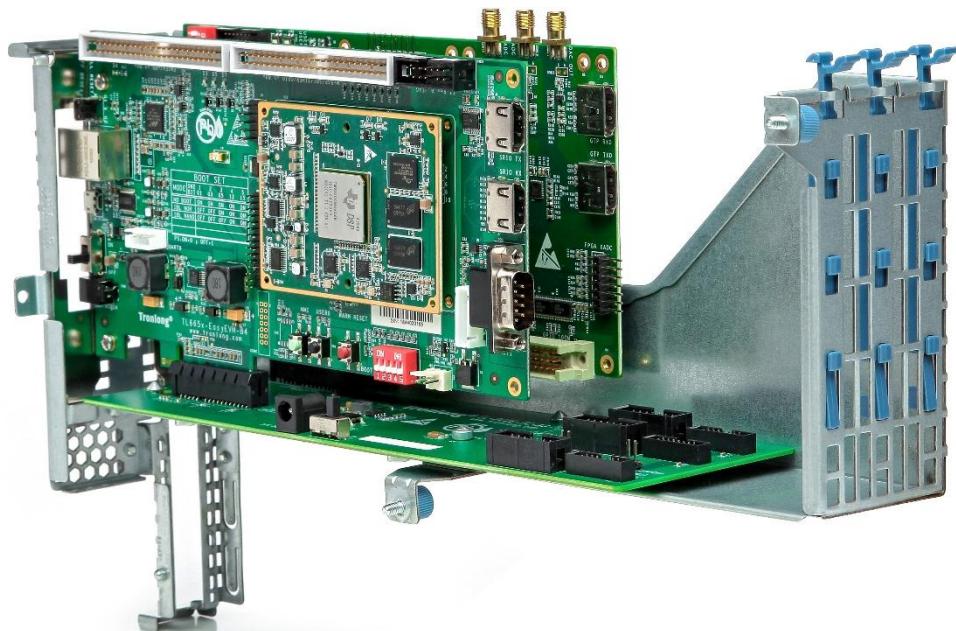

图 3 开发板斜视图 2

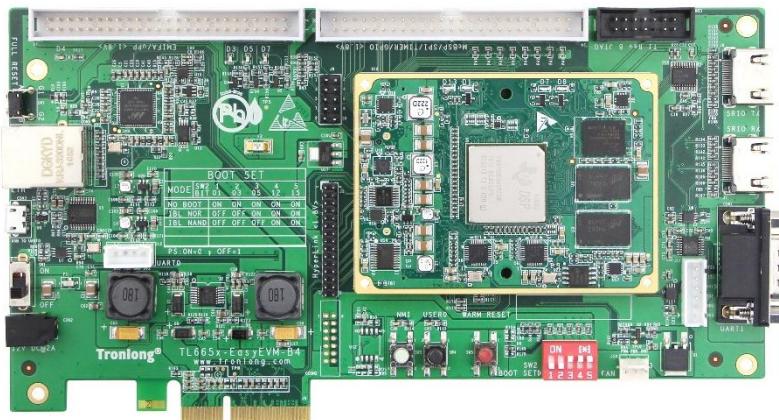

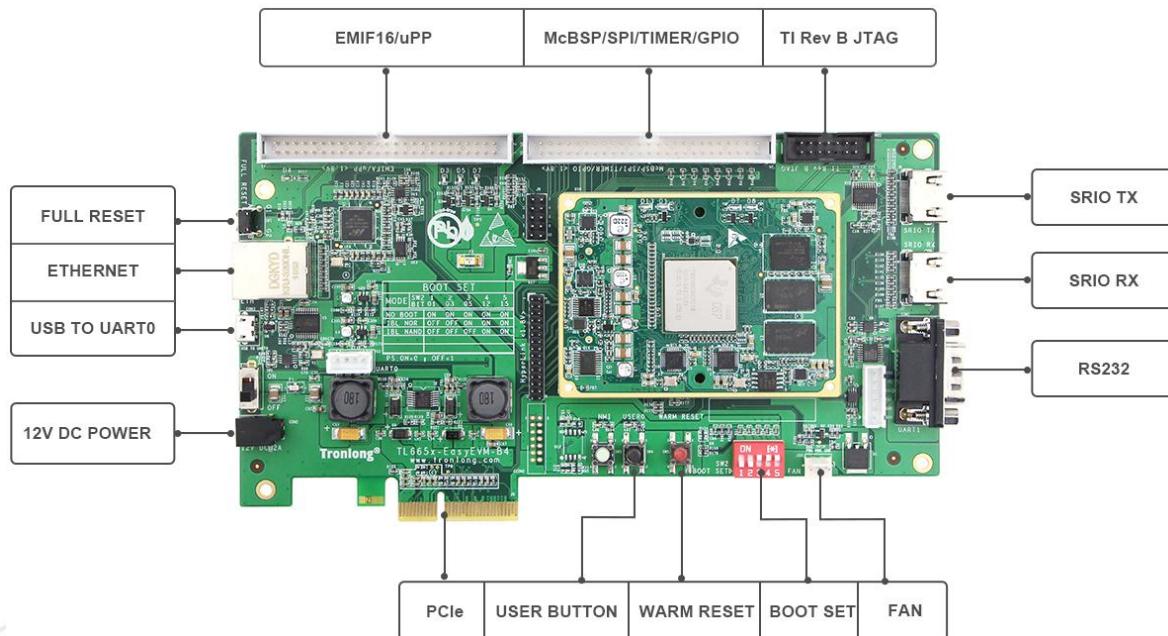

图 4 DSP 开发板正面图

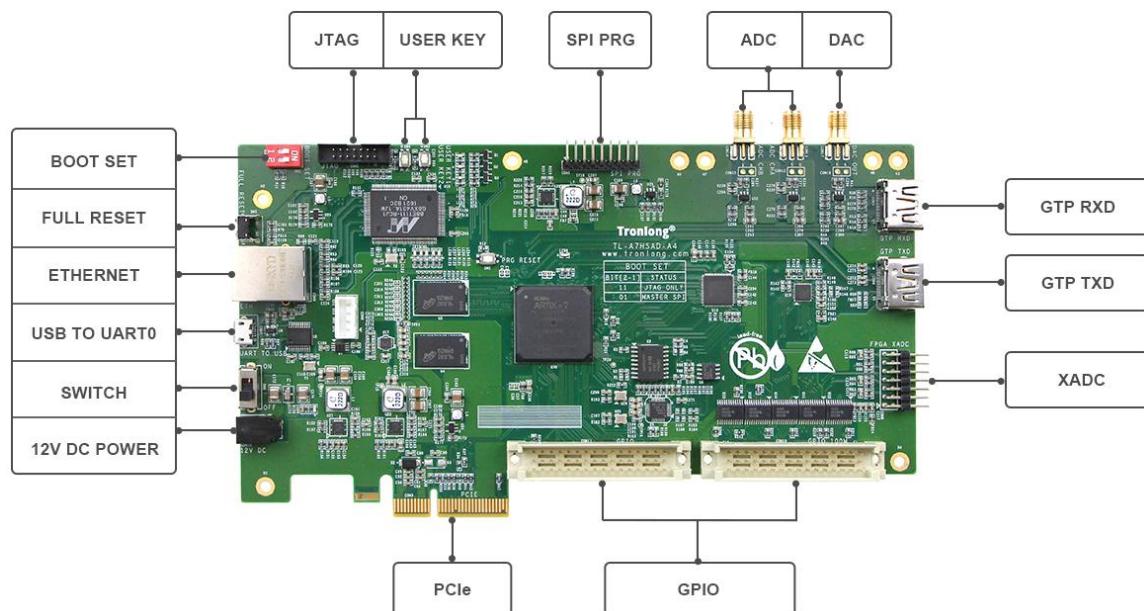

图 5 FPGA 采集卡正面图

广州创龙基于 TI 设计的 TL665xFI-EasyEVM 是一款 DSP+FPGA 高速大数据采集处理架构，适用于高端图像处理、高速大数据传输和音视频等大数据采集处理领域。

此设计通过 I2C、PCIe、SRI0 等通信接口将 DSP 开发板和 FPGA 采集卡结合在一起，组成 DSP+FPGA 架构，实现了需求独特、灵活、功能强大的 DSP+FPGA 高速数据采集处理系统。

DSP 和 FPGA 可以独立开发，互不干扰。其中 DSP 开发板使用核心板+底板形式，SO M-TL665x 核心板引出丰富的资源信号引脚，客户只需要专注上层运用，降低了开发难度和时间成本。FPGA 采集卡提供工业级高速数据传输 PCIe x4 接口，串行高速输入输出 GTP 总线通过 HDMI 接口提供稳定、可靠的高速传输能力，还引出丰富的 IO 接口，为产品搭建提供极大的便利。

提供丰富的 Demo 程序，包含 DSP 开发例程、DSP 与 FPGA 通信例程、FPGA 开发例程，全面的技术支持，协助客户进行底板设计和调试以及多核软件开发。

## 2 DSP+FPGA TMS320C665x + Xilinx Artix-7 典型运用领域

- ✓ 数据采集处理显示系统 Telecom Tower: 远端射频单元 (RRU)

- ✓ 高速数据采集和生成

- ✓ 高速数据采集处理系统

- ✓ 高端图像处理设备

- ✓ 高端音视频数据处理

- ✓ 通信系统

## 3 DSP+FPGA TMS320C665x + Xilinx Artix-7 通讯原理

- 前端由 FPGA 采集数据 (AD 或视频)，数据通过 PCIe、SRIO、I2C 等通信接口传输到 DSP；

- 数据被 DSP 处理之后，可用于数据对比和分析、网络转发、SATA 硬盘存储等应用；

- DSP 根据处理结果，将得到的逻辑控制命令送 FPGA，由 FPGA 控制板载 DA 实现逻辑输出，更新速率 175MSPS。

### 硬件框图

图 6 开发板硬件框图

(1) 高速数据采集前端部分由 FPGA 同步采集两路 AD 模拟输入信号，可实现对 AD 数据进行预滤波处理，AD 采样率最高可达 250MSPS。另外一路 DAC 可输出任意幅值和任意波形的并行 DA 数据，更新速率 175MSPS。

(2) 高速数据传输部分由 I2C、PCIe、SRIO 等通信接口构成。大规模吞吐量的 AD 和 DA 数据，可通过 SRIO 和 PCIe 接口在 DSP 和 FPGA 之间进行高速稳定传输；DSP 对 FPGA 进行逻辑控制和进行中等规模吞吐量的数据交换，同时可通过 I2C 对 FPGA 端进行初始化设置和参数配置。

(3) 高速数据处理部分由 DSP 核和算法库构成。可实现对 AD 和 DA 数据进行时域、频域、幅值等信号参数进行实时变换处理（如 FFT 变换、FIR 滤波等）。

(4) 视频采集、输出拓展部分由 CameraLink 输入输出模块、VGA 输出模块、千兆网等部分构成。接口资源丰富，方案选择灵活方便，是高端图像处理系统的理想选择。

图 7 DSP 开发板硬件资源图解

图 8 FPGA 采集卡硬件资源图解

#### 4 DSP+FPGA TMS320C665x + Xilinx Artix-7 硬件参数

表 1 DSP 端硬件参数

|     |                                               |

|-----|-----------------------------------------------|

| CPU | 单核 TMS320C6655/双核 TMS320C6657, 主频 1.0/1.25GHz |

| ROM | 128/256MByte NAND FLASH                       |

创龙

|                      |                                                                                                                              |

|----------------------|------------------------------------------------------------------------------------------------------------------------------|

|                      | 64Mbit SPI NOR FLASH                                                                                                         |

| <b>RAM</b>           | 512M/1GByte DDR3                                                                                                             |

| <b>EEPROM</b>        | 1Mbit                                                                                                                        |

| <b>SENSOR</b>        | 1x TMP102AIDRLT, 核心板温度传感器, I2C 接口                                                                                            |

| <b>B2B Connector</b> | 2x 50pin 公座 B2B, 2x 50pin 母座 B2B, 间距 0.8mm, 合高 5.0mm;<br>1x 80pin 高速 B2B 连接器, 间距 0.5mm, 合高 5.0mm, 共 280pin, 信号速率最高可达 10GBaud |

| <b>LED</b>           | 2x 供电指示灯 (核心板 1 个, 底板 1 个)                                                                                                   |

|                      | 5x 用户指示灯 (核心板 2 个, 底板 3 个)                                                                                                   |

| <b>KEY</b>           | 2x 复位按键, 包含 1 个系统复位和 1 个软复位                                                                                                  |

|                      | 1x NMI 按键                                                                                                                    |

|                      | 1x 用户按键                                                                                                                      |

| <b>SRIO</b>          | 1x SRIO, 四端口四通道, 每通道最高通信速率 5GBaud                                                                                            |

| <b>PCIe</b>          | 1x PCIe Gen2, 单端口双通道, 每通道最高通信速率 5GBaud                                                                                       |

| <b>HyperLink</b>     | 1x HyperLink, 最高通信速率 40GBaud, KeyStone 处理器间互连的理想接口                                                                           |

| <b>IO</b>            | 2x 25pin IDC3 简易牛角座, 间距 2.54mm, 含 uPP、EMIF16 拓展信号                                                                            |

|                      | 2x 25pin IDC3 简易牛角座, 间距 2.54mm, 含 McBSP、SPI、TIMER、GPIO 等拓展信号                                                                 |

| <b>UART</b>          | 1x UART0, Micro USB 接口, 提供 4 针 TTL 电平测试端口                                                                                    |

|                      | 1x UART1, DB9 接口, 提供 6 针 TTL 电平测试端口                                                                                          |

| <b>Ethernet</b>      | 1x SGMII, RJ45 接口, 10/100/1000M 自适应                                                                                          |

| <b>JTAG</b>          | 1x 14pin TI Rev B JTAG 接口, 间距 2.54mm                                                                                         |

| <b>FAN</b>           | 1x FAN, 12V 供电, 间距 2.54mm                                                                                                    |

| <b>BOOT SET</b>      | 1x 5bit 拨码开关                                                                                                                 |

| <b>SWITCH</b>        | 1x 电源开关                                                                                                                      |

| <b>POWER</b>         | 1x 12V 2A 直流输入 DC417 电源接口, 外径 4.4mm, 内径 1.65mm                                                                               |

**备注:** 广州创龙 SOM-TL6655、SOM-TL6657 核心板在硬件上 pin to pin 兼容。

表 2 采集卡硬件参数

|                 |                                                 |

|-----------------|-------------------------------------------------|

| <b>FPGA</b>     | Xilinx Artix-7 XC7A100T-2FGG484I                |

| <b>ROM</b>      | 256Mbit SPI NOR FLASH                           |

| <b>RAM</b>      | 512M/1GByte DDR3                                |

| <b>EEPROM</b>   | 2Kbit                                           |

| <b>LED</b>      | 1x 供电指示灯                                        |

|                 | 1x PRG 状态灯                                      |

|                 | 3x 用户指示灯                                        |

| <b>KEY</b>      | 1x 复位按键                                         |

|                 | 1x PRG REESET 按键                                |

|                 | 2x 用户按键                                         |

| <b>ADC</b>      | 双通道, 量程 0~8.5V, 12bit, 最高 250MHz 采样率, LVDS 信号输出 |

| <b>DAC</b>      | 175MHz, 12bit, 最大输出电流 5mA                       |

| <b>XADC</b>     | 1x XADC 双通道, 12bit, 1MHz, 1.0Vp-p               |

| <b>PCIe</b>     | 1x PCIe Gen2, 单端口双通道, 每通道最高通信速率 5GBaud          |

| <b>GTP</b>      | 1x GTP, 双通道, 每通道最高速率 5GBaud, 通过 HDMI 座引出        |

| <b>IO</b>       | 2x 48pin 欧式连接器, GPIO 拓展                         |

|                 | 1x I2C, 通过 HDMI 座引出                             |

| <b>Ethernet</b> | 1x GMII, RJ45 接口, 10/100/1000M 自适应              |

| <b>UART</b>     | 1x UART, Micro USB 接口, 提供 4 针 TTL 电平测试端口        |

| <b>JTAG</b>     | 1x 14pin JTAG 接口, 间距 2.0mm                      |

| <b>BOOT SET</b> | 1x 2bit 拨码开关                                    |

| <b>SWITCH</b>   | 1x 电源开关                                         |

| <b>POWER</b>    | 1x 12V 2A 直流输入 DC417 电源接口, 外径 4.4mm, 内径 1.65mm  |

## 5 DSP+FPGA TMS320C665x + Xilinx Artix-7 软件参数

创龙

表 3

|            |                  |

|------------|------------------|

| DSP 端软件支持  | 裸机、SYS/BIOS 操作系统 |

| CCS 版本号    | CCS5.5           |

| 软件开发套件提供   | MCSDK            |

| Vivado 版本号 | 2015.2           |

## 6 DSP+FPGA TMS320C665x + Xilinx Artix-7 开发资料

- (1) 提供核心板引脚定义 (DSP 端)、可编辑底板原理图、可编辑底板 PCB、采集卡原理图、芯片 Datasheet，缩短硬件设计周期；

- (2) 提供丰富的 Demo 程序，包含 DSP 开发例程、DSP 与 FPGA 通过 PCIe、SRIO、I2C 通信例程、FPGA 开发例程；

- (3) 提供丰富的平台开发包、入门教程，节省软件整理时间，上手容易；

部分开发例程详见附录 A，开发例程主要包括：

- 裸机开发例程

- SYS/BIOS 开发例程

- 多核开发例程

- FPGA 开发例程

## 7 DSP+FPGA TMS320C665x + Xilinx Artix-7 电气特性

### DSP 端核心板工作环境

表 4

| 环境参数  | 最小值   | 典型值 | 最大值  |

|-------|-------|-----|------|

| 工业级温度 | -40°C | /   | 85°C |

| 工作电压  | /     | 9V  | /    |

### FPGA 采集卡工作环境

**创龙**

表 5

| 环境参数 | 最小值 | 典型值 | 最大值  |

|------|-----|-----|------|

| 工作温度 | 0°C | /   | 70°C |

| 工作电压 | /   | 12V | /    |

**DSP 端功耗**

表 6

| 类别  | 典型值电压  | 典型值电流   | 典型值功耗 |

|-----|--------|---------|-------|

| 核心板 | 8.95V  | 418.8mA | 3.75W |

| 整板  | 11.97V | 597.4mA | 7.15W |

备注：功耗测试基于广州创龙 TL6657-EasyEVM 开发板进行。

**FPGA 端功耗**

表 7

| 典型值电压  | 典型值电流 | 典型值功耗 |

|--------|-------|-------|

| 12.05V | 150mA | 1.80W |

备注：功耗测试基于广州创龙 TL-A7HSAD 采集卡进行。

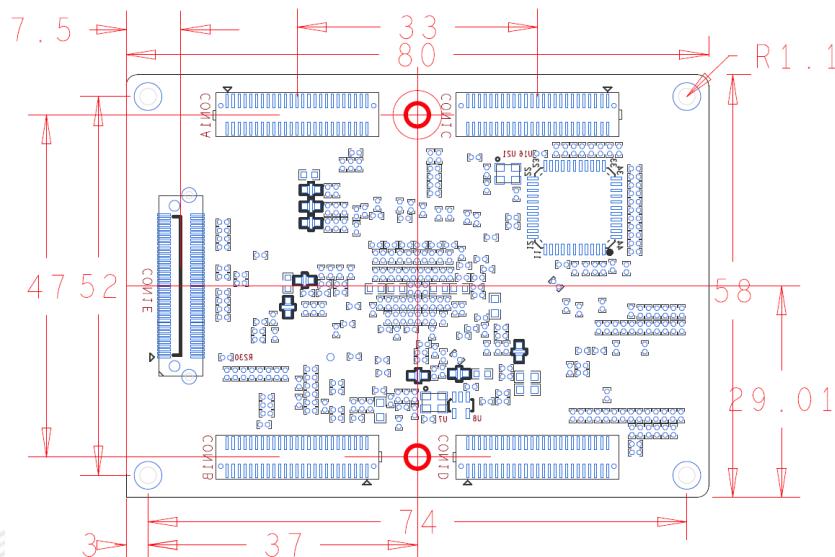

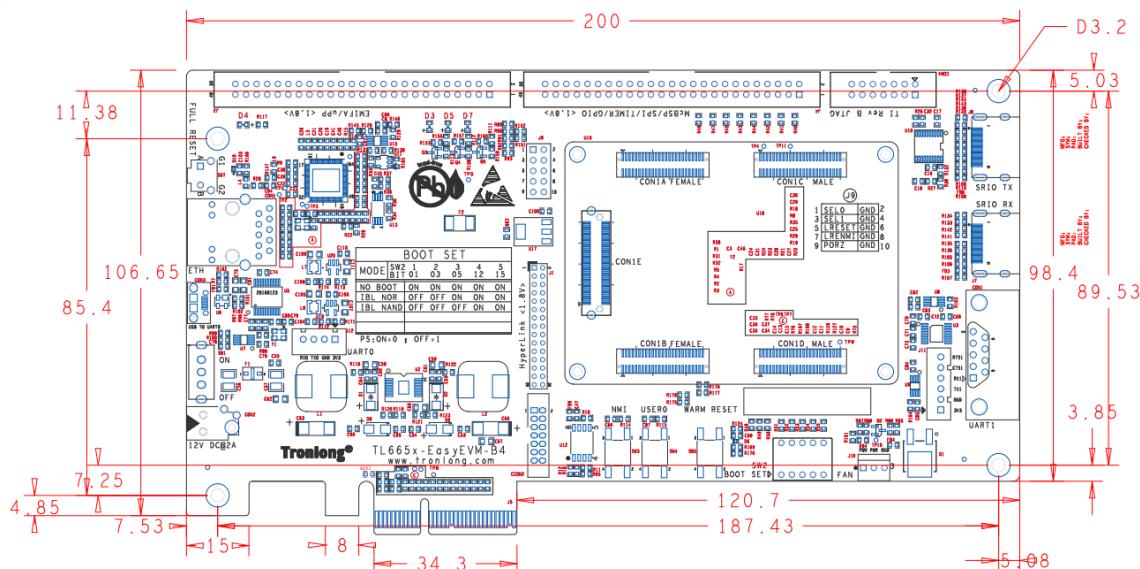

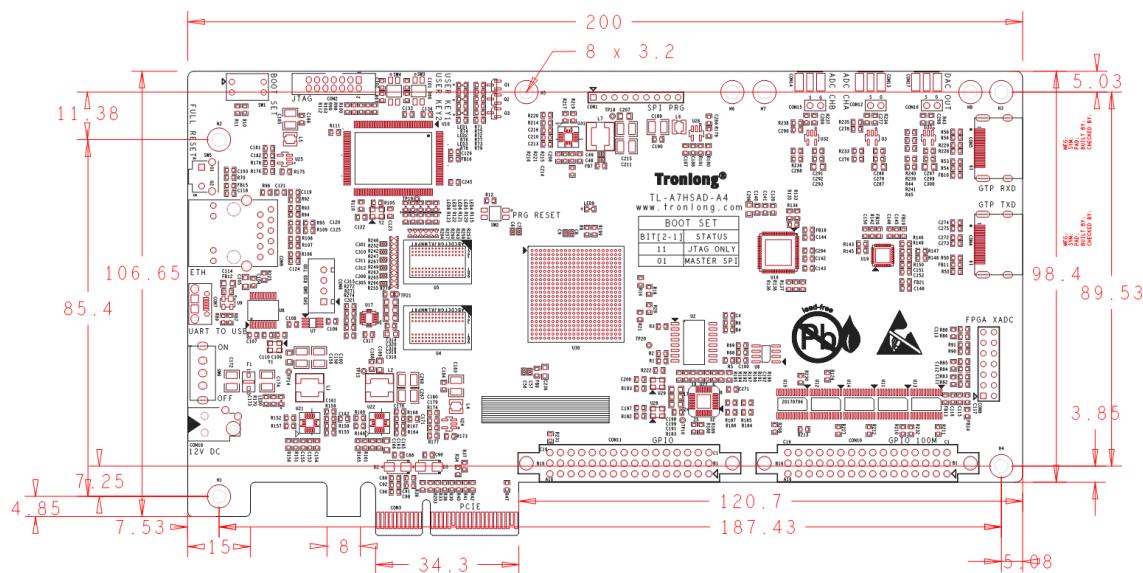

**8 DSP+FPGA TMS320C665x + Xilinx Artix-7 机械尺寸图**

表 8

|          | 核心板       | DSP 开发板        | FPGA 采集卡       |

|----------|-----------|----------------|----------------|

| PCB 尺寸   | 80mm*58mm | 200mm*106.65mm | 200mm*106.65mm |

| 安装孔数量    | 4 个       | 8 个            | 8 个            |

| 散热器安装孔数量 | 2 个       | /              | /              |

图 9 核心板机械尺寸图

图 10 开发板机械尺寸图

图 11 采集卡机械尺寸图

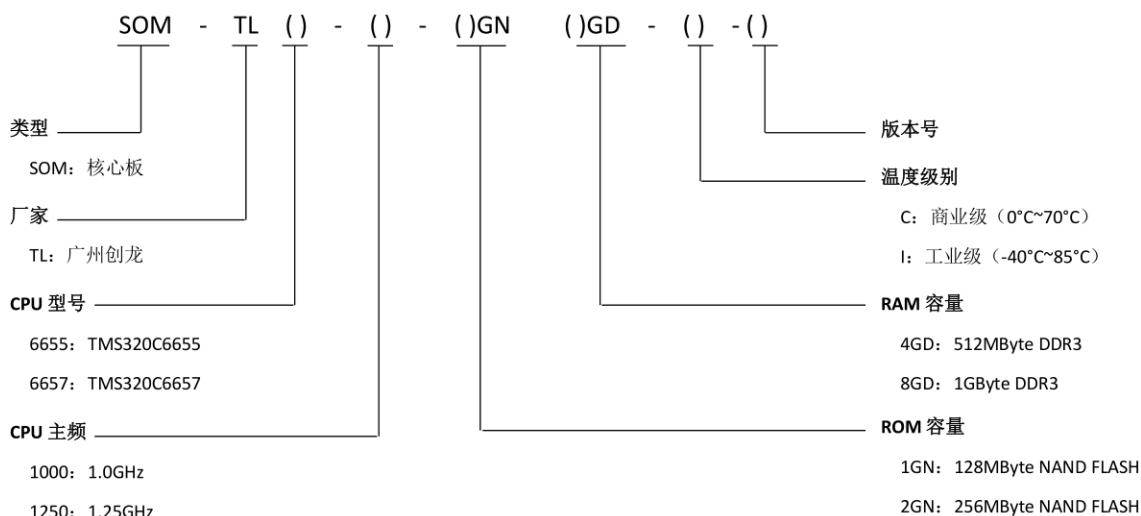

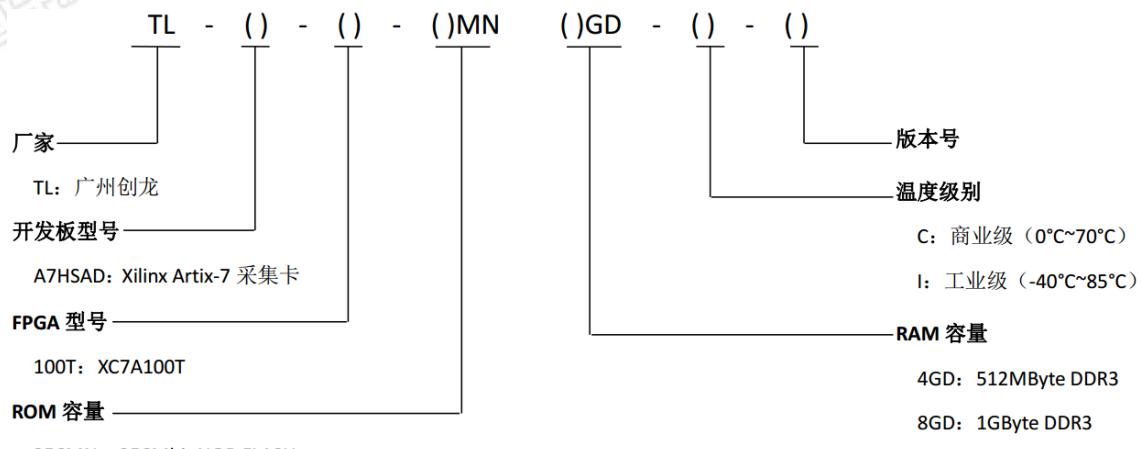

### 9 DSP+FPGA TMS320C665x + Xilinx Artix-7 产品订购型号

表 9 SOM-TL665x 核心板型号

| 型号                       | CPU 主频    | NAND FLASH | DDR3     | 温度级别 |

|--------------------------|-----------|------------|----------|------|

| SOM-TL6655-1000-1GN4GD-I | 单核 1.0GHz | 128MByte   | 512MByte | 工业级  |

| SOM-TL6655-1000-1GN8GD-I | 单核 1.0GHz | 128MByte   | 1GByte   | 工业级  |

| SOM-TL6657-1000-1GN4GD-I | 双核 1.0GHz | 128MByte   | 512MByte | 工业级  |

| SOM-TL6657-1000-1GN8GD-I | 双核 1.0GHz | 128MByte   | 1GByte   | 工业级  |

表 10 TL-A7HSAD 采集卡型号

| 型号                        | FPGA 型号  | NOR FLASH | DDR3     | 温度级别 |

|---------------------------|----------|-----------|----------|------|

| TL-A7HSAD-100T-256MN4GD-C | XC7A100T | 256Mbit   | 512MByte | 商业级  |

| TL-A7HSAD-100T-256MN8GD-C | XC7A100T | 256Mbit   | 1GByte   | 商业级  |

**备注：**标配为 SOM-TL6655-1000-1GN4GD-I 和 TL-A7HSAD-100T-256MN4GD-C，其他型号请与相关销售人员联系。

### 型号参数解释

图 12 DSP 端型号参数详解

图 13 FPGA 端型号参数详解

## 10 DSP+FPGA TMS320C665x + Xilinx Artix-7 开发板套件清单

表 11

| 名称                        | 数量  |

|---------------------------|-----|

| TL665x-EasyEVM 开发板 (含核心板) | 1 块 |

| TL-A7HSAD 采集卡             | 1 块 |

| TL-PCIe-TC 转接板            | 1 块 |

| 12V2A 电源适配器               | 1 个 |

| 12V6A 电源适配器               | 1 个 |

|                 |     |

|-----------------|-----|

| 资料光盘            | 2 套 |

| Micro USB 数据线   | 2 条 |

| 直连网线            | 2 条 |

| HDMI 线          | 2 条 |

| RS232 交叉串口母母线   | 1 条 |

| USB 转 RS232 串口线 | 1 条 |

| SMA 连接线         | 4 条 |

| 跳线帽             | 2 个 |

| 金属固定架           | 1 个 |

| 金属挡板            | 2 片 |

| 散热片             | 1 片 |

| 风扇              | 1 个 |

## 11 DSP+FPGA TMS320C665x + Xilinx Artix-7 技术支持

- (1) 协助底板设计和测试，减少硬件设计失误；

- (2) 协助解决按照用户手册操作出现的异常问题；

- (3) 协助产品故障判定；

- (4) 协助正确编译与运行所提供的源代码；

- (5) 协助进行产品二次开发；

- (6) 提供长期的售后服务。

## 12 DSP+FPGA TMS320C665x + Xilinx Artix-7 增值服务

- 主板定制设计

- 核心板定制设计

- 嵌入式软件开发

- 项目合作开发

**创龙**

- 技术培训

**DSP+FPGA TMS320C665x + Xilinx Artix-7 更多帮助**

销售邮箱: [sales@tronlong.com](mailto:sales@tronlong.com)

技术邮箱: [support@tronlong.com](mailto:support@tronlong.com)

创龙总机: 020-8998-6280

技术热线: 020-3893-9734

创龙官网: [www.tronlong.com](http://www.tronlong.com)

技术论坛: [www.51ele.net](http://www.51ele.net)

线上商城: <https://tronlong.taobao.com>

TMS320C665x、TMS320C6678 交流群: 79635273、332643352

TI 中文论坛: <http://www.deyisupport.com/>

TI 英文论坛: <http://e2e.ti.com/>

TI 官网: [www.ti.com](http://www.ti.com)

TI WIKI: <http://processors.wiki.ti.com/>

FPGA 交流群: 311416997、101245165

Xilinx 官网: [www.xilinx.com](http://www.xilinx.com)

Xilinx 论坛: <https://forums.xilinx.com/>

Xilinx WIKI: <http://www.wiki.xilinx.com/>

## 附录 A 开发例程

表 12

| 裸机开发例程                  |                           |

|-------------------------|---------------------------|

| 例程                      | 功能                        |

| GPIO_LED                | GPIO 输出 (LED 灯)           |

| GPIO_LED_C++            | GPIO 输出 (LED 灯)           |

| GPIO_KEY                | GPIO 输入 (按键中断)            |

| UART0_POLL              | UART1 串口查询收发              |

| NMI                     | NMI 不可屏蔽中断                |

| Timer                   | 定时器                       |

| WatchDog                | 看门狗                       |

| SPI_FLASH               | SPIFLASH 读写               |

| IIC EEPROM              | IIC EEPROM 读写             |

| EDMA3                   | EDMA3 一维数据传输              |

| UART1_INT               | UART1 串口中断收发              |

| I2C_TempSensor          | IIC 总线温度传感器测试             |

| I2C_TempSensor_POLL     | IIC 总线温度传感器测试             |

| NANDFLASH               | NANDFLASH 读写测试            |

| GPIO_LED_Assembly       | GPIO 输出 (标准汇编)            |

| GPIO_LED_LinearAssembly | GPIO 输出 (线性汇编)            |

| NonOS_MPAX              | 访问相同的逻辑地址                 |

| FFT_Real                | 快速傅里叶变换/逆变换               |

| FFT_Real_Benchmark      | 快速傅里叶变换/逆变换 (打开/关闭缓存速度对比) |

| FIR                     | 有限长单位冲激响应滤波器              |

| IIR                     | 无限脉冲响应数字滤波器               |

| DCT                     | 图像离散余弦变换                  |

|                             |                 |

|-----------------------------|-----------------|

| RGB2Gray                    | RGB24 图像转灰度     |

| HIST                        | 灰度图像直方图         |

| IntEqualize                 | 直方图均衡化          |

| ImageReverse                | 图像反色            |

| Canny                       | 边缘检测            |

| Threshold                   | 灰度图像二值化         |

| LinerTrans                  | 灰度图像线性变换        |

| Zoom                        | 图像缩放            |

| Rotate                      | 图像旋转            |

| MATH                        | 数学函数库           |

| Matrix                      | 矩阵运算            |

| Codec_Universal_Dma_Ti_ECPY | 调用 EDMA3 数据搬移算法 |

| FC_ECPY                     | 数据搬移的应用程序       |

| Codec_MPEG4Encoder          | MPEG4 视频编码      |

| Codec_MPEG4Decoder          | MPEG4 视频解码      |

| Algorithm LSB Hide          | 图片添加水印          |

| Algorithm_Plate_Recognition | 车牌识别            |

表 13

| SYS/BIOS 开发例程 |          |

|---------------|----------|

| 例程            | 功能       |

| Task          | 任务       |

| CLOCK         | 时钟       |

| Task_MUTEX    | 抢占式多任务   |

| Task_STATIC   | 静态创建任务   |

| Timer         | 定时器 (通用) |

| Timer_C665x   | 定时器 (专用) |

|                                     |                        |

|-------------------------------------|------------------------|

| Timer_C665x_Runtime                 | 定时器（动态创建）              |

| MEMORY                              | 内存分配                   |

| HWI_C66x                            | 硬件中断（HWI 设备专用组件）       |

| HWI_C66x_Hook                       | 硬件中断（HWI 挂钩函数）         |

| HWI_C66x_Nest                       | 硬件中断（HWI 中断嵌套）         |

| HWI_Runtime                         | 硬件中断（HWI）              |

| HWI_Runtime_Post_SWI                | 硬件中断（HWI 发布软件中断）       |

| HWI_Runtime_Post_Task               | 硬件中断（HWI 触发任务）         |

| SWI                                 | 软件中断（静态配置）             |

| SWI_Runtime                         | 软件中断（SWI）              |

| SWI_Runtime_Post_Conditionally_andn | 软件中断（有条件触发 ANDN）       |

| SWI_Runtime_Post_Conditionally_dec  | 软件中断（有条件触发 DEC）        |

| SWI_Runtime_Post_Unconditionally_or | 软件中断（无条件触发 OR）         |

| Timestamp                           | 时间戳（通用）                |

| Timestamp_C665x                     | 时间戳（专用）                |

| EDMA3                               | EDMA3 一维数据传输           |

| UART1_INT                           | UART1 串口中断收发           |

| McBSP0_LoopBack_Test                | McBSP0 外部回环测试          |

| uPP_8Bit_B_TO_A                     | uPP 双通道 8 位外部线路回路读写    |

| uPP_16Bit_B_TO_A                    | uPP 双通道 16 位外部线路回路读写   |

| PCIe                                | PCIe 板间通信              |

| SRIO                                | SRIO 板间通信              |

| SRIO_2x_FPGA2DSP                    | SRIO_2x_FPGA2DSP       |

| SRIO_DSP_2x_SWRITE                  | FPGA 与 DSP 的 SRIO 通信测试 |

| NDK_TCP                             | TCP 服务器                |

| NDK_UDP                             | UDP 通信                 |

| NDK_TCP_Benchmark                   | TCP 发送/接收速度测试          |

|                  |                            |

|------------------|----------------------------|

| NDK_Telnet       | Telnet 协议                  |

| NDK_Runtime      | 网络 Web 服务器 (支持串口输入 IP)     |

| NDK_WebServer    | 网络 Web 服务器                 |

| NDK_TCP_Client   | TCP 客户端                    |

| NDK_RawSocket    | 以太网数据链路层通信                 |

| NDK_UIA          | 基于网络传输的系统分析                |

| DSP_FPGA_CL_SRIO | CameraLink 工业相机高性能实时采集处理系统 |

| Board_C665x      | 开发板全基本功能测试                 |

表 14

| 多核开发例程                                    |                         |

|-------------------------------------------|-------------------------|

| 例程                                        | 功能                      |

| MultiCore_SingleImage                     | 多核单镜像通信测试               |

| MultiCore_DualImage                       | 多核多镜像通信测试               |

| MultiCore_SingleImage_SYSBIOS             | 多核单镜像 SYSBIOS 通信测试      |

| MultiCore_DualImage_SYSBIOS               | 多核多镜像 SYSBIOS 通信测试      |

| MultiCore_SingleImage_Semaphore2          | 硬件信号量测试                 |

| MultiCore_SingleImage2_Semaphore2_SYSBIOS | 多核单镜像 SYSBIOS 通信测试      |

| OpenMP_Hello                              | OpenMP 的测试              |

| OpenMP_Hello_SYSBIOS                      | 基于 SYSBIOS 的 OpenMP 测试  |

| OpenMP_Matrix-Vector_Multiplication       | 基于 OpenMP 的矩阵-向量乘法      |

| OpenMP_RGB2Gray                           | 基于 OpenMP 的 RGB24 图像转灰度 |

| OpenMP_MPAX                               | 访问相同的逻辑地址               |

| MultiCore_IPC_MessageQ                    | MessageQ 模块通讯测试         |

| MultiCore_IPC_Notify                      | Notify 模块通信测试           |

| MultiCore_IPC_SharedRegion                | SharedRegion 模块通信测试     |

| MultiCore_IPC_Image_Canny                 | 边缘检测                    |

表 15

| 基于广州创龙编写的 RTSC 组件的例程 |                  |

|----------------------|------------------|

| 例程                   | 功能               |

| RTSC_Fan             | 对散热风扇转速进行控制      |

| RTSC_FFT_Real        | 快速傅里叶变换/逆变换      |

| RTSC_UART0_POLL      | UART0 串口查询收发     |

| RTSC_UART1_POLL      | UART1 串口查询收发     |

| RTSC_I2C_TempSensor  | IIC 总线温度传感器测试    |

| RTSC_SysMin          | SysMin 组件的输出调试演示 |

| RTSC_SysStd          | SysStd 组件的输出调试演示 |

| RTSC_LoggerBuf       | 日志输出到缓冲区的演示例程    |

| RTSC_LoggerStd       | 实时输出日志信息的演示例程    |

| RTSC_Benchmark       | 测量代码性能方法         |

| RTSC_UART0_INTERRUPT | UART0 串口中断收发     |

| RTSC_LED             | LED 测试           |

| RTSC_KEY             | 按键测试             |

| RTSC_UART            | 日志输出到缓冲区的演示例程    |

表 16

| FPGA 开发例程 |               |

|-----------|---------------|

| 例程        | 功能            |

| LED       | LED 测试        |

| KEY       | 按键测试          |

| PWM       | PWM 测试        |

| UART      | UART 回环测试     |

| EEPROM    | IIC 总线写入和读取测试 |

| DDR3      | DDR3 的读写测试    |

|                    |                                  |

|--------------------|----------------------------------|

| XADC               | XADC 功能测试                        |

| UDP_DEMO           | UDP 网络通信功能测试                     |

| ADC_AD9613         | AD 测试                            |

| DAC_AD9706         | DA 测试                            |

| PCIE_EP_X2         | PCIE 数据读写功能测试                    |

| GTP_CONNECTION     | GTP 接口回环通讯及信号质量                  |

| FPGA_SRIO          | SRIO 接口数据回环收发测试                  |

| SRIO_2x_FPGA2DSP   | FPGA 与 DSP 的 SRIO 通信测试           |

| SRIO_DSP_2x_SWRITE | FPGA 与 DSP 的 SRIO 通信测试           |

| SRIO_DMA_DSP       | SRIO_DMA 方式收发测试                  |

| SRIO_ADC           | FPGA 与 DSP 的 ADC 通讯测试            |

| PCIE_SGDMA_ADC     | PCIE 传输 ADC 数据测试(SGDMA)          |

| CAMERALINK_VGA     | CameraLink 相机图像采集实时显示 (黑白)       |

| I2C                | I2C 功能测试                         |

| CAMERALINK_OUT     | CameraLink 板间输入输出测试              |

| PCIE_DSP_ADC       | FPGA 与 DSP 的 PCIe 板间以 DMA 方式通讯测试 |

| VGA_TEST           | VGA 视频输出模块测试                     |

| DSP_FPGA_CL_SRIO   | CameraLink 相机图像采集实时边缘处理显示(黑白)    |

| UDP_ADC            | ADC 采集的 UDP 网络通信功能测试             |

| PCIE_DSP           | FPGA 与 DSP 的 PCIe 板间通讯测试         |

| PCIE_SGDMA         | PCIE SGDMA 的传输功能测试               |

| USB_TEST           | USB 模块功能测试                       |