## TL665xF-EasyEVM 开发板硬件说明书

### Revision History

| Draft Date | Revision No. | Description   |

|------------|--------------|---------------|

| 2018/01/25 | V1.1         | 1.修改为 A2 版硬件。 |

| 2017/3/29  | V1.0         | 1.初始版本。       |

创龙

## 目 录

|                     |    |

|---------------------|----|

| 前 言 .....           | 3  |

| 1 处理器 .....         | 4  |

| 2 NAND FLASH .....  | 5  |

| 3 RAM .....         | 5  |

| 4 温度传感器 .....       | 6  |

| 5 EEPROM .....      | 6  |

| 6 NOR FLASH .....   | 7  |

| 7 电源接口和拨码开关 .....   | 8  |

| 8 LED 指示灯 .....     | 9  |

| 9 按键 .....          | 11 |

| 10 启动拨码开关 .....     | 13 |

| 11 JTAG 接口 .....    | 14 |

| 12 串口 .....         | 16 |

| 13 千兆以太网口 .....     | 18 |

| 14 散热风扇接口 .....     | 19 |

| 15 拓展 IO 信号 .....   | 20 |

| 16 FMC 接口 .....     | 23 |

| 17 底板 B2B 连接器 ..... | 24 |

| 18 SRIO 接口 .....    | 27 |

| 19 PCIe 接口 .....    | 28 |

| 20 模式调试接口 .....     | 29 |

| 21 XADC 接口 .....    | 30 |

| 22 SFP 光纤接口 .....   | 31 |

| 23 BANK 电压 .....    | 32 |

| 更多帮助 .....          | 33 |

## 前 言

广州创龙结合 TI KeyStone 系列多核架构 TMS320C665x 及 Xilinx Artix-7 系列 FPGA 设计的 TL665xF-EasyEVM 开发板是一款 DSP+FPGA 高速大数据采集处理平台，其底板采用沉金无铅工艺的 6 层板设计，适用于高端图像处理、软件无线电、雷达声纳、高端数控系统、机器视觉等高速数据处理领域。核心板在内部通过 uPP、EMIF16、SRIO 通信接口将 DSP 与 FPGA 结合在一起，组成 DSP+FPGA 架构，实现了需求独特、灵活、功能强大的 DSP+FPGA 高速数据采集处理系统。

TL665xF-EasyEVM 开发板引出 CPU 全部资源信号引脚，二次开发极其容易，客户只需要专注上层运用，降低了开发难度和时间成本，让产品快速上市，及时抢占市场先机。创龙不仅提供丰富的 Demo 程序，还提供 DSP 核间通信、DSP 与 FPGA 间通讯开发教程以及全面的技术支持，协助客户进行底板设计和调试以及多核软件开发。

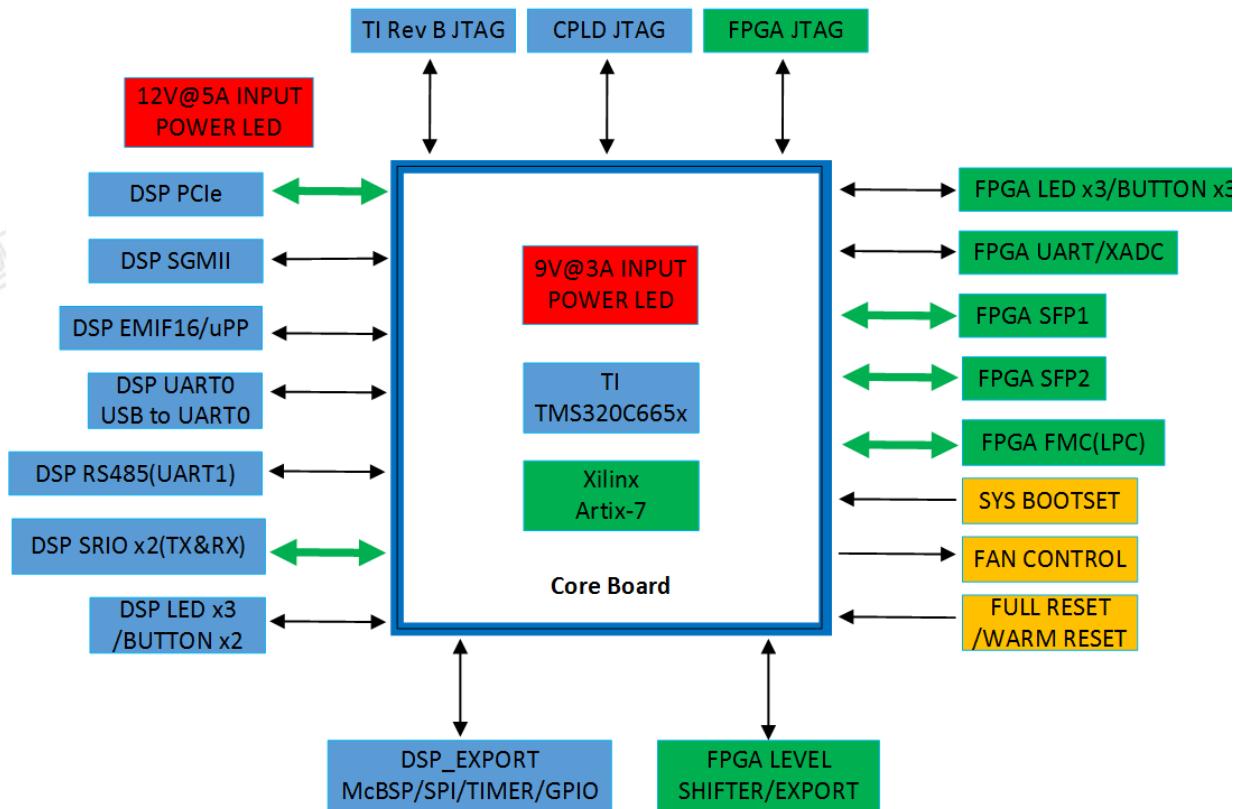

## 1 创龙 TMS320C665x DSP + Artix-7 FPGA 处理器

基于 TI KeyStone C66x 多核定点/浮点 DSP TMS320C665x + Xilinx Artix-7 FPGA 处理器, TMS320C665x 主频为 1.0G/1.25GHz, 单核运算能力高达 40GMACS 和 20GFLOPS, FPGA XC7A100T 逻辑单元 101K 个, DSP Slice 240 个拥有多种工业接口资源, 其 CPU 功能框图:

图 1

图 2

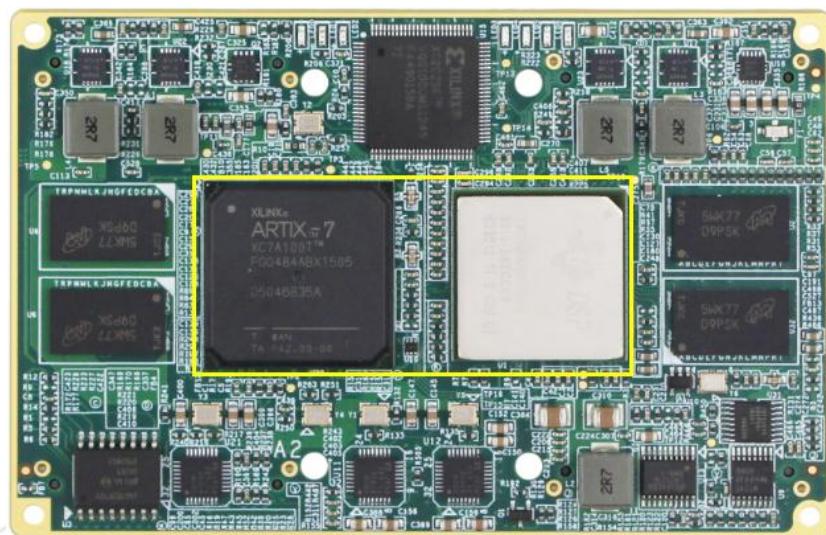

## 2 创龙 TMS320C665x DSP + Artix-7 FPGA NAND FLASH

核心板上采用工业级 NAND FLASH(128MByte)，硬件如下图：

图 3

## 3 创龙 TMS320C665x DSP + Artix-7 FPGA RAM

RAM 采用工业级低功耗 DDR3L，其中 FPGA 和 DSP 均为 512M/1GByte 可选，左边为 FPGA 端的 DDR3，右边为 DSP 端的 DDR3，硬件如下图：

图 4

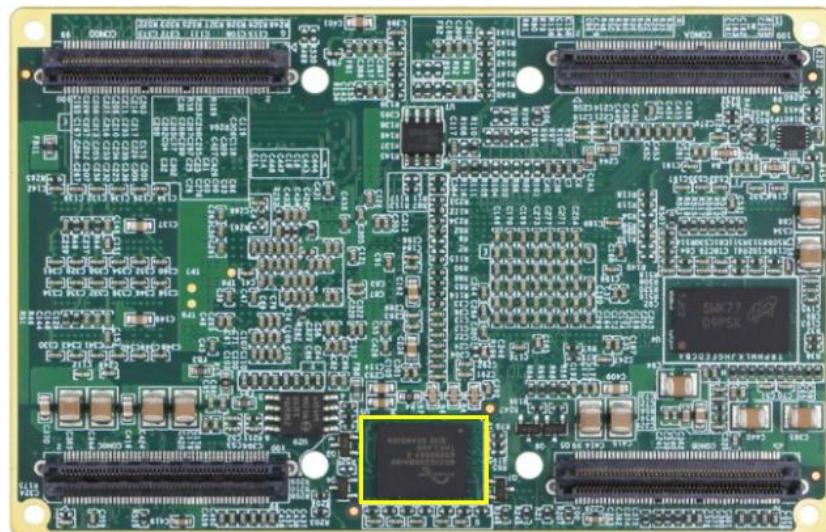

#### 4 创龙 TMS320C665x DSP + Artix-7 FPGA 温度传感器

核心板上采用 I2C 接口的 TMP102 温度传感器，实现了系统温度的实时监测，测量误差 $\leq 2^\circ$ ，测试温度为-40°C 至 125°C，硬件如下图：

图 5

#### 5 创龙 TMS320C665x DSP + Artix-7 FPGA EEPROM

核心板上采用 I2C 接口 1Mbit 大小的工业级 EEPROM，硬件如下图：

创龙

图 6

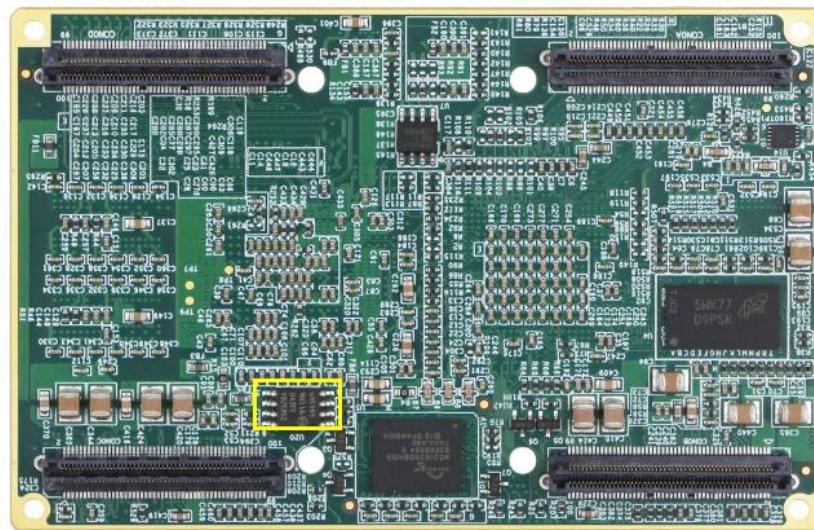

## 6 创龙 TMS320C665x DSP + Artix-7 FPGA NOR FLASH

核心板上 DSP 端使用 128Mbit SPI NOR FLASH , FPGA 端使用 256Mbit SPI NOR FLASH, 如下图所示:

图 7 DSP 端

图 8 FPGA 端

## 7 创龙 TMS320C665x DSP + Artix-7 FPGA 电源接口和拨码开关

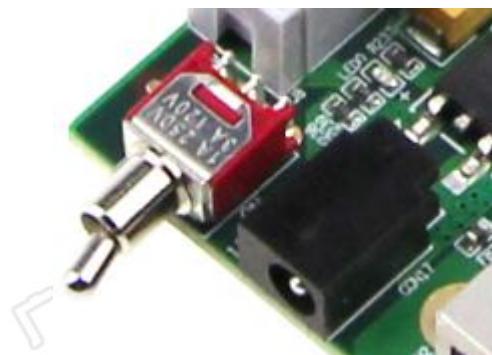

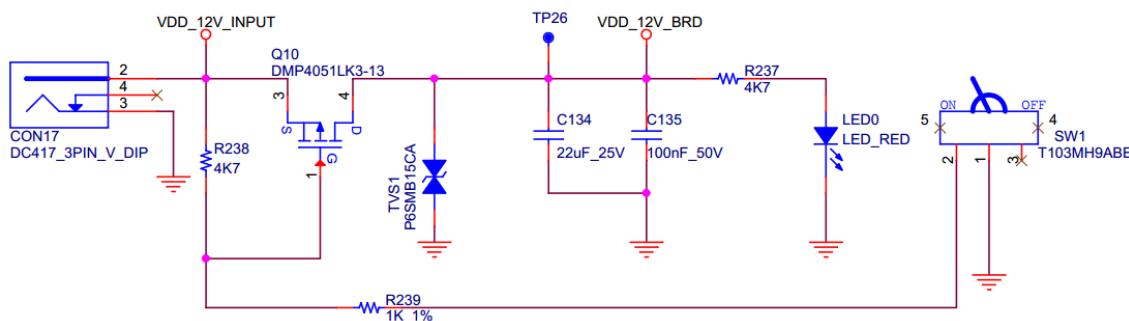

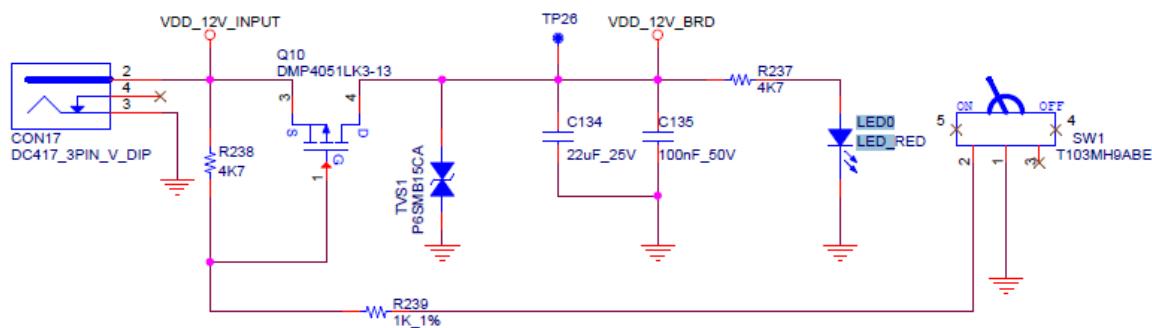

开发板采用 12V@5A 直流电源供电, CON17 为电源接口, SW1 为电源拨码开关, 硬件及引脚定义如下图:

图 9

图 10

## 8 创龙 TMS320C665x DSP + Artix-7 FPGA LED 指示灯

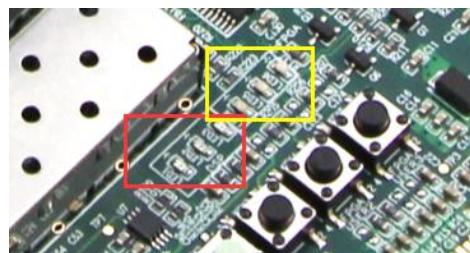

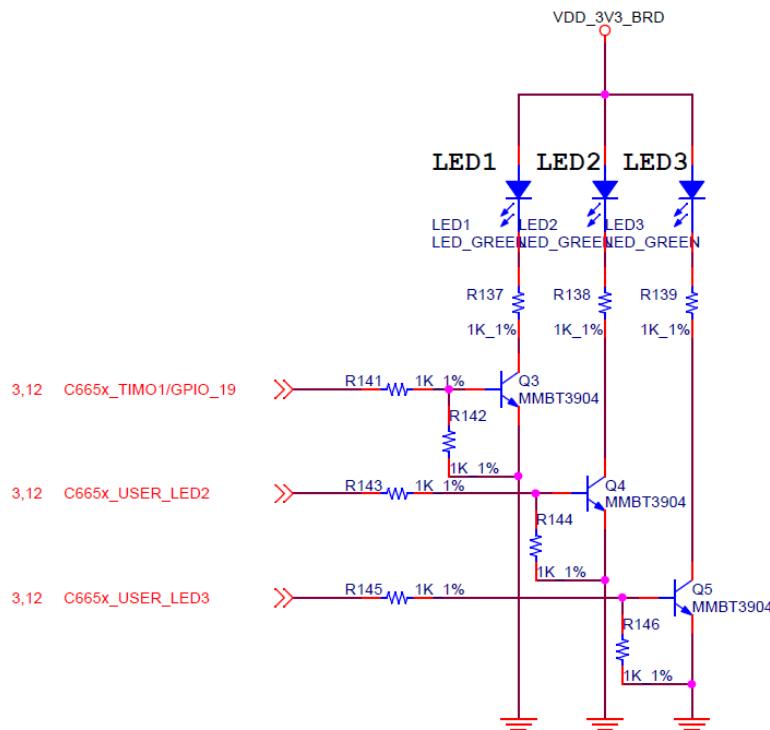

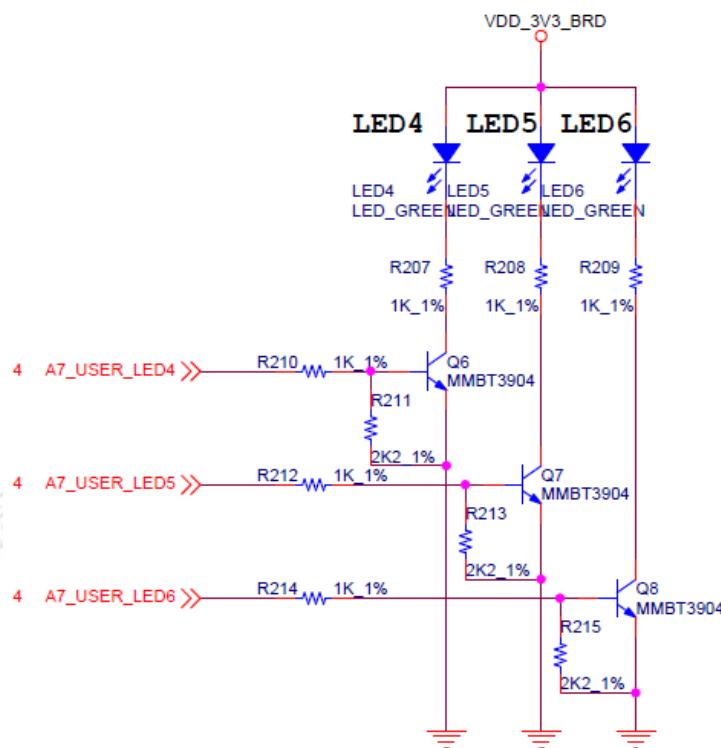

核心板上有 7 个指示灯(LED0~LED6)，LED0 为电源指示灯，LED1~LED2 是 DSP 用户指示灯，LED3~LED6 是 FPGA 用户指示灯（其中 LED5 为 PRO 指示灯）。如下图所示：

图 11

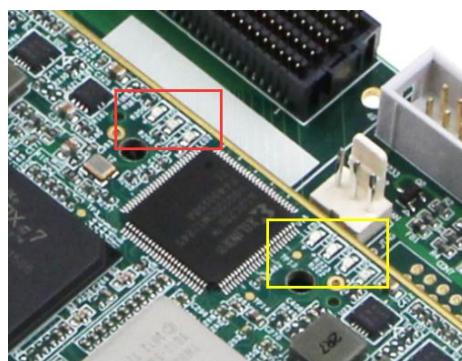

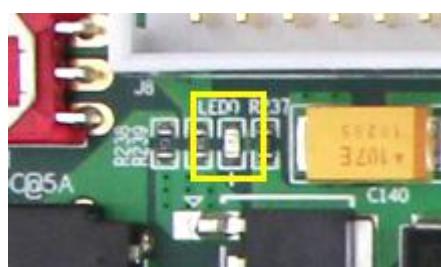

开发板底板有 1 个电源指示灯(LED0)和 6 个可编程用户指示灯(LED1~LED6)。LED1~LED3 是 DSP 用户指示灯，LED4~LED6 是 FPGA 用户指示灯，硬件及引脚定义如下图：

图 12 LED0

图 13 LED0

图 14 USER LED

图 15 底板 DSP 指示灯

图 16 底板 FPGA 指示灯

## 9 创龙 TMS320C665x DSP + Artix-7 FPGA 按键

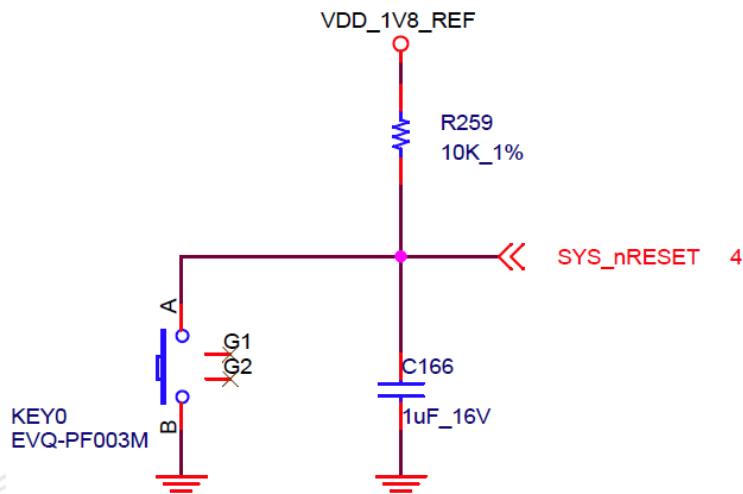

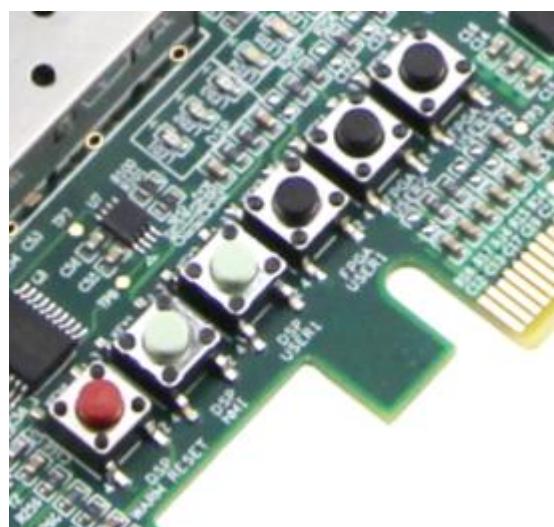

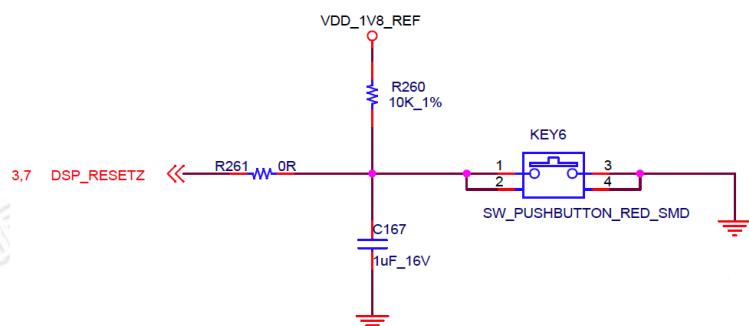

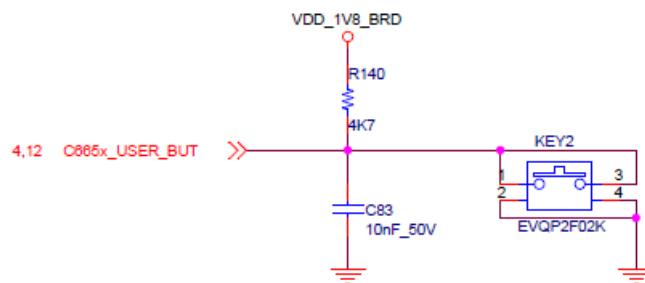

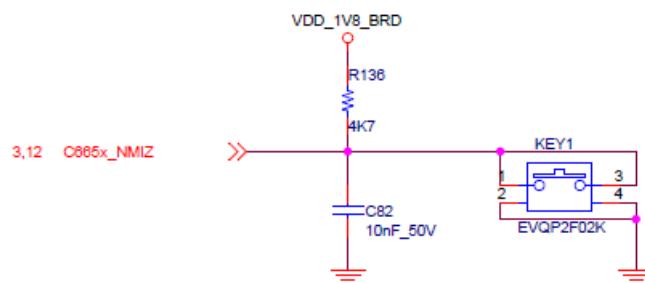

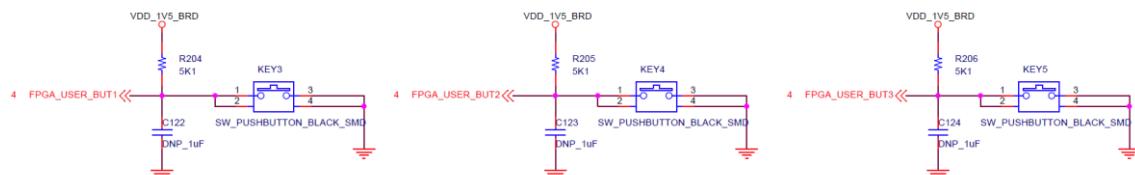

共有 1 个系统复位按键(KEY0: FULL RESET), 1 个热复位按键(KEY6: WARM RESET), 2 个 DSP 端的用户按键(KEY1: NMI, KEY2: USER0), 3 个 FPGA 端的用户按键(KEY3: USER1, KEY4: USER2; KEY5: USER3), 硬件及引脚定义如下图:

图 17 FULL RESET

图 18 系统复位按键

图 19 各按键对应位置

图 20 热复位按钮

图 21 DSP 端的用户按键

图 22 FPGA 端的用户按键

## 10 创龙 TMS320C665x DSP + Artix-7 FPGA 启动拨码开关

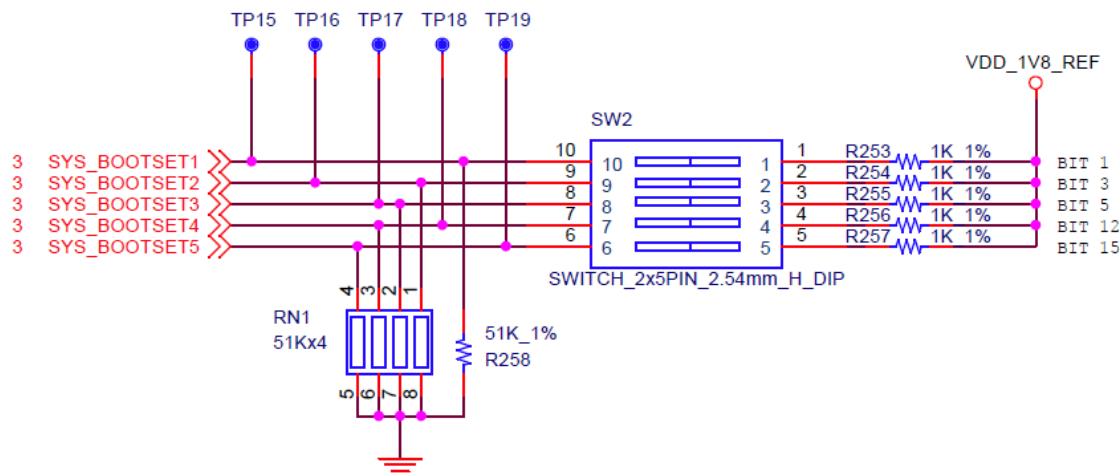

SW2 设有 5 位启动拨码开关, 如下图方向放置, 当拨码拨至 ON 的一端表示为 1, 硬件及引脚定义如下图:

图 23

## Boot Configuration

| MODULE       | SWH | 1 | 2 | 3 | 4 | 5 |

|--------------|-----|---|---|---|---|---|

| DSP_No Boot  |     | 0 | 0 | 0 | X | X |

| DSP_IBL NOR  |     | 1 | 0 | 0 | X | X |

| DSP_IBL NAND |     | 1 | 1 | 0 | X | X |

| DSP_NOR      |     | 1 | 1 | 1 | X | X |

| DSP_PCIE EP  |     | 1 | 0 | 1 | X | X |

| DSP_PCIE T   |     | X | X | X | 1 | X |

| DSP CFG FPGA |     | X | X | X | X | 1 |

P.S:ON = 1 , OFF = 0 ,Don't Care = X

图 24

图 25

## 11 创龙 TMS320C665x DSP + Artix-7 FPGA JTAG 接口

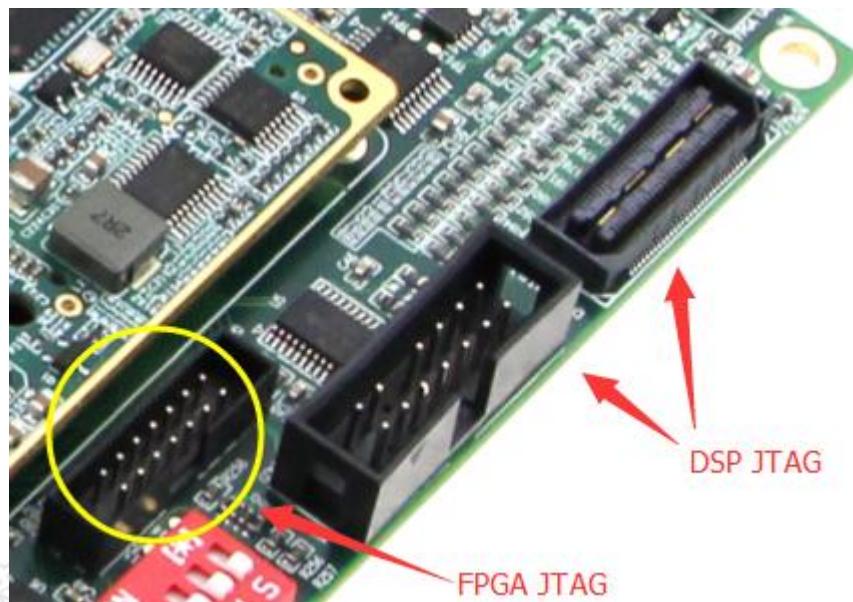

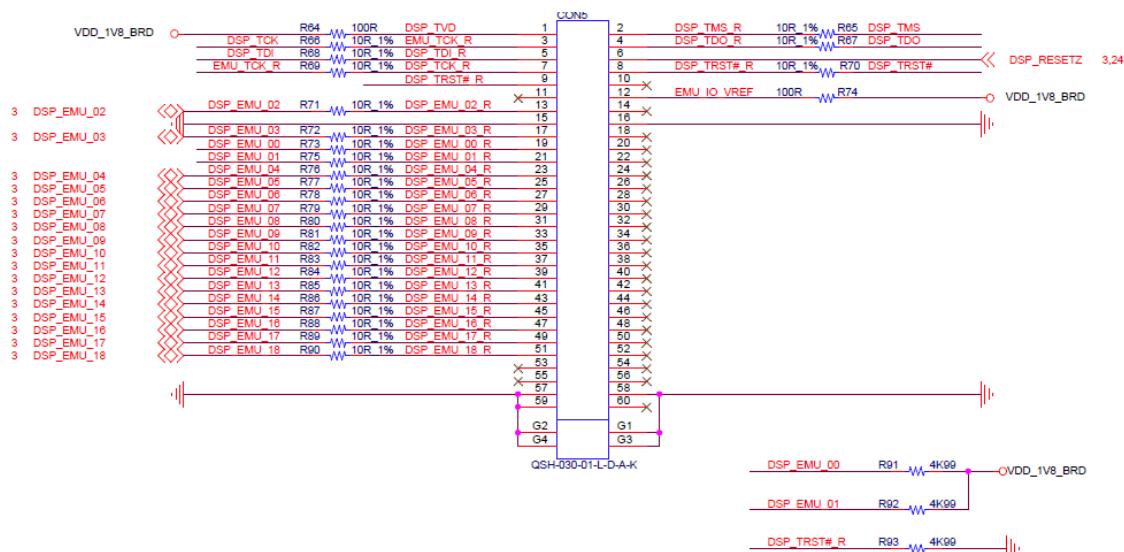

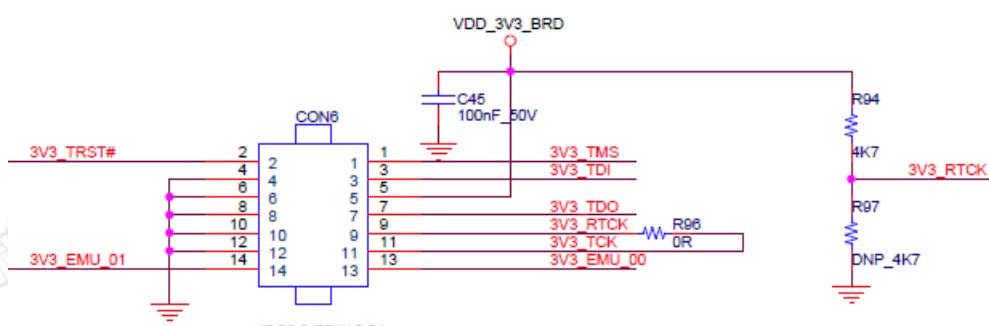

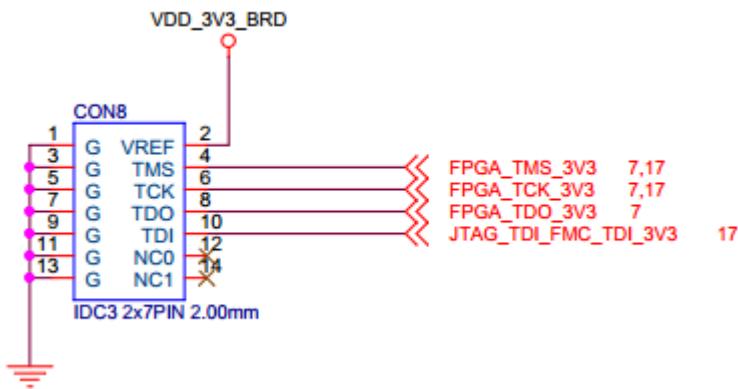

开发板引出 3 个 JTAG 接口，DSP 端 2 个(CON5:MIPI、CON6:TI Rev B JTAG)，FPGA 端 1 个(CON8:FPGA JTAG)，硬件及引脚定义如下图：

图 26

图 27 MIPI

图 28 TI Rev B JTAG

创龙

图 29 FPGA JTAG

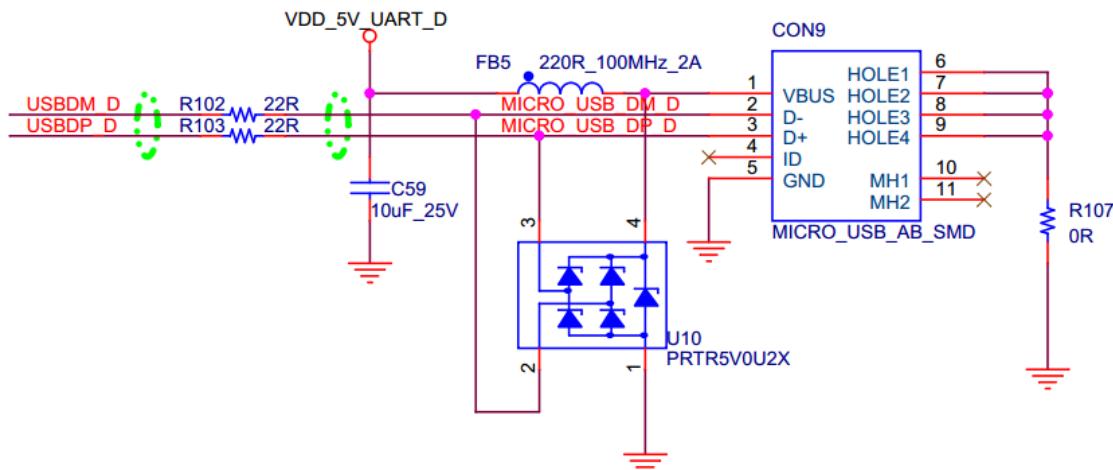

## 12 创龙 TMS320C665x DSP + Artix-7 FPGA 串口

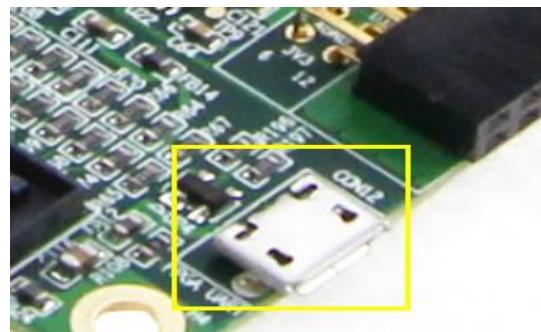

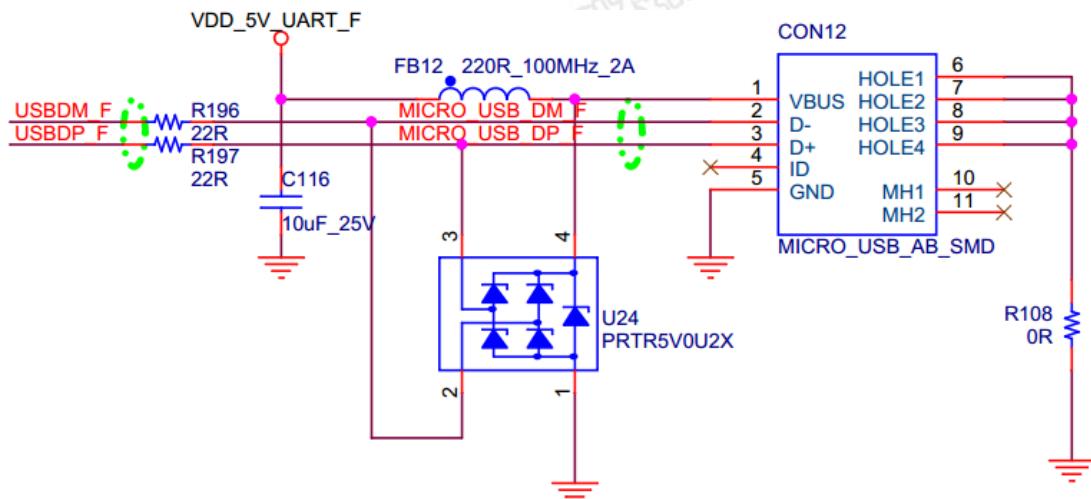

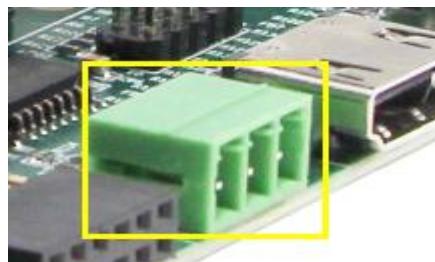

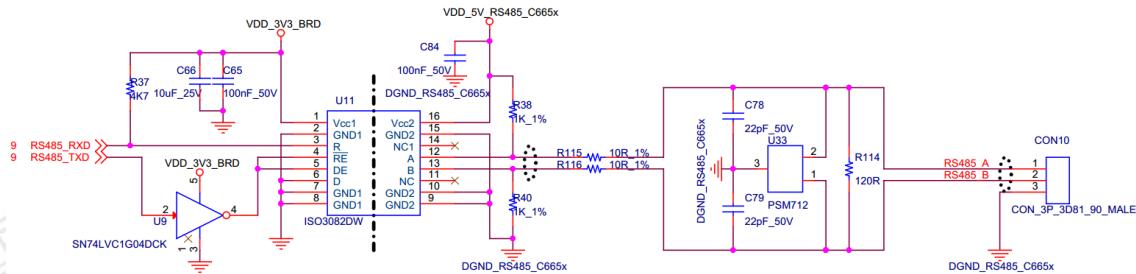

开发板上共引出了 3 个串口，分别是 CON9、CON10 和 CON12。DSP 端 2 个，CON9 是 UART0，使用 CH340 转成 Micro USB 接口；CON10 是 UART1，为 RS485 串口。FPGA 端 1 个，CON12 是 UART，使用 CH340 转成 Micro USB 接口，硬件及引脚定义如下图：

图 30 DSP 端串口

图 31

图 32 FPGA 端串口

图 33

图 34 DSP RS485

图 35

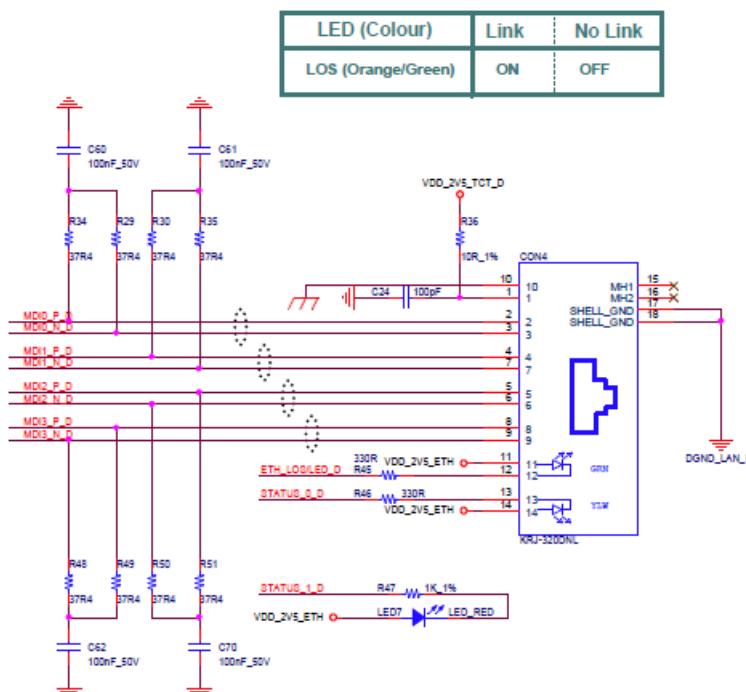

### 13 创龙 TMS320C665x DSP + Artix-7 FPGA 千兆以太网口

开发板引出一个 RJ45 千兆以太网口(CON4)，采用了 Marvell Alaska 88E1112 网络芯片，可自适应 10/100/1000M 网络，RJ45 连接头内部已经包含了耦合线圈，因此不必另接网络变压器，使用普通的直连网线即可连接本开发板至路由器或者交换机，若是 PC 和开发板直接相连需要使用交叉网线。硬件及引脚定义如下图：

图 36

图 37 DSP 端网络接口

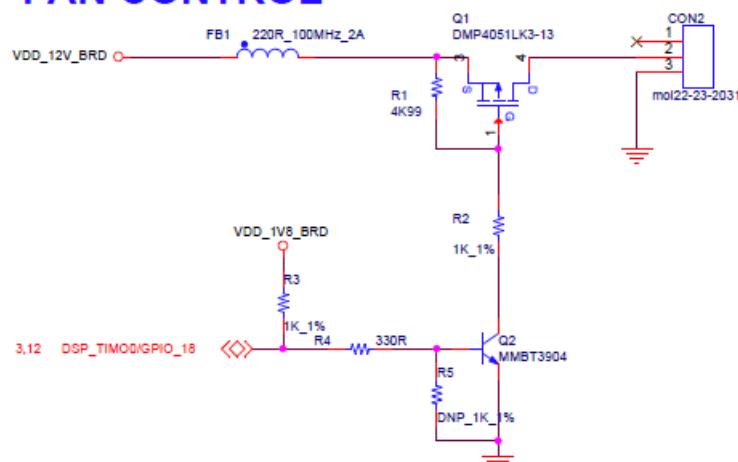

## 14 创龙 TMS320C665x DSP + Artix-7 FPGA 散热风扇接口

CON2 是散热风扇接口，采用 3pin，间距 2.54mm，供电电压为 12V。硬件及引脚定义如下图：

图 38

## FAN CONTROL

图 39

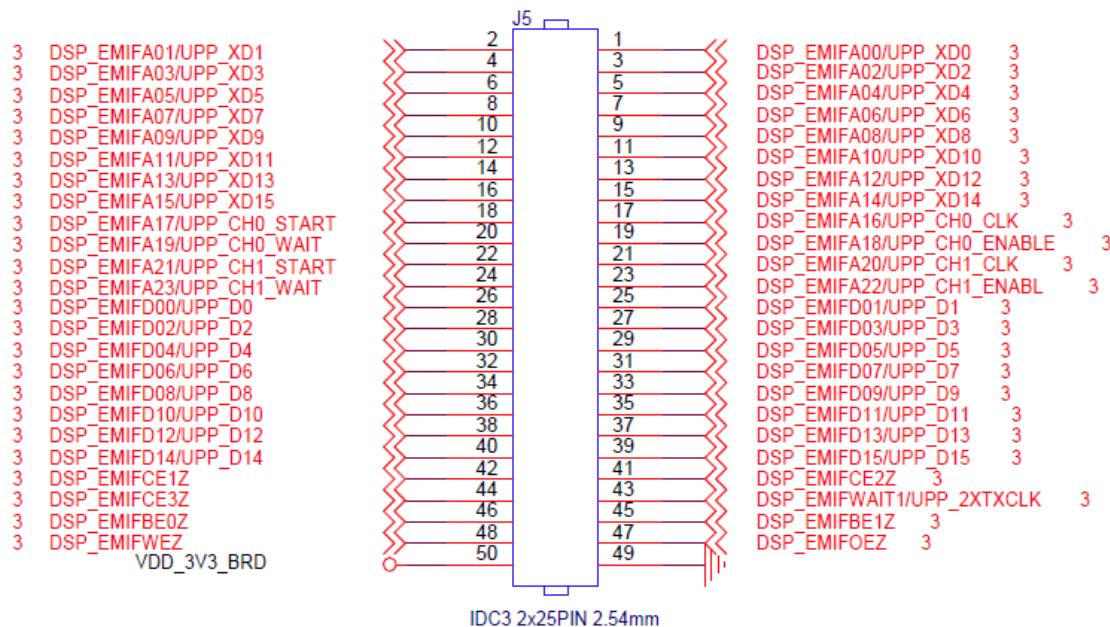

15 创龙 TMS320C665x DSP + Artix-7 FPGA 拓展 IO 信号

(1) J5以50pin、2.54mm间距IDC3简易牛角座引出了EMIF16、uPP拓展信号，硬件及引脚定义如下图：

图 40

IDC3 2x25PIN 2.54mm

图 41

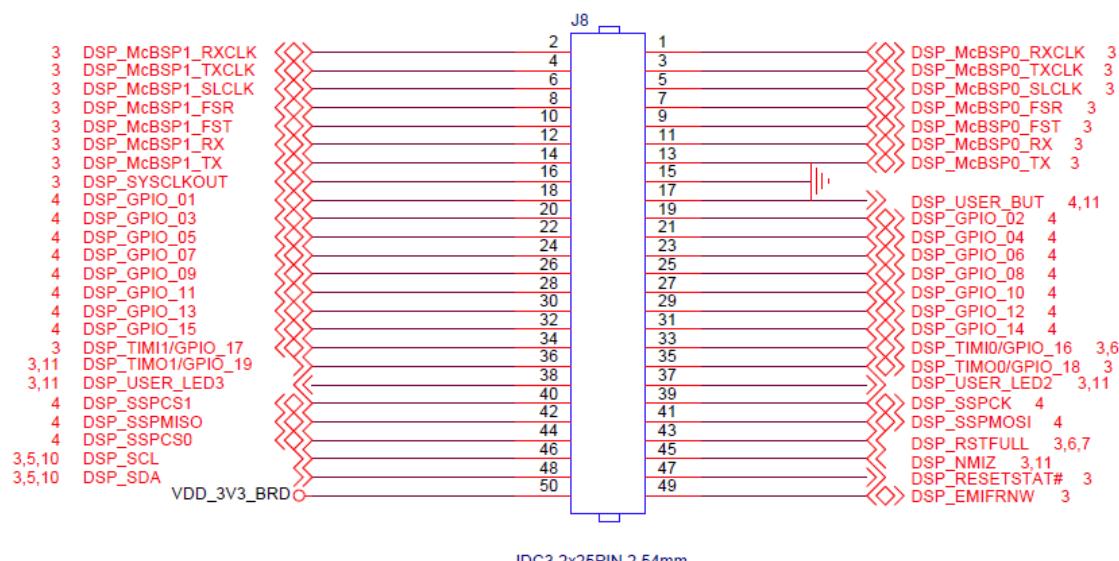

(2) J8以50pin、2.54mm间距IDC3简易牛角座引出了McBSP、SPI、TIMER、GPIO等拓展信号，硬件及引脚定义如下图：

图 42

图 43

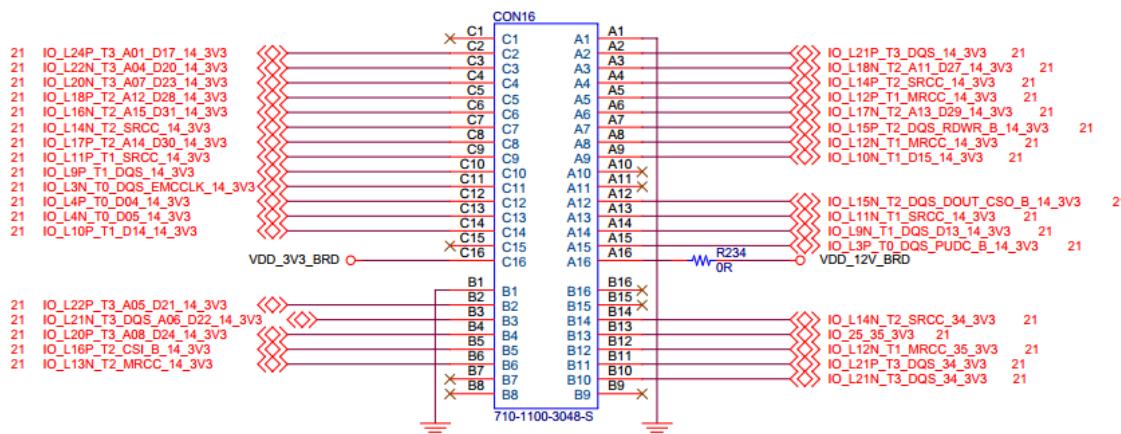

(3) 欧式连接器 CON16 (FPGA 端) 引出 GPIO 等拓展信号, 硬件及引脚定义如下图:

图 44

图 45

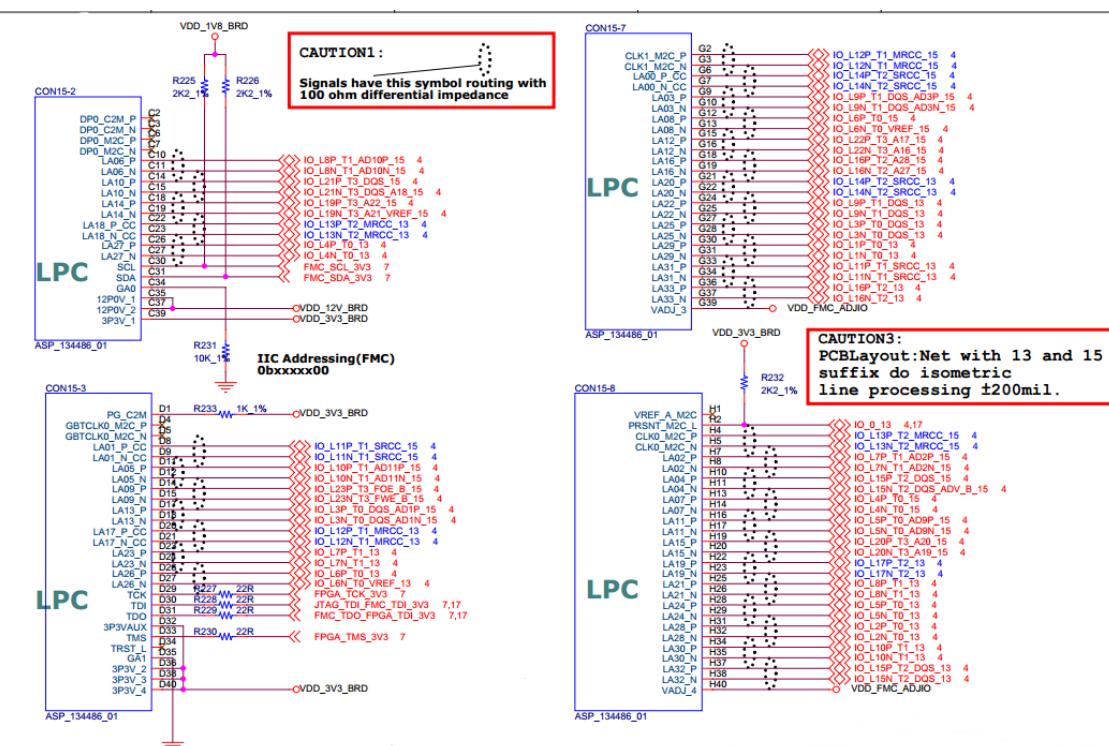

## 16 创龙 TMS320C665x DSP + Artix-7 FPGA FMC 接口

开发板上引出了 1 个工业级 FPGA FMC 连接器(CON15), FMC-LPC 标准。支持高速 A DC、DAC 和视频输入输出, 硬件及引脚定义如下图:

图 46

图 47

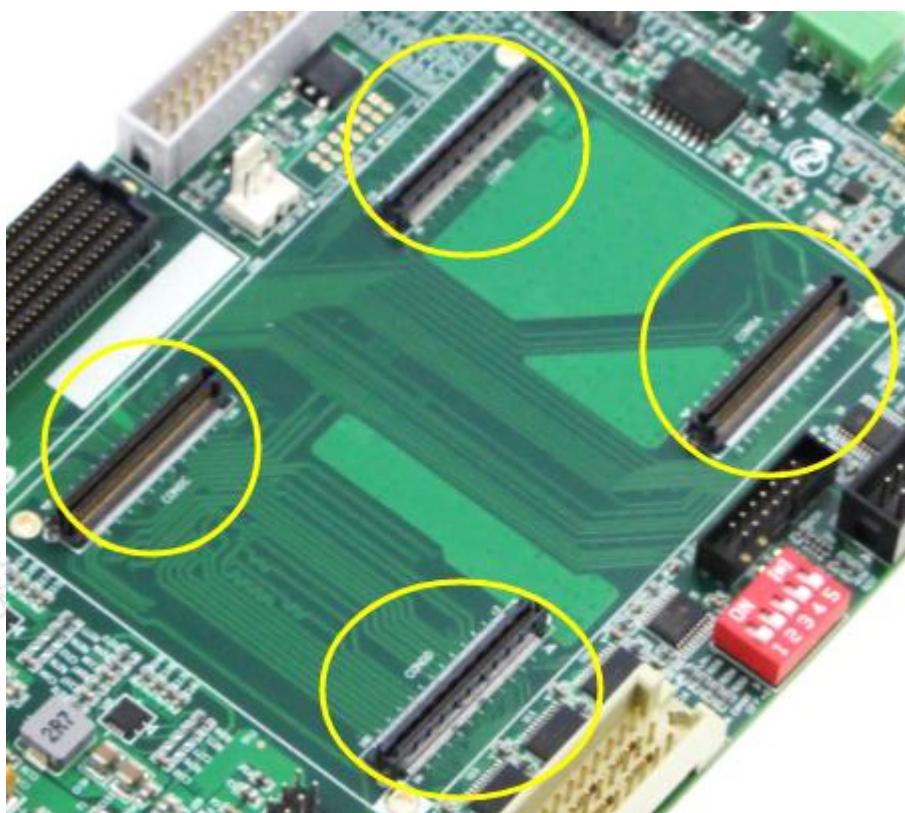

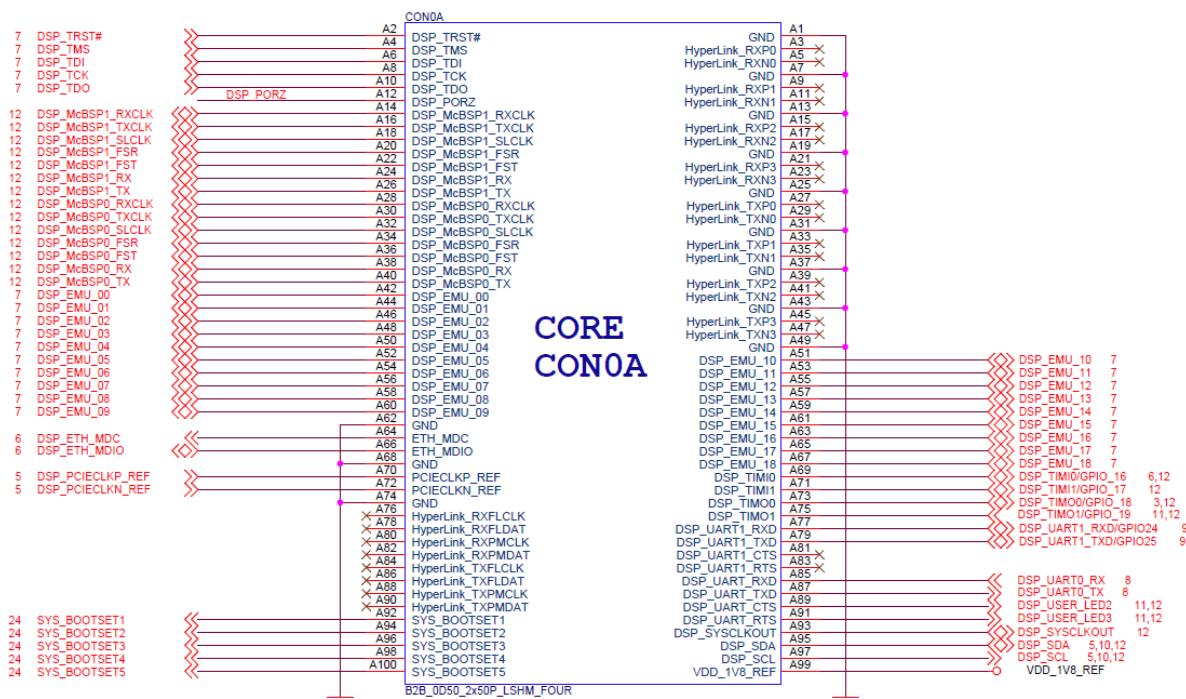

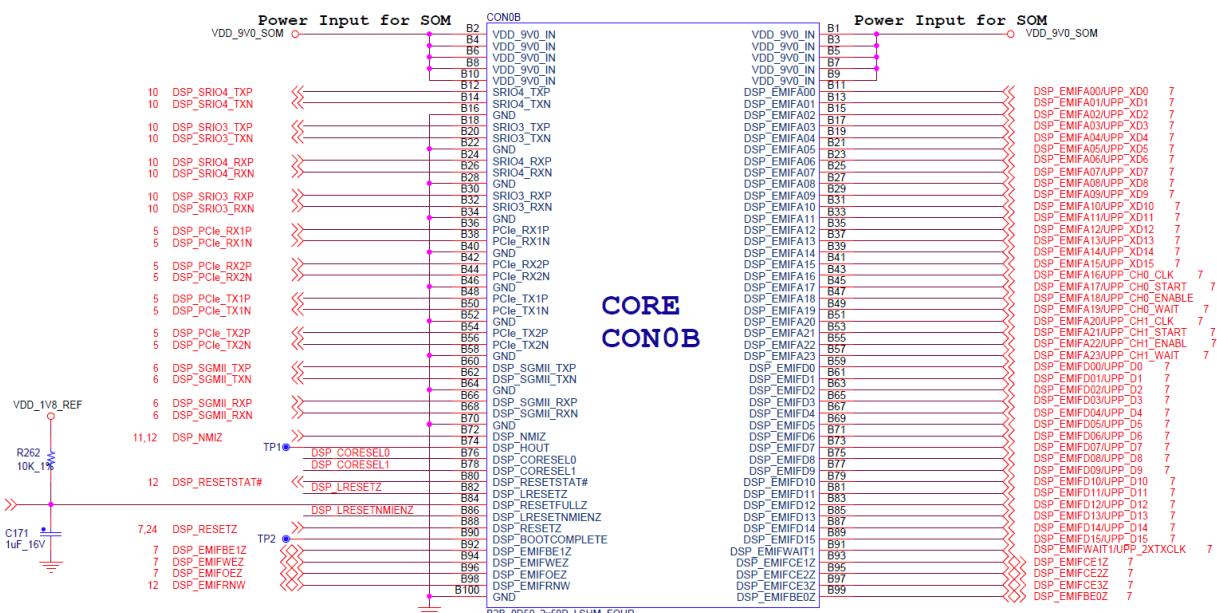

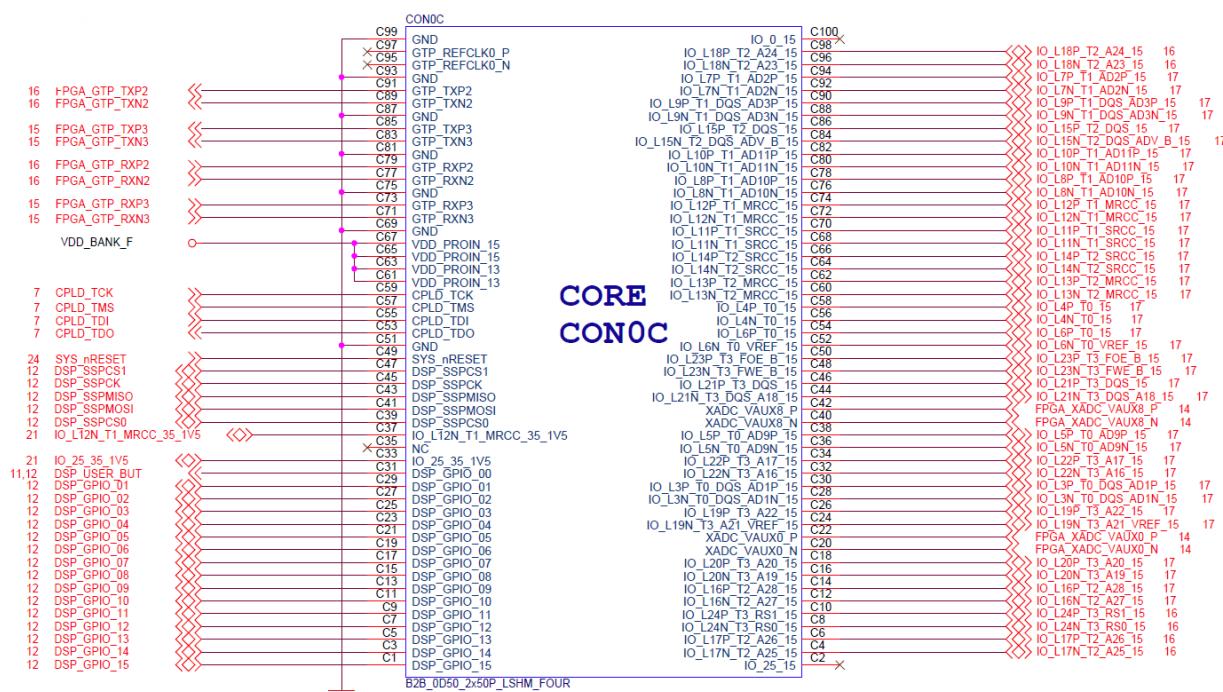

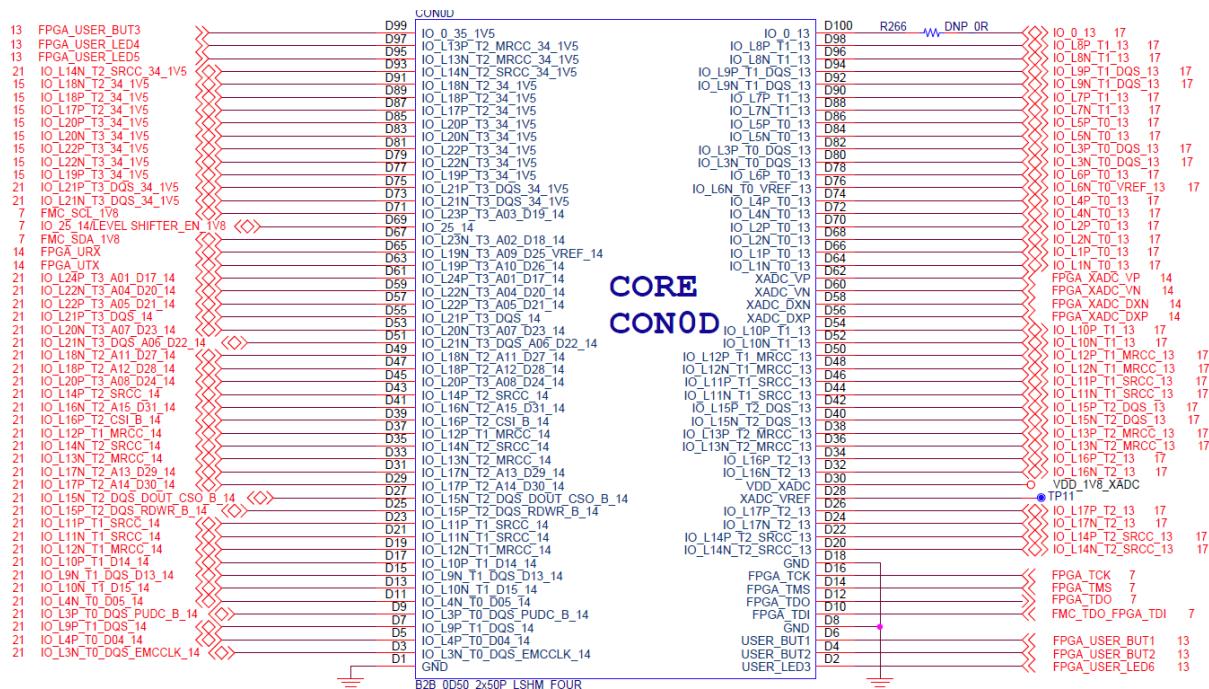

## 17 创龙 TMS320C665x DSP + Artix-7 FPGA 底板 B2B 连接器

开发板使用底板+核心板设计模式，底板共有 4 个高速 B2B 连接器，传输速率可高达 10GBaud，4 x100pin，0.5mm 间距，合高 5.0mm。硬件及引脚定义如下图：

图 48

图 49 CON0A 连接器

图 50 CONOB 连接器

图 51 CONOC 连接器

图 52 CON1D 连接器

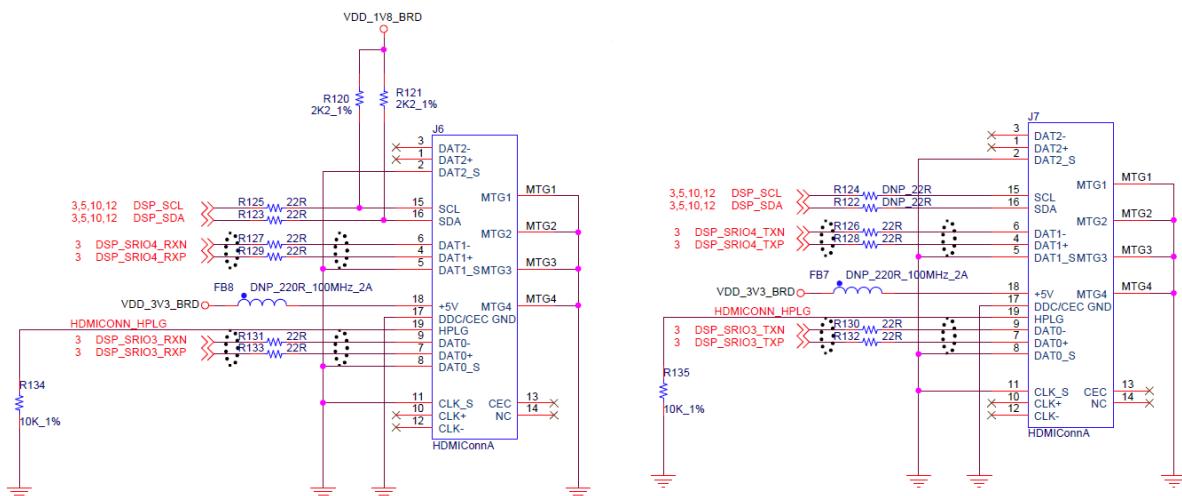

18 创龙 TMS320C665x DSP + Artix-7 FPGA SRIO 接口

SRI0 由 SRI0 RX(J6)和 SRI0 TX(J7)组成 (DSP 端) , 以 2 个 HDMI 接口形式引出, 支持 4 路数据传输, 最高传输速率为 5GBaud, 硬件及引脚定义如下图:

图 53

图 54

## 19 创龙 TMS320C665x DSP + Artix-7 FPGA PCIe 接口

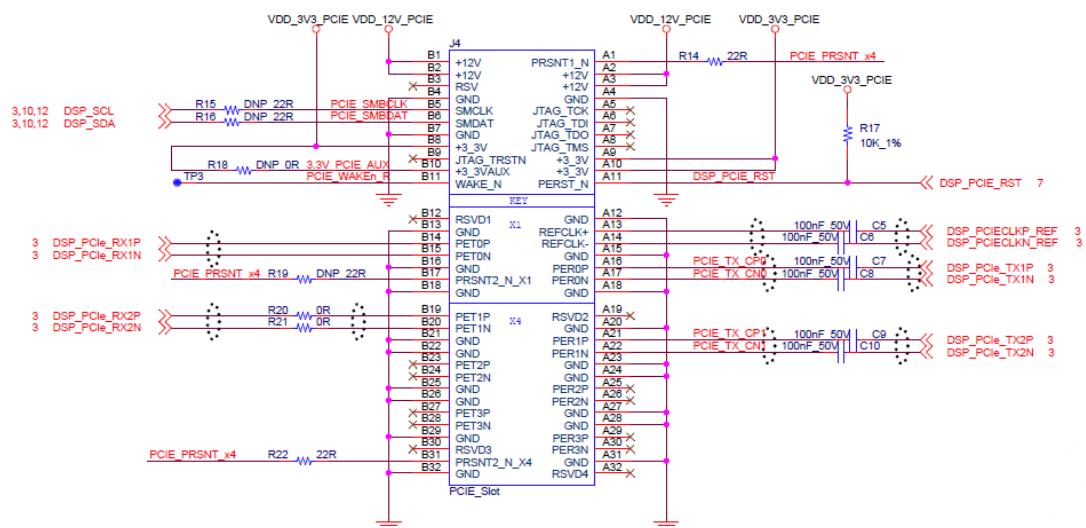

开发板引出了 PCIe Gen2 接口(J4), 2 通道, 编码方案为 8b/10b, 总共 64pin, 主接口区 42pin, 单通道理论最高传输速率达 5GBaud, 总传输速率为  $5\text{GBaud} \times 8/10 = 8\text{Gbit/s}$ , 硬件及引脚定义如下图:

图 55

图 56

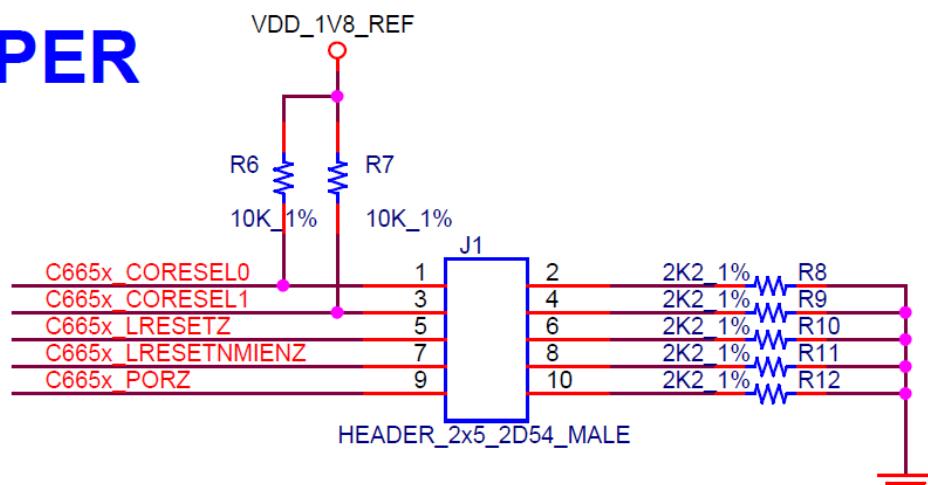

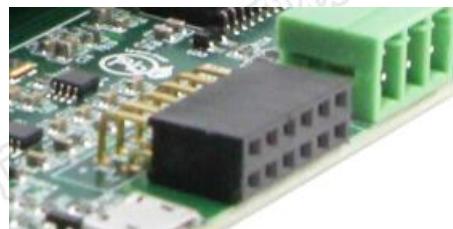

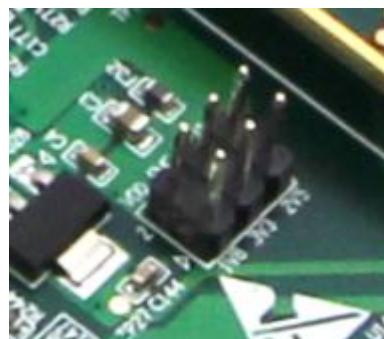

## 20 创龙 TMS320C665x DSP + Artix-7 FPGA 模式调试接口

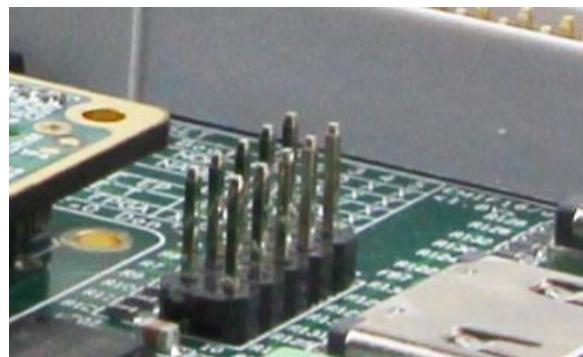

开发板 J1 为模式调试接口，采用 2\*5pin、2.54mm 间距双排针连接方式，主要用于复位、NMI 等调试，硬件及引脚定义如下图：

图 57

# JUMPER

图 58

CORESEL0/CORESEL1: 核心选择管脚, 用于选择启动或者复位的核心。

LRESETZ: Warm Retset 软复位管脚。

LRESETNMIENZ: 模式选择使能管脚。

PORZ: 上电复位管脚, 用于上电时的复位行为。

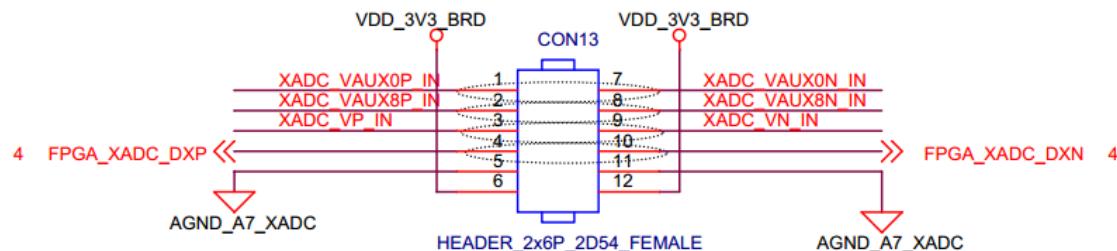

## 21 创龙 TMS320C665x DSP + Artix-7 FPGA XADC 接口

开发板引出了 FPGA 内部 XADC 信号(CON13), 硬件及引脚定义如下图:

图 59

图 60

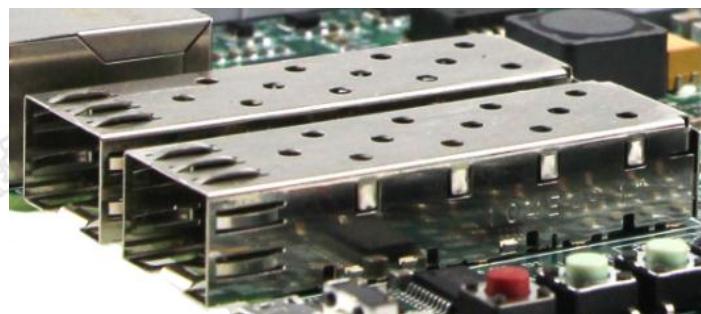

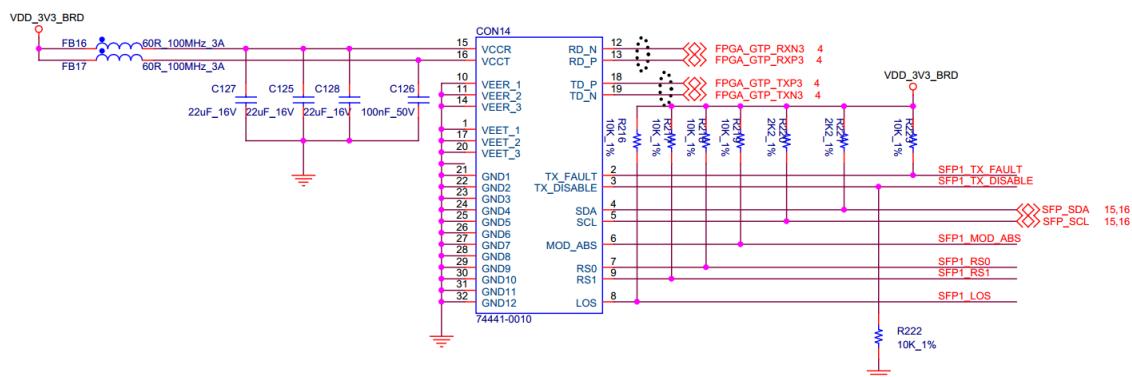

## 22 创龙 TMS320C665x DSP + Artix-7 FPGA SFP 光纤接口

SFP 光纤接口由 SFP1(CON14)和 SFP2(CON19)组成 (FPGA 端) , 传输速率可高达 5Gbit/s, 硬件及引脚定义如下图:

图 61

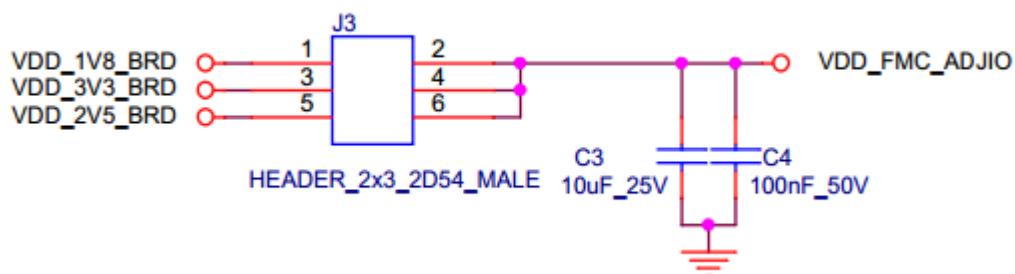

## 23 创龙 TMS320C665x DSP + Artix-7 FPGA BANK 电压

开发板引出一个 BANK 电压 (J3, FPGA 端) , 1.8V、2.5V 以及 3.3V 可选, 硬件及引脚定义如下图:

图 64

图 65

**创龙 TMS320C665x DSP + Artix-7 FPGA 更多帮助**

销售邮箱: [sales@tronlong.com](mailto:sales@tronlong.com)

技术邮箱: [support@tronlong.com](mailto:support@tronlong.com)

创龙总机: 020-8998-6280

技术热线: 020-3893-9734

创龙官网: [www.tronlong.com](http://www.tronlong.com)

技术论坛: [www.51ele.net](http://www.51ele.net)

线上商城: <https://tronlong.taobao.com>