**Tronlong®**

# TL6678F-EasyEVM

## 开发板硬件说明书

**广州创龙电子科技有限公司**

© 2013 Guangzhou Tronlong Electronic Technology Co.,Ltd.

## TL6678F-EasyEVM 开发板硬件说明书

### 前 言

TL6678F-EasyEVM 是广州创龙基于 SOM-TL6678F 核心板而研发的一款多核高性能 DSP+FPGA 开发板。开发板采用核心板+底板方式，底板采用沉金无铅工艺的 8 层板设计，尺寸为 247.33mm\*139.8mm，它为用户提供了 SOM-TL6678F 核心板的测试平台。为了方便用户开发和参考使用，上面引出了各种常见的接口，可以帮助用户快速评估 SOM-TL6678F 核心板的整体性能。

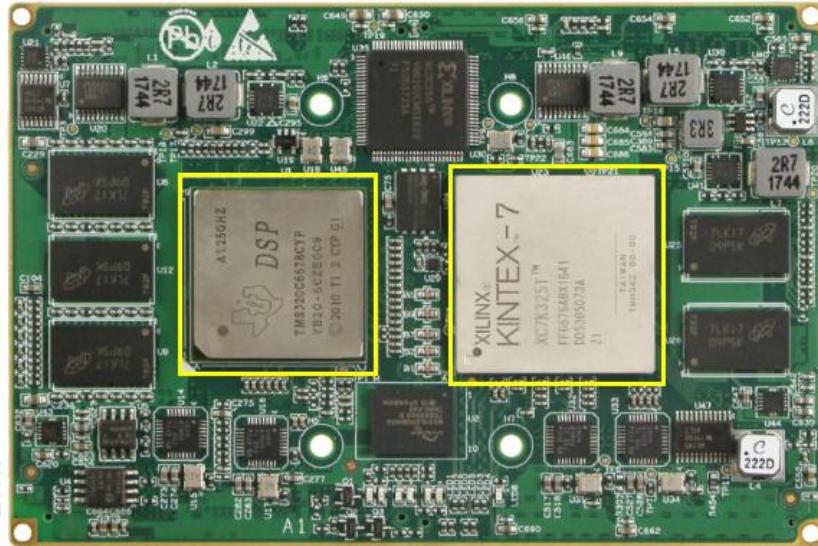

广州创龙 SOM-TL6678F 核心板基于 TI KeyStone C66x 多核定点/浮点 TMS3206678 + Xilinx Kintex-7 FPGA 设计的高性能 DSP+FPGA 高速大数据采集处理器，采用沉金无铅工艺的 14 层板设计，尺寸为 112mm\*75mm，经过专业的 PCB Layout 保证信号的完整性，和经过严格的质量管控，满足多种环境应用。

## 1 详解基于创龙 TI DSP TMS320C6678 + Xilinx FPGA Kintex-7 的处理器

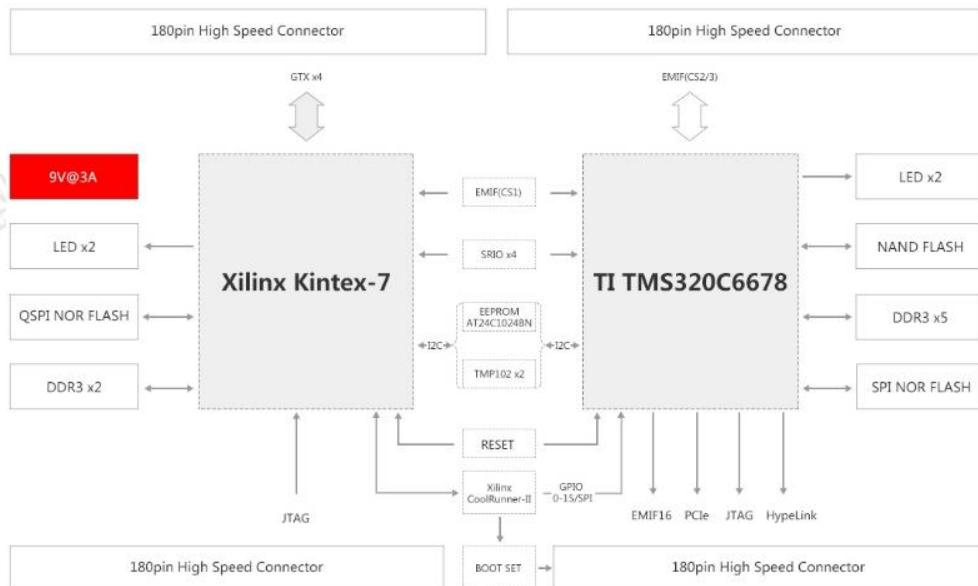

基于 TI KeyStone C66x 多核定点/浮点 DSP TMS320C6678 + Xilinx Kintex-7 FPGA 的高性能信号处理器，TI TMS320C6678 集成 8 核 C66x，每核主频 1.0/1.25GHz，每核运算能力高达 40GMACS 和 20GFLOPS，FPGA XC7K325T 逻辑单元 326K 个，DSP Slice 840 个，8 对速率为 12.5Gb/s 高速串行收发器，以下是 CPU 功能框图：

图 1 功能框图

图 2

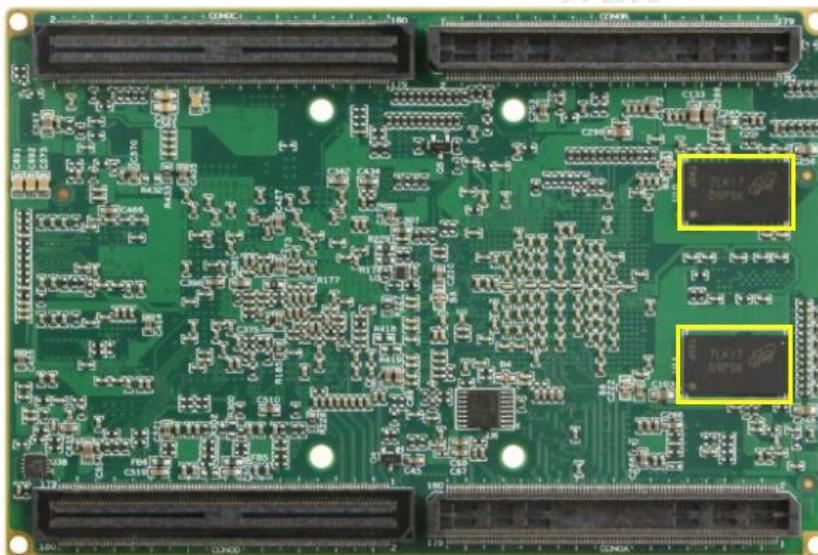

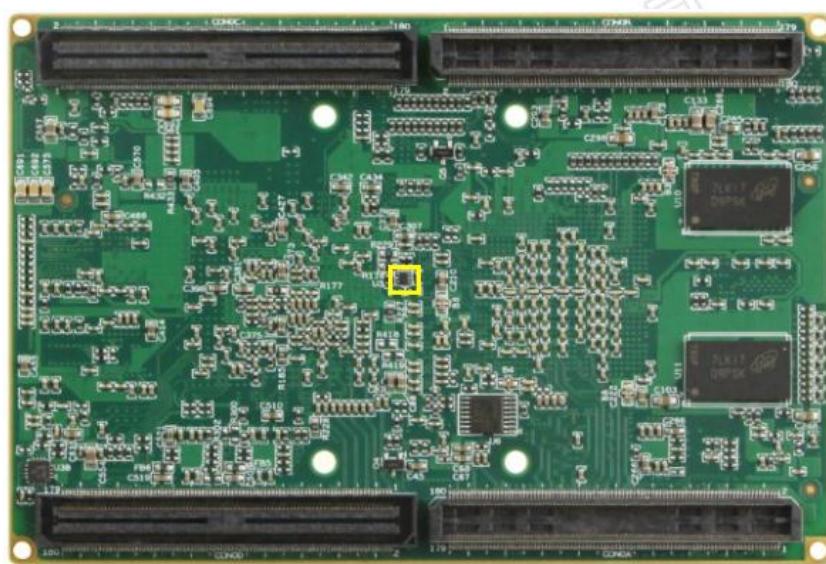

## 2 详解基于创龙 TI DSP TMS320C6678 + Xilinx FPGA Kintex-7 的 NAND FLASH

核心板上采用工业级 NAND FLASH, DSP 端 128MByte, 硬件如下图:

#### 4 详解基于创龙 TI DSP TMS320C6678 + Xilinx FPGA Kintex-7 的 RAM

RAM 采用工业级低功耗 DDR3L，DSP 端 1/2Gbyte 可选，FPGA 端 512M/1Gbyte 可选，硬件如下图：

图 5 DSP 端 DDR 图 1

图 6 DSP 端 DDR 图 2

图 7 FPGA 端 DDR

## 5 详解基于创龙 TI DSP TMS320C6678 + Xilinx FPGA Kintex-7 的 EEPROM

核心板上采用 I2C 接口 1Mbit 大小的工业级 EEPROM，硬件如下图：

图 8

## 6 详解基于创龙 TI DSP TMS320C6678 + Xilinx FPGA Kintex-7 的 ECC

RAM 采用工业级低功耗 DDR3L，DSP 端 256M/512MByte 可选，硬件如下图：

图 9

## 7 详解基于创龙 TI DSP TMS320C6678 + Xilinx FPGA Kintex-7 的温度传感器

核心板上有 2 个采用 I2C 接口的 TMP102 温度传感器，DSP 端 1 个，FPGA 端 1 个，实现了系统温度的实时监测，测量误差 $\leq 2^{\circ}\text{C}$ ，测试温度为 $-40^{\circ}\text{C}$ 至 $125^{\circ}\text{C}$ ，硬件如下图：

图 10 DSP 端温度传感器

图 11 FPGA 端温度传感器

## 8 详解基于创龙 TI DSP TMS320C6678 + Xilinx FPGA Kintex-7 的 B2B 连接器

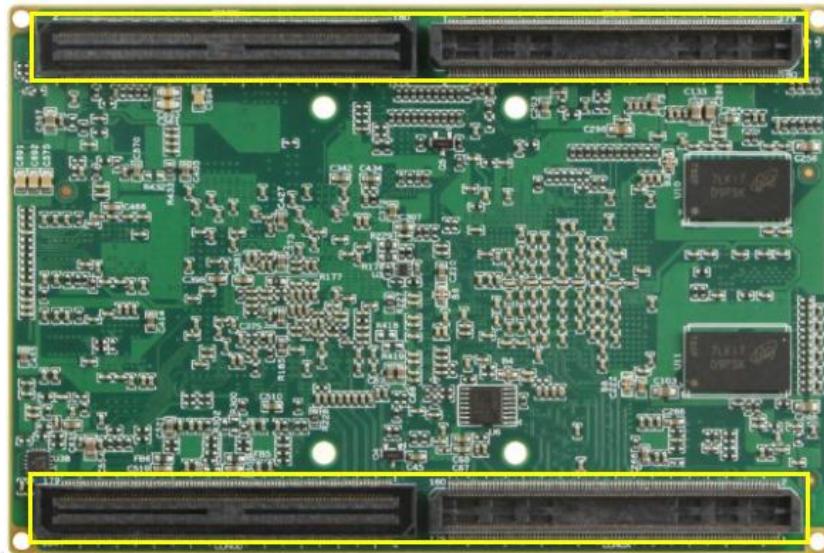

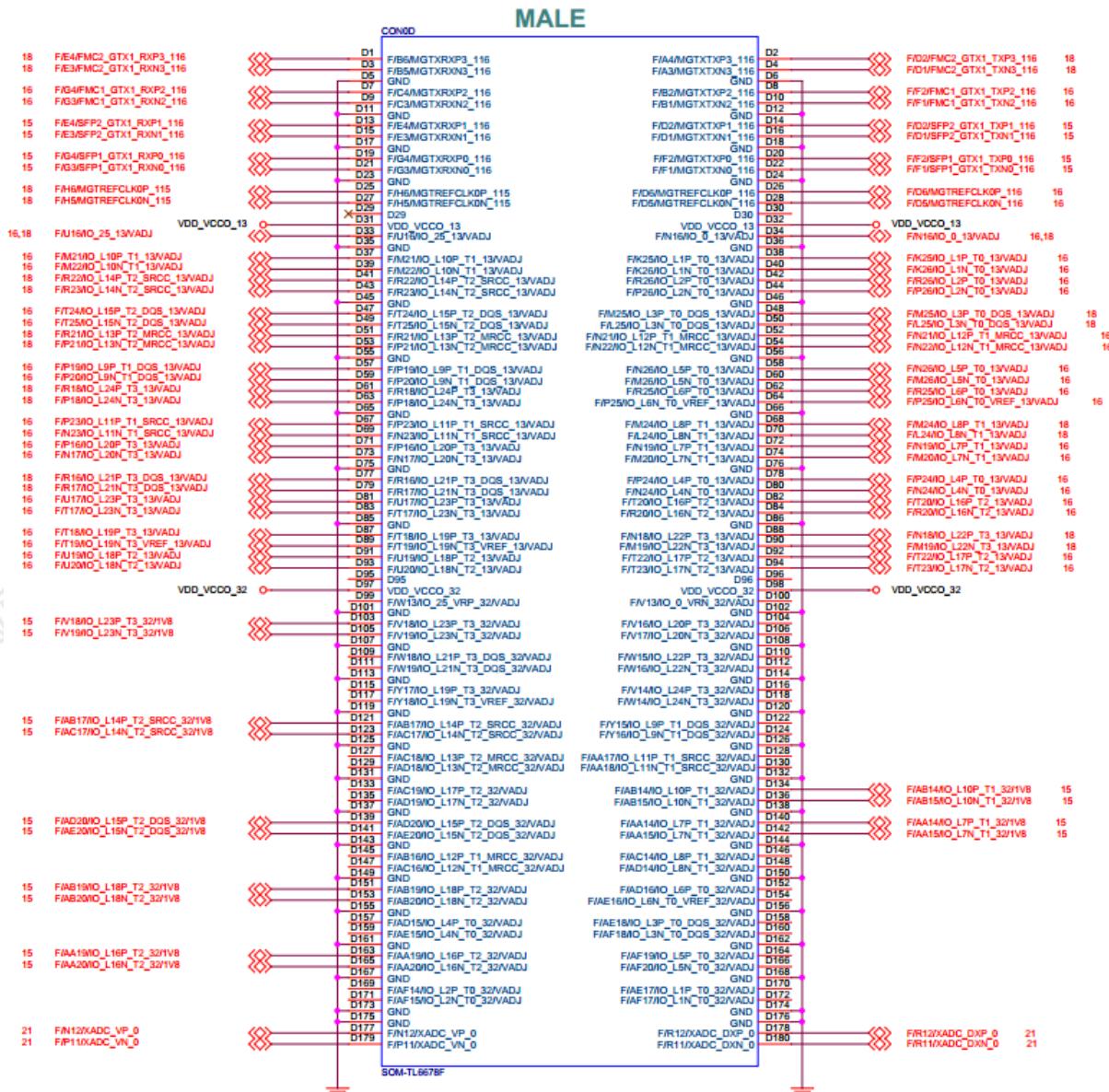

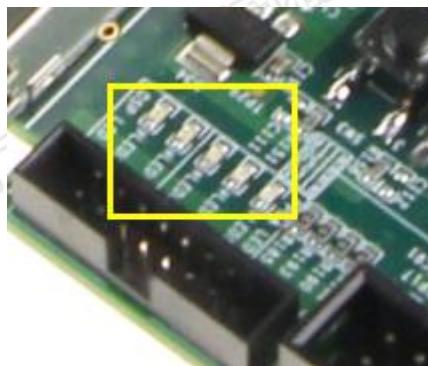

开发板使用底板+核心板设计模式，底板和核心板各有 4 个 B2B 高速连接器，均为 180pin, 0.5mm 间距，合高 5.0mm 连接器，传输速率可高达 10GBaud，硬件及引脚定义如下图：

图 12 核心板 B2B 连接器

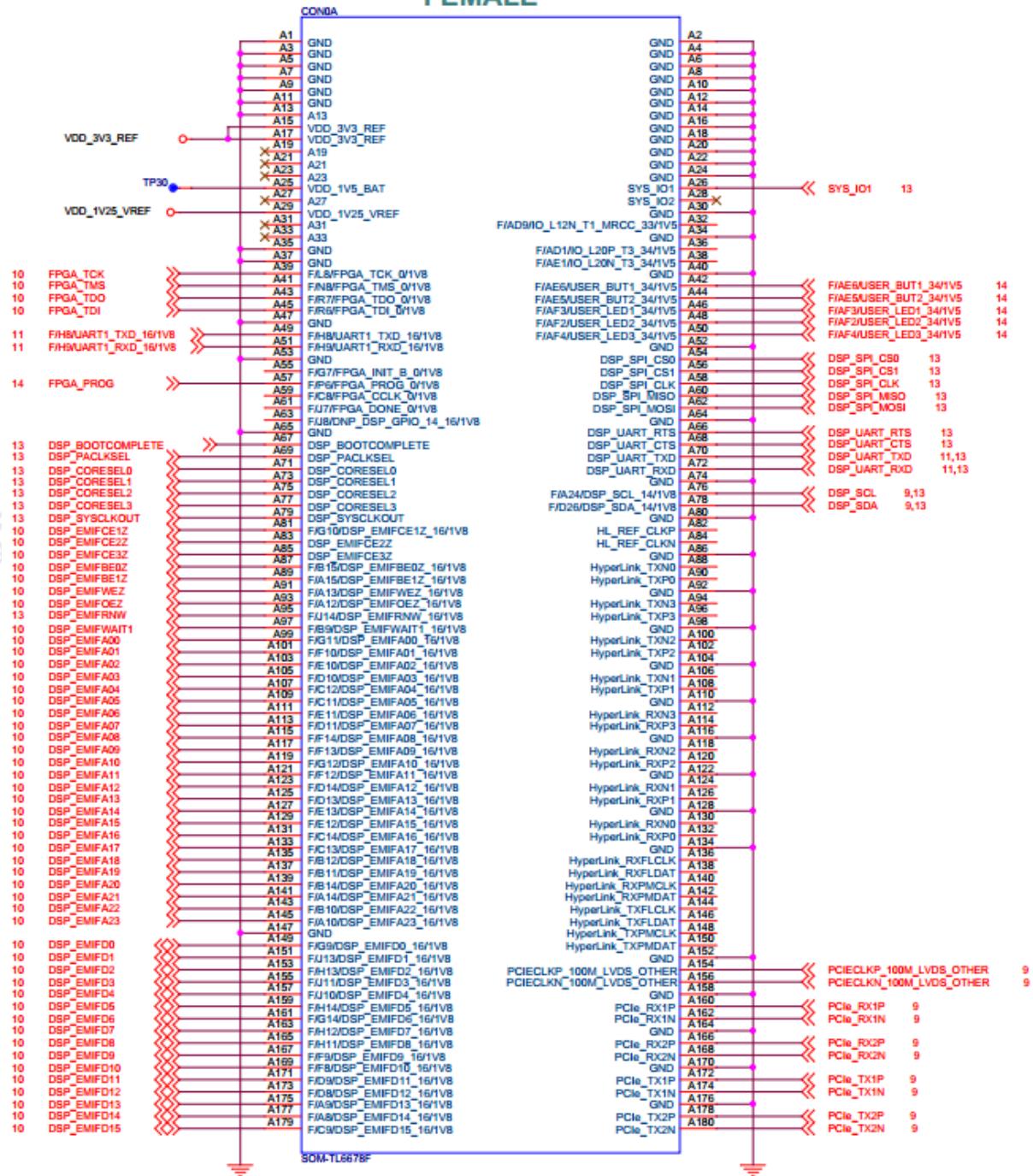

## FEMALE

图 13 CON0A

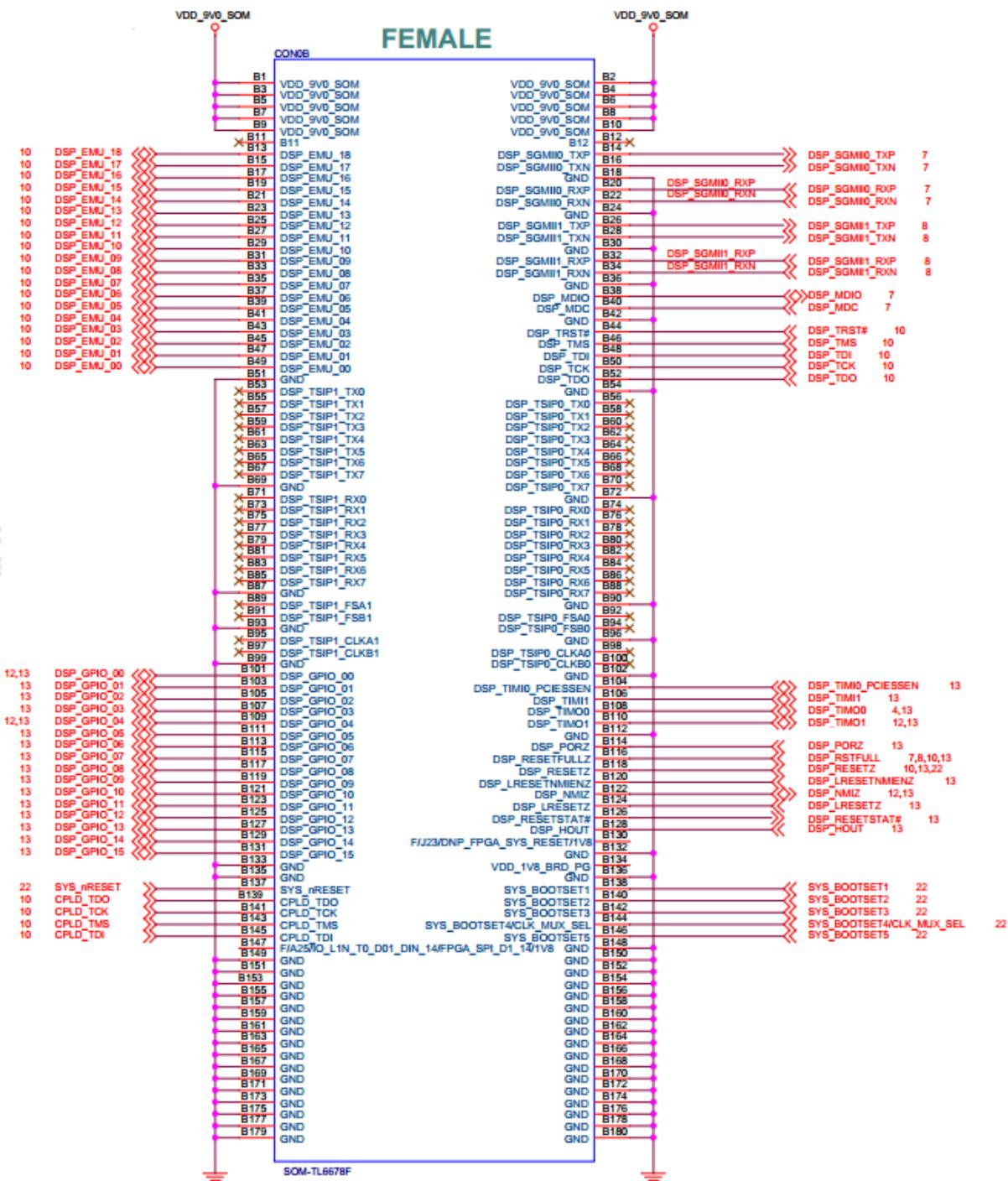

图 14 CON0B

## MALE

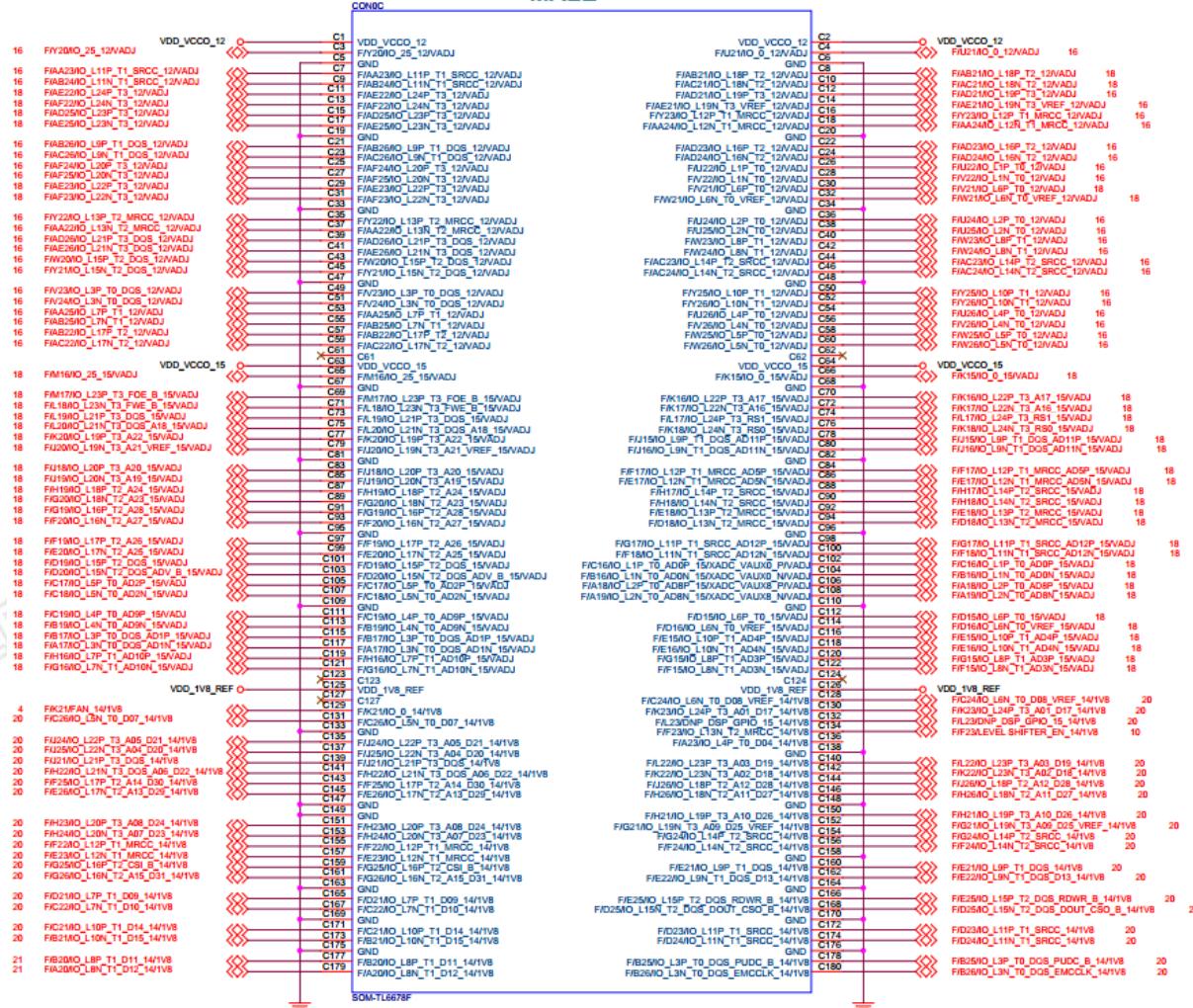

图 15 CONOC

图 16 CON0D

9 详解基于创龙 TI DSP TMS320C6678 + Xilinx FPGA Kintex-7 的 LED 指示灯

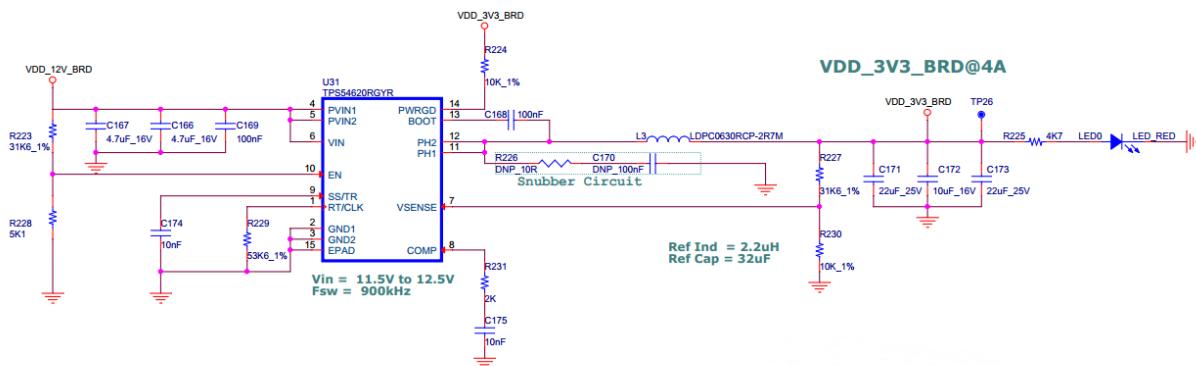

(1) 核心板上有 1 个电源指示灯(LED0), 1 个 CPLD 状态灯(LED8), 5 个用户可编程指示灯: DSP 端 2 个(LED1、LED2), FPGA 端 3 个(LED3~LED5), 硬件及引脚定义如下图:

图 17

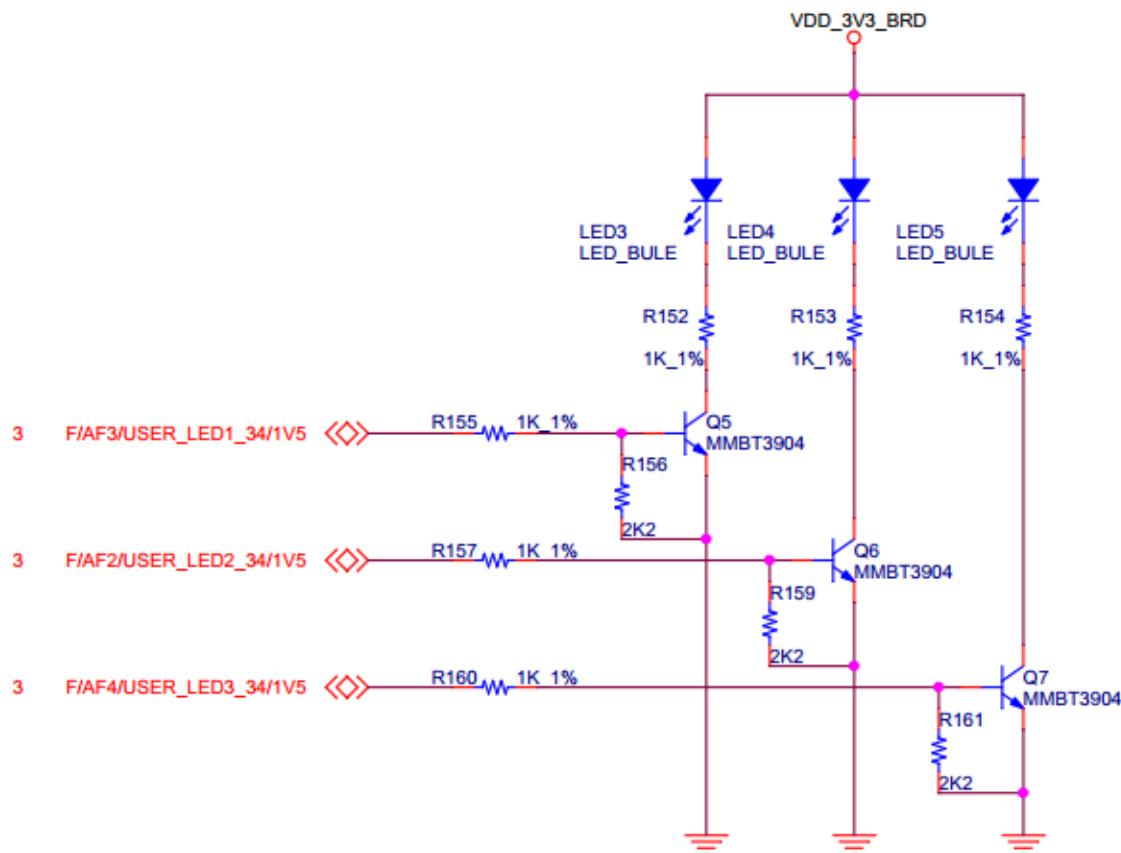

(2) 开发板底板有 1 个电源指示灯(LED0), 5 个用户可编程指示灯: DSP 端 2 个(LED1、LED2), FPGA 端 3 个 (LED3~LED5) , 硬件及引脚定义如下图:

图 18 电源指示灯

图 19 用户可编程指示灯

图 22 开发板 FPGA USER LED

## 10 详解基于创龙 TI DSP TMS320C6678 + Xilinx FPGA Kintex-7 的按键

共有 2 个系统复位按键(KEY1: WARM RESET, KEY2: FULL RESET), 5 个用户测试用按键, DSP 端 2 个(SW1: NMI, SW2: USER1), FPGA 端 3 个(SW3~SW4: USER, SW5: PROG), 硬件及引脚定义如下图:

图 23

图 24 系统复位按键

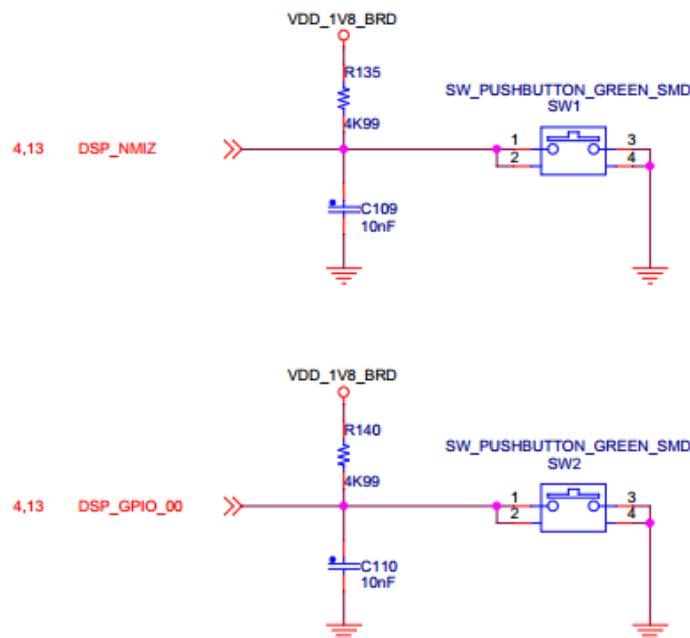

## NMI/USER BUTTON

图 25 DSP 端的用户测试用按键

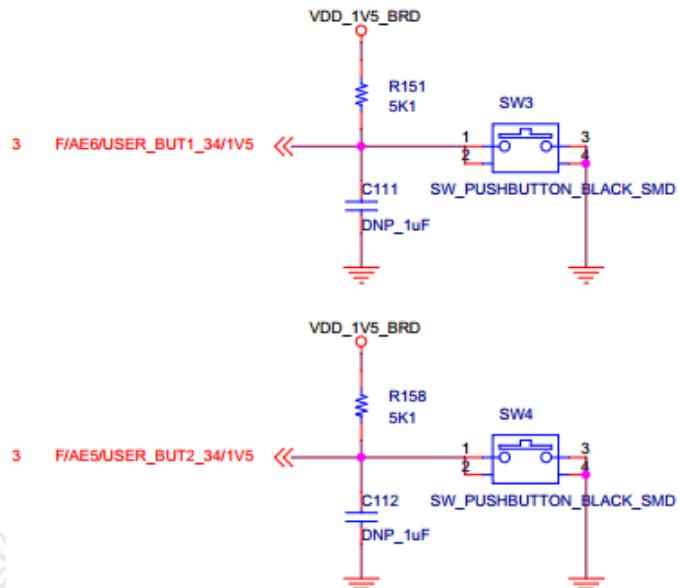

## USER BUTTON

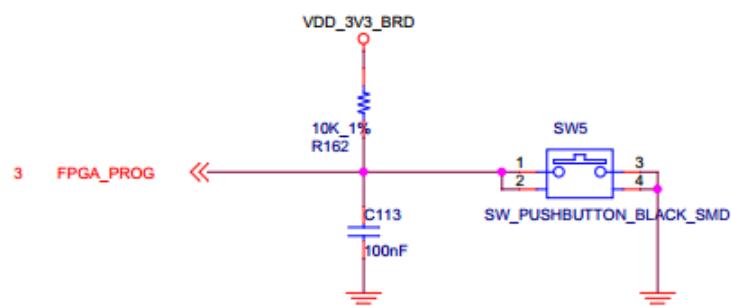

## PRG RESET

图 26 FPGA 端的用户测试用按键