**Tronlong®**

# TL5728F-EVM

## 开发板规格书

**广州创龙电子科技有限公司**

© 2013 Guangzhou Tronlong Electronic Technology Co.,Ltd.

**Revision History**

| Draft Date | Revision No. | Description                                                                          |

|------------|--------------|--------------------------------------------------------------------------------------|

| 2018/09/07 | V1.2         | 1. 修改电气特性参数。                                                                         |

| 2018/06/10 | V1.1         | 1. 开发板更新为 A2 版本。<br>2. 删除 FPGA 端 USB 接口, COLD RESET 按键。<br>3. 替换开发板所有图片, 修正文档部分描述内容。 |

| 2017/10/13 | V1.0         | 1. 初始版本。                                                                             |

## 目 录

|           |           |

|-----------|-----------|

| 1 开发板简介   | 4         |

| 2 典型运用领域  | 7         |

| 3 软硬件参数   | 8         |

| 4 开发资料    | 13        |

| 5 电气特性    | 14        |

| 6 机械尺寸图   | 14        |

| 7 产品订购型号  | 16        |

| 8 开发板套件清单 | 16        |

| 9 技术支持    | 17        |

| 10 增值服务   | 17        |

| 更多帮助      | 错误!未定义书签。 |

| 附录 A 开发例程 | 19        |

## TI Sitara AM5728（双 DSP +双 ARM）+ Xilinx Artix-7 FPGA 开发板简介

- 基于 TI Sitara AM5728（浮点双 DSP C66x +双 ARM Cortex-A15）+ Xilinx Artix-7 FPGA 工业控制及高性能音视频处理器；

- TI AM5728 为多核异构 CPU，集成双核 Cortex-A15、双核 C66x 浮点 DSP、双核 PRU-ICSS、双核 IPU Cortex-M4、双核 GPU 等处理单元，支持 OpenCL、OpenMP、IPC 多核开发；

- FPGA 芯片使用 Xilinx Artix-7 系列处理器，FPGA 端 NOR FLASH 大小为 32MByte，DDR3 大小 512M/1GByte 可选；

- AM5728 与 FPGA 内部通过 GPMC、I2C 总线实现通信；外部通过高速连接器引出 PCIe，可在底板上实现通信；

- 双核 PRU-ICSS 工业实时控制子系统，支持 EtherCAT、EtherNet/IP、PROFIBUS 等工业协议；

- 高性能 GPU，双核 SGX544 3D 加速器和 GC320 2D 图形加速引擎，支持 OpenGL ES2.0；

- 强劲的视频编解码能力，支持 1 路 1080P60 或 2 路 720P60 或 4 路 720P30 视频硬件编解码，支持 H.265 视频软解码；

- 支持高达 1 路 1080P60 全高清视频输入和 1 路 LCD+1 路 HDMI 1.4a 输出；

- 开发板引出 V-PORT 视频接口，可以灵活接入视频输入模块；

- FPGA 扩展接口，可连多通道 AD、DA 等模块，拓展能力强；

- XADC 接口，模拟到数字转换，片内或片外参考电压可选；

- 双 SFP 接口，传输速率可高达 5Gbit/s，可接 SFP 光口模块或 SFP 电口模块；

- 工业级 FMC 连接器，支持高速 ADC、DAC 和视频输入输出等 FMC-LPC 标准模块；

- 外设接口丰富，集成双千兆网、PCIe、SATA 2.0、GPMC、USB 2.0、UART、SPI、QSPI、I2C、DCAN、PMOD 等工业控制总线和接口，支持极速接口 USB 3.0；

- 工业级精密 B2B 连接器，0.5mm 间距，稳定，易插拔，防反插，所有数据接口使用高速连接器，保证信号完整性。

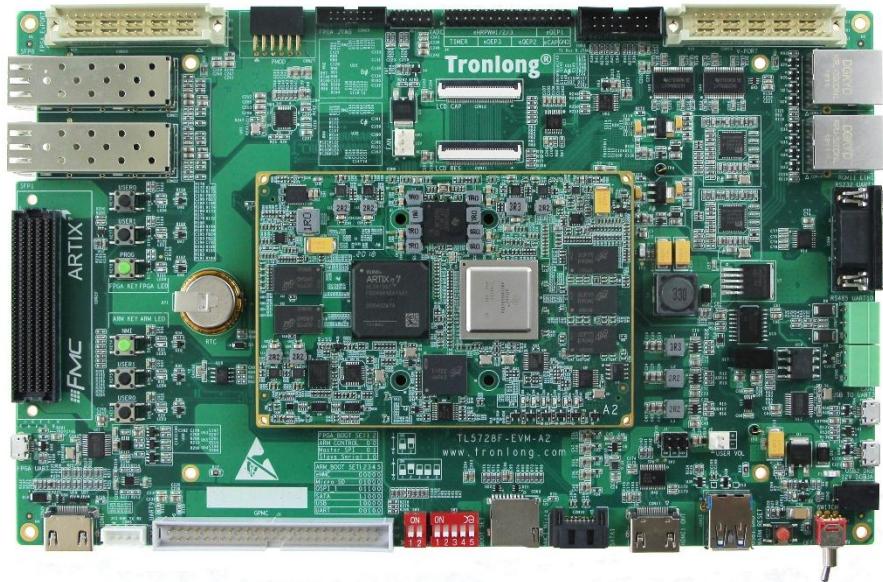

图 1 开发板正面图 1

图 2 开发板正面图 2

图 3 开发板斜视图

图 4 开发板侧视图 1

图 5 开发板侧视图 2

图 6 开发板侧视图 3

图 7 开发板侧视图 4

广州创龙基于 TI Sitara AM5728(浮点双 DSP C66x +双 ARM Cortex-A15) + Xilinx Artix-7 FPGA 设计的 TL5728F-EVM 开发板是一款 DSP+ARM+FPGA 架构的开发平台，该平台适用于电力采集、电机控制器、雷达信号采集分析、医用仪器、机器视觉等领域。TL5728F-EVM 开发板的底板采用沉金无铅工艺的 6 层板设计，其核心板内部 AM5728 通过 GPMC 总线与 FPGA 通信，组成 DSP+ARM+FPGA 架构，开发板 ARM 端主要用于控制、显示、简单算法处理；DSP 端主要用于复杂算法运算；FPGA 端主要用于采集、缓存、算法处理、高速 AD/DA 控制、IO 扩展等。

TL5728F-EVM 开发板具有丰富的接口，广州创龙不仅为客户提供丰富的 Demo 程序以及 DSP+ARM+FPGA 多核通信开发教程，还提供长期、全面的技术支持，协助客户进行底板的设计和调试以及 DSP+ARM+FPGA 软件开发，帮助客户以最快的速度进行产品的二次开发，实现产品的快速上市。

## 2TI Sitara AM5728（双 DSP +双 ARM）+ Xilinx Artix-7 FPGA 开发板典型运用

### 领域

- ✓ 工业 PC&HMI

- ✓ 工业机器人

- ✓ 机器视觉

- ✓ 医疗影像

- ✓ 电力自动化

- ✓ EtherCAT 主/从控制器

- ✓ 工业多协议智能网关

- ✓ 高端数控系统

3TI Sitara AM5728 (双 DSP +双 ARM) + Xilinx Artix-7 FPGA 开发板软硬件参

数

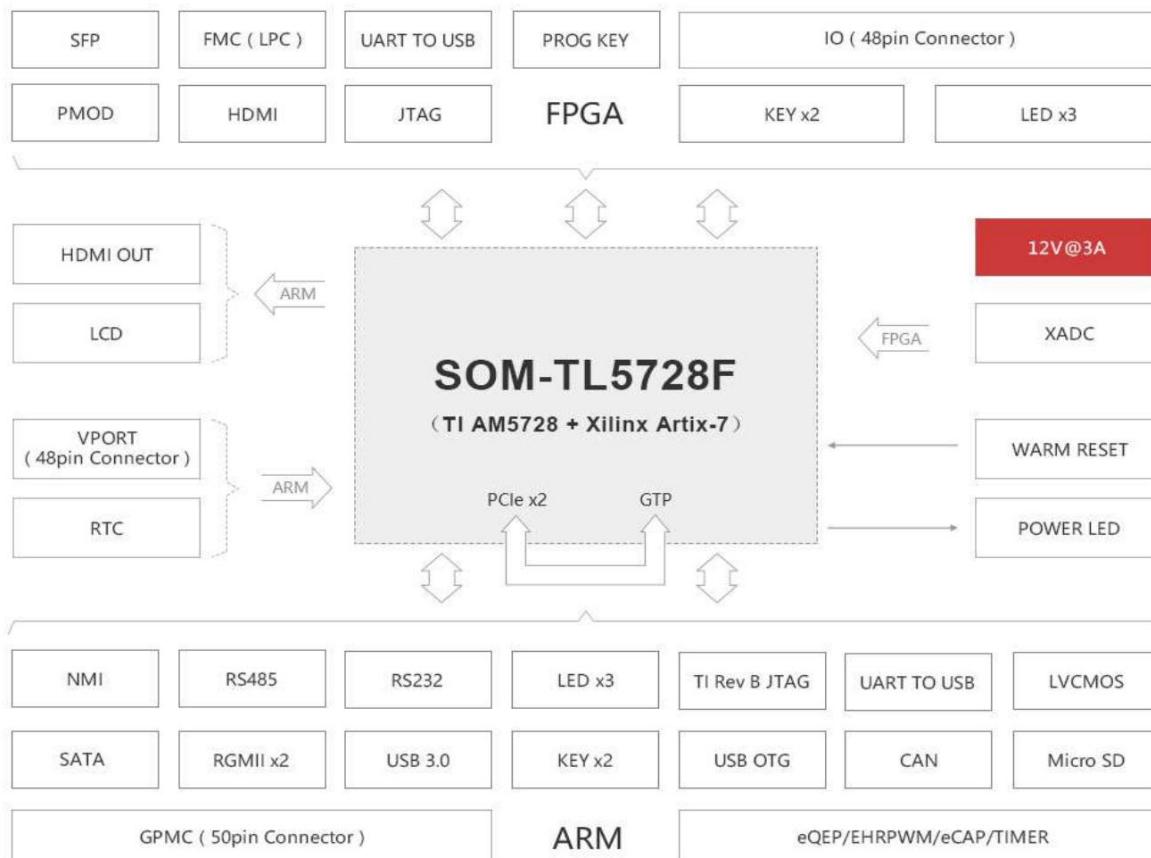

## 硬件框图

图 8 开发板硬件框图

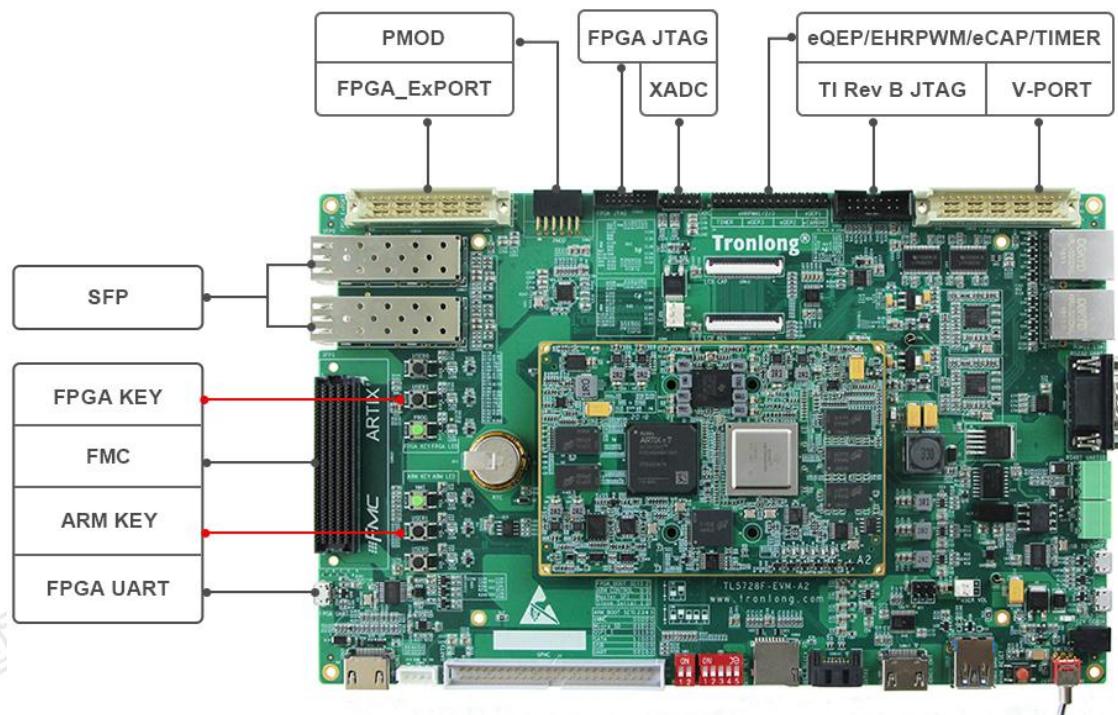

图 9 开发板硬件资源图解 1

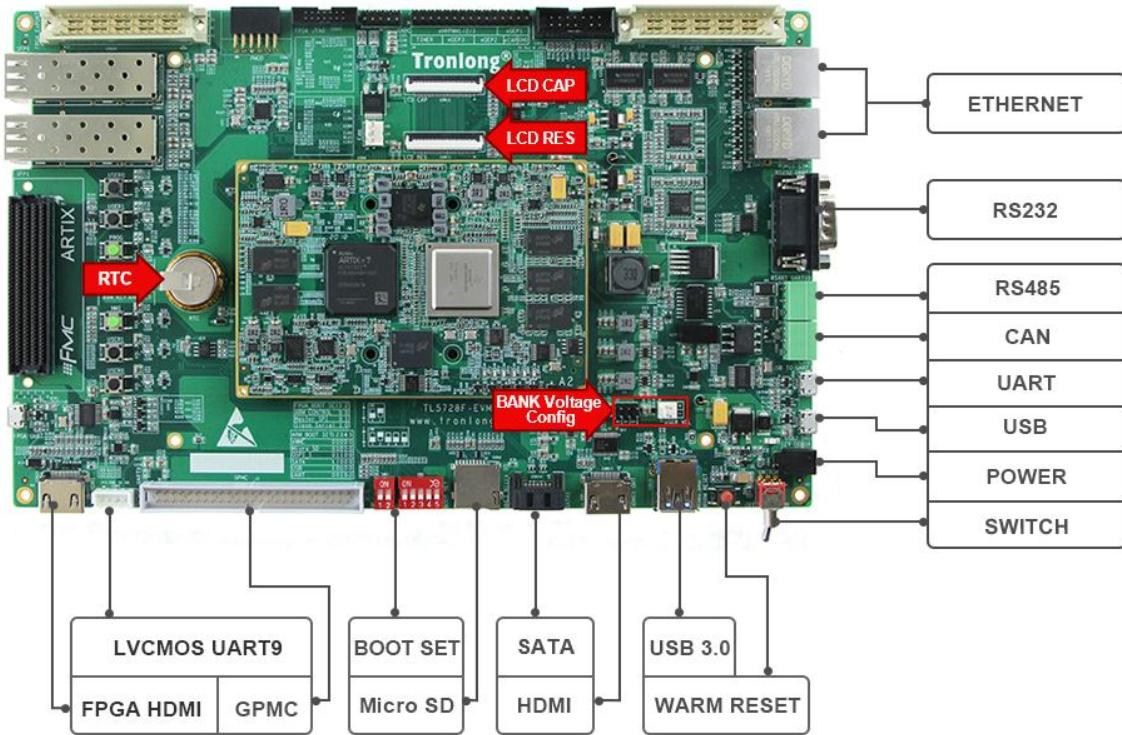

图 10 开发板硬件资源图解 2

## 硬件参数

表 1 DSP+ARM 端硬件参数

|                                |                                                                                               |

|--------------------------------|-----------------------------------------------------------------------------------------------|

| <b>CPU</b>                     | TI Sitara AM5728, 浮点双 ARM Cortex-A15 + 双 DSP C66x<br>主频: 750MHz(DSP) + 1.5GHz(ARM), 兼容 AM5718 |

| <b>L2 Cache</b>                | ARM Cortex-A15: 1MByte<br>C66x: 288KByte                                                      |

| <b>On-Chip Memory</b>          | 2.5MByte                                                                                      |

| <b>ROM</b>                     | 4/8GByte eMMC                                                                                 |

| <b>RAM</b>                     | 1/2GByte DDR3                                                                                 |

| <b>ENCRYPT</b>                 | 1x ATAES132A-SHEQ                                                                             |

| <b>SENSOR</b>                  | 1x TMP102AIDRLT                                                                               |

| <b>LED</b>                     | 2x 供电指示灯 (底板 1 个, 核心板 1 个)                                                                    |

|                                | 5x 用户指示灯 (底板 3 个, 核心板 2 个)                                                                    |

| <b>B2B Connector</b>           | 2x 180pin 高速 B2B 公座连接器, 2x 180pin 高速 B2B 母座连接器, 间距 0.5mm, 合高 5mm, 共 720pin                    |

| <b>IO</b>                      | 1x 30pin 排针, 间距 2.54mm, 包含 eQEP、eCAP、PWM、TIMER 等拓展信号                                          |

|                                | 1x 50pin IDC3 简易牛角座, 间距 2.54mm, 含 GPMC 等拓展信号                                                  |

| <b>KEY</b>                     | 2x 用户按键                                                                                       |

|                                | 2x 复位按键, 包含 1 个系统复位和 1 个软复位                                                                   |

|                                | 1x NMI 按键                                                                                     |

| <b>JTAG</b>                    | 1x 14pin TI Rev B JTAG 接口, 间距 2.54mm                                                          |

| <b>DISPLAY &amp; VIDEO OUT</b> | 1x 电阻触摸屏接口, 40pin FFC 母座, 间距 0.5mm                                                            |

|                                | 1x 电容触摸屏接口, 40pin FFC 母座, 间距 0.5mm                                                            |

|                                | 1x HDMI 1.4a 接口                                                                               |

| <b>BOOT SET</b>                | 1x 5bit 拨码开关                                                                                  |

| <b>SD</b>                      | 1x Micro SD 接口                                                                                |

| <b>RTC</b>                     | 1x 5V 1.5F 法拉电容                                                                               |

| <b>Ethernet</b>                | 2x RGMII, RJ45 接口, 10/100/1000M 自适应                                                           |

| <b>USB</b>                     | 1x Micro USB 2.0 接口                                                                           |

|               |                                                |

|---------------|------------------------------------------------|

|               | 1x USB 3.0 接口                                  |

| <b>CAN</b>    | 1x 3pin 3.81mm 绿色端子                            |

| <b>UART</b>   | 1x UART3, 串口转 USB 接口, 全双工模式                    |

|               | 1x RS232 串口 (UART1), 全双工模式                     |

|               | 1x RS485 串口 (UART10), 半双工模式                    |

|               | 1x UART9, LVCMOS 串口, 全双工模式                     |

| <b>SATA</b>   | 1x 7pin SATA 硬盘接口                              |

| <b>VPORT</b>  | 1x 48pin V-PORT 接口                             |

| <b>SWITCH</b> | 1x 电源开关                                        |

| <b>FAN</b>    | 1x FAN, 12V 供电, 间距 2.54mm                      |

| <b>POWER</b>  | 1x 12V 6A 直流输入 DC417 电源接口, 外径 4.4mm, 内径 1.65mm |

表 2 FPGA 端硬件参数

|             |                                                       |

|-------------|-------------------------------------------------------|

| <b>FPGA</b> | Xilinx Artix-7 XC7A100T-2FGG484I, 兼容 XC7A15/35/50/75T |

| <b>RAM</b>  | 512M/1GByte DDR3                                      |

| <b>ROM</b>  | 32MByte SPI NOR FLASH                                 |

| <b>LED</b>  | 1x 运行指示灯 (核心板)                                        |

|             | 5x 用户指示灯 (核心板 2 个, 底板 3 个)                            |

| <b>KEY</b>  | 2x 用户按键                                               |

|             | 1x PROGRAM 按键                                         |

| <b>JTAG</b> | 1x 14pin JTAG 接口, 间距 2.0mm                            |

| <b>SFP</b>  | 2x SFP, 由 2 个高速串行收发器 (GTP) 引出                         |

| <b>IO</b>   | 1x 400pin FMC 连接器, LPC 标准                             |

|             | 1x 12pin PMOD 接口                                      |

|             | 1x 48pin 欧式连接器, FPGA 扩展                               |

| <b>HDMI</b> | 1x HDMI 1.4 接口                                        |

| <b>XADC</b> | 1x 10pin XADC 接口, 2x 12bit 1M ADC FPGA 自带             |

## Artix-7 FPGAs

| Artix-7 FPGAs                                                                                |                                                     |             |             |             |             |             |             |             |             |

|----------------------------------------------------------------------------------------------|-----------------------------------------------------|-------------|-------------|-------------|-------------|-------------|-------------|-------------|-------------|

| Transceiver Optimization at the Lowest Cost and Highest DSP Bandwidth<br>(1.0V, 0.95V, 0.9V) |                                                     |             |             |             |             |             |             |             |             |

|                                                                                              | Part Number                                         | XC7A12T     | XC7A15T     | XC7A25T     | XC7A35T     | XC7A50T     | XC7A75T     | XC7A100T    | XC7A200T    |

| Logic Resources                                                                              | Logic Cells                                         | 12,800      | 16,640      | 23,360      | 33,280      | 52,160      | 75,520      | 101,440     | 215,360     |

|                                                                                              | Slices                                              | 2,000       | 2,600       | 3,650       | 5,200       | 8,150       | 11,800      | 15,850      | 33,650      |

|                                                                                              | CLB Flip-Flops                                      | 16,000      | 20,800      | 29,200      | 41,600      | 65,200      | 94,400      | 126,800     | 269,200     |

| Memory Resources                                                                             | Maximum Distributed RAM (Kb)                        | 171         | 200         | 313         | 400         | 600         | 892         | 1,188       | 2,888       |

|                                                                                              | Block RAM/FIFO w/ ECC (36 Kb each)                  | 20          | 25          | 45          | 50          | 75          | 105         | 135         | 365         |

|                                                                                              | Total Block RAM (Kb)                                | 720         | 900         | 1,620       | 1,800       | 2,700       | 3,780       | 4,860       | 13,140      |

| Clock Resources                                                                              | CMTs (1 MMCM + 1 PLL)                               | 3           | 5           | 3           | 5           | 5           | 6           | 6           | 10          |

| I/O Resources                                                                                | Maximum Single-Ended I/O                            | 150         | 250         | 150         | 250         | 250         | 300         | 300         | 500         |

|                                                                                              | Maximum Differential I/O Pairs                      | 72          | 120         | 72          | 120         | 120         | 144         | 144         | 240         |

| Embedded Hard IP Resources                                                                   | DSP Slices                                          | 40          | 45          | 80          | 90          | 120         | 180         | 240         | 740         |

|                                                                                              | PCIe® Gen2 <sup>[1]</sup>                           | 1           | 1           | 1           | 1           | 1           | 1           | 1           | 1           |

|                                                                                              | Analog Mixed Signal (AMS) / ADC                     | 1           | 1           | 1           | 1           | 1           | 1           | 1           | 1           |

|                                                                                              | Configuration AES / HMAC Blocks                     | 1           | 1           | 1           | 1           | 1           | 1           | 1           | 1           |

|                                                                                              | GTP Transceivers (6.6 Gb/s Max Rate) <sup>[2]</sup> | 2           | 4           | 4           | 4           | 4           | 8           | 8           | 16          |

| Speed Grades                                                                                 | Commercial                                          | -1, -2      | -1, -2      | -1, -2      | -1, -2      | -1, -2      | -1, -2      | -1, -2      | -1, -2      |

|                                                                                              | Extended                                            | -2L, -3     |

|                                                                                              | Industrial                                          | -1, -2, -1L |

| Available User I/O: 3.3V SelectIO™ HR I/O (GTP Transceivers)                                 |                                                     |             |             |             |             |             |             |             |             |

| CPG236                                                                                       | Dimensions (mm)                                     | 10 x 10     | 0.5         | 106 (2)     | 106 (2)     | 106 (2)     | 106 (2)     |             |             |

| CSG324                                                                                       |                                                     | 15 x 15     | 0.8         | 210 (0)     | 210 (0)     | 210 (0)     | 210 (0)     | 210 (0)     | 210 (0)     |

| CSG325                                                                                       |                                                     | 15 x 15     | 0.8         | 150 (2)     | 150 (4)     | 150 (4)     | 150 (4)     |             |             |

| FTG256                                                                                       |                                                     | 17 x 17     | 1.0         | 170 (0)     | 170 (0)     | 170 (0)     | 170 (0)     | 170 (0)     | 170 (0)     |

| SBG484 / SBV484                                                                              |                                                     | 19 x 19     | 0.8         |             |             |             |             |             | 285 (4)     |

| Footprint Compatible                                                                         | FGG484                                              | 23 x 23     | 1.0         | 250 (4)     | 250 (4)     | 250 (4)     | 285 (4)     | 285 (4)     | 285 (4)     |

|                                                                                              | FBG484 / FBV484                                     | 23 x 23     | 1.0         |             |             |             |             |             |             |

图 11 Xilinx Artix-7 FPGA 硬件资源

## 软件参数

表 3 软件参数

|               |                                              |         |

|---------------|----------------------------------------------|---------|

| ARM 端软件支持     | Linux-RT 4.9.65, TI-RTOS                     |         |

| DSP 端软件支持     | TI-RTOS                                      |         |

| CCS 版本号       | CCS 7.4                                      |         |

| VIVADO 版本号    | 2015.2                                       |         |

| 图形界面开发工具      | Qt                                           |         |

| 双核通信组件支持      | IPC                                          |         |

| 软件开发套件提供      | Processor-SDK Linux-RT、Processor-SDK TI-RTOS |         |

| Linux-RT 驱动支持 | QSPI Flash                                   | DDR3    |

|               | PCIe                                         | eMMC    |

|               | MMC/SD                                       | USB 3.0 |

|               | PCIe 2.0                                     | USB 2.0 |

|               | LED                                          | BUTTON  |

|  |                        |                      |

|--|------------------------|----------------------|

|  | RS232                  | RS485                |

|  | HDMI OUT               | DCAN                 |

|  | SATA                   | RTC                  |

|  | 4.3in Touch Screen LCD | 7in Touch Screen LCD |

|  | SPI                    | QSPI                 |

|  | UART                   | JTAG                 |

|  | EMCRYDT IC             | TEMPERATURE SENSOR   |

|  | KBD                    | HDQ                  |

|  | NMI                    | SYS INT              |

|  | eCAP                   | I2C                  |

## 4TI Sitara AM5728 (双 DSP + 双 ARM) + Xilinx Artix-7 FPGA 开发板开发资料

- (1) 提供核心板引脚定义、可编辑底板原理图、可编辑底板 PCB、芯片 Datasheet，缩短硬件设计周期；

- (2) 提供系统烧写镜像、内核驱动源码、文件系统源码，以及丰富的 Demo 程序；

- (3) 提供完整的平台开发包、入门教程，节省软件整理时间，上手容易；

- (4) 提供详细的 DSP+ARM+FPGA 架构通信教程，完美解决 DSP+ARM+FPGA 架构开发瓶颈；

- (5) 提供基于 Qt 的图形界面开发教程。

部分开发例程详见附录 A，开发例程主要包括：

- 基于 ARM 端的 Linux-RT 开发例程

- 基于 TI-RTOS 的 ARM、DSP、PRU、IPU 的开发例程

- 基于 OpenCL、OpenMP、IPC 的多核开发例程

- 基于 OpenCV 的图像开发例程

- 基于 Qt 的入门开发例程

- 基于 TI-RTOS 和 Linux-RT 的 EtherCAT 开发例程

- 视频采集和编解码例程

### 5TI Sitara AM5728 (双 DSP +双 ARM) + Xilinx Artix-7 FPGA 开发板电气特性

#### 核心板工作环境

表 4

| 环境参数  | 最小值   | 典型值      | 最大值  |

|-------|-------|----------|------|

| 工业级温度 | -40°C | /        | 85°C |

| 工作电压  | /     | 9V (±5%) | /    |

#### 功耗测试

表 5

| 类别  | 典型值电压 | 典型值电流 | 典型值功耗  |

|-----|-------|-------|--------|

| 核心板 | 9V    | 870mA | 7.83W  |

| 整板  | 12V   | 950mA | 11.40W |

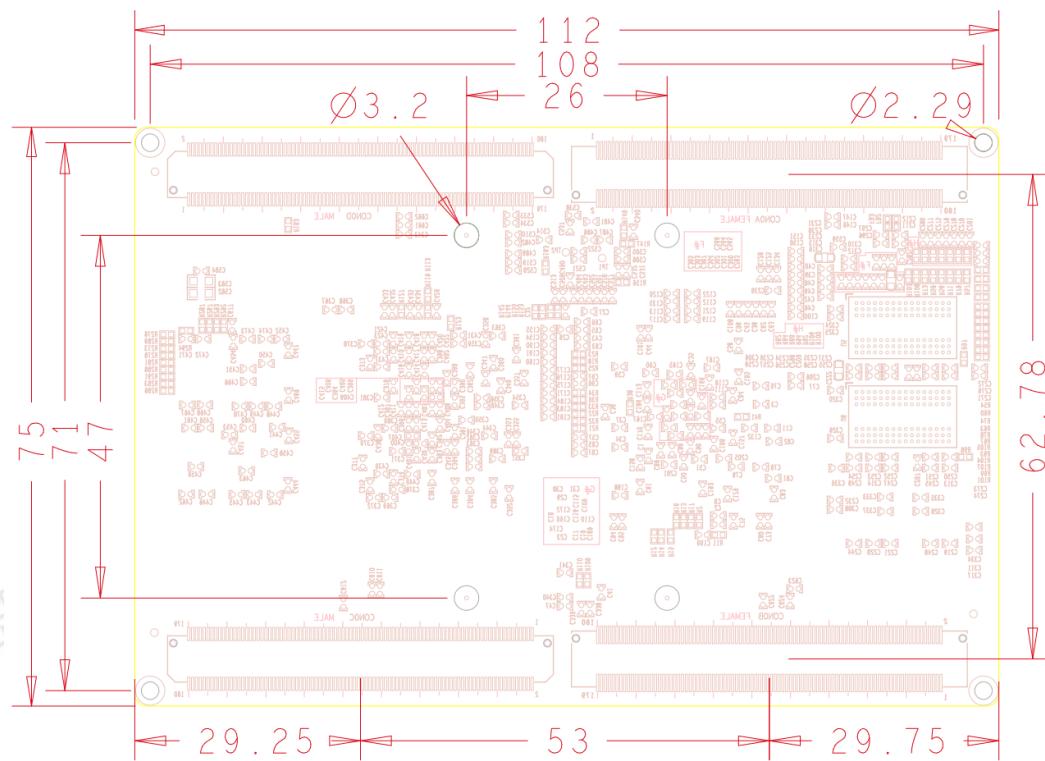

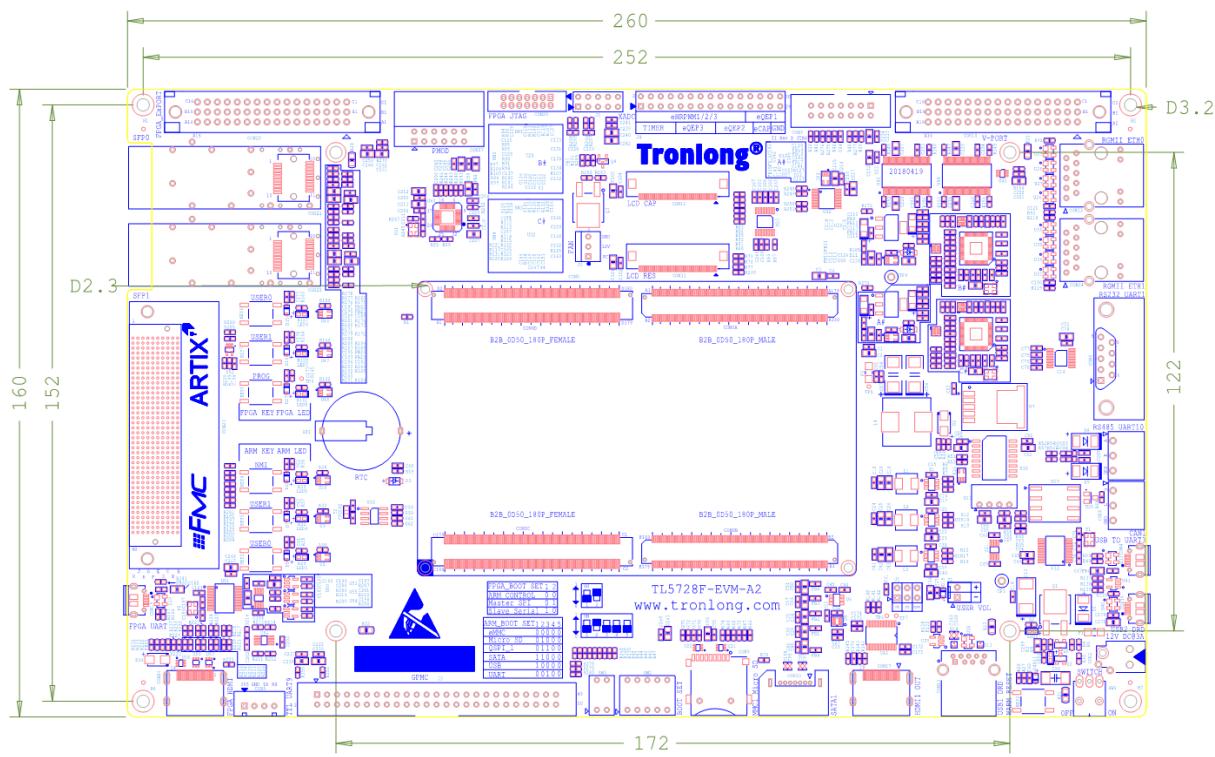

### 6TI Sitara AM5728 (双 DSP +双 ARM) + Xilinx Artix-7 FPGA 开发板机械尺寸

#### 图

表 6

|        | 开发板         | 核心板        |

|--------|-------------|------------|

| PCB 尺寸 | 260mm*160mm | 112mm*75mm |

| 安装孔数量  | 4 个         | 4 个        |

图 12 核心板机械尺寸图

图 13 开发板机械尺寸图

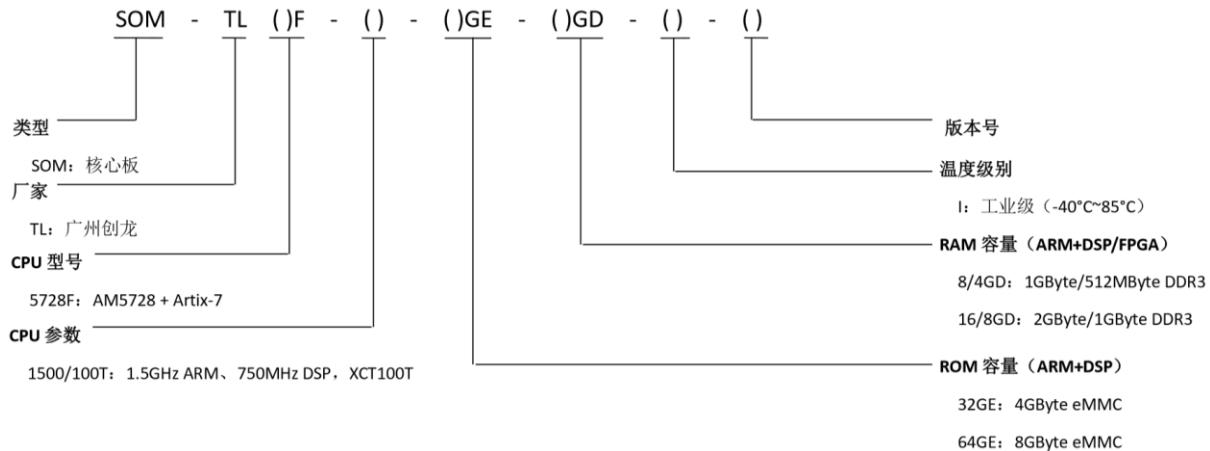

## 7TI Sitara AM5728（双 DSP +双 ARM）+ Xilinx Artix-7 FPGA 开发板产品订购

### 型号

表 7 核心板型号

| 型号                                  | CPU 主频                   | eMMC   | DDR3<br>(DSP/FPGA) | FPGA 型号  | 温度级别 |

|-------------------------------------|--------------------------|--------|--------------------|----------|------|

| SOM-TL5728F-1500/100T-32GE-8/4GD-I  | ARM:1.5GHz<br>DSP:750MHz | 4GByte | 1GByte/512MByte    | XC7A100T | 工业级  |

| SOM-TL5728F-1500/100T-64GE-16/8GD-I | ARM:1.5GHz<br>DSP:750MHz | 8GByte | 2GByte/1GByte      | XC7A100T | 工业级  |

备注：标配 SOM-TL5728F-1500/100T-32GE-8/4GD-I，其他型号请与相关销售人员联系。

### 型号参数解释

图 14

## 8TI Sitara AM5728（双 DSP +双 ARM）+ Xilinx Artix-7 FPGA 开发板开发板套件清单

表 8

| 名称                     | 数量  |

|------------------------|-----|

| TL5728F-EVM 开发板 (含核心板) | 1 块 |

|                       |     |

|-----------------------|-----|

| 12V6A 电源适配器           | 1 个 |

| 资料光盘                  | 2 套 |

| Micro USB 线           | 2 条 |

| 直连网线 (RJ45)           | 2 根 |

| Micro SD 系统卡          | 1 张 |

| SD 卡读卡器               | 1 个 |

| HDMI 线                | 1 条 |

| TL070A 7 寸电阻触摸屏       | 1 个 |

| FFC 软排线 0.5-40p-120mm | 2 条 |

| 散热片                   | 1 块 |

| 风扇                    | 1 个 |

| 双纤光纤模块                | 2 块 |

| 双芯光纤线缆                | 2 根 |

### 9TI Sitara AM5728 (双 DSP +双 ARM) + Xilinx Artix-7 FPGA 开发板技术支持

- (1) 协助底板设计和测试，减少硬件设计失误；

- (2) 协助解决按照用户手册操作出现的异常问题；

- (3) 协助产品故障判定；

- (4) 协助正确编译与运行所提供的源代码；

- (5) 协助进行产品二次开发；

- (6) 提供长期的售后服务。

### 10TI Sitara AM5728 (双 DSP +双 ARM) + Xilinx Artix-7 FPGA 开发板增值服务

- 主板定制设计

- 核心板定制设计

- 嵌入式软件开发

- 项目合作开发

- 技术培训

## 附录 ATI Sitara AM5728（双 DSP +双 ARM）+ Xilinx Artix-7 FPGA 开发板开发例程

表 9

| 视频采集与编码例程          |                      |

|--------------------|----------------------|

| 例程                 | 功能                   |

| RTSP_Server_Launch | H.264 编码视频流 RTSP 服务器 |

| 多路 RTSP            | 多路 RTSP 解码显示         |

| TVP5158            | 4 路 D1 视频采集          |

| GV7601             | HD-SDI 视频采集          |

| RTSP Client        | 网络摄像头采集显示和保存为 MP4    |

| jpegenc            | JPEG 编码              |

| ADV7611            | ADV7611 HDMI 采集      |

| TVP7002            | VGA 视频采集             |

| ov5640             | OV5640 视频采集          |

| GigE               | GigE 工业相机图像采集        |

表 10

| PRU 开发例程         |            |

|------------------|------------|

| 例程               | 功能         |

| TL_PRU_Led_Blink | PRU 点亮流水灯  |

| TL_PRU_Button    | PRU 实现按键控制 |

表 11

| Qt 开发例程    |         |

|------------|---------|

| 例程         | 功能      |

| HelloWorld | Qt 入门例程 |

|     |           |

|-----|-----------|

| LED | 点亮开发板 LED |

|-----|-----------|

表 12

| OpenCL 开发例程   |                       |

|---------------|-----------------------|

| 例程            | 功能                    |

| vecadd        | 向量相加                  |

| vecadd_openmp | 使用 OpenMP 并行进行向量相加    |

| float_compute | 分别在 ARM 和 DSP 端进行浮点计算 |

| dsplib_fft    | FFT 运算                |

| monte_carlo   | 蒙特卡洛法运算               |

表 13

| OpenMP 开发例程    |               |

|----------------|---------------|

| 例程             | 功能            |

| dsphereap      | 在 DSP 上创建和使用堆 |

| vecadd         | 向量的并行相加       |

| vecadd_complex | 复数向量的并行相加     |

| 其他             | 包含在 SDK       |

表 14

| OpenCV 开发例程  |                         |

|--------------|-------------------------|

| 例程           | 功能                      |

| TI 官方综合例程    | OpenCV+OpenCL+OpenGL 运用 |

| Sobel        | 边缘检测算法                  |

| Canny        | 边缘检测算法                  |

| VideoCapture | 图像采集                    |

表 15

| IPC 开发例程 |

|----------|

|----------|

| 例程                      | 功能                                |

|-------------------------|-----------------------------------|

| ex02_messageq           | 核间传递数据的消息                         |

| ex12_mmrpc              | 使用 MmRpc 模块调用远程函数                 |

| ex41_forwardmsg         | 核间传递消息                            |

| ex68_power              | 接收消息关闭                            |

| tl-gatemap-mutex-access | 实现 ARM 和 DSP 对共享内存的互斥访问           |

| tl-messageq-cmem-fft    | 实现 DSP 对共享内存的数据进行 FFT 幅值运算        |

| tl-messageq-edma-memcpy | 实现 DSP 核使用 EDMA 与 ARM 核传递数据并计算总耗时 |

表 16

| EtherCAT 开发例程                 |

|-------------------------------|

| 基于 RTOS 的 EtherCAT 开发例程手册     |

| 基于 Linux-RT 的 EtherCAT 开发例程手册 |

表 17

| FPGA 开发例程   |                  |

|-------------|------------------|

| 例程          | 功能               |

| LED         | LED 测试           |

| KEY         | 按键测试             |

| UART        | UART 回环测试        |

| DDR3        | DDR3 的读写测试       |

| XADC        | XADC 功能测试        |

| USB         | USB 功能测试         |

| TL9613/9706 | AD/DA 模块测试       |

| SFP         | 光口转网口, 进行 UDP 通信 |

| HDMI        | HDMI 的输出         |

| TL7123P     | VGA 显示           |