# 一种高效率的 ACBC-C 三级运放的设计 \*

和雨,肖知明,王宇,胡伟波

(南开大学 电子信息与光学工程学院,天津 300350)

**摘要:**采用 TSMC 180 nm 的 CMOS 工艺,设计实现了一个具有高效率、大的电容负载驱动能力的三级运算放大器。提出了一种基于共源共栅密勒补偿(Cascode Miller Compensation,CMC)和交流升压补偿(AC Boosting Compensation,ACBC)的 ACBC-C 补偿结构,其中,ACBC 通过增加一条交流通路的方式提高了 GBW 以及电容驱动能力。输出级采用 AB 类结构以实现高效率。CMC 可以适应 AB 类输出级结构,在保证线性度的同时实现效率最大化,并且消除密勒电容带来的零点,更好地对稳定性进行补偿。电路仿真结果表明:当设定相位裕度下限为 45°时,最大可承受负载电容约为 3 100 pF;当在输出端接 1 000 Ω 负载电阻时,电路效率为 95.299%。

**关键词:**电容负载驱动能力;AB 类输出级;交流升压补偿;共源共栅密勒补偿

中图分类号: TN432

文献标识码: A

DOI:10.16157/j.issn.0258-7998.191370

中文引用格式: 和雨,肖知明,王宇,等. 一种高效率的 ACBC-C 三级运放的设计[J]. 电子技术应用, 2020, 46(6): 36-39, 50.

英文引用格式: He Yu, Xiao Zhiming, Wang Yu, et al. Design of a high-efficiency ACBC-C three-stage operational amplifier[J]. Application of Electronic Technique, 2020, 46(6): 36-39, 50.

## Design of a high-efficiency ACBC-C three-stage operational amplifier

He Yu, Xiao Zhiming, Wang Yu, Hu Weibo

(College of Electronic Information and Optical Engineering, Nankai University, Tianjin 300350, China)

**Abstract:** Using TSMC 180 nm CMOS technology, a three-stage operational amplifier with high efficiency and large capacitive load driving capability is designed and implemented. This paper proposes an ACBC-C compensation structure based on CMC (Cascode Miller Compensation) and ACBC (AC Boosting Compensation). Among them, ACBC by adding an AC path increases the GBW and the capacitive driving ability. The output stage uses a class AB structure to achieve high efficiency. And CMC can adapt to the class AB output stage structure, maximize efficiency while keeping great linearity, and remove the zero caused by Miller capacitor, and better compensate the stability. The simulation results show that when the phase margin is set to 45 degrees, the maximum load capacity can be as high as 3 100 pF, and that when a 1 000 Ω load resistor is connected to the output, the circuit efficiency achieves 95.299%.

**Key words:** capacitive load driving capability; class AB output stage; AC boosting compensation; cascode Miller compensation

## 0 引言

随着半导体工艺节点的下降,芯片的电源电压越来越低。越低的电源电压就意味着许多传统的电路结构变得不再适用<sup>[1]</sup>。放大器是模拟集成电路领域的一个重要模块之一,放大器的增益可以通过在输出级使用共源共栅结构来提高,但是随着电源电压的下降,共源共栅结构会严重限制输出电压摆幅<sup>[2]</sup>。在适应摩尔定律的同时,许多可替代的电路结构不断涌现。多级运放可以保证在足够大的输出电压摆幅的同时提高增益。但是每增加一级放大级,至少会产生一个高阻抗点,进而引入一个极点,过多的极点会极大地影响放大器的稳定性。因此,多级运放的频率补偿变得尤为重要。极点分离是频率补偿过程中的常用手段之一,通过改变电容来改变主极点和

其他非主极点的位置可以达到极点分离的效果。针对三级运放,嵌套密勒补偿(Nested Miller Compensation, NMC)是最常用的补偿方式之一,只需两个密勒电容,就可以达到稳定电路的目的。但是嵌套密勒补偿是以牺牲 GBW 为代价的,并且这种补偿方式适用的负载电容范围很小<sup>[3]</sup>。此外,如果要增大负载电容范围,需要增大内部密勒电容的尺寸,相应的芯片面积也会增大。为了解决这些问题,许多新的补偿方式被提出,阻尼因子控制频率补偿(Damping-Factor-Control Frequency-Compensation, DFCFC)通过增加一个阻尼网络的方式,极大地提高了 GBW,但是 DFCFC 适用于大负载电容的情况下,对于较小的负载电容,DFCFC 并没有表现出良好的特性<sup>[3]</sup>。ACBC 补偿<sup>[4]</sup>通过增加一条交流通路的方式,也极大地提高了 GBW,并且在 NMC 的基础上,拓宽了可承受负

\* 基金项目:广东省重点领域研发计划(2019B010128001)

载电容范围,表现出非常优越的特性。但是ACBC补偿结构中的密勒电容会引入一个右半平面零点,该零点对稳定性具有负面影响。CMC可以在不增加额外的消零电阻以及前馈通路的同时消除该右半平面零点<sup>[5]</sup>。本文创新性地提出将ACBC与CMC结合,形成ACBC-C结构,并研究其优越特性。

此外,高效率也是运算放大器的衡量指标之一,高效率代表电路中大多数的功耗都来自于负载,很少有功率的浪费。AB类放大器相比A类放大器具有较高的效率,所以本电路采用AB类输出结构。AB类输出结构形成了推挽式输出,也适用于上述的ACBC-C补偿结构。所以本文针对具有高效率的ACBC-C三级运放进行分析和仿真。

### 1 ACBC 三级运放基本原理

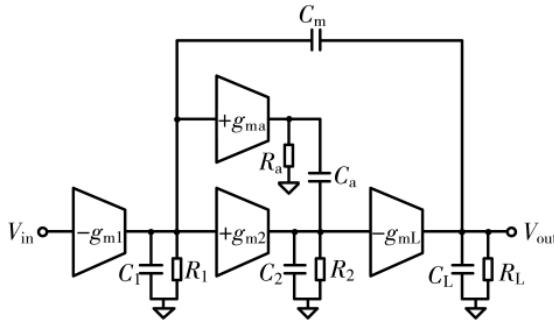

如图1所示,  $g_{ni}$  ( $i=1, 2$ ) 表示第  $i$  级的跨导,  $g_{ml}$  表示输出级跨导,  $g_{m1}$ 、 $g_{m2}$  以及  $g_{ml}$  构成三级运放。 $C_i$  ( $i=1, 2$ ),  $R_i$  ( $i=1, 2$ ) 分别表示第  $i$  级的寄生电容和第  $i$  级的等效输出阻抗,  $C_L$  和  $R_L$  分别表示输出级的负载电容和负载电阻,  $C_m$  是密勒补偿电容,  $g_{ma}$  是增加的一条交流通路,  $R_a$  是  $g_{ma}$  的等效输出阻抗。将  $g_{m2}$  和  $g_{ma}$  设置成同相放大级,  $g_{ml}$  为反相放大级,当  $C_m$  作为反馈元件时,可以形成负反馈环路。当输入信号频率较低的时候,由于  $C_a$  的存在,  $g_{ma}$  对电路的影响可以忽略,因此电路的直流增益为:

$$A_{dc} = g_{m1} g_{m2} g_{ml} R_1 R_2 R_L \quad (1)$$

图1 ACBC 三级运放结构图

为了更为简单地计算该三级运放的传输函数,作出三点假设:(1)每一级直流增益远大于1;(2)每一级的寄生电容远小于密勒电容、负载电容以及  $C_a$ ;(3)  $g_{ma}$  跨导级的等效输出阻抗  $R_a$  远小于  $g_{m2}$  跨导级的等效输出阻抗  $R_2$ 。

基于以上三点假设,传输函数为<sup>[6]</sup>:

$$A_{v}(s) = \frac{A_{dc}(1 + \frac{s}{\omega_1} + \frac{s^2}{\omega_1 \omega_4} + \frac{s^3}{\omega_1 \omega_3 \omega_4})}{(1 + \frac{s}{\omega_d})(1 + \frac{s}{\omega_1} + \frac{s^2}{\omega_1 \omega_2} + \frac{s^3}{\omega_1 \omega_2 \omega_3})} \quad (2)$$

$$\omega_d = \frac{-1}{C_m g_{m2} g_{ml} R_1 R_2 R_L} \quad (3)$$

$$\omega_1 = g_{m2} / (A_{2h} C_a) \quad (4)$$

$$\omega_2 = A_{2h} g_{ml} / C_L \quad (5)$$

$$\omega_3 = 1 / R_a C_2 \quad (6)$$

$$\omega_4 = -A_{2h} g_{ml} / C_m \quad (7)$$

$$A_{2h} = (g_{m2} + g_{ma}) R_a \quad (8)$$

其中,主极点为  $\omega_d$ ,也就是该放大器的带宽。对上述公式做一些简化,可以得到:

$$p_{nd1} = -\omega_1 = -g_{m2} / (A_{2h} C_a) \quad (9)$$

$$p_{nd2} = -\omega_2 = -A_{2h} g_{ml} / C_L \quad (10)$$

$$p_{nd3} = -\omega_3 = -1 / R_a C_2 \quad (11)$$

$$z_1 = -\omega_1 = -g_{m2} / (A_{2h} C_a) \quad (12)$$

$$z_2 = -\omega_3 = -1 / R_a C_2 \quad (13)$$

$$z_3 = -\omega_4 = A_{2h} g_{ml} / C_m \quad (14)$$

$$\omega_{GBW} = g_{ml} / C_m \quad (15)$$

其中,  $p_{nd1}$ 、 $p_{nd2}$ 、 $p_{nd3}$  为三个非主极点,  $z_1$ 、 $z_2$ 、 $z_3$  为三个零点。通过式(9)和式(12)可以看出,  $z_1$  零点和  $p_{nd1}$  极点相互抵消。通过式(11)和式(13)可以看出,  $z_2$  零点和  $p_{nd3}$  极点相互抵消。剩余的一个非主极点可以通过调节  $A_{2h}$  来达到极点分离的效果。后面的讨论将以  $p_{nd2}$  作为第一个非主极点。

根据三阶巴特沃斯响应,设置第一个非主极点的频率为 GBW 的 2 倍,可以得到:

$$\frac{A_{2h} g_{ml}}{2 g_{ml}} = \frac{C_L}{C_m} \quad (16)$$

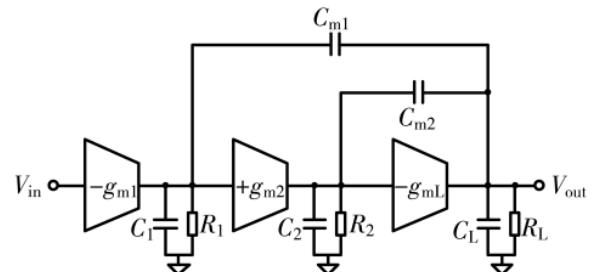

NMC 补偿结构如图2所示,在同样的条件下,其极点公式为:

$$p_{nd1} = -g_{m2} / C_{m2} \quad (17)$$

$$p_{nd2} = -g_{ml} / C_L \quad (18)$$

$$\omega_{GBW} = g_{ml} / C_{ml} \quad (19)$$

设置第一个非主极点频率为 GBW 的 2 倍,第二个非主极点的频率为 GBW 的 4 倍,可以得到:

$$\frac{g_{ml}}{4 g_{ml}} = \frac{C_L}{C_{ml}} \quad (20)$$

因此,在同样的负载电容  $C_L$  和跨导  $g_{ml}$  的条件下,密勒电容之比为:

$$\frac{C_m}{C_{ml}} = \frac{1}{2 A_{2h}} \quad (21)$$

图2 NMC 结构图

设定合理的  $R_a$ ,保证  $A_{2h} > 1$ ,就可以将密勒电容减小  $1/2 A_{2h}$  倍。由此可以看出,ACBC 补偿相比 NMC 补偿表现出优越的特性,具有更大的电容负载驱动能力,更小的密勒电容尺寸,更大的 GBW。

但是根据式(14)可知,还存在一个右半平面零点,这

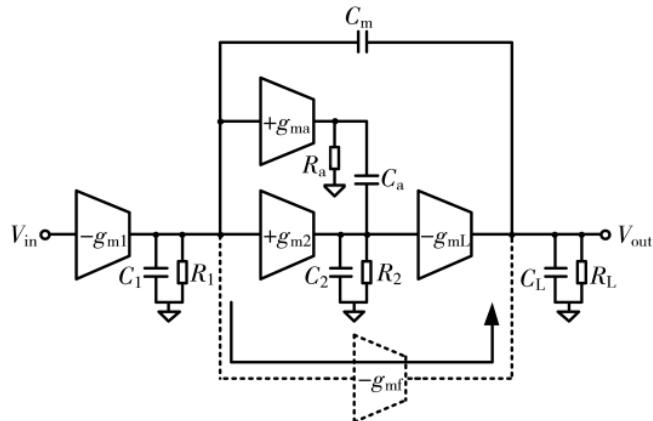

一个零点是密勒电容  $C_m$  的前馈通路带来的,为了抑制这个零点的产生,可以在  $C_m$  旁边串联一个电阻,调节电阻的阻值,可以消除零点或者将该零点转为左半平面零点。但是增加的电阻会增大电路面积。文献[4]中所使用的方法是在第一级输出和输出端之间增加一条前馈跨导通路,设置合理跨导值,也可以达到消除零点的目的。此外,所增加的前馈跨导通路还会与输出级形成推挽式输出结构,提高了压摆率。但是增加前馈通路的方法限制了输出级的类型。如图 3 所示,增加的一条前馈通路  $g_{mf}$  与输出级的跨导  $g_{ml}$  构成推挽式输出结构,  $g_{mf}$  的输入由第一级输出决定,难以控制其直流偏置点,因此,难以实现高效率。

图 3 增加前馈跨导通路后的 ACBC 结构图

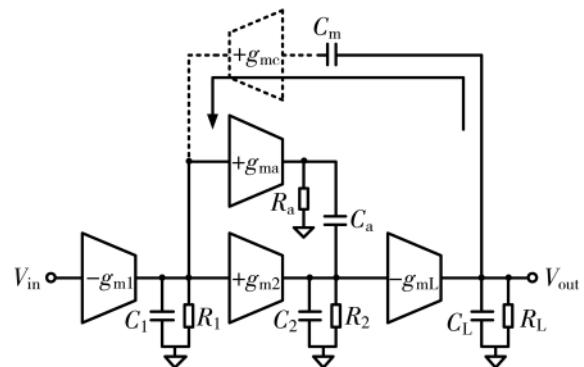

## 2 改进后 ACBC-C 三级运放基本原理

为了得到效率和稳定性最优化的补偿方案,提出了基于 ACBC 和 CMC 的 ACBC-C 补偿方案,CMC 可以通过抑制前馈通路来消除密勒补偿电容所产生的零点。该补偿方案结合了 ACBC 和 CMC 各自的优势,又不限制输出级类型。如图 4 所示,相比图 1,增加了  $g_{mc}$  跨导。密勒电容  $C_m$  反馈到  $g_{mc}$  跨导的输入端,  $g_{mc}$  跨导输出端接入第一级跨导级的输出端,该跨导级的存在抑制了前馈通路的产生,防止了由于  $C_m$  的前馈通路而带来的右半平面

图 4 所提出的 ACBC-C 补偿结构图

零点,更好地为电路进行稳定性补偿。此外,CMC 补偿结构不会限制输出级类型,输出级类型可以根据实际需要选择。在本电路中,为了得到高效率的三级运放,选择 AB 类输出级结构。

## 3 电路与仿真分析

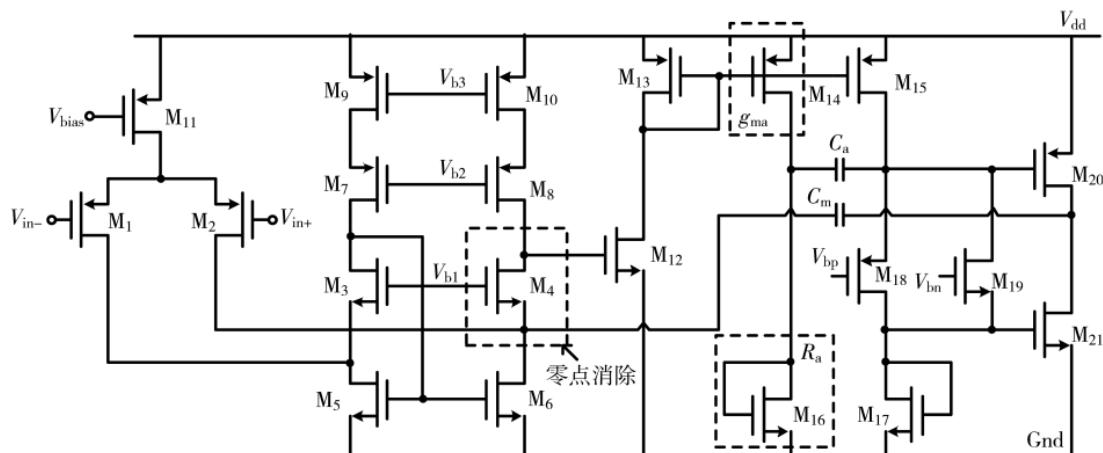

整体电路设计图如图 5 所示。其中,  $M_1 \sim M_{11}$  为第一级跨导级,  $M_{12} \sim M_{13}$  以及  $M_{15}$  为第二级跨导级,  $M_{14}$  为交流跨导级,其等效输出阻抗  $R_a$  由  $M_{16}$  控制,为  $M_{16}$  的跨导的倒数,  $M_{20}$  和  $M_{21}$  为输出级,  $M_{18}$  以及  $M_{19}$  作为 AB 类输出结构的电平移位器存在,主要作用是控制输出级的直流偏置电压,提高效率,零点消除部分主要是由  $M_4$  和  $C_m$  组成,  $M_4$  抑制了前馈通路的产生。Spectre 仿真所使用的电源电压为 1.8 V,温度为 25 ℃,工艺角为  $tt$ 。仿真主要针对电路的稳定性以及效率等参数。

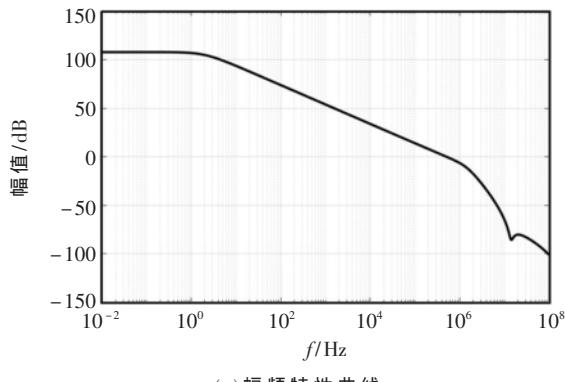

图 6 是基于 ACBC-C 补偿结构的三级运放的频率响应曲线,所使用的负载电容为 2 000 pF,可以看出,该三级运放的低频增益为 107 dB,GBW 为 730 kHz,相位裕度为 57°。

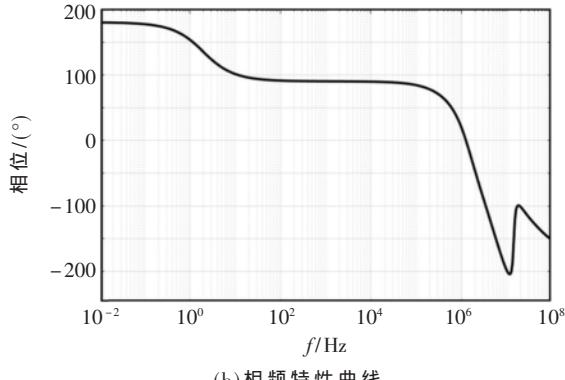

图 7 仿真了负载电容从 1 pF 到 10 nF 的范围内,基于 NMC 的三级运放、基于 ACBC 的三级运放以及基于 ACBC-C 的三级运放的相位裕度变化。为了便于比较,三种运放使用相同的密勒补偿电容,具有相同的跨导级。其中对 NMC 进行了一些简单的零点处理。可以看出,在

图 5 晶体管级电路图

(a)幅频特性曲线

(b)相频特性曲线

图 6 所提出的三级放大器的幅频特性曲线和相频特性曲线

图 7 三种补偿结构的可承受负载电容

负载电容较小的时候,所使用的 ACBC-C 补偿结构的三级运放的相位裕度约为  $90^\circ$ ,此时类似于一个单极点系统。但是,基于 ACBC 补偿结构的三级运放的相位裕度约为  $85^\circ$  左右,基于 NMC 补偿结构的三级运放的相位裕度仅为  $70^\circ$ 。这是第一个非主极点的频率没有足够远,或者零点的频率没有足够远导致的。随着负载电容的增大,由负载电容和输出级等效输出阻抗引起的极点的频率开始往靠近 GBW 的方向移动,相位裕度也开始变差。可以清晰看出,基于 ACBC-C 补偿结构的三级运放可以承受更大的负载电容。如果设定相位裕度  $45^\circ$  为下限,基于 ACBC-C 补偿结构的三级运放可以承受最大的负载电容为  $3\text{--}100\text{ pF}$ 。GBW 的拓宽可以通过减小密勒补偿电容来实现,更小的补偿电容意味着更小的可承受负载电容范围。此时设定了三种补偿方式的密勒电容和跨导级相同,因此 GBW 相同。但是基于 ACBC-C 补偿结构的三级运放已经相对基于 NMC 和 ACBC 补偿结构的三级运放具有更大的负载电容范围,如果设定相等的负载电容,前者将会具有更高的 GBW。

电路采用 AB 类输出级结构,仿真显示,在输出端接  $1\text{ k}\Omega$  的负载电阻,电路的效率为 95.299%。

电路使用的总电流为  $52.218\text{ 2 }\mu\text{A}$ ,电源电压为  $1.8\text{ V}$ ,因此,总功耗为  $0.093\text{ 6 mW}$ 。可以看出,该电路具有低功耗、高效率以及大的带负载能力。

表 1 比较了几种同类型补偿结构的三级放大器的重要参数,可以看出,所提出的基于 ACBC 补偿的 AB 类放大器具有更加优越的性能。

表 1 本设计与其他结构的关键参数比较

|                   | ACBC<br>文献[4] | SMFFC<br>文献[7] | CILA<br>文献[8] | ACBC-C<br>本文 |

|-------------------|---------------|----------------|---------------|--------------|

| 负载电容/pF           | 500           | 150            | 350           | 2 000        |

| 开环增益/dB           | >100          | >100           | >100          | >100         |

| 相位裕度/( $^\circ$ ) | 52            | 57             | 58            | 57           |

| 功耗/mW             | 0.316@2 V     | 0.41@2 V       | 12.7@1.2 V    | 0.09@1.8 V   |

| 效率/%              | --            | --             | --            | 95.299       |

#### 4 结论

本文提出了一种改进型 ACBC 补偿结构,该结构去除了原始的 ACBC 补偿结构的前馈跨导级,以减小对输出级类型的限制。同时,在 ACBC 基础上采用了 CMC 补偿结构,CMC 抑制了密勒补偿电容的前馈通路,消除了密勒补偿电容带来的零点,进一步提高了电路的稳定性,而且不额外增加电路面积与功耗。为了得到高效率的三级运放,本文使用了 AB 类输出级结构,通过控制输出级 MOS 管的直流偏置,将效率最大化。

#### 参考文献

- [1] LEUNG K N, MOK P K T. Analysis of multistage amplifier-frequency compensation[J]. IEEE Transactions on Circuits and Systems-I, 2001, 48(9): 1041–1056.

- [2] Qin Chuan, Zhang Lei, Zhou Chunyuan, et al. Dual AC boosting compensation scheme for multistage amplifiers[J]. IEEE Transactions on Circuits and Systems-II, 2017, 64(8): 882–886.

- [3] RIBNER D B, COPELAND M A. Design techniques for cascaded CMOS op amps with improved PSRR and common-mode input range[J]. IEEE Journal of Solid-State Circuits, 1984, 19(6): 919–925.

- [4] Peng Xiaohong, SANSEN W. AC boosting compensation scheme for low-power multistage amplifiers[J]. IEEE Journal of Solid-State Circuits, 2004, 39(11): 2074–2079.

- [5] YOUSRY R, SHARAF K. AC boosting compensation with

(下转第 50 页)

- [8] HALLIN J, KJELLBERG T, SWAHN T. A 100-Gb/s 1:4 demultiplexer in InP DHBT technology[C]. 2006 IEEE Compound Semiconductor Integrated Circuit Symposium, 2006.

- [9] KARNFELT C, HALLIN J, KJELLBERG T, et al. Flip-chip mounted 1:4 demultiplexer IC in InP DHBT technology operating up to 100 Gb/s[C]. 2007 European Microwave Conference, 2007.

- [10] 唐霆宇. 一种小型化超宽带接收前端的设计与实现[J].

电子技术应用, 2019, 45(6): 11-14.

- [11] 孙帆, 黄海波, 卢军, 等. 一种新型的 12 位 SAR ADC 设计[J]. 电子技术应用, 2019, 45(11): 36-41.

(收稿日期: 2020-01-02)

#### 作者简介:

周浩(1995-), 男, 硕士研究生, 主要研究方向: 超高速 InP 集成电路设计。

张有涛(1979-), 男, 博士, 高级工程师, 主要研究方向: 混合信号集成电路设计。

(上接第 39 页)

- zero cancellation for multistage amplifiers[C]. International Conference on Microelectronics, 2007.

- [6] SANSEN W M C. 模拟集成电路设计精粹[M]. 陈莹梅, 译. 北京: 清华大学出版社, 2007.

- [7] Fan Xiaohua, MISHRA C, SANCHEZ-SINENCIO E. Single Miller capacitor frequency compensation technique for low-power multistage amplifiers[J]. IEEE Journal of Solid-State Circuits, 2005, 40(3): 584 - 592.

- [8] TAN M, KI W H. A cascode Miller-compensated three-stage amplifier with local impedance attenuation for optimized complex-pole control[J]. IEEE Journal of Solid-State Circuits, 2015, 50(Z): 440 - 449.

(收稿日期: 2019-12-15)

#### 作者简介:

和雨(1995-), 女, 硕士研究生, 主要研究方向: 模拟集成电路设计。

肖知明(1983-), 男, 博士, 研究员, 主要研究方向: 电源管理、模拟/射频集成电路设计。

王宇(1996-), 女, 硕士研究生, 主要研究方向: 模拟集成电路设计。

胡伟波(1982-), 通信作者, 男, 博士, 研究员, 主要研究方向: 模/数、数/模转换器、无线感知芯片和系统实现, 第三代半导体, 生物芯片。

(上接第 44 页)

- tions on Very Large Scale Integration Systems, 2018, 26(3): 470-483.

- [8] NOGUCHI H, TAKEDA S, NOMURA K, et al. Variable nonvolatile memory arrays for adaptive computing systems[C]. International Electron Devices Meeting (IEDM), 2013.

- [9] Kang Wang, Wang Haotian, Wang Zhaohao. In-memory processing paradigm for bitwise logic operations in STT-MRAM[J]. IEEE Transactions on Magnetics, 2017, 53(11).

- [10] PATTERSON D, ANDERSON T, CARDWELL N, et al. A case for intelligent RAM[J]. IEEE Micro, 1997, 17(2): 34-44.

- [11] LEE H, ALZATE J G, DORRANCE R, et al. Design of a fast and low-power sense amplifier and writing circuit for high-speed MRAM[J]. IEEE Transactions on Magnetics, 2014, 51(5): 1-7.

- [12] DONG Q, WANG Z, LIM J, et al. A 1 Mb 28 nm STT-MRAM with 2.8 ns read access time at 1.2 V VDD using single-cap offset-cancelled sense amplifier and

in-situ self-write-termination[C]. IEEE International Solid-state Circuits Conference, 2018.

- [13] NA T, KIM J, KIM J P, et al. Reference-scheme study and novel reference scheme for deep submicrometer STT-RAM[J]. IEEE Transaction on Circuits System I, 2014, 23 (4): 3376-3385.

- [14] ZHAO W S, CHAPPERT C, JAVERLIAC V, et al. High speed, high stability and low power sensing amplifier for MTJ/CMOS hybrid logic circuits[J]. IEEE Transaction on Magnetics, 2009, 45(10): 3784-3787.

- [15] 周永亮. 基于 65 nm SRAM 的低失调自启动灵敏放大器的分析与设计[D]. 合肥: 安徽大学, 2017.

(收稿日期: 2020-02-14)

#### 作者简介:

陆楠楠(1990-), 男, 硕士研究生, 主要研究方向: 新型存储器电路设计。

王少昊(1981-), 男, 博士研究生, 副教授, 主要研究方向: 非线性光学、光子集成电路、新型存储器电路设计。

黄继伟(1976-), 通信作者, 男, 博士研究生, 副教授, 主要研究方向: 射频、模拟集成电路、MEMS 技术。

## 版权声明

经作者授权，本论文版权和信息网络传播权归属于《电子技术应用》杂志，凡未经本刊书面同意任何机构、组织和个人不得擅自复印、汇编、翻译和进行信息网络传播。未经本刊书面同意，禁止一切互联网论文资源平台非法上传、收录本论文。

截至目前，本论文已经授权被中国期刊全文数据库（CNKI）、万方数据知识服务平台、中文科技期刊数据库（维普网）、DOAJ、美国《乌利希期刊指南》、JST 日本科技技术振兴机构数据库等数据库全文收录。

对于违反上述禁止行为并违法使用本论文的机构、组织和个人，本刊将采取一切必要法律行动来维护正当权益。

特此声明！

《电子技术应用》编辑部

中国电子信息产业集团有限公司第六研究所