# 基于 STT-MRAM 的位逻辑运算方案及灵敏放大器设计 \*

陆楠楠, 王少昊, 黄继伟

(福州大学 物理与信息工程学院, 福建 福州 350108)

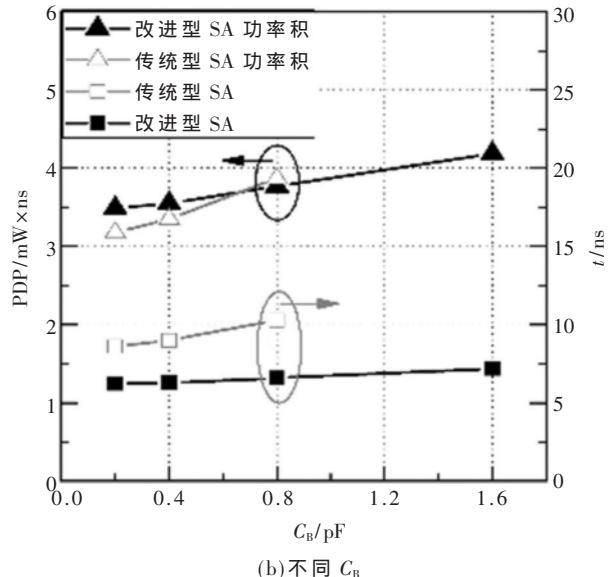

**摘要:** 基于 1T1MTJ 的自旋转移矩-磁随机存储器(STT-MRAM)提出了一种改进型存内位逻辑计算方案。该方案通过精简 2T2MTJ 存内位逻辑运算方案提升了存储阵列密度, 通过互补型读出电路增加了“与非”和“或非”的运算功能。此外, 还通过增加支路电压稳定电路的方法, 提出了一种适用于上述方案的改进型高速灵敏放大器。基于中芯国际 55 nm LL 逻辑工艺的仿真结果表明, 相较于传统的灵敏放大器, 该方案不仅读取速度提升了 33%, 在适配大型存储阵列( $C_B \geq 0.8 \text{ pF}$ )时还拥有更强的读取能力与更优的功率积(PDP)。

**关键词:** 自旋转移矩-磁随机存储器(STT-MRAM); 位逻辑运算; 高速; 灵敏放大器

中图分类号: TN432

文献标识码: A

DOI: 10.16157/j.issn.0258-7998.200097

中文引用格式: 陆楠楠, 王少昊, 黄继伟. 基于 STT-MRAM 的位逻辑运算方案及灵敏放大器设计[J]. 电子技术应用, 2020, 46(6): 40–44, 50.

英文引用格式: Lu Nannan, Wang Shaohao, Huang Jiwei. Bit logic operation scheme and sense amplifier design based on STT-MRAM[J]. Application of Electronic Technique, 2020, 46(6): 40–44, 50.

## Bit logic operation scheme and sense amplifier design based on STT-MRAM

Lu Nannan, Wang Shaohao, Huang Jiwei

(College of Physics and Information Engineering, Fuzhou University, Fuzhou 350108, China)

**Abstract:** Based on the spin transfer torque-magnetic random access memory of 1T1MTJ, an improved bit logic operation scheme in the memory is proposed in this paper. This scheme improves the storage array density by simplifying the 2T2MTJ bit logic operation scheme in the memory and increases the operation functions of "NAND" and "NOR" through the complementary readout circuit. In addition, an improved high-speed sense amplifier suitable for the above scheme is proposed by adding a branch voltage stabilizing circuit. Simulation results based on 55 nm LL logic process of SMIC show that, compared with traditional sense amplifiers, this scheme not only improves the reading speed by 33%, but also has stronger reading ability and better PDP when it is suitable for large storage arrays( $C_B \geq 0.8 \text{ pF}$ ).

**Key words:** spin transfer torque-magnetic random access memory; bit logic operation; high speed; sense amplifier

## 0 引言

磁随机存储器(MRAM)利用磁隧道结(MTJ)器件的不同磁阻态来实现对数据的存储<sup>[1]</sup>。MRAM 不仅与现有的 CMOS 工艺兼容, 还具有体积小、功耗低、访问速度快、非易失性、近无限次读/写操作和抗辐射能力强等优点<sup>[2-3]</sup>。因此, 基于自旋转移矩单元的 MRAM(STT-MRAM)已成为目前最具产业化前景的下一代新型非易失性存储器之一<sup>[4]</sup>。

在传统计算机体系架构中, 处理器与内存之间有限的数据带宽限制了系统整体效能与效率的提升, 使其无法满足当前物联网和大数据等新兴应用领域的传感器终端收集海量数据需求<sup>[5-6]</sup>。以 MRAM 为代表的新型非易失性存储器中可以直接在存储器中实现高速率与低

能耗的位逻辑运算, 因此成为下一代计算体系架构的研究热点<sup>[7-10]</sup>。早期的方案通过在存储阵列内部<sup>[7]</sup>或外部<sup>[8]</sup>添加控制逻辑电路实现对数据的预处理来实现存内位逻辑运算。PATTERSON D 等人随后提出了直接利用存储单元的外围电路(如灵敏放大器)实现存内位逻辑运算的方案, 进一步减少了芯片的面积与功耗<sup>[9]</sup>。基于 MRAM 的存内位逻辑运算方案主要以 1T1MTJ<sup>[7]</sup>、2T2MTJ<sup>[9]</sup>等典型存储阵列结构为核心。为了在每个运算单元中实现多种运算功能, 附加的逻辑控制操作数也被引入 2T2MTJ 阵列中来实现位逻辑“与”、“或”、“与非”和“或非”的运算<sup>[9]</sup>。

为了 MRAM 存储阵列实现高密度、高速率与高准确率的存内位逻辑运算, 本文基于 1T1MTJ 存储阵列提出了一种改进型存内位逻辑计算方案, 通过添加一组逻辑标记位实现多种位逻辑运算功能。本文还提出了一种适用于该方案的改进型高速灵敏放大器, 通过增加支路电压

\* 基金项目: 国家重点研发计划(2018YFB0407603)

稳定电路来提升灵敏放大器的读取精度和存内位逻辑运算速度。本文使用中芯国际 55 nm LL 逻辑工艺库对该电路结构进行了电路前仿，并在输入输出电容、工艺角、不同磁阻方面与采用典型电流型灵敏放大器的电路进行了比较分析。

## 1 基于 STT-MRAM 的高密度位逻辑运算方案

### 1.1 1T1MTJ 的存内位逻辑运算方案

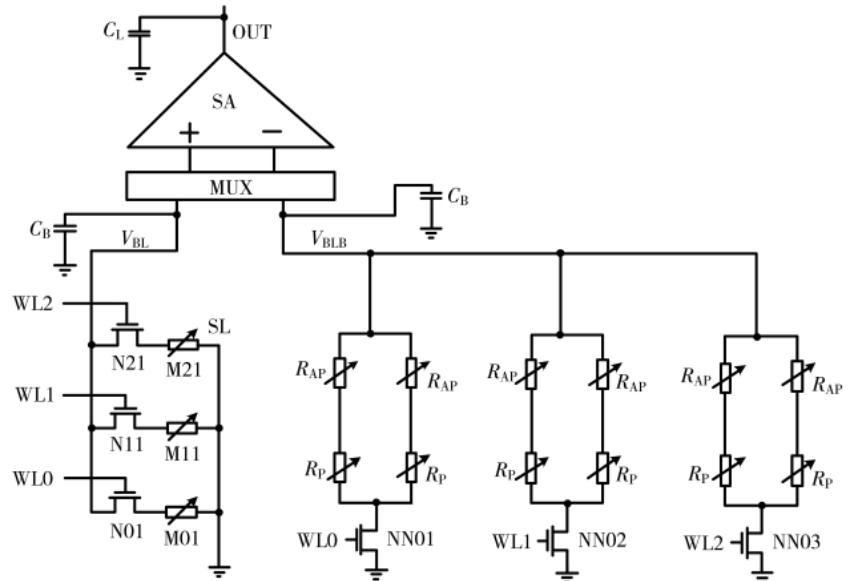

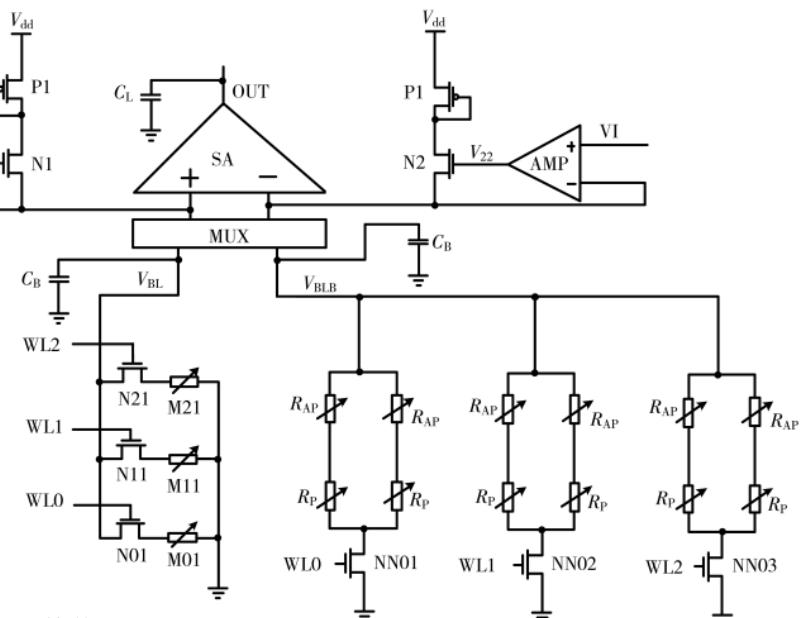

图 1 显示了一种典型的基于 2T2MTJ 存储阵列的存内位逻辑运算方案<sup>[9]</sup>。该方案中，每个存内运算单元包含三根控制位线(WL0~WL2)，每根控制位线分别连接一组 MTJ 对。每个非易失 MTJ 有平行态(记为 P)和反平行态(记为 AP)两种状态，分别对应着其电阻值的低阻状态( $R_{MTJ}=R_P$ )和高阻状态( $R_{MTJ}=R_{AP}$ )，两个阻态间的相对电阻差记为  $TMR=(R_{AP}-R_P)/R_P$ 。在 2T2MTJ 存储单元中，可将一组 MTJ 对的(P, AP)状态表示为数据“0”，将(AP, P)状态表示为数据“1”。当实施写操作时，将控制位线设为  $WL0=1, WL1=1, WL2=1$ ，可通过写驱动电路的电流方向<sup>[11]</sup>，对三根控制位线上的 MTJ 对分别进行写“0”或写“1”。 $WL0$  对应的 MTJ 对中存储的控制操作数表示逻辑操作类型(“与”或“或”)， $WL1$  和  $WL2$  对应的则为输入的两位操作数。在实施运算操作时，位逻辑运算将按照控制操作数指定的逻辑操作类型对两位操作数进行运算，其运算结果在经过灵敏放大器比较放大后在 OUT 端输出。

尽管上述方案有自参考、存储在存储器中的数字信息通过比较磁阻之差读出<sup>[9]</sup>的优势，但却显著增大了存内位逻辑运算

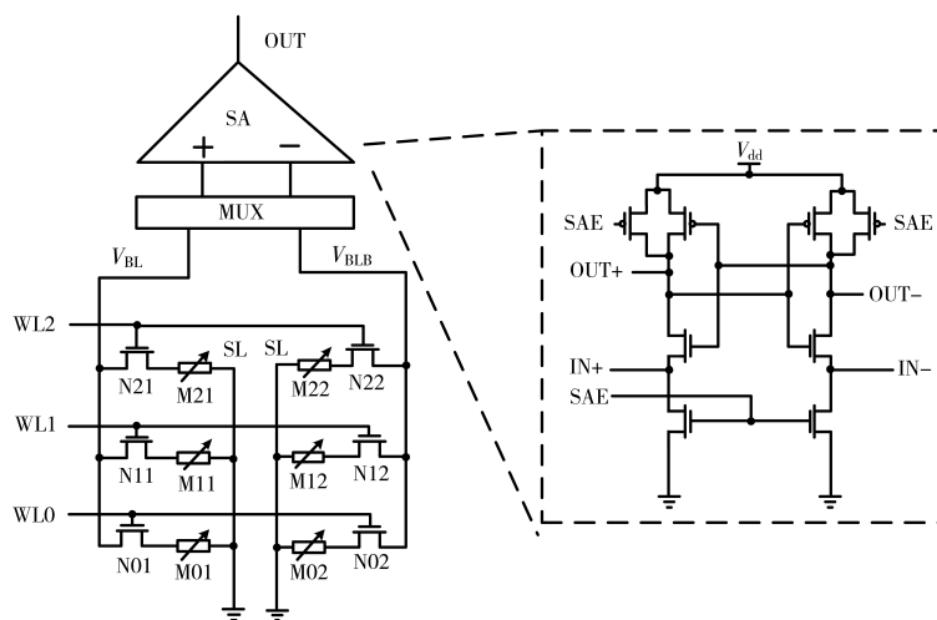

单元的面积。为了进一步提升存内运算单元的密度<sup>[12]</sup>，本文提出一种基于 1T1MTJ 加参考单元结构的一种改进型存内位逻辑运算方案，如图 2 所示。该方案将上述方案的三组 2T2MTJ 单元简化为三组 1T1MTJ 结构，三根控制位线的控制逻辑与 2T2MTJ 方案相同。而参考单元结构由三组高阻态和低阻态的磁隧道结两两并联而成，在 PVT 变化下，保持感测余度不降低<sup>[13]</sup>。本方案中的灵敏放大器的输出是互补型结构，因此 OUT+端口输出的功能与 2T2MTJ 方案相同，即可进行“与”和“或”运算，而 OUT-端口输出还可进行额外的“与非”和“或非”运算。表 1 所示是真值表中展示了设高阻态为“1”、设低阻态为“0”时的运算示例结果。

图 2 1T1MTJ 阵列的范例

图 1 文献[9]2T2MTJ 阵列范例(内插图为电流型互补灵敏放大器)

图 1 内插展示了本方案中的电流型互补灵敏放大器结构<sup>[14]</sup>，应用于图 2，该结构在比较放大前需要进行预充电操作<sup>[11, 14]</sup>。读取操作可分为三个阶段，由外界时序控制信号(SAE、 $WL_0 \sim WL_n$ )控制。以单个位逻辑运算单元为例，即只包含 SAE 使能信号与三路控制位信号( $WL_0 \sim WL_2$ )：在第一阶段，四路控制信号均设为低电平，灵敏放大器首先进行预充电，然后将 OUT+与 OUT-输出电压抬升至  $V_{dd}$ ；第二阶段为感应阶段，四路控制信号均设为高电平，OUT+与 OUT-端均开始放电；在 OUT+与 OUT-端形成互补信号后，进入第三阶段，此时将 SAE 设为高电平，对 OUT+与 OUT-输

# 微电子技术

## Microelectronic Technology

表 1 1T1MTJ 存内位逻辑运算真值表

| 逻辑标记<br>(M01) | 数据<br>(M11)   | 数据<br>(M21)   | 输出<br>OUT-    | 输出<br>OUT+ |

|---------------|---------------|---------------|---------------|------------|

| 与             | 0( $R_P$ )    | 0( $R_P$ )    | 0( $R_P$ )    | 1          |

| /             | 0( $R_P$ )    | 0( $R_P$ )    | 1( $R_{AP}$ ) | 1          |

| 与             | 0( $R_P$ )    | 1( $R_{AP}$ ) | 0( $R_P$ )    | 1          |

| 非             | 0( $R_P$ )    | 1( $R_{AP}$ ) | 1( $R_{AP}$ ) | 0          |

| 或             | 1( $R_{AP}$ ) | 0( $R_P$ )    | 0( $R_P$ )    | 1          |

| /             | 1( $R_{AP}$ ) | 0( $R_P$ )    | 1( $R_{AP}$ ) | 0          |

| 或             | 1( $R_{AP}$ ) | 1( $R_{AP}$ ) | 0( $R_P$ )    | 1          |

| 非             | 1( $R_{AP}$ ) | 1( $R_{AP}$ ) | 1( $R_{AP}$ ) | 0          |

出结果进行锁存<sup>[9]</sup>。在后续的电路仿真中,由于需要考虑到在实际电路中 MRAM 阵列的大小以及电路驱动下一级负载的能力,因此分别增加了位线输入电容  $C_B$  和负载输出电容  $C_L$ 。

### 1.2 1T1MTJ 存内位逻辑运算的典型读电路仿真结果

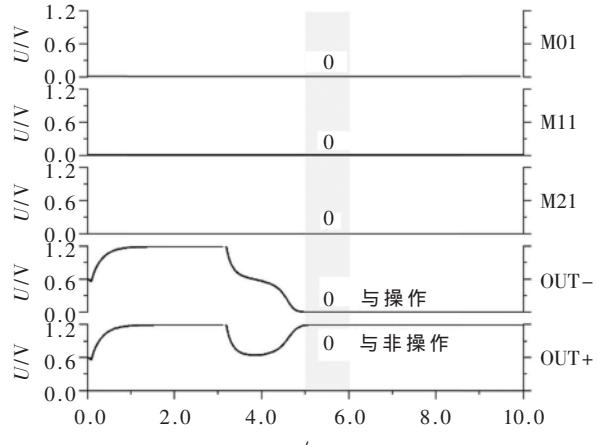

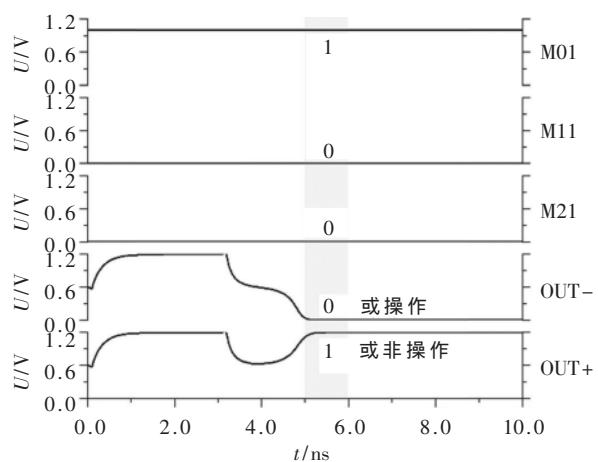

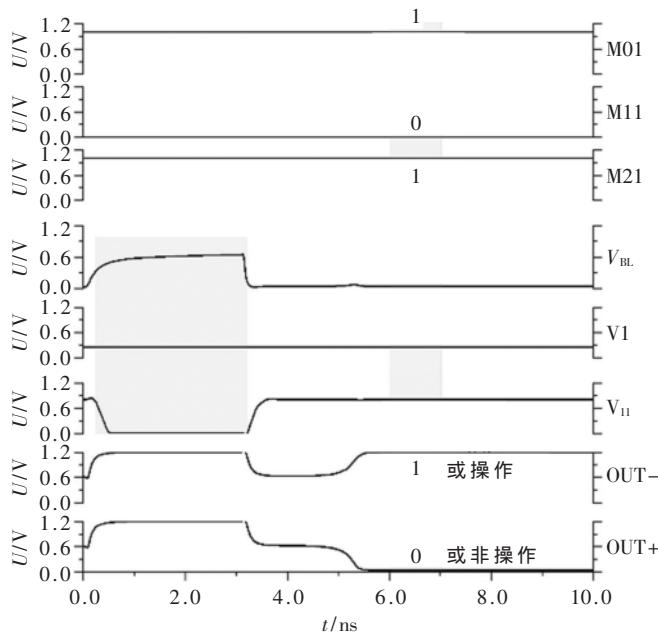

通过使用中芯国际 55 nm LL 逻辑工艺设计,仿真演示了上述基于 1T1MTJ MRAM 结构的改进存内位逻辑运算方案。图 3(a)和图 3(b)分别演示了“与”、“与非”操作和“或”、“或非”操作的瞬态波形,图中所用电源电压为  $V_{dd}=1.2$  V, MTJ 的 TMR=150%。

### 2 1T1MTJ 位逻辑运算方案的改进型高速灵敏放大器

图 1 内插展示的灵敏放大器结构除互补型输出外与上述 1T1MTJ 相同,属于典型的电流型结构<sup>[14]</sup>。该结构尽管整体功耗较低<sup>[14]</sup>,但却由于大阵列中位线电容  $C_B$  变大限制了在存内位逻辑运算中读取数据。因此,本文采用增加支路电压稳定电路的方法,提出了一种适用于存内位逻辑运算的高速灵敏放大器。如图 4 所示电路结构,在灵敏放大器输入两端分别增加了两个偏置型检测放大器(AMP),其作用是在电流型灵敏放大器(SA)感应阶段抬升存储阵列与参考阵列的位线(BL)的电压,提升 SA 的判决速度。AMP 的状态由输入电压 VI 控制,VI 应略大于晶体管开启电压以保证在灵敏放大的感应阶段中  $V_{11}$  和  $V_{22}$  的输出为高电平。图 5 展示了该改进型 SA 结构进行“或”和“或非”操作时的瞬态波形。其基本工作步骤与传统型结构基本相同,区别在于在第二(感应)阶段,当  $V_{BL}$  和  $V_{BLB}$  间形成电压差后,增强支路 AMP 将所检测到的所在支路电压  $V_{BL}/V_{BLB}$  分别与 VI 进行比较。当满足  $V_{11}/V_{22}$  从高电平变低电平条件后,N1/N2 管打开以稳定两条位线上的电压。当 N1/N2 开启后,OUT+/OUT-开始放电并逐渐形成互补信号。

如图 4 所示,传统的灵敏放大器电路 SA 的输入级

(a)“与”和“与非”

(b)“或”和“或非”

图 3 逻辑运算结果

图 4 改进型的灵敏放大器结构

分别连接一个检测放大器 AMP,SA 的两个输入级经过多路选择器分别连接 1T1MTJ 阵列和参考阵列。本文通

图 5 改进灵敏放大器读取工作原理

过中芯国际 55 nm LL 逻辑工艺设计改进灵敏放大器, 设置仿真温度  $T=27^{\circ}\text{C}$ , 来测试改进型灵敏放大器的性能。

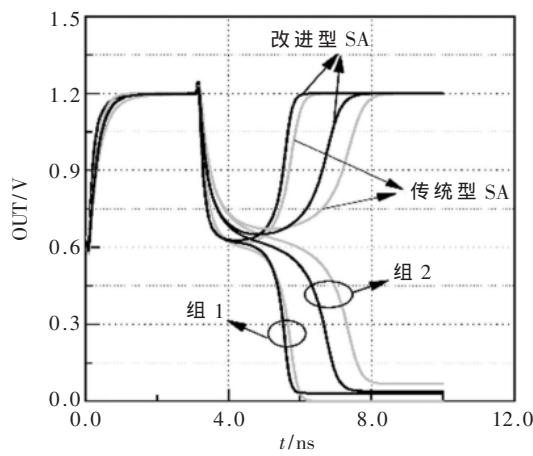

### 3.1 面对不同尺寸阵列的感测结果比较

首先通过电路仿真将图 2 所示的传统型 SA 与图 4 所示的改进型 SA 针对不同大小阵列的性能表现进行了比较, 仿真结果如图 6 所示, 其中  $V_{dd}=1.2\text{ V}$ 。在两组仿真中, 组 1 代表小尺寸阵列, 其中  $C_B=C_L=0.05\text{ pF}$ ; 组 2 代表大尺寸阵列, 其中  $C_B=C_L=0.5\text{ pF}$ 。如图 6 所示, 在面对小阵列与大阵列时, 改进型 SA 的感应速度比传统型 SA 分别快 0.3 ns 与 0.93 ns。该结果反映了面向大存内运算阵列时, 改进型 SA 有显著的感应速度优势。

图 6 两种灵敏放大器输出结果对比

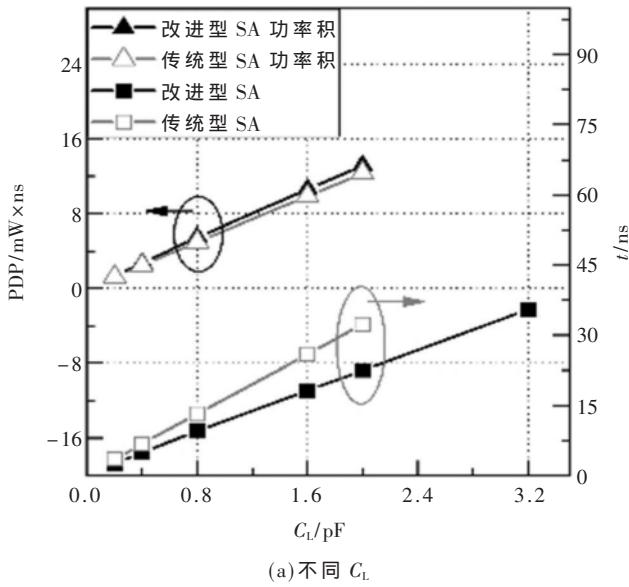

### 3.2 不同输入输出电容对放大器性能的影响

对在不同  $C_L$  和  $C_B$  的条件下的放大器对存储与参考阵列的感应放大性能进行了比较。同时假设  $R_P=3.5\text{ k}\Omega$ 、 $\text{TMR}=150\%$ , 参考阵列阻值为  $R_{ref}=6.25\text{ k}\Omega$ 。

此外, 为避免设置  $V_{dd}=1.2\text{ V}$  时出现传统型 SA 进入亚阈值状态而无法工作的状态, 将电源电压设为  $V_{dd}=1.8\text{ V}$ 。图 7(a)比较了  $C_L$  从 0.2 pF 增大至 3.2 pF 时两种 SA 的输出级连接下一级负载逐渐变大的性能变化, 图中  $C_B=0.5\text{ pF}$ 。如图 7(a)所示, 尽管改进型 SA 将存内位逻辑运算速度提升了 33%, 但是增加的两个 AMP 结构较传统型 SA 增加了额外 25% 的功耗。因此, 还引入功率积 (PDP)<sup>[12]</sup>, 即 SA 结构的整体功耗与感应速度的乘积, 来反映仅就两种 SA 结构本身的综合性能比较, PDP 越小则结构性能越好。如图 7(a)所示, 在  $C_L$  增大过程中, 改进型 SA 的 PDP 与传统型 SA 同步增加, 且略大于传统型 SA 的 PDP。图 7(b)比较了  $C_B$  从 0.2 pF 增大至 1.6 pF 时两型 SA 的存储阵列从小变化到大的性能变化, 图中  $C_L=0.5\text{ pF}$ 。如图 7(b)所示, 改进型 SA 的 PDP 在  $C_B=0.2\text{ pF}$  时大于传统型 SA 的 PDP。当  $C_B=0.8\text{ pF}$  时改进型 SA 的

(a) 不同  $C_L$ (b) 不同  $C_B$

图 7 两种 SA 的感应速度与 PDP 比较

PDP 较传统型 SA 的小 5%。当  $C_B$  进一步增大时, 改进型 SA 的 PDP 仍可以较小的斜率增加。相较而言, 传统型 SA 则无法工作。因此, 可以认为在面向大存储阵列时, 改进型 SA 较传统型 SA 有显著的性能优势。

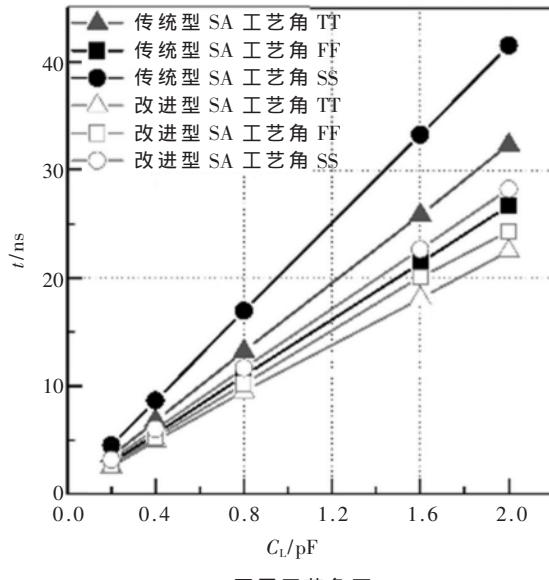

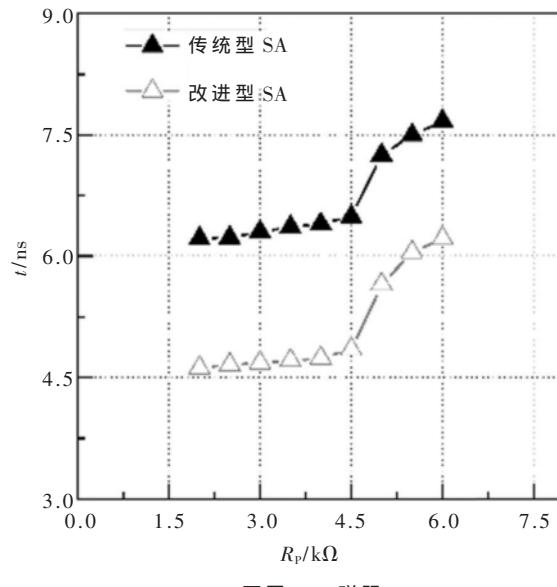

### 3.3 工艺角和不同磁阻下的放大器仿真

为了进一步验证本文提出的方案, 仿真分析比较了改进型 SA 与传统型 SA 在不同工艺角条件下以及不同 MTJ 磁阻情况下的读取性能。根据图 1 内插展示的灵敏放大器电路结构, 可将灵敏放大器的读出时间<sup>[15]</sup>定义为  $t$ :

$$t = \frac{C_B \times \Delta V}{I} \quad (1)$$

式中,  $C_B$  为位线电容,  $\Delta V$  读取过程中两条位线上的电压摆幅,  $I$  为位线放电电流。在图 8(a)中, 采用与 3.2 节相同的 MTJ 典型阻值, 比较了  $C_L$  从 0.2 pF 增大至 2 pF 时两种 SA 在 TT、FF、SS 工艺角下的感应时间变化。如图 8(a)所示, 当  $C_B=0.5$  pF 时, 在不同工艺角下, 改进型 SA 所用读出时间均小于传统型 SA。图 8(b)展示了在  $R_p$  从 1 kΩ 增大至 6 kΩ, 图中 TMR 保持在 150%, 参考单元按照  $R_{ref} = ((R_p + R_{AP}) / (R_{AP} + R_p))$  关系从 1.75 kΩ 增大到 10.5 kΩ 时两种 SA 读出时间的变化。当  $C_L=0.5$  pF 和  $C_B=0.5$  pF 时, 如图 8(b)所示, 在不同的 MTJ 阻值下, 改进型 SA 的读出时间均小于传统型 SA。此外, 当  $R_p > 4.5$  kΩ 时, 即超过两种 SA 的设计输入负载值时, 读取电流  $I$  急剧变小会导致读出时间的骤然增大。

## 4 结论

本文基于 1T1MTJ 的 MRAM 存储阵列提出了一种改进型存内位逻辑计算方案, 阵列密度较基于 2T2MTJ 的方案显著提高。而该方案读出电路的互补型输出能实现“与”、“或”运算外, 还能同时完成“与非”和“或非”的运算功能。此外, 针对传统型灵敏放大器的读出时间受

限于位线电容  $C_B$  的问题, 本文提出了一种适用于上述方案的改进型高速灵敏放大器, 通过增加支路电压稳定电路来提升灵敏放大器的读取速度。理论分析与仿真结果表明, 该方案相较传统的灵敏放大器, 不仅读取速度提升了 33%, 在适配大型存储阵列 ( $C_B \geq 0.8$  pF) 时还拥有更强的读取能力与更优的功率积(PDP)。

### 参考文献

- [1] APALKOV D , BERNARD D , SLAUGHTER J M . Magnetoresistive random access memory[J]. Proceedings of the IEEE , 2016 , 104(10): 1796–1830.

- [2] SEO M K , SIM S H , OH M H , et al. A 130-nm 0.9-V 66-MHz 8-Mb(256K×32) local SONOS embedded flash EEPROM[J]. IEEE Journal of Solid-State Circuits , 2005 , 40 (4): 877–883.

- [3] KIM C , KWON K , PARK C . A covalent-bonded cross-coupled current-mode sense amplifier for STT-MRAM with 1T1MTJ common source-line structure array[C]. IEEE International Solid-state Circuits Conference , 2015.

- [4] RIZZO N D , HOUSSEMEDDINE D , JANESKY J , et al. A fully functional 64 Mb DDR3 ST-MRAM built on 90 nm CMOS technology[J]. IEEE Transactions on Magnetics , 2013 , 49(7): 4441–4446.

- [5] LIN C J , KANG S H , WANG Y J , et al. 45 nm low power CMOS logic compatible embedded STT MRAM utilizing a reverse-connection 1 T/1MTJ cell[C]. Proceedings of IEEE International Electron Devices Meeting , 2009.

- [6] WULF W A , MCKEE S A . Hitting memory wall: implications obvious[J]. ACM SIGARCH Computer Architecture News , 1995 , 23(1): 20–24.

- [7] JAIN S , RANJAN A , ROY K , et al. Computing in memory with spin-transfer torque magnetic RAM[J]. IEEE Transac-

(a) 不同工艺角下

(b) 不同 MTJ 磁阻

(下转第 50 页)

# 微电子技术

## Microelectronic Technology

- [8] HALLIN J , KJELLBERG T , SWAHLN T.A 100-Gb/s 1:4 demultiplexer in InP DHBT technology[C].2006 IEEE Compound Semiconductor Integrated Circuit Symposium , 2006.

- [9] KARNFELT C , HALLIN J , KJELLBERG T , et al.Flip-chip mounted 1:4 demultiplexer IC in InP DHBT technology operating up to 100 Gb/s[C].2007 European Microwave Conference , 2007.

- [10] 唐霆宇.一种小型化超宽带接收前端的设计与实现[J].

电子技术应用 , 2019 , 45(6) : 11-14.

- [11] 孙帆, 黄海波, 卢军, 等.一种新型的 12 位 SAR ADC 设计[J]. 电子技术应用 , 2019 , 45(11) : 36-41.

(收稿日期: 2020-01-02)

### 作者简介:

周浩(1995-), 男, 硕士研究生, 主要研究方向: 超高速 InP 集成电路设计。

张有涛(1979-), 男, 博士, 高级工程师, 主要研究方向: 混合信号集成电路设计。

(上接第 39 页)

- zero cancellation for multistage amplifiers[C]. International Conference on Microelectronics , 2007.

- [6] SANSEN W M C. 模拟集成电路设计精粹[M]. 陈莹梅, 译. 北京: 清华大学出版社 , 2007.

- [7] Fan Xiaohua , MISHRA C , SANCHEZ-SINENCIO E. Single Miller capacitor frequency compensation technique for low-power multistage amplifiers[J]. IEEE Journal of Solid-State Circuits , 2005 , 40(3) : 584 - 592.

- [8] TAN M , KI W H. A cascode Miller-compensated three-stage amplifier with local impedance attenuation for optimized complex-pole control[J]. IEEE Journal of Solid-State Circuits ,

2015 , 50(Z) : 440 - 449.

(收稿日期: 2019-12-15)

### 作者简介:

和雨(1995-), 女, 硕士研究生, 主要研究方向: 模拟集成电路设计。

肖知明(1983-), 男, 博士, 研究员, 主要研究方向: 电源管理、模拟/射频集成电路设计。

王宇(1996-), 女, 硕士研究生, 主要研究方向: 模拟集成电路设计。

胡伟波(1982-), 通信作者, 男, 博士, 研究员, 主要研究方向: 模/数、数/模转换器、无线感知芯片和系统实现, 第三代半导体, 生物芯片。

(上接第 44 页)

- tions on Very Large Scale Integration Systems , 2018 , 26(3) : 470-483.

- [8] NOGUCHI H , TAKEDA S , NOMURA K , et al. Variable nonvolatile memory arrays for adaptive computing systems[C]. International Electron Devices Meeting(IEDM) , 2013.

- [9] Kang Wang , Wang Haotian , Wang Zhaohao. In-memory processing paradigm for bitwise logic operations in STT-MRAM[J]. IEEE Transactions on Magnetics , 2017 , 53(11).

- [10] PATTERSON D , ANDERSON T , CARDWELL N , et al. A case for intelligent RAM[J]. IEEE Micro , 1997 , 17(2) : 34-44.

- [11] LEE H , ALZATE J G , DORRANCE R , et al. Design of a fast and low-power sense amplifier and writing circuit for high-speed MRAM[J]. IEEE Transactions on Magnetics , 2014 , 51(5) : 1-7.

- [12] DONG Q , WANG Z , LIM J , et al. A 1 Mb 28 nm STT-MRAM with 2.8 ns read access time at 1.2 V VDD using single-cap offset-cancelled sense amplifier and

in-situ self-write-termination[C]. IEEE International Solid-state Circuits Conference , 2018.

- [13] NA T , KIM J , KIM J P , et al. Reference-scheme study and novel reference scheme for deep submicrometer STT-RAM[J]. IEEE Transaction on Circuits System I , 2014 , 23 (4) : 3376-3385.

- [14] ZHAO W S , CHAPPERT C , JAVERLIAC V , et al. High speed, high stability and low power sensing amplifier for MTJ/CMOS hybrid logic circuits[J]. IEEE Transaction on Magnetics , 2009 , 45(10) : 3784-3787.

- [15] 周永亮. 基于 65 nm SRAM 的低失调自启动灵敏放大器的分析与设计[D]. 合肥: 安徽大学 , 2017.

(收稿日期: 2020-02-14)

### 作者简介:

陆楠楠(1990-), 男, 硕士研究生, 主要研究方向: 新型存储器电路设计。

王少昊(1981-), 男, 博士研究生, 副教授, 主要研究方向: 非线性光学、光子集成电路、新型存储器电路设计。

黄继伟(1976-), 通信作者, 男, 博士研究生, 副教授, 主要研究方向: 射频、模拟集成电路、MEMS 技术。

## 版权声明

经作者授权，本论文版权和信息网络传播权归属于《电子技术应用》杂志，凡未经本刊书面同意任何机构、组织和个人不得擅自复印、汇编、翻译和进行信息网络传播。未经本刊书面同意，禁止一切互联网论文资源平台非法上传、收录本论文。

截至目前，本论文已经授权被中国期刊全文数据库（CNKI）、万方数据知识服务平台、中文科技期刊数据库（维普网）、DOAJ、美国《乌利希期刊指南》、JST 日本科技技术振兴机构数据库等数据库全文收录。

对于违反上述禁止行为并违法使用本论文的机构、组织和个人，本刊将采取一切必要法律行动来维护正当权益。

特此声明！

《电子技术应用》编辑部

中国电子信息产业集团有限公司第六研究所