# X 频段接收组件三维 SiP 微系统设计

付 浩, 刘德喜, 祝大龙, 齐伟伟

(北京遥测技术研究所, 北京 100094)

**摘要:** 针对 X 频段多波束相控阵组件小型化、模块化的设计需求, 结合多芯片组件技术、微波毫米波高密度垂直互连技术, 利用 HFSS 对半开放式准同轴引脚进行优化设计, 同时采用上下腔三维布局方式, 设计了以 ML-SL-SL-CPWG 和 ML-SL-CPWG 作为无引线引脚的小型化 X 频段接收组件 SiP 微系统模块。接收组件增益  $\geq 32.8$  dB, 噪声系数  $\leq 3.0$  dB, 整个模块体积仅为  $12.5 \text{ mm} \times 15 \text{ mm} \times 5.4 \text{ mm}$ , 较原有二维平面链路系统面积缩小了 63%, 体积缩小了 76%, 同时模块化设计在系统应用中具有极大的优势。

**关键词:** 接收组件; 系统级封装; 高温共烧陶瓷; 小型化

中图分类号: TN454

文献标识码: A

DOI: 10.16157/j.issn.0258-7998.191396

中文引用格式: 付浩, 刘德喜, 祝大龙, 等. X 频段接收组件三维 SiP 微系统设计[J]. 电子技术应用, 2020, 46(7): 7-9, 14.

英文引用格式: Fu Hao, Liu Dexi, Zhu Dalong, et al. Design of 3D SiP microsystems for X-band receive[J]. Application of Electronic Technique, 2020, 46(7): 7-9, 14.

## Design of 3D SiP microsystems for X-band receive

Fu Hao, Liu Dexi, Zhu Dalong, Qi Weiwei

(Beijing Research Institute of Telemetry, Beijing 100094, China)

**Abstract:** Aiming at the design requirements of miniaturization and modularization of X-band multi-wave phased array components, this paper designs a SiP receiving module combining multi-chip module technology and microwave millimeter wave high-density vertical interconnection technology. Using HFSS to optimize the design of the semi-open quasi-coaxial structure, and using the three-dimensional layout of the double sided multi-cavity, the ML-SL-SL-CPWG and ML-SL-CPWG were designed as the no-lead pins for the X-band receiving SiP module. Receiver component gain  $\geq 32.8$  dB, noise figure  $\leq 3.0$  dB. And the module volume is only  $12.5 \text{ mm} \times 15 \text{ mm} \times 5.4 \text{ mm}$ , which is 63% area smaller and 76% volume smaller than the original two-dimensional planar system. At the same time, modular design has great advantages in system application.

**Key words:** receiving components; system in package; HTCC; miniaturization

## 0 引言

组件作为相控阵系统核心关键部分, 占据着整机尺寸的一大半部分, 其成本甚至可以高达整个相控阵系统的 60%<sup>[1]</sup>。随着射频微波电路的快速发展, 传统的二维独立封装集成方式很难满足现在系统需求, 对组件模块的小型化、多芯片模块技术(Microwave Multi-chip Module, MMCM)、系统级封装(System in Package, SiP)以及射频链路三维集成提出了更高的要求<sup>[2]</sup>。针对当前复杂的电磁环境以及全空域多波束的测控需求, 研究和设计体积更小、成本更低、性能更优、可靠性更高的组件具有重要意义。

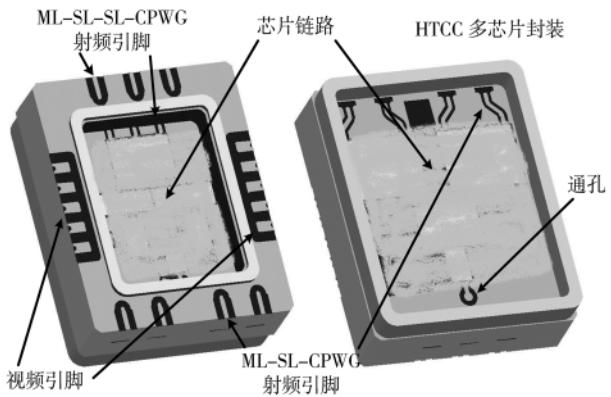

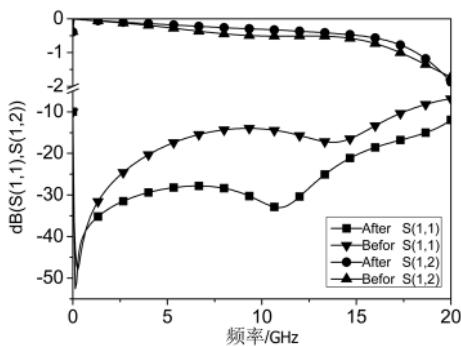

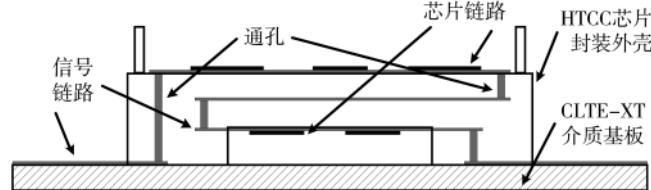

本文应用 SiP 技术中多芯片封装技术(Multi-Chip Package, MCP)将 X 频段接收组件射频链路进行了如图 1 所示的上下腔三维小型化高密度封装, 大大缩减了组件模块体积, 可实现对 X 频段左、右旋来波信号的滤波、低噪声放大、数控移相及衰减, 最终形成四波束输出, 供后端进行数据处理。

图 1 接收组件三维示意图

## 1 接收组件系统设计

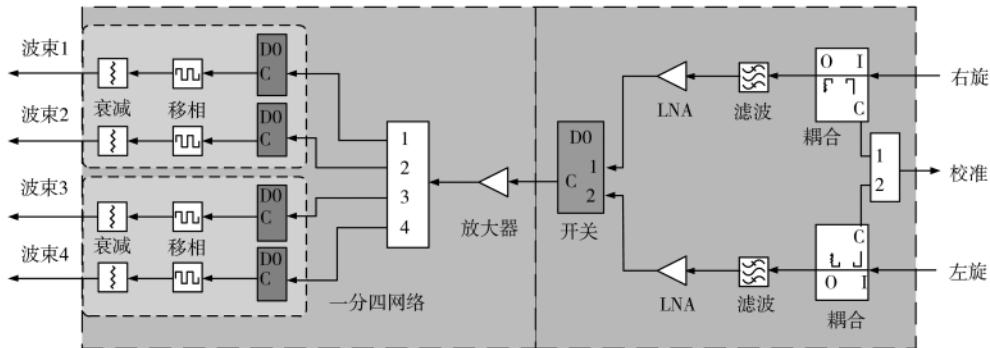

多波束接收组件原理框图如图 2 所示, 为满足组件的高性能、小型化设计需求, 采用了射频裸芯片表贴方式, 主要的射频芯片包括耦合组件、前端滤波器、低噪

图 2 接收组件原理框图

放、开关、一分四网络及实现信号移相衰减的数控多能芯片。来波信号经校准耦合单元、滤波器送至低噪声放大器,信号放大后,利用开关芯片选择所接收来波信号的极化方式,之后对信号进行了二级放大,并将信号分成4路,分别将4波束接收信号输出组件。

表1所给出的是接收组件链路指标分配,包含增益、电压驻波比和噪声系数,噪声级联公式如下<sup>[3]</sup>:

$$NF = NF_1 + \frac{NF_2 - 1}{G_1} + \frac{NF_3 - 1}{G_1 G_2} + \dots + \frac{NF_n - 1}{G_1 G_2 G_3 \dots G_{n-1}} \quad (1)$$

式中,  $NF_n$  为第  $n$  级器件噪声,  $G_n$  为第  $n$  级增益。由式(1)不难得出,在链路中前级级联器件的噪声对整个链路噪声起主要决定作用,所以组件选用噪声系数较小的耦合器、低噪放等作为级联前级<sup>[4]</sup>,经计算整个链路噪声系数小于 2.61 dB,链路总增益为 32.8 dB。

表 1 组件各级参数指标

| 器件名称   | Gain/dB | VSWR | NF/dB | 链路噪声/dB | 增益/dB |

|--------|---------|------|-------|---------|-------|

| 耦合器组件  | -0.2    | 1.2  | 0.2   | 0.2     | /     |

| 滤波器    | -1.5    | 1.5  | 1.5   | 1.7     | /     |

| 低噪声放大器 | 27      | 1.5  | 0.9   | 2.6     | /     |

| 旋向开关   | -1      | 1.4  | 1     | 2.6     | /     |

| 驱动放大器  | 28      | 1.5  | 1.5   | 2.6     | /     |

| 一分四网络  | -6.5    | 1.2  | 0.5   | 2.6     | /     |

| 多功能芯片  | -12     | 1.5  | 12    | 2.61    | /     |

| 结构过渡   | -1      | 1.2  | 1     | 2.61    | 33.8  |

## 2 多芯片三维 SiP 设计

为解决传统电路面积较大、接插件种类数量较多、模块灵活性较差等存在的问题,设计了一种基于半开放式准同轴引脚的上下腔多芯片封装模块,可实现上述多芯片链路的高密度三维 SiP 集成<sup>[5]</sup>。模块组件正面采用金属可伐框起腔设计,背面则采用 HTCC 多层介质基板开腔设计,正反面射频链路则通过垂直互连技术由中间层带状线实现互连。

### 2.1 多芯片封装引脚

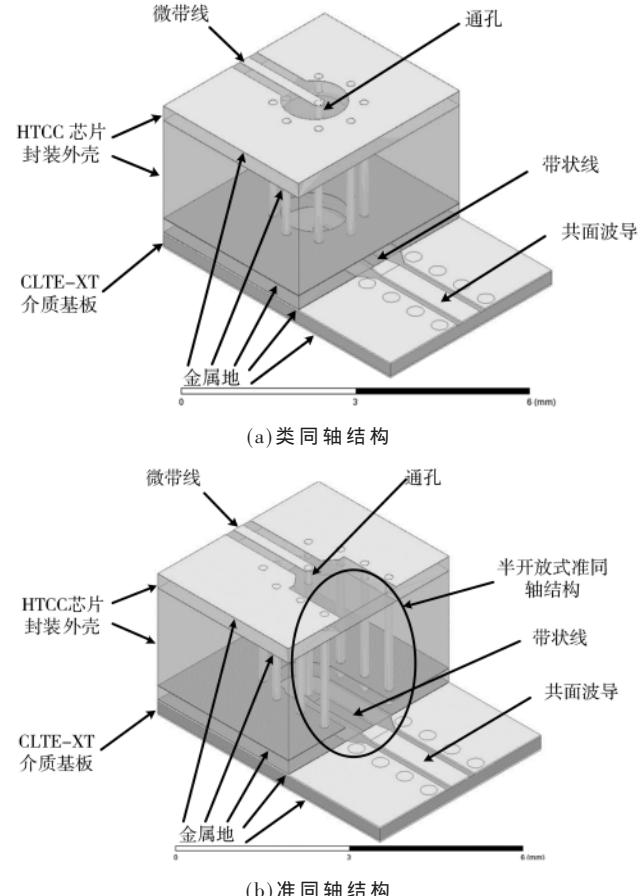

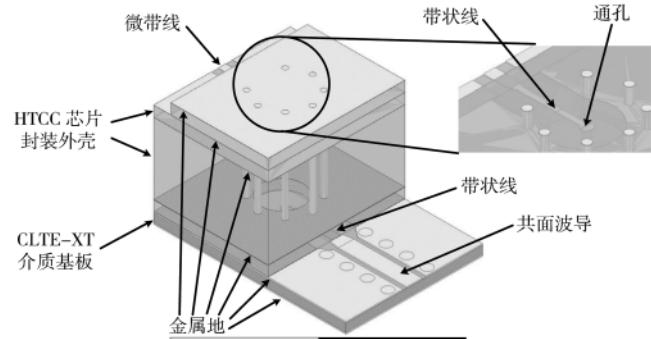

图 3 为 HFSS 软件中多种过渡结构的三维引脚模型,上边部分为多层陶瓷介质共烧形成的多芯片封装,HTCC 外壳中间层多层金属地对引脚过渡性能影响较

图 3 ML-SL-CPWG 引脚结构

小,因此为简化仿真并未在模型中体现,下部分则采用 CLTE-XT 作为介质基板。由 HTCC 微带线作为输入端,经半开放式准同轴结构,再由底层带状线过渡至共面波导,作为引脚输出。

采用图 3(b)所示准同轴结构是为了改善射频传输性能,同时避免规则的圆形反焊盘易激励其高次模谐振。针对传统类同轴结构进行了射频方向金属地开口的结构优化,将环绕型接地孔转换为半开放式准同轴结构,同时将陶瓷介质基板的金属地也做射频方向开口处理。

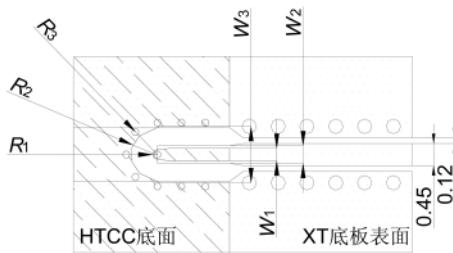

图 4 是上述引脚结构 HTCC 管壳与 XT 底板互联结

图 4 HTCC SiP 引脚关键尺寸

构关键尺寸平面结构图。对各个关键尺寸进行仿真优化后,选取垂直通孔焊盘半径  $R_1=0.1$  mm,通孔反焊盘半径  $R_2=0.5$  mm,准同轴结构中地孔距信号孔的距离  $R_3=0.8$  mm,HTCC 输出线宽  $W_1=0.25$  mm,XT 底板与 HTCC 输出线焊接部分线宽  $W_2=0.36$  mm,准同轴金属地开口宽度  $W_3=1.15$  mm,最终过渡至 0.508 mm 厚 CLTE-XT 底板线宽为 0.45 mm 的标准 50  $\Omega$  共面波导传输线。

如图 5 所示,对比类同轴与准同轴仿真结果,可以看出在 DC~15 GHz 内  $S_{11}$  小于  $-20$  dB,在 X 频段  $S_{11}$  优于  $-30$  dB,在高频 12 GHz 处  $S_{21}$  仅为 0.37 dB,较传统类同轴 ML-SL-CPWG 引脚传输性能有较为明显的提升。

图 5 ML-SL-CPWG 引脚仿真对比

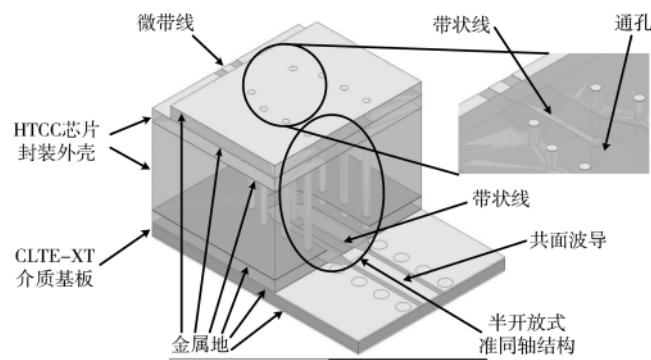

同时对如图 6(a)所示的 ML-SL-SL-CPWG 的半开放准同轴引脚进行了建模优化对比。由仿真结果可知,ML-SL-SL-CPWG 引脚在 X 频段  $S_{11}$  小于  $-25$  dB,12 GHz 处  $S_{12}$  为 0.44 dB。通过两类引脚的对比可以看出,半开放式准同轴过渡结构可以优化提升 HTCC 与介质基板之间射频信号的高效传输,为 HTCC 多芯片封装 SiP 模块提供了可靠的互连方案。

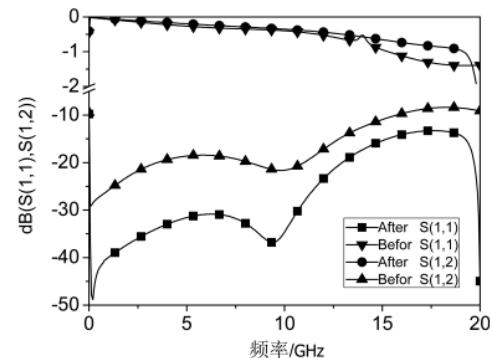

## 2.2 上下腔三维链路布局

整个接收组件射频链路从旋向选择开关之后分为上下腔两部分,实现了射频链路在垂直方向上的叠加,如图 7 所示。实现了链路小型化的同时,将两级放大器分别置于正面腔与背面腔中,避免了敏感芯片之间的电磁串扰。

该 HTCC 模块共有 21 层陶瓷介质,L1 层为正面射频电路层,L5 层为 HTCC 陶瓷基板内带状线传输层,L8~L10 层为整个接收组件电源、时钟、使能、锁存以及数据 I/O 层,L12 层背面为背面腔体内的射频电路层,

(a) 类同轴结构

(b) 准同轴结构

(c) 仿真结果

图 6 ML-SL-SL-CPWG 引脚

图 7 组件三维布局示意图

L13~L21 层在陶瓷板中间开 7.8 mm×9.8 mm 的空腔,形成背面腔体,整个接收组件小模块体积为 12.5 mm×15 mm×5.4 mm。

接收组件模块化设计,使得整个多波束系统具有极高的灵活性、可重构性,模块化设计大大减少了结构过

(下转第 14 页)

小。这种隔离器的设计方法简单,易于操作,其结构很适合嵌入常规的集成电路电源网上。

#### 参考文献

- [1] HONG J S. Microstrip filters for RF/microwave applications[M]. Hoboken, New Jersey: John Wiley & Sons, 2011.

- [2] 徐海燕,陈鹤鸣.大入射角一维磁光子晶体宽带光隔离器[J].光子学报,2015,44(10):137-142.

- [3] 计量,张怀武,牛旭博.微波集成隔离器的仿真与设计[J].压电与声光,2013,35(4):614-616.

- [4] 邓晓东,彭承敏,徐光亮,等.隔离器负载用微波吸收材料的研制[J].电子元件与材料,2009,28(7):65-67,72.

- [5] 朱叶,王世山.一种用于差、共模噪声抑制的平面EMI扼流圈[J].电工电能新技术,2014,33(5):22-26.

- [6] 石立雄,官伯然.基于枝节加载开环谐振器的带阻隔离器设计[J].微波学报,2014,30(5):72-75.

- [7] 雷涛,吴良威,周瑞山,等.新型D-CRLH传输线宽带带阻隔离器设计[J].电子元件与材料,2018,37(1):62-65.

- [8] 王春阳,唐修连.基于折叠型谐振结构的宽带带阻隔离器的设计[J].电子器件,2018,41(4):950-953.

- [9] WU S H, LIN Y S. A wideband noise-isolation bandstop power distribution network using quarter-wavelength line-based structure[J]. IEEE Transactions on Components,

(上接第9页)

渡、接插件的种类和数量。

#### 3 结论

本文采用无引线式ML-SL-SL-CPWG和ML-SL-CPWG作为模块输入输出引脚,设计了X频段双通道四波束接收组件SiP模块,实现了射频链路的Z轴方向3D垂直堆叠,整个模块体积为12.5 mm×15 mm×5.4 mm,较现有平面链路系统面积缩小了63%,体积缩小了76%,小型化程度明显。同时,采用小模块设计也避免了一系列微组装工艺,有利于采用先进工艺和高效设备,实现机械化、自动化生产,缩短研制周期,降低生产成本。

多芯片封装外壳(MCP)作为SiP封装的典型应用<sup>[6-7]</sup>,拥有广阔的应用发展空间,小型一体化、高集成度封装是未来的射频链路系统发展方向,多腔体HTCC外壳的标准化、高效宽带也成为进一步的探索研究方向。

#### 参考文献

- [1] 王磊.基于多层板的多功能组件微波互联技术研究[J].电子技术应用,2019,45(6):7-10.

- [2] 周骏,窦文斌,沈亚,等.应用SIP技术的宽带板间垂直互连结构[J].固体电子学研究与进展,2012,32(1):36-39.

- [3] MOORE L, BARRETT J. Board-folding method for fabrication

Packaging and Manufacturing Technology, 2014, 4(6): 1071-1081.

- [10] REN S W, WU L S, PENG H L, et al. Quasi-elliptic wideband bandstop filter using stepped-impedance coupled line[J]. IEEE Microwaves and Wireless Components Letters, 2015, 25(6): 364-366.

- [11] CHEN F C, HU H T, LI R S, et al. Design of wide-stopband bandpass filter and diplexer using uniform impedance resonators[J]. IEEE Transactions on Microwave Theory and Techniques, 2016, 64(12): 4192-4203.

- [12] MALHERBE J A G. Wideband bandpass filter with extremely wide upper stopband[J]. IEEE Transactions on Microwave Theory and Techniques, 2018, 66(6): 2822-2827.

(收稿日期:2020-01-12)

#### 作者简介:

张志文(1997-),男,硕士研究生,主要研究方向:集成电路设计、射频电路设计。

王策兴(1995-),男,硕士研究生,主要研究方向:集成电路设计、射频电路设计。

粟涛(1977-),通信作者,男,博士,副教授,主要研究方向:集成电路设计、集成电路射频电动力学,E-mail:sutao@mail.sysu.edu.cn。

of 3-D system in package devices[J]. IEEE Transaction on Components, Packaging and Manufacturing Technology, 2012, 2(7): 1209-1216.

- [4] 唐霆宇.一种小型化超宽带接收前端的设计与实现[J].电子技术应用,2019,45(6):11-14.

- [5] 郭超,何其胜.Ka波段多通道接收机研制[J].微波学报,2017,33(8):108-111.

- [6] He Shuwei, Huang Zhi, Wang Dong, et al. A LTCC-BGA multi-chip packaging technology for MMICs up to Ku-band[C]. 2014 15th International Conference on Electronic Packaging Technology, 2014: 138-140.

- [7] Jia Shiwang, Han Wei, Liu Weiwei. Design and implementation of a Ka band tile-type receiver module[J]. Radio Communications Technology, 2018, 44(3): 301-305.

(收稿日期:2019-12-19)

#### 作者简介:

付浩(1995-),男,硕士研究生,主要研究方向:微波毫米波电路与系统。

刘德喜(1973-),男,硕士,研究员,主要研究方向:微波毫米波电路与系统。

祝大龙(1980-),男,博士,研究员,主要研究方向:微波毫米波电路与系统。

## 版权声明

经作者授权，本论文版权和信息网络传播权归属于《电子技术应用》杂志，凡未经本刊书面同意任何机构、组织和个人不得擅自复印、汇编、翻译和进行信息网络传播。未经本刊书面同意，禁止一切互联网论文资源平台非法上传、收录本论文。

截至目前，本论文已经授权被中国期刊全文数据库（CNKI）、万方数据知识服务平台、中文科技期刊数据库（维普网）、DOAJ、美国《乌利希期刊指南》、JST 日本科技技术振兴机构数据库等数据库全文收录。

对于违反上述禁止行为并违法使用本论文的机构、组织和个人，本刊将采取一切必要法律行动来维护正当权益。

特此声明！

《电子技术应用》编辑部

中国电子信息产业集团有限公司第六研究所