Thomas Cameron博士

ADI公司通信业务部CTO

# 5G毫米波无线电 射频技术

## 简介

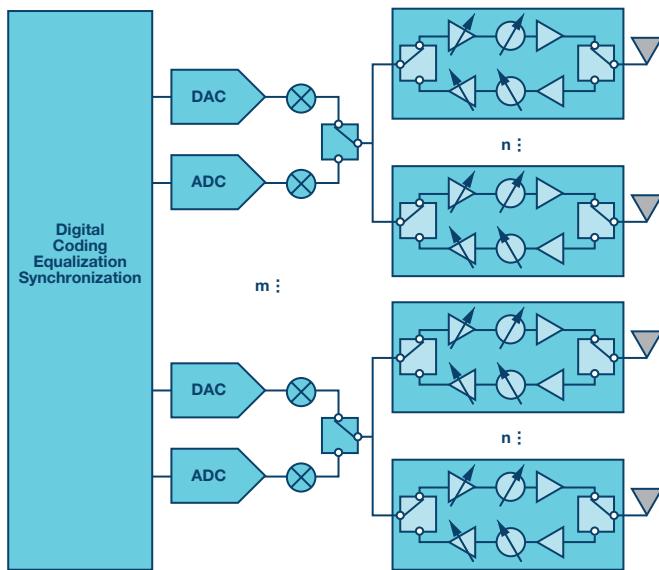

业界普遍认为，混合波束赋形（例如图1所示）将是工作在微波和毫米波频率的5G系统的首选架构。这种架构综合运用数字（MIMO）和模拟波束赋形来克服高路径损耗并提高频谱效率。如图1所示， $m$ 个数据流的组合分割到 $n$ 条RF路径上以形成自由空间中的波束，故天线元件总数为乘积 $m \times n$ 。数字流可通过多种方式组合，既可利用高层MIMO将所有能量导向单个用户，也可以利用多用户MIMO支持多个用户。

图1. 混合波束赋形框图

本文将考察一个简单的大规模天线阵列示例，借以探讨毫米波无线电的最优技术选择。现在深入查看毫米波系统无线电部分的框图，我们看到一个经典超外差结构完成微波信号到数字信号的变换，然后连接到多路射频信号处理路径，这里主要是运用微波移相器和衰减器来实现波束赋形。

传统上，毫米波系统是利用分立器件构建，导致其尺寸较大且成本较高。这样的系统里面的器件使用CMOS、SiGe BiCMOS和GaAs等技术，使每个器件都能得到较优的性能。例如，数据转换

器现在采用CMOS工艺开发，使采样速率达到GHz范围。上下变频和波束赋形功能可以在SiGe BiCMOS中有效实现。根据系统指标要求，可能需要基于GaAs功率放大器和低噪声放大器，但如果SiGe BiCMOS能够满足要求，利用它将能实现较高的集成度。

对于5G毫米波系统，业界希望将微波器件安装在天线基板背面，这要求微波芯片的集成度必须大大提高。例如，中心频率为28 GHz的天线的半波阵子间距约为5 mm。频率越高，此间距越小，芯片或封装尺寸因而成为重要考虑因素。理想情况下，单波束的整个框图都应当集成到单个IC中；实际情形中，至少应将上下变频器和RF前端集成到单个RFIC中。集成度和工艺选择在某种程度上是由应用决定的，在下面的示例分析中我们将体会到这一点。

## 示例分析：天线中心频率为28 GHz，EIRP为60 dBm

此分析考虑一个典型基站天线系统，EIRP要求为60 dBm。使用如下假设条件：

- ▶ 天线阵子增益 = 6 dBi (瞄准线)

- ▶ 波形PAPR = 10 dB (采用QAM的OFDM)

- ▶ P1dB时的功率放大器PAE = 30%

- ▶ 发射/接收开关损耗 = 2 dB

- ▶ 发射/接收占空比 = 70%/30%

- ▶ 数据流 = 8

- ▶ 各电路模块的功耗基于现有技术。

该模型以8个数据流为基础来构建，连接到不同数量的RF链。模型中的天线数量以8的倍数扩大，最多512个元件。

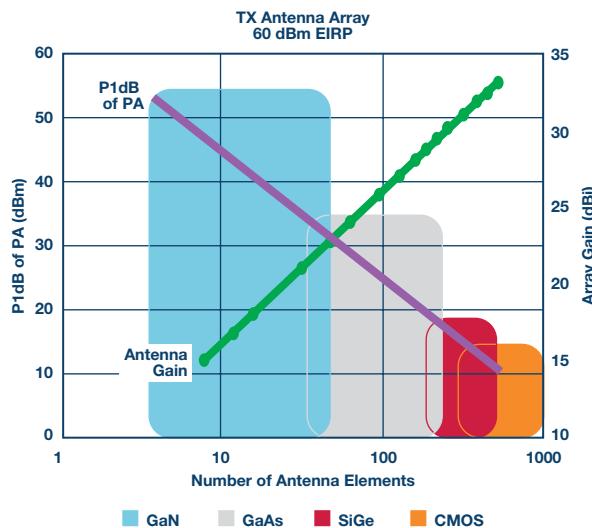

图2显示了功率放大器线性度随着天线增益提高而变化的情况。注意：由于开关损耗，放大器的输出功率要比提供给天线的功率高2 dB。当给天线增加元件时，方向性增益随着X轴对数值提高而线性提高，因此，各放大器的功耗要求降低。

为了便于说明，我们在曲线上叠加了技术图，指示哪种技术对不同范围的天线元件数量最佳。注意：不同技术之间存在重叠，这是因为每种技术都有一个适用的值范围。另外，根据工艺和电路设计实践，具体技术可以实现的性能也有一个范围。元件非常少时，各链需要高功率PA（GaN和GaAs），但当元件数量超过200时，P1dB降到20 dBm以下，处于硅工艺可以满足的范围。当元件数量超过500时，PA性能处于当前CMOS技术就能实现的范围。

图2. 天线增益与功率放大器输出水平要求的关系

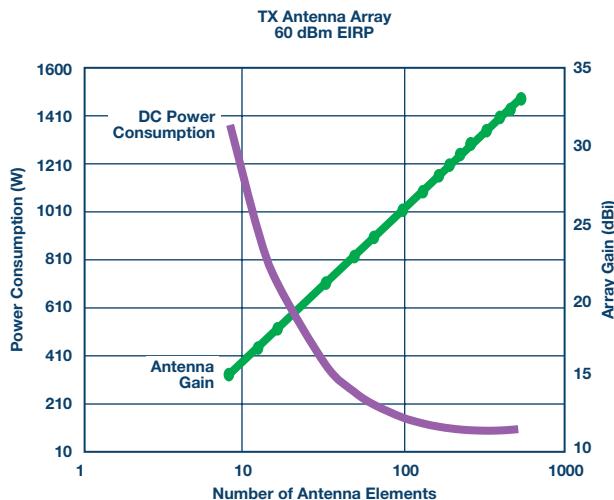

现在考虑元件增加时天线Tx系统的功耗，如图3所示。同预期一样，功耗与天线增益成反比关系，但有一个限值。超过数百元件时，PA的功耗不再占主导地位，导致效益递减。

图3. 天线增益与天线Tx部分直流功耗的关系

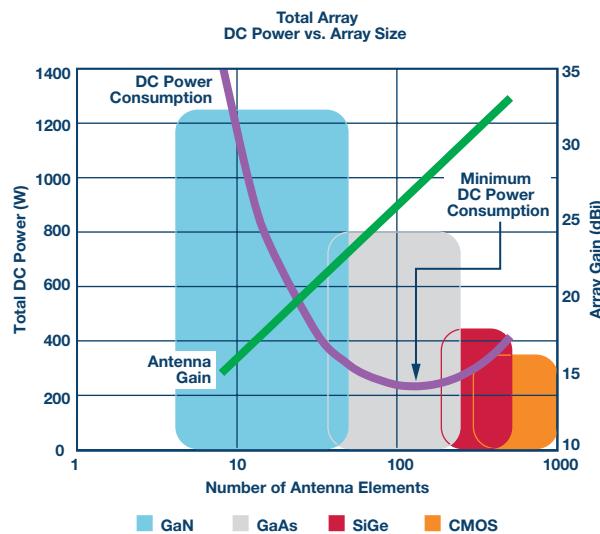

整个系统的功耗如图4所示（包括发射机和接收机）。同预期一样，接收机的功耗随着RF链的增加而线性提高。若将不断下降的Tx功耗曲线叠加在不断上升的Rx功耗曲线上，我们会观察到一个最低功耗区域。

本例中，最低值出现在大约128个元件时。回顾图2给出的技术图，要利用128个元件实现60 dBm的EIRP，最佳PA技术是GaAs。

虽然使用GaAs PA可以实现最低的天线功耗和60 dBm EIRP，但这可能无法满足系统设计的全部要求。前面提到，很多情况下要求将RFIC放在天线元件的 $\lambda/2$ 间距以内。使用GaAs发射/接收模块可提供所需的性能，但不满足尺寸约束条件。为了利用GaAs发射/接收模块，需要采用其他封装和布线方案。

优先选择可能是增加天线元件数量以使用集成到RFIC中的SiGe BiCMOS功率放大器。图4显示，若将元件数量加倍，达到约256时，SiGe放大器便能满足输出功率要求。功耗的增幅很小，而且可以把SiGe BiCMOS RFIC放到天线元件（28 GHz）的 $\lambda/2$ 间距以内。

将这一做法扩展到CMOS，我们发现CMOS也能实现整体60 dBm EIRP，但从技术图看，元件数量还要加倍。因此，这种方案会导致尺寸和功耗增加，考虑到电流技术限制，CMOS方法不是可行的选择。

图4. 整个天线阵列的直流功耗与天线增益的关系

我们的分析表明：同时考虑功耗和集成尺寸的话，当前实现60 dBm EIRP天线的最佳方案是将SiGe BiCMOS技术集成到RFIC中。然而，如果考虑将更低功耗的天线用于CPE，那么CMOS当然是可行的方案。

这一分析是基于当前可用技术，但毫米波硅工艺和设计技术正在取得重大进步。我们预计未来的硅工艺会有更好的能效和更高的输出功率能力，将能实现更小的尺寸并进一步优化天线尺寸。

随着5G的到来日益临近，设计人员将持续遇到挑战。为毫米波无线电应用确定最佳技术方案时，考虑信号链的所有方面和不同IC工艺的各种优势是有益的。随着5G生态系统不断发展，ADI公司依托独有的比特到毫米波能力，致力于为客户提供广泛的技术组合（包括各种电路设计工艺）和系统化方法。

## 在线支持社区

访问ADI在线支持社区，与ADI公司技术专家互动。提出您的棘手设计问题、浏览常见问题解答，或参与讨论。

[请访问ezchina.analog.com](http://ezchina.analog.com)

## 参考设计

Circuits from the Lab®参考设计由ADI工程师构建并测试，提供丰富的文档和经过工厂测试的评估硬件。

[请访问www.analog.com/cn/cftl](http://www.analog.com/cn/cftl)

**全球总部**

One Technology Way

P.O. Box 9106, Norwood, MA

02062-9106 U.S.A.

Tel: (1 781) 329 4700

Fax: (1 781) 461 3113

**大中华区总部**

上海市浦东新区张江高科园区

祖冲之路 2290 号展想广场 5 楼

邮编: 201203

电话: (86 21) 2320 8000

传真: (86 21) 2320 8222

**深圳分公司**

深圳市福田中心区

益田路与福华三路交汇处

深圳国际商会中心

4205-4210 室

邮编: 518048

电话: (86 755) 8202 3200

传真: (86 755) 8202 3222

**北京分公司**

北京市海淀区西小口路 66 号

中关村东升科技园

B-6 号楼 A 座一层

邮编: 100191

电话: (86 10) 5987 1000

传真: (86 10) 6298 3574

**武汉分公司**

湖北省武汉市东湖高新区

珞瑜路 889 号光谷国际广场

写字楼 B 座 2403-2405 室

邮编: 430073

电话: (86 27) 8715 9968

传真: (86 27) 8715 9931

©2016 Analog Devices, Inc. All rights reserved. Trademarks and registered trademarks are the property of their respective owners. Ahead of What's Possible is a trademark of Analog Devices.

T15301sc-0-11/16

[analog.com/cn](http://analog.com/cn)

超越一切可能™