# 一种浪涌保护电路的研究和设计

董大伟,李江陵

(中国电子信息产业集团有限公司,北京 100190)

**摘要:**浪涌冲击是电子产品常见问题之一,它经常造成电子产品的损坏。设计了一种新型的浪涌保护钳位电路,该保护电路包括一个基准电路以及一个反馈控制电路。基准电路在源电压超过钳位电压时根据源电压生成基准电压,反馈控制电路用于接收基准电压并将输出电压钳位到钳位电压。基于上华 0.18 μm CMOS 的工艺对其仿真,结果表明该电路可以很好地实现 38 V、27 V、18 V、10 V 的钳位,与传统的 TVS 二极管相比,具有低漏电流、恒定的钳位电压和接近于零的导通电阻等优点。

**关键词:**浪涌保护;钳位电路;TVS 二极管;集成电路

中图分类号: TN402

文献标识码: A

DOI: 10.16157/j.issn.0258-7998.200395

中文引用格式: 董大伟,李江陵. 一种浪涌保护电路的研究和设计[J]. 电子技术应用, 2020, 46(7): 74–77.

英文引用格式: Dong Dawei, Li Jiangling. Research and design of a surge protection circuit[J]. Application of Electronic Technique, 2020, 46(7): 74–77.

## Research and design of a surge protection circuit

Dong Dawei, Li Jiangling

(China Electronic Corporation, Beijing 100190, China)

**Abstract:** Surge shock is one of the major reliability issues in electronic products. It causes damage to electronic products. This paper investigated and designed a new type of surge protection clamp circuit, which includes a reference and a feedback control. The reference circuit generates a reference voltage based on the source voltage when the source voltage exceeds the clamping voltage, and the feedback control circuit is used to receive the reference voltage and clamp the output voltage to the clamping voltage. Based on the simulations of Shanghai 0.18 μm CMOS process, the results show that the circuit achieves 38 V, 27 V, 18 V, 10 V clamping. Compared with traditional TVS diodes, it has low leakage current and constant clamping voltage, and on-resistance is close to zero.

**Key words:** surge protection; clamp circuit; TVS diode; integrated circuit

## 0 引言

众所周知,电子产品在使用中经常会遇到意外的电压瞬变和浪涌,从而导致电子产品的损坏。损坏的原因是电子产品中的半导体器件(包括二极管、晶体管、可控硅等)被烧毁或击穿。据估计,电子产品的故障有 75% 是由于瞬变和浪涌造成的<sup>[1-5]</sup>。电压的瞬变和浪涌无处不在,电网、雷击、爆破,就连人在地毯上行走都会产生上万伏的静电感应电压,这些,都是电子产品的隐形致命杀手。

因此,为了提高电子产品的可靠性和人体自身的安全性,必须对电压瞬变和浪涌采取防护措施。

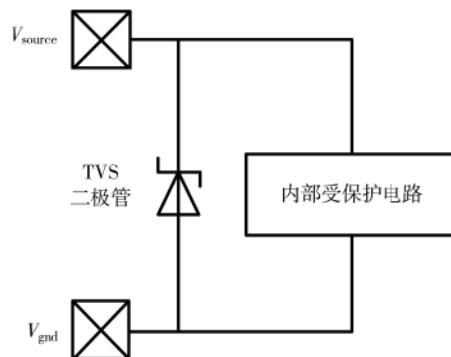

通常,采用浪涌保护器以确保提供给受保护电子设备的电压不超过其击穿电压。提供这种浪涌保护功能的常规设备包括瞬态电压抑制(TVS)二极管<sup>[6-7]</sup>和通过模拟电路实现的电压调节器<sup>[8-9]</sup>。常规的 TVS 二极管结构如图 1 所示。将 TVS 二极管与需保护电路或器件并联,

图 1 TVS 二极管原理图

当浪涌来临时,它能将电压钳位在一定值并且泄放大量电流,以此来保护内部电路不被击穿。

传统的 TVS 二极管其钳位电压会随着二极管吸收的电流变化而变化<sup>[10-12]</sup>。因此 TVS 二极管的钳位电压相比于其触发电压会更大,在 I-V 曲线中两者的斜率称为

# 微电子技术

Microelectronic Technology

TVS 二极管的导通动态电阻,显然具有高的动态电阻的钳位器件会导致浪涌保护机制不理想,因为为了令其钳位电压达到要求,必须将 TVS 二极管的触发电压设置为低于实际所需的钳位电压,这样会导致其触发电压过低引起 TVS 二极管的误触发。

为了避免上述问题,并提供更精确的浪涌保护解决方案,期望减小钳位器件的动态电阻从而使其钳位电压与电流水平无关。本文研究并设计了一种新型的浪涌保护钳位电路,该保护电路包括一个基准电路以及一个反馈控制电路。

## 1 浪涌保护钳位电路设计

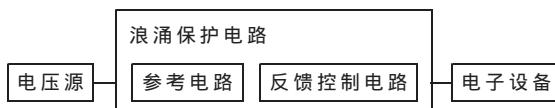

为了避免传统 TVS 二极管动态电阻变化导致的钳位电压变化,本文设计的浪涌保护钳位电路结构框图如图 2 所示。浪涌保护电路并联在所需保护电子设备的两端,其由参考电路和反馈控制电路两级组成。参考电路在源电压超过钳位电压时根据源电压生成基准电压,反馈控制电路用于接收基准电压并将输出电压钳位到钳位电压,同时由于反馈控制电路的存在,其钳位电压并不会随着电流变化而变化。

图 2 设计电路基本框图

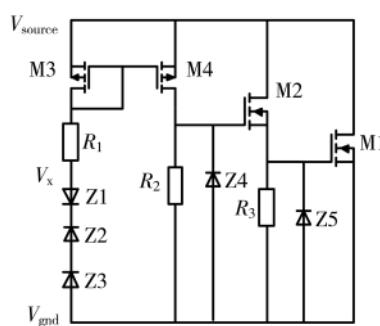

根据电路框图所设计的电路结构如图 3 所示。电路中二极管串是参考电压模块,由齐纳二极管组成,其参考电压由齐纳二极管的方向和个数决定。同时,齐纳二极管要求有较低的电流系数,这样即使当源电压超过参考电压时,参考电路在不同的热条件下也保持稳定。其余部分为反馈控制电路,M3 和 M4 两个 PMOS 构成一个电流镜,产生参考电流;M2 为驱动管,产生 M1 的开启电流;M1 为泄放管(宽度一般为几十毫米),用于释放浪涌电流。当浪涌电压大于二极管串击穿电压时,二极管串产生基准电压,即  $V_x$  电压值保持不变。同时,在 M3 一侧产生参考电流,经过电流镜的电流复制作用于 M4,此电流经过电阻  $R_2$  可以抬升  $R_2$  两端的电压,从而使驱动管 M2 的栅极大于其阈值电压,开启 M2。M2 开启后产生的驱动电流经过  $R_3$  抬升  $R_3$  两端的电压,从而使主泄放器件 M1 打开,M1 可以泄放大量的电流,使整个芯片钳位在一定的电压。由于 M1 的尺寸较大(宽度一般为几十毫米),因此需要 M2 产生足够的驱动电流开启 M1。驱动电流的大小为:

$$I_{M2} = C_{ox, M1} \frac{dV}{dt} \quad (1)$$

其中  $I_{M2}$  为 M2 产生的驱动电流, $C_{ox, M1}$  为 M1 的栅极电容。通常情况下,需要数十微安的电流才足以驱动泄放管。此外,为了提高 M1 的放电效率,可适当抬升 M1 的栅极电压。将 M1 的栅极瞬时电压抬升至超过其最大栅极电压(即  $V_{th, max}$ )有利于增强其放电能力。

随着源级电压  $V_{source}$  的增加,更多的电流被注入到缓冲晶体管 M2 中,这又进一步拉高了主钳位器件 M1 的栅极电压从而可以泄放更多的电流,以此调节其输出电压到钳位电压。同理,当源级电压  $V_{source}$  减小(假设源级电压仍大于钳位电压),更少的电流被注入到缓冲晶体管 M2 中,这继而减少了主钳位器件 M1 上栅极电压,从而使泄放电流减小将输出电压调节至钳位电压。通过反馈控制这种方式,使得输出电压能够精确地钳位到所期望的钳位电压,而不管主钳位晶体管泄放的电流如何。结果可以使浪涌保护电路的最终动态电阻几乎为零。

## 2 浪涌测试模型及电路仿真

### 2.1 浪涌测试模型

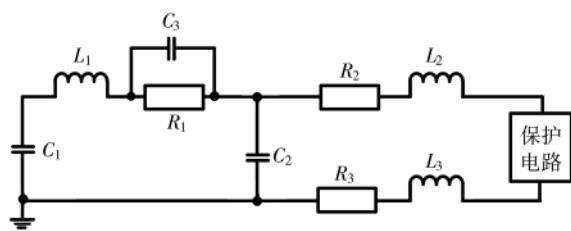

工业界常见的浪涌测试模型如图 4 所示,参考标准为 IEC 61000-4-5。根据 IEC 61000-4-5 调节电阻电容以及电感的值可以产生符合仿真要求的波形。

图 4 浪涌测试模型

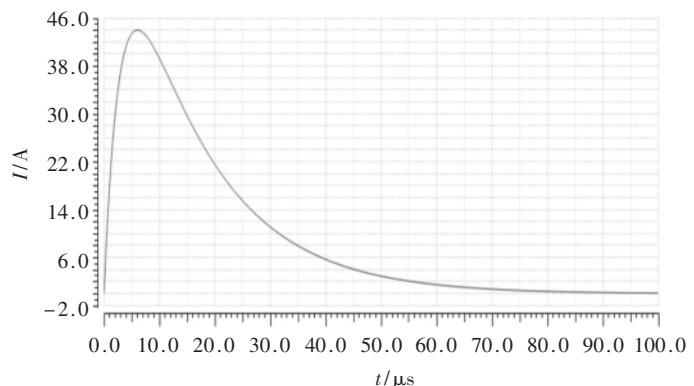

按照仿真要求搭建其测试模型,仿真得到其波形图,如图 5 所示。其上升时间为 5  $\mu s$ 。

图 3 浪涌保护芯片电路图

图 5 浪涌测试放电波形

## 2.2 仿真所需指标

表 1 为测试电路所需要到达的仿真指标。根据项目要求所需四种不同钳位电压的浪涌保护电路, 其钳位电压分别为 38 V、27 V、18 V、10 V。 $I_{pp(c)}$  为浪涌保护电路所能泄放电流的大小,  $I_{pp(r)}$  为其泄露电流的大小,  $V_{rw}$  为电路正常工作时的源端电压 VDD。

## 2.3 浪涌保护电路仿真结果

仿真的浪涌保护电路的各个器件参数如表 2 所示。钳位电压的等级改变主要依靠齐纳二极管串的个数与方向, 如在钳位电压到达 10 V 这个等级下, 需要将一个反向和两个正向的齐纳二极管串联作为其参考电压模块, 而当钳位电压为 18 V 时, 则要将两个正向和三个反向的齐纳二极管串联作为其参考电压模块。M1 为主电流泄放器件, 以此 M1 具有较大的尺寸, 其宽度通常有几十微米。

表 2 浪涌保护电路参数

| 钳位电压/V | 二极管串联  | M3/M4                               | M2                                     | M1                                        |

|--------|--------|-------------------------------------|----------------------------------------|-------------------------------------------|

| 38     | 五反向三正向 | $W=80 \mu\text{m}, L=1 \mu\text{m}$ | $W=800 \mu\text{m}, L=0.2 \mu\text{m}$ | $W=30 \text{ mm}, L=0.2 \mu\text{m}, M=4$ |

| 27     | 四反向    | $W=80 \mu\text{m}, L=1 \mu\text{m}$ | $W=800 \mu\text{m}, L=0.2 \mu\text{m}$ | $W=30 \text{ mm}, L=0.2 \mu\text{m}, M=4$ |

| 18     | 两反向三正向 | $W=80 \mu\text{m}, L=1 \mu\text{m}$ | $W=800 \mu\text{m}, L=0.2 \mu\text{m}$ | $W=40 \text{ mm}, L=0.2 \mu\text{m}, M=4$ |

| 10     | 一反向两正向 | $W=80 \mu\text{m}, L=1 \mu\text{m}$ | $W=800 \mu\text{m}, L=0.2 \mu\text{m}$ | $W=40 \text{ mm}, L=0.2 \mu\text{m}, M=4$ |

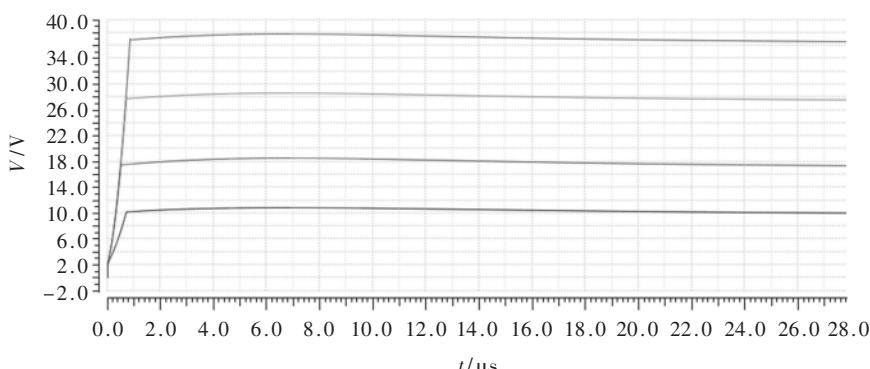

仿真结果如图 6~图 11 所示。图 6 为浪涌保护电路在受到浪涌冲击时的钳位电压情况, 从图中可知, 四个电路的钳位电压分别为 37.8 V、27.0 V、18.2 V、10.1 V, 并且其钳位电压基本上不随时间的变化而变化, 说明其钳位电压基本固定且动态电阻基本为零。

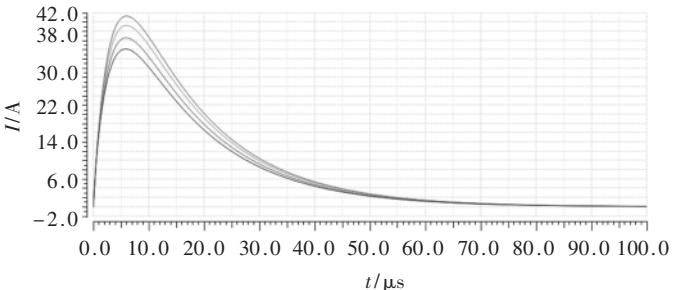

图 7 为浪涌保护电路泄放电流的波形, 四个电路的最大泄放电流分别为 34 A、36.8 A、39.6 A、41.4 A, 符合仿真所需指标。

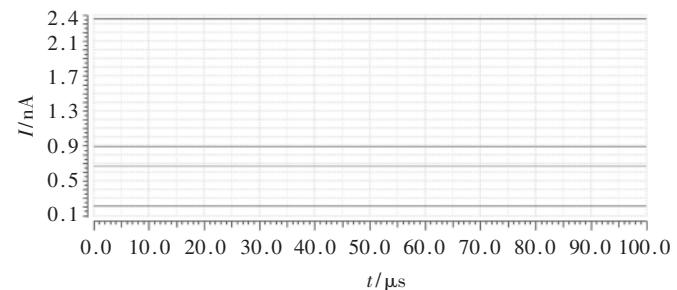

图 8 为浪涌保护电路在所保护芯片正常工作时的漏电流仿真情况, 四个电路的漏电流分别为 2.4 nA、0.9 nA、0.7 nA、0.2 nA。

图 6 电压随时间变化波形

图 7 泄放电流随时间变化波形

图 8 电路正常工作的漏电流

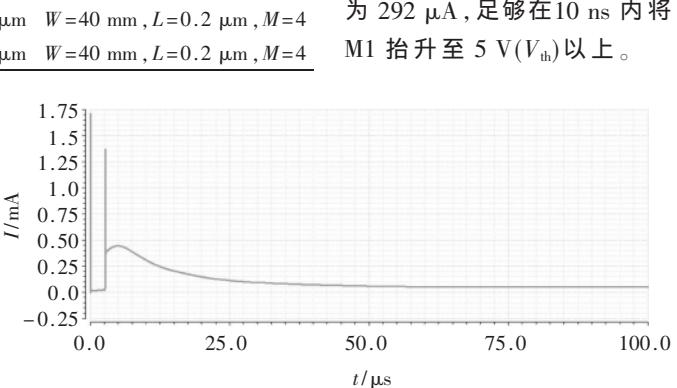

图 9 M1 驱动电流随时间变化波形

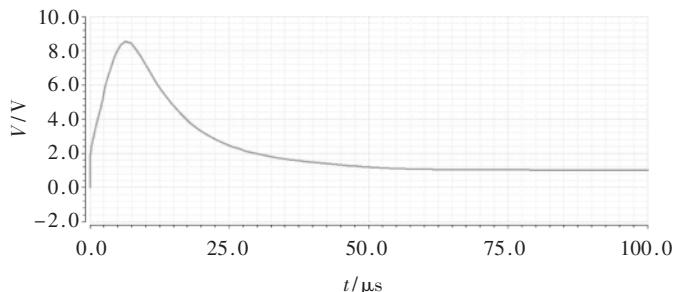

图 10 为 M1 栅极电压随时间变化波形。如图, M1 栅极瞬时最大电压为 8.5 V, 可有效地提高 M1 泄放电流的能力。

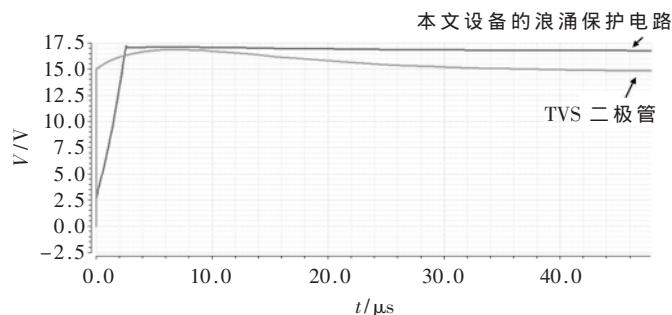

图 11 为设计的浪涌保护电路和传统 TVS 二极管的浪涌仿真对比。两者尺寸相当且防护等级相同 (即相近的箝位电压)。如图 11 所示, TVS 二极管开启后存在一个明显的过冲 (约 17 V), 之后将电压箝位在 15 V; 而设计的浪涌保护电路其箝位电压基本不变 (约为 17 V), 其动态电阻基本为零, 可以提供更精确的防护。

## 3 结论

本文研究并设计了一种浪涌保护电

图 10 M1 棚极电压随时间变化波形

图 11 设计的浪涌保护电路和 TVS 二极管浪涌仿真结果

路,其由参考电路和反馈控制电路两级组成。通过对其实现得出以下结论:

- (1) 保护电路的钳位电压可通过调节参考电路来改变。

- (2) 和传统的TVS二极管相比较,新型浪涌保护电路的钳位电压固定,且其具有接近于零的动态电阻,能够提供更加精确的浪涌保护。

- (3) 保护电路能够在较快时间内泄放大量的电流,使被保护电路能不被击穿。

- (4) 浪涌保护电路的漏电流很小,功耗较低,不影响被保护电路正常工作。

#### 参考文献

- [1] DUVVURY C.ESD qualification changes for 45 nm and beyond[C].IEEE International Electron Devices Meeting. IEEE , 2008.

- [2] WANG A Z,FENG H G,GONG K, et al.On-chip ESD protection design for integrated circuits: an overview for IC

- (上接第 73 页)

- 676-680.

- [7] 张瑞.基于断言的形式化验证与 UVM 的综合应用[D].西安:西安电子科技大学,2018.

- [8] HAVLICEK J,WOLFSTHAL Y.PSL and SVA :two standard assertion languages addressing complementary engineering needs[Z].2003.

- [9] 王鹏,刘万和,刘锐,等.基于 SystemVerilog 可重用测试平台的实现[J].电子技术应用,2015,41(2):61-64.

- [10] AEEC.ARINC664 aircraft data networks , part7 : avionics

- designers[J].Microelectronics Journal , 2001 , 32(9) : 733-747.

- [3] AMERASEKERA A ,DUVVURY C.ESD in silicon integrated circuits[M].England : Wiley , 2002.

- [4] CALE T S,MERCHANT T P,BORUCKI L J , et al.Topography simulation for the virtual wafer fab[J].Thin Solid Films , 2000 , 365(2) : 152-175.

- [5] AMERASEKERA A ,DUVVURY C.The impact of technology scaling on ESD robustness and protection circuit design[J]. IEEE Transactions on Components , Packaging , and Manufacturing Technology : Part A , 1995 , 18(2) : 314-320.

- [6] KING Y C,DAI S H,LIN C J.Leakage suppression of low-voltage transient voltage suppressor[J].IEEE Transactions on Electron Devices , 2008 , 55(1) : 206-210.

- [7] ROIG J,FLORES D,CORTES I, et al.Lateral punch-through TVS devices for on-chip protection in low-voltage applications[J].Microelectronics and Reliability , 2005 , 45(7) : 1181-1186.

- [8] POON S,MALONEY T.New considerations for MOSFET power clamps[J].Microelectronics and Reliability , 2003 , 43 (7) : 987-991.

- [9] SMITH J,BOSELLI G.A MOSFET power supply clamp with feed back enhanced triggering for ESD protection in advanced CMOS technologies[J].Proceedings of EOS/ESD Symposium , 2003 , 42(5) : 8 - 16.

- [10] 周成龙,郭艳辉,刘强,等.一种新型瞬态浪涌抑制技术研究[J].新技术新工艺,2018(4): 70-73.

- [11] 杨尊松,王立新,肖超,等.瞬态电压抑制二极管的概述和展望[J].电子设计工程,2016,24:108-112.

- [12] OBREJA V V N.Transient surge voltage suppressors and their performance in circuit over-voltage protection[C]. Semiconductor Conference , 2008 CAS 2008 International , 2008 : 321-324.

(收稿日期:2020-05-19)

#### 作者简介:

董大伟(1981-),男,硕士,高级工程师,主要研究方向:专业集成电路设计、总线设计与应用。

李江陵(1990-),男,本科,助理工程师,主要研究方向:专业集成电路设计、集成电路制造工艺。

full duplex switched Ethernet(AFDX) network[S].Airlines Electronic Engineering Committee , 2005.

(收稿日期:2019-12-09)

#### 作者简介:

阎芳(1982-),女,副研究员,研究生导师,主要研究方向:民机系统安全性设计与评估、机载电子软件适航技术。

李翔(1994-),通信作者,男,硕士研究生,主要研究方向:机载复杂电子硬件验证,E-mail:MH\_LIXIANG@163.com。

徐双平(1992-),男,硕士研究生,主要研究方向:机载复杂电子硬件验证。

## 版权声明

经作者授权，本论文版权和信息网络传播权归属于《电子技术应用》杂志，凡未经本刊书面同意任何机构、组织和个人不得擅自复印、汇编、翻译和进行信息网络传播。未经本刊书面同意，禁止一切互联网论文资源平台非法上传、收录本论文。

截至目前，本论文已经授权被中国期刊全文数据库（CNKI）、万方数据知识服务平台、中文科技期刊数据库（维普网）、DOAJ、美国《乌利希期刊指南》、JST 日本科技技术振兴机构数据库等数据库全文收录。

对于违反上述禁止行为并违法使用本论文的机构、组织和个人，本刊将采取一切必要法律行动来维护正当权益。

特此声明！

《电子技术应用》编辑部

中国电子信息产业集团有限公司第六研究所