# 基于 SOPC 的脉冲信号参数测量系统设计 \*

李海生, 张凡

(长治学院 电子信息与物理系, 山西 长治 046011)

**摘要:** 为提高测量系统的精度、集成度和设计灵活性, 设计了基于可编程片上系统(SOPC)的脉冲信号参数测量系统。系统通过采用等精度测频法实现对频率的测量, 利用等效脉冲计数法完成对占空比和上升时间的精确测量, 所设计的测量系统在硬件和软件上都可进行编程。经过测试和验证, 设计的系统可实现对脉冲信号频率、占空比、幅值和上升时间的测量, 测量结果具有较高的精度, 其中时间测量精度可达 1 ns。

**关键词:** 脉冲信号; 参数测量; 频率; 可编程片上系统; 上升时间

中图分类号: TN98; TM935

文献标识码: A

DOI: 10.16157/j.issn.0258-7998.191300

中文引用格式: 李海生, 张凡. 基于 SOPC 的脉冲信号参数测量系统设计[J]. 电子技术应用, 2020, 46(7): 84–87.

英文引用格式: Li Haisheng, Zhang Fan. Design of pulse signal parameter measurement system based on SOPC[J]. Application of Electronic Technique, 2020, 46(7): 84–87.

## Design of pulse signal parameter measurement system based on SOPC

Li Haisheng, Zhang Fan

(Electronic Information and Physics Department, Changzhi University, Changzhi 046011, China)

**Abstract:** In order to improve the accuracy, integration and flexibility of the system, a pulse signal parameter measurement system based on system-on-a-programmable-chip(SOPC) is designed. The system realizes the frequency measurement by using the equal precision frequency measurement method, and the duty cycle and rise time measurement are realized by using the equivalent pulse counting method. The designed measurement system is programmable in hardware and software. After testing and verification, the system can realize the measurement of pulse signal frequency, duty cycle, amplitude and rise time. The measurement results have high accuracy, and the time measurement accuracy can reach 1 ns.

**Key words:** pulse signal; parameter measurement; frequency; system-on-a-programmable-chip(SOPC); raise time

## 0 引言

脉冲信号广泛应用于通信、测控、雷达和导航等领域, 在很多场合下需要对脉冲信号进行参数(频率、周期、占空比、幅值和上升时间等)的测量<sup>[1-2]</sup>。如在扭矩的测量中, 需要对磁电式传感器的多路脉冲信号进行相位差的测量<sup>[3]</sup>; 在雷达领域的敌我识别询问信号检测中, 需要对敌我识别信号的时域参数包括脉冲宽度、幅度和到达时刻进行测量<sup>[4]</sup>。随着相关技术的发展, 脉冲信号的频率越来越高。从早期使用单片机作为控制器进行测量<sup>[5]</sup>, 再到后边使用 DSP 进行测量<sup>[6]</sup>, 一直在不断更新核心处理器。可编程逻辑器件的发展, 为高速脉冲信号的测量提供了新的设计方法。现有的测量系统多数是基于 FPGA 和单片机相结合<sup>[7]</sup>, 这样可以很好地发挥各自的优点, 但也存在着集成度不高、性能不稳定等缺点。本文提出了基于可编程片上系统的设计方法, 将处理器集成于 FPGA 内部, 所设计的测量系统具有很高的灵活性和

集成度。

### 1 系统设计原理

#### 1.1 等精度测频法原理

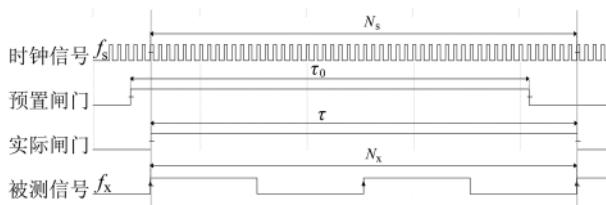

频率测量常用的方法是等精度测频法, 等精度测频法的测量精度不受被测信号的影响, 在测量频段内精度保持不变。其原理是通过在一定的闸门时间  $\tau_0$  内, 对被测量信号  $f_x$  和标准时钟信号  $f_s$  同时进行计数, 得到计数结果分别为  $N_x$  和  $N_s$ <sup>[8]</sup>。那么被测信号频率即为:

$$f_x = f_s N_x / N_s \quad (1)$$

等精度测频原理如图 1 所示, 其中预置闸门时间  $\tau_0$  是不确定的值, 随着被测信号变化, 实际的闸门时间  $\tau$  要始终保持为被测信号周期的整数倍, 即满足:

$$\tau = N_x / f_x \quad (2)$$

等精度测频法可以有效避免对被测信号产生的  $\pm 1$  计数误差, 在不考虑标准时钟信号  $f_s$  本身误差的前提下, 测量误差主要是对标准时钟信号计数产生  $\pm 1$  的计数误差, 等精度测量的相对误差为:

\* 基金项目: 国家自然科学基金(11847036); 长治学院院级科研项目(zc201901)

# 测控技术与仪器仪表 Measurement Control Technology and Instruments

图 1 等精度测频时序图

$$\varepsilon = \frac{\Delta N_s}{N_s} = \pm \frac{1}{N_s} = \pm \frac{1}{\tau f_s} \quad (3)$$

由式(3)可知,等精度测频的相对误差仅与闸门时间 $\tau$ 和标准时钟信号 $f_s$ 有关,与被测信号频率无关。

## 1.2 等效脉冲计数法

占空比测量主要是对脉冲信号的高低电平持续时间进行计算统计,通过对测量信号一个周期的计数 $N$ 和高电平时间的计数 $N_H$ ,就可以计算得到所测信号的占空比:

$$D_s = N_H/N \quad (4)$$

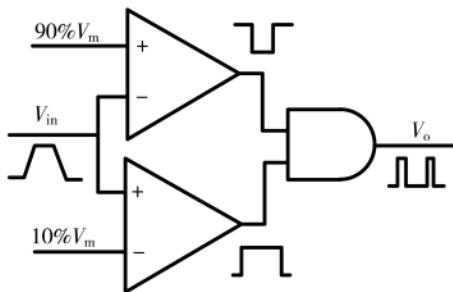

脉冲信号的上升时间是指信号的幅值从 10% 增加到 90% 所需要的时间,通过幅值测量采集到脉冲信号幅度后,通过 D/A 模块分别输出幅度的 10% 和 90% 与被测信号进行比较,就可以得到上升时间。

对于占空比和上升时间的测量一般是通过计数器完成,传统方法是用被测信号来控制计数器工作,完成对标准时钟信号的计数,其精度受限于器件的最高工作效率。

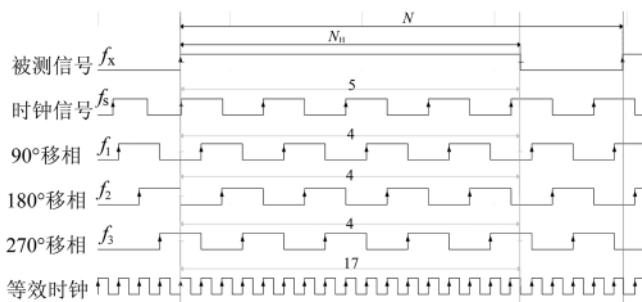

通过采用等效脉冲计数法可以有效提高测量精度,使用锁相环的倍频和数字移相技术,产生多路不同相位的同频时钟信号进行多路计数,其等效时钟频率相对于单路时钟可以提高多倍,从而实现更高精度的测量<sup>[9-11]</sup>。基于 4 路移相时钟的等效脉冲计数时序如图 2 所示。

图 2 基于 4 路移相时钟的等效脉冲计数时序图

在图 2 中,通过锁相环产生的 4 路倍频时钟信号 $f_s$ 、 $f_1$ 、 $f_2$ 、 $f_3$  相位分别为 0°、90°、180°、270°。通过 4 路同频时钟的同时计数,得到的计数值分辨力由原来的 1 提高到 0.25,与一路时钟相比,精度提高了 4 倍。如果继续提高同频时钟的数量,精度可以继续提高。

## 1.3 SOPC 介绍

可编程片上系统也属于嵌入式系统,是采用可编程

逻辑技术将系统的所用功能都放在一块芯片内完成,相比其他嵌入式系统具有较高的集成度和灵活性,可以对硬件和软件进行相应的编程来实现某些特定功能和场合的应用。在可编程片上系统中至少有一个嵌入式处理内核作为核心控制器,再搭配丰富 IP Core 资源来完成某些特定功能,有的甚至包含模拟电路模块,并且有足够的可编程逻辑资源可以完成数字电路的搭建,在软硬件方面都可编程,具有单芯片、微封装、低功耗、可扩充、可裁剪和可升级等优点。

所设计的脉冲信号参数测量系统是基于 Altera 公司的 Cyclone IV 系列的 FPGA 芯片完成的,通过使用集成开发环境 Quartus II 来完成数字逻辑的设计,借助于 Qsys 开发工具来进行 Nios II 的嵌入式系统硬件的设计,再利用 Nios II EDS 完成对软核处理器内部软件程序的开发,最终完成可编程片上系统的开发。

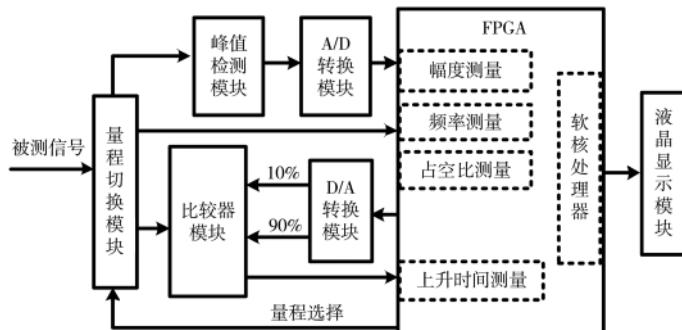

## 2 系统硬件设计

系统设计采用 FPGA 芯片 EP4CE15E22C8N 作为 SOPC 的开发平台,通过峰值检测模块对信号幅度的测量来控制量程切换模块完成输入信号放大、直通、衰减挡位的切换<sup>[12]</sup>。得到合适的脉冲信号后,一路给 FPGA 完成频率和占空比测量,另一路给比较器模块完成对上升时间的测量,最后经过数据处理将脉冲信号的参数显示到液晶屏上。系统设计框图如图 3 所示。

图 3 脉冲信号参数测量系统框图

### 2.1 量程切换模块

由于 FPGA 的 I/O 口的供电电压是 3.3 V,不能对被测信号进行直接测量,故需要量程切换模块先从高往低切换,直到 A/D 转换模块采集到的电压值接近 3.3 V。经过预处理的信号分两路,一路给 FPGA 完成频率和占空比测量,另一路是给比较器模块来处理得到上升时间<sup>[13]</sup>。

### 2.2 峰值检测模块

由于测量信号是脉冲信号,需要先进行峰值检波后,再通过 A/D 模块进行幅值的测量。被测信号幅度提前未知,需将被测信号进行衰减,再根据测量的幅度值逐次调节量程直至信号幅值合适。峰值检测模块主要是来完成脉冲信号幅值的测量,传统的峰值检测电路主要由二极管和电容组成,存在着线性度差、通频带窄等缺点,

# 测控技术与仪器仪表

## Measurement Control Technology and Instruments

测量精度有限。本设计选用 AD 公司的专用峰值保持器 PKD01,PKD01 具有峰值检测、峰值保持和复位 3 种工作模式,采用跨导运算放大器,具有响应速度快、线性好、峰值保持精度高等优点<sup>[14]</sup>,可以很好地满足设计要求。

### 2.3 比较器模块

比较器模块是将被测脉冲信号的上升时间信息转化为方波信号,通过将两路比较器 TLV3501 的比较阈值设置为被测信号幅值的 10% 和 90%,产生的两路比较结果输入到 FPGA 进行处理,从中提取得到脉冲信号的上升时间<sup>[15]</sup>。测量示意图如图 4 所示。

图 4 上升时间测量示意图

### 2.4 A/D 和 D/A 转换模块

A/D 转换模块主要完成信号幅值的测量,选用 TI 公司的 8 路 12 位低功耗 AD 转换芯片 ADC128S102。ADC128S102 是一款具有采样保持的逐次逼近型 ADC,转换速率是 500 kS/s~1 MS/s。

D/A 转换模块用来产生 10% 和 90% 的被测信号幅值给比较器模块,用来测量脉冲信号上升时间,选用 TI 公司的 TSSOP 封装的兼容 I<sup>2</sup>C 接口的 8 路 12 位 D/A 转换芯片 DAC7678 完成。

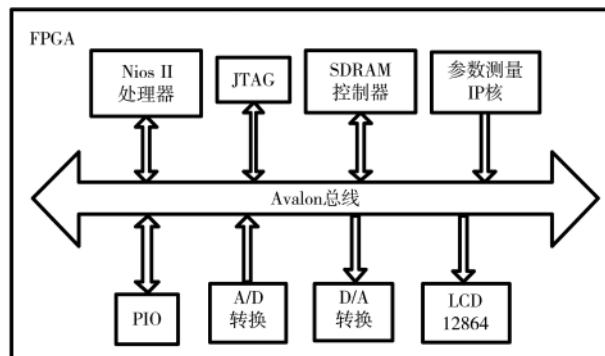

## 3 SOPC 的设计

### 3.1 Nios II 系统设计

脉冲信号的参数主要包括幅值、频率、占空比和上升时间,通过在 FPGA 内部嵌入 Nios II 软核处理器,并对相应的参数测量模块进行驱动程序的编写和设计,然后将模块封装定义成外围接口 IP 核挂载到 Avalon 总线上,这样 Nios II 处理器就可以通过总线控制读取测量到的参数,进行数据处理和显示。脉冲参数测量系统的 SOPC 设计结构框图如图 5 所示。

图 5 基于 FPGA 的 SOPC 内部设计结构图

### 3.2 参数测量模块

参数测量模块主要是对频率、占空比和上升时间这 3 个参数进行测量,使用 Verilog HDL 完成逻辑设计后,按照 Avalon 总线要求封装成 IP 核。频率采用等精度测频法,而上升时间和占空比的测量采用等效脉冲法进行测量。测量得到的参数信息放在 5 个 32 位的寄存器中,频率测量是 fbase\_cnt 和 fx\_cnt 两个寄存器,占空比是 dutyH\_cnt 和 dutyL\_cnt 两个寄存器,上升时间是 t\_cnt 寄存器,在 SOPC 中 Nios II 处理器通过 Avalon 总线读取寄存器数据。

## 4 系统设计验证

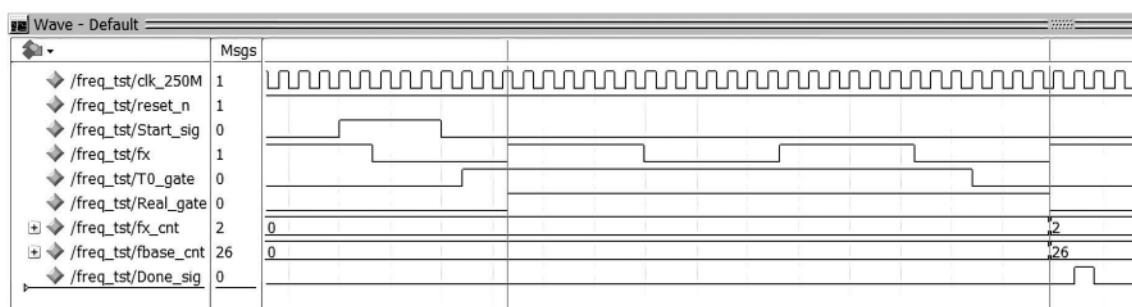

### 4.1 等精度测频法验证

FPGA 外接 50 MHz 晶振,时钟信号 clk\_250M 是经过 PLL 倍频产生的 250 MHz 时钟,闸门信号 T0\_gate 是控制被测信号计数器 fx\_cnt 和标准时钟信号计数器 fbase\_cnt 的工作来完成等精度频率测量的计数。当检测到开始测量信号 Start\_sig 的上升沿后,实际闸门信号 Real\_gate 就开始对被测信号 f<sub>x</sub> 进行检测,来自适应调整预置闸门信号 T0\_gate,使得实际闸门信号为被测信号周期的整数倍。完成计数后,产生测量完成信号 Done\_sig,并输出频率测量计数值。在 ModelSim 中的仿真时序图如图 6 所示。

预置闸门时间设置为 100 ns,被测信号周期是 53.2 ns,标准时钟信号是 4 ns。从图 6 中可知,被测信号计数器 fx\_cnt 是 2,即实际闸门时间调整为被测信号周期的 2 倍;标准时钟信号计数器 fbase\_cnt 是 26。通过式(1)可得测量到的周期是 52 ns,相对误差的计数值为 2.26%。如

图 6 等精度测频的时序仿真图

# 测控技术与仪器仪表 Measurement Control Technology and Instruments

果将闸门时间增大,可以进一步减小测量误差。

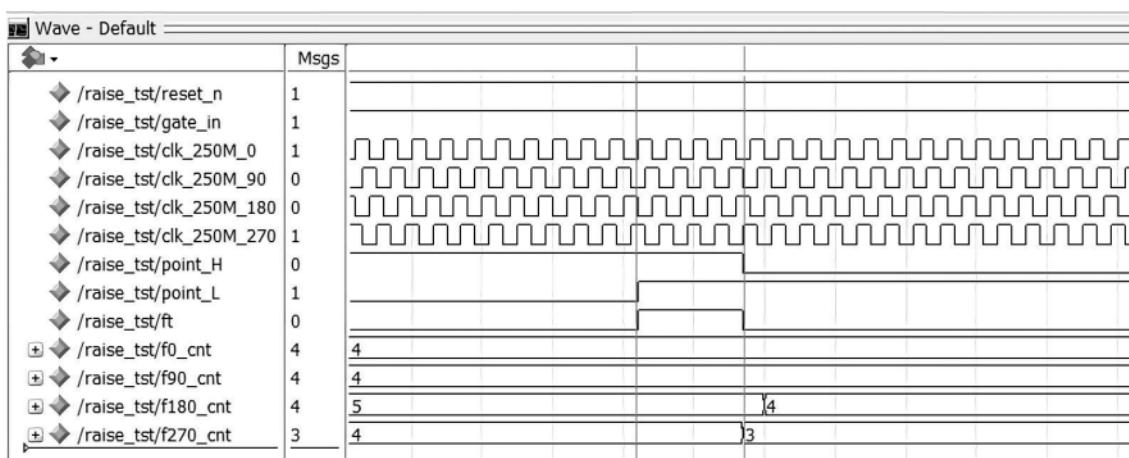

## 4.2 上升时间测量验证

通过时钟倍频技术和移相技术,在FPGA内部产生4路250 MHz的同频时钟信号,相位差间隔为90°,point\_H和point\_L是比较器模块的输出,两个逻辑与产生ft信号,ft的脉冲宽度即为被测信号的上升时间。4个不同相位的时钟信号计数器f0\_cnt、f90\_cnt、f180\_cnt、f270\_cnt分别对ft的脉冲宽度进行测量计数。在ModelSim的仿真时序图如图7所示。

模拟产生的被测信号上升时间是15 ns,PLL输出的4路时钟信号周期都为4 ns。从图7的仿真时序图中可知,4路时钟计数器对ft的脉宽测量计数值分别为4、4、4、3,通过测量值计算可知上升时间是15 ns,精度达到了1 ns。相比于单路时钟的测量,测量的精度提高了4倍。

## 5 结论

本文设计的脉冲参数测量系统选用FPGA作为核心控制器,通过在FPGA内部嵌入Nios II软核处理器,不需要使用额外的单片机,极大简化了系统的设计。通过设计频率、占空比、幅值和上升时间参数测量模块,封装成IP核,Nios II通过Avalon总线读取测量数据,并通过计算将参数信息显示到液晶屏上。系统分模块设计,结构简单,可在硬件和软件上进行功能更改扩展,具有很高的集成度和灵活性,在雷达、通信和检测领域具有很好的应用前景。

## 参考文献

- [1] 林浩,韩庆敏,宋栋,等.基于实时工业以太网的脉冲发生器[J].电子技术应用,2018,44(10):64–67,72.

- [2] 姚旺,金红新,赵鹏飞,等.基于多DSP的PD脉冲压缩雷达信号处理机的设计[J].电子技术应用,2017,43(7):51–54.

- [3] 杜冬,尹学峰,吉小军.基于FPGA的脉冲信号发生/测试仪一体化设计[J].电子测量技术,2015,38(1):64–68,94.

- [4] 高新平.敌我识别S模式询问信号实时检测技术[J].无线电工程,2016,46(6):27–29.

- [5] 陈蓉,何英萍,陈红仙.基于单片机的脉冲信号参数测量系统[J].电子设计工程,2018,26(14):153–157.

- [6] 曾菊容.脉冲信号参数测量仪的DSP设计[J].宜宾学院学报,2018,18(6):28–31.

- [7] 高英杰,陈婕,刘飞,等.基于FPGA和单片机的实时脉冲信号参数测量仪[J].金陵科技学院学报,2018,34(1):6–9.

- [8] 张国勤.基于单片机与FPGA的等精度频率计设计[J].四川兵工学报,2015,36(12):85–88.

- [9] 叶超,冯莉,欧阳艳晶.基于FPGA的精密时间间隔测量仪设计[J].信息与电子工程,2009,7(2):159–163.

- [10] 郑卉卉,程少云.基于数字移相的高精度到达时间测量系统[J].计算机测量与控制,2007(4):429–431.

- [11] 仵晓辉,师廷伟,金长江.基于移相技术的脉冲宽度精确测量方法及FPGA实现[J].周口师范学院学报,2012,29(2):108–109.

- [12] 张秀芝.基于FPGA的脉冲信号参数测量系统[D].哈尔滨:哈尔滨理工大学,2018.

- [13] 李德明,胡君辉.基于FPGA的脉冲信号参数测量系统设计[J].实验技术与管理,2019,36(5):101–106.

- [14] 马桥斌,李利品,孙亮亮,等.基于TMS320F2812的多道脉冲幅度分析器设计[J].电子测试,2012(12):11–14,19.

- [15] 章腾辉,姚成军,吴佳佳,等.脉冲信号参数测试仪的设计[J].工业控制计算机,2017,30(5):157–159.

(收稿日期:2019-11-29)

## 作者简介:

李海生(1992-),男,硕士研究生,助教,主要研究方向:嵌入式系统应用。

张凡(1987-),男,博士,副教授,主要研究方向:核物理。

图7 上升时间测量的时序仿真图

## 版权声明

经作者授权，本论文版权和信息网络传播权归属于《电子技术应用》杂志，凡未经本刊书面同意任何机构、组织和个人不得擅自复印、汇编、翻译和进行信息网络传播。未经本刊书面同意，禁止一切互联网论文资源平台非法上传、收录本论文。

截至目前，本论文已经授权被中国期刊全文数据库（CNKI）、万方数据知识服务平台、中文科技期刊数据库（维普网）、DOAJ、美国《乌利希期刊指南》、JST 日本科技技术振兴机构数据库等数据库全文收录。

对于违反上述禁止行为并违法使用本论文的机构、组织和个人，本刊将采取一切必要法律行动来维护正当权益。

特此声明！

《电子技术应用》编辑部

中国电子信息产业集团有限公司第六研究所