# 基于 LC 巴伦的伪差分功率放大器设计 \*

彭 林 , 李嘉进 , 梁钊铭 , 章国豪

(广东工业大学 信息工程学院 , 广东 广州 510006)

**摘要:** 为了在局部热点区域实现系统容量的成倍提升, 需要能支持高频、大带宽工作的无线网络基础设施进行超密集组网, 采用 GaAs HBT 工艺设计出适用于 5G 微基站的 4.8~5.0 GHz 三级高增益、大输出功率放大器。利用伪差分结构来抑制接地寄生电感的影响, 通过片外低损耗 LC 巴伦完成单端与差分对之间的转换, 结合有源自适应偏置网络与 RC 负反馈电路, 并应用宽带匹配与预失真补偿的方法, 基于 ADS 仿真验证了在中心频点 4.9 GHz 处可实现 35.8 dB 的功率增益与 33.5% 的峰值功率附加效率, 且工作频带内能输出不低于 35 dBm 的饱和功率, 可满足典型应用场景对网络信号无缝覆盖的要求。

**关键词:** 巴伦 ; 伪差分 ; 射频功率放大器 ; 自适应偏置 ; 5G 微基站

中图分类号 : TN722

文献标识码 : A

DOI : 10.16157/j.issn.0258-7998.200302

中文引用格式 : 彭林 , 李嘉进 , 梁钊铭 , 等. 基于 LC 巴伦的伪差分功率放大器设计 [J]. 电子技术应用 , 2020 , 46(8): 9-12.

英文引用格式 : Peng Lin , Li Jiajin , Liang Zhaoming , et al. Design of pseudo-differential power amplifier based on LC balun [J]. Application of Electronic Technique , 2020 , 46(8): 9-12.

## Design of pseudo-differential power amplifier based on LC balun

Peng Lin , Li Jiajin , Liang Zhaoming , Zhang Guohao

(School of Information Engineering , Guangdong University of Technology , Guangzhou 510006 , China)

**Abstract :** In order to greatly improve the system capacity in local hotspots, the wireless communication infrastructure that can support high-frequency and wideband operation is required for ultra-dense networking. A 4.8~5.0 GHz three-stage high-gain and large-output power amplifier is designed using GaAs heterojunction bipolar transistor(HBT) process to be targeted for 5G microcells. The pseudo-differential structure is adopted to suppress the influence of ground parasitic inductance, while the conversion between single-ended and differential pairs is completed by off-chip low-loss LC balun. In conjunction with active adaptive bias network and RC negative feedback circuit, meanwhile applying the methods of wideband matching and predistortion compensation, ADS(Advanced Design System) simulations verified that the proposed power amplifier can achieve 35.8 dB power gain with 33.5% peak power-added efficiency at a center frequency of 4.9 GHz, and deliver not less than 35 dBm saturated output power in the operating band, which can meet the requirements of seamless coverage of network signals in typical application scenarios.

**Key words :** balun ; pseudo-differential; radio frequency power amplifier(RFPA) ; adaptive bias ; 5G microcell

## 0 引言

作为新一代移动通信技术, 兼具高数据率、低时延与高可靠性的商用 5G 网络将逐步渗透到社会各个领域, 以用户为中心构建全方位的信息生态系统, 可满足未来海量设备接入通信的需求。毫米波技术和 Sub-6 GHz 同属于 3GPP(3rd Generation Partnership Project) 规定的 5G 标准, 但由于毫米波的波长较短, 所致其信号传输衰耗大, 易受环境的影响; Sub-6 GHz 则是 LTE(Long Term Evolution) 频段向上延续而来的带宽资源, 支持广域覆盖、高移动性服务等业务场景, 一定程度上能够利用现有的基站设施从而简化 5G 部署<sup>[1]</sup>。按照规划, 国内蜂窝网络

运营商将在 3.3~3.6 GHz 以及 4.8~5.0 GHz 上进行 5G 的初期组网。

功率放大器作为无线通信系统中射频前端发射通路的核心组件, 是将已调制的频带信号放大到所需要的功率值, 并馈送到天线上辐射出去。在微基站应用中, 由于硅基 CMOS 工艺存在耐压能力不足、衬底损耗和 Knee 电压较大等物理缺陷而被排除; 宽禁带 GaN 器件虽然能在更高的工作电压下提供更优的功率密度, 但目前受限于生产成本、良率等因素暂不是最佳选择, 所以未来一段时间内仍然以 GaAs 功放为主, 因其具备经市场验证的可靠性、较高性价比和完整产业链的优势。为了应对城区高用户密度、大数据流量和众多接入点, 同时要解决更高工作频率下所带来愈发严重的寄生效应, 密集架

\* 基金项目 : 国家自然科学基金(61974035); 广东省省级科技计划项目(计算与通信芯片)(2017B090908007)

设的微基站群如何在保持一定带宽的前提下,依然实现高增益、大功率输出的指标成为一项难题。本文基于2-μm InGaP/GaAs HBT工艺设计了一款4.9 GHz三级伪差分功率放大器,能有效减轻因芯片内部、封装与测试板接地时附带的寄生电感对系统性能产生的不利影响,并通过片外LC巴伦实现单端与差分对之间的转换,同时给出了整体电路的设计方法、理论分析和仿真结果。

## 1 伪差分功率放大器结构

对于应用最广泛的经典单端功放结构,芯片上有源HBT器件的射极需要通过背孔连接到物理地;在高频情况下,到地通孔的寄生电感会恶化功放的性能指标,甚至会带来振荡的风险。更严峻的问题是,倘若工艺不支持TWV(Through-Wafer Via)技术,那么功放的接地就必须借助键合线连接到PCB板,而此时由于键合线的长度、高度、角度以及与其他键合线的耦合程度均不可控,这就导致设计中无法通过建模的方式来准确估计这些不确定性,封装也将进一步加剧寄生效应的负面影响,从而给产品的初始研发带来了挑战<sup>[2-3]</sup>。

差分结构则可以利用双HBT晶体管共射互连结点上所产生的射频虚拟地来消除上述单端方案存在的弊病,因此它能实现更优的高频增益与一致性,降低衬底耦合作用对其他电路的干扰,增强了集成模组稳定性;同时,在相同的输出功率水平下,差分功放的负载线阻抗是传统单端结构的4倍,阻抗变换比的大幅减小有利于避免匹配网络可能引入的较大插入损耗与窄小带宽。由于功率放大器处理的信号能量很强,各种干扰对其影响很小,设计中通常不考虑共模噪声抑制能力,但全差分结构中尾电阻的负反馈在一定程度上会降低晶体管的 $V_{BE}$ 并因此削减了输出功率,而且其导致的热损耗在高功率场景对效率的影响也不应忽视。另外,当射频输入信号强度逐渐增加时,尾电流源的存在会限制输出电流的最大值进而引起增益压缩现象,且尾电流源晶体管上需要维持一定的压降以确保工作于饱和区,所以其还会降低输出电压的摆幅。综上分析,为了实现Sub-6 GHz n79频段下高增益、大输出的目标,可以将差分对管的射极都直接接地,形成伪差分结构,让晶体管的输出电流能正相关地跟随输入信号强度的变化,同时也能避免尾电阻的直流分压影响。

## 2 电路设计

### 2.1 LC 巴伦

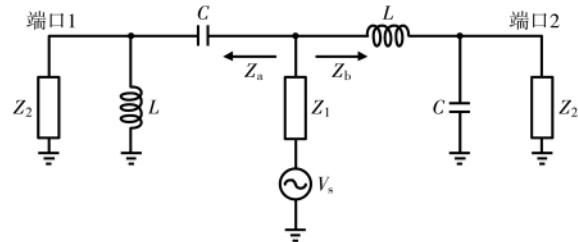

差分对需要巴伦模块作为射频信号输入时的功分器以及功率输出时的合成器,两者本质上为互易关系。理想情形下,巴伦中两个差分端口的阻抗值必须保持相等,所传输的对称等幅信号间存在180°的相位差<sup>[4-5]</sup>。相比变压器、传输线等其他类型的射频巴伦而言,LC巴伦所具有的低成本与简单易实现性,使它获得了更加广泛的应用,图1为其等效电路形式。

图1 LC 巴伦等效电路

假定单端口的阻抗为 $Z_1$ ,两个平衡端口的阻抗为 $Z_2$ ,从射频信号输入的单端口往左、右两边看到的阻抗分别为:

$$Z_a = Z_C + Z_L // Z_2 = \frac{(1 - \omega^2 LC)Z_2 + j\omega L}{-\omega^2 LC + j\omega CZ_2} \quad (1)$$

$$Z_b = Z_L + Z_C // Z_2 = \frac{(1 - \omega^2 LC)Z_2 + j\omega L}{1 + j\omega CZ_2} \quad (2)$$

并且由 $Z_a$ 和 $Z_b$ 并联后得到的合成阻抗值应等于 $Z_1$ 的共轭,即:

$$Z_1^* = Z_a // Z_b = \frac{Z_a Z_b}{Z_a + Z_b} = \frac{(1 - \omega^2 LC)Z_2 + j\omega L}{(1 - \omega^2 LC) + j2\omega CZ_2} \quad (3)$$

当巴伦谐振, $\omega^2 LC = 1$ 时,能量可以很好地在单端口与差分端口之间均分传输,据此将 $Z_1^*$ 简化:

$$Z_1^* = \frac{L}{2CZ_2} \quad (4)$$

并进一步推导得出如下两个关系式:

$$\omega L = \sqrt{2Z_2 Z_1^*} \quad (5)$$

$$\omega C = \frac{1}{\sqrt{2Z_2 Z_1^*}} \quad (6)$$

其中, $Z_2$ 和 $Z_1^*$ 的乘积可以表示成:

$$Z_2 Z_1^* = (R_2 + jX_2)(R_1 - jX_1) \\ = (R_2 R_1 + X_2 X_1) + j(X_2 R_1 - R_2 X_1) \quad (7)$$

可知要保证电感 $L$ 和电容 $C$ 的设计参数为可实现的实数值,搭建巴伦电路时还需满足:

$$\frac{R_1}{R_2} = \frac{X_1}{X_2} \quad (8)$$

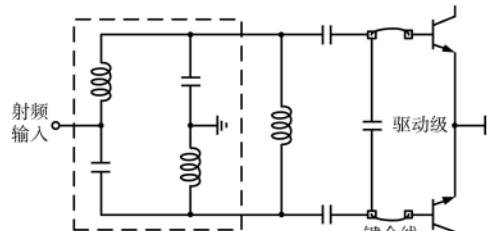

为了提高元件 $Q$ 值并方便后期进行实物可调性测试,本设计将输入、输出匹配网络均置于片外基板实现,如图2所示。输出级匹配的好坏将直接影响功放能否实现预期的性能,是整体电路最关键的部分,在图2(b)中,为避免增加不必要的匹配元件且达成单端与平衡端阻抗须互成比例的要求,并考虑到 $L_2$ 与 $C_2$ 在分别起有限射频扼流与隔直作用的同时,实际上还一并构成L形匹配,故本文在设计中结合非理想因素,利用其等效的阻抗变换特性确保将负载50 Ω小幅变换至另一纯电阻性的中间过渡值。另外,由于差分两路匹配网络的结构和版图均完全对称,射频信号链路间的相位差为180°,上下两路并联元件共地可直接相连,交点呈现交流虚拟地且直流偏置不存在,由此即可把物理接地给省略掉,合

(a) 输入 LC 巴伦匹配电路

(b) 输出 LC 巴伦匹配电路

图 2 LC 巴伦匹配电路

并后等效电容的容值等于单路并联匹配电容值的一半，所以就能通过键合线配合单个表贴的并联电容  $C_3$  将功率管的最优输出阻抗向上变换至巴伦平衡端，同时也能借此把 LC 巴伦的阻抗变换比控制在一个较低的范围来延展带宽。这样既节省了元件的使用，也减少了匹配损耗与偏差，提高了级联功放的输出性能。

## 2.2 自适应偏置电路

当晶体管工作于大信号时，由于 HBT 基-射结二极管的钳位作用，射频交流信号与偏置电流的叠加波形中进入负半轴的部分，对应至集电极电流会呈现出底部失真，即被限幅截断，不能放大；结合正弦函数的傅里叶变换可知，整流后的平均直流量将随着输入功率的增大而增加，且综合晶体管的自热效应，发射结压降降低了  $\Delta V_{BE}$ ，原静态工作点因此发生了偏离，将导致增益压缩与相位失真问题。

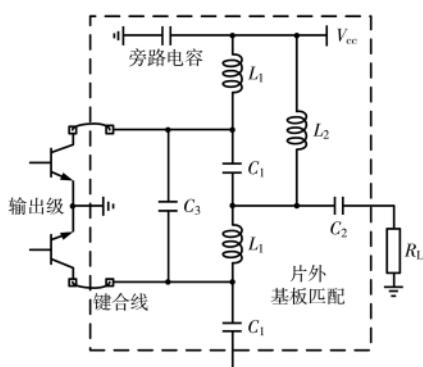

为了以较少的版图面积开销来补偿大信号状态下跨导的减小进而改善线性度，同时提高稳定性，本文采用了如图 3 所示的自适应偏置电流源电路<sup>[6]</sup>。

其中， $Q_0$  的偏置电流  $I_b$  由  $Q_2$  和  $Q_3$  组成的电流镜提供，通过调节限流电阻  $R_1$  即可获得所需参考值；电阻  $R_{bias}$ 、 $Q_3$  的基-射结二极管与到地电容  $C_L$  一并构成了线性化电路，在工作频率下，其整体阻抗减小，相当于引入一条射频通路，并且  $R_1$  与将基极和集电极接在一起作二极管用的两个串联 HBT 相并联，其交流阻抗较  $C_L$  大很多，因此泄漏进偏置电路的射频信号主要经线性化电路短路到地，从而保持了  $Q_3$  的基极电位  $V_{B3}$  相对恒定。输入信号逐渐增大会使得功率管  $Q_0$  感应出更多的直流量，

图 3 自适应偏置电路

其基极电位  $V_{B0}$  存在以下关系式：

$$V_{B0} = V_{B3} - V_{BE3} - I_b R_{bias} \quad (9)$$

得益于  $C_L$  的引入，加之  $Q_3$  与  $Q_0$  管的器件特性一致，小部分流进偏置网络的射频信号同样能让  $Q_3$  管感应出相应的直流量，表现为阻抗减小；又因  $V_{B3}$  被钳位至固定电平，故  $V_{BE3}$  的下降补偿了  $V_{B0}$  的减小，同时将基极电流  $I_b$  拔高，这样便使  $Q_0$  的线性驱动能力自适应地得到了增强。另一方面，由于主功放的总发射极面积远大于偏置管，这意味着偏置网络的阻抗相比而言会很大，也即泄漏的信号能量实质上微乎其微，可忽略其对放大链路增益的损耗。

考虑到多指晶体管功率耗散所引发的热耦合与自热效应，发射区中的电子在受到热激发后，会产生漂移，漂移的电子总数随温度升高而逐渐增多，若在恒定的基-射结电压驱动下，则  $Q_0$  和  $Q_3$  的基极电流会不同程度地增大一些，因而可将晶体管的 PN 结等效视作具有负温度系数的可变电阻。此时其正向导通电压减小，所以靠近功率管芯放置的两堆叠二极管，它们两端的压降就会随温度升高而些许下降，由此拉低  $Q_3$  的基极电位。类似，镇流电阻  $R_{bias}$  也能通过负反馈，有效抑制住直流分量随温度变化而产生的波动，即  $Q_1$ 、 $Q_2$  与  $R_{bias}$  协同起到温度补偿的作用，可阻止形成热失控(Thermal runaway)，避免出现电流增益坍塌。最后，为了抑制潜在不稳定，本设计在驱动级晶体管的输出端与其输入端之间引入了 RC 串联反馈电路，联合  $R_{bias}$  用以吸收增益起伏过大时的能量，一定程度上还有助于消除失真产物并实现宽带匹配。

## 3 仿真结果

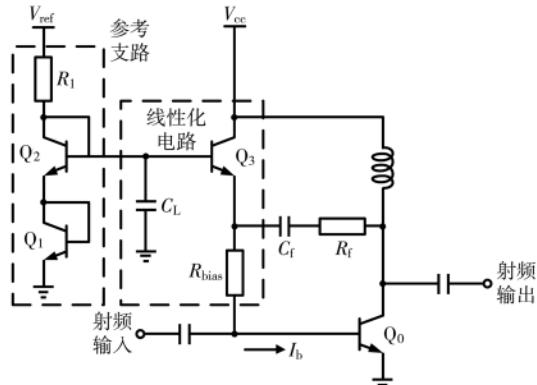

4.9 GHz 伪差分功放电路采用三级架构、5 V 供电与 3.3 V 的参考电压，单路上从驱动到功率输出各级分别并联了 4、10 和 40 个晶体管，对应的静态电流设置成 24 mA、63 mA 和 180 mA 以确保功放能获得足够大的功率输出与增益能力；级间匹配设计遵循最大功率传输定理并使用高通双 L 形网络来拓展带宽。另外，所有贴片式电容元件均使用村田制作所 0201 尺寸的型号，基板

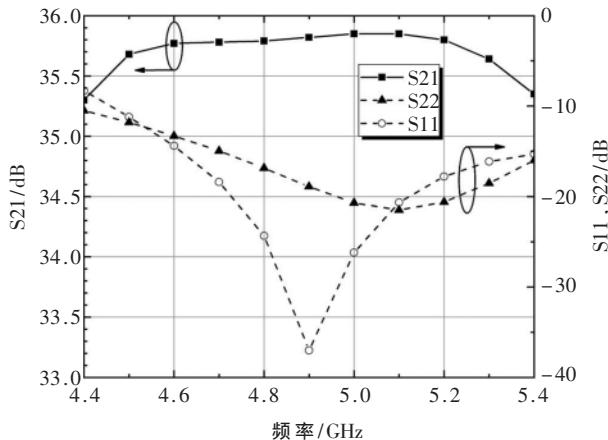

绕线电感通过 Momentum 电磁仿真建模。整体电路经过 ADS 软件的调谐优化后,小信号 S 参数的仿真结果如图 4 所示,在 4.5~5.3 GHz 的频带范围内,三级伪差分功放实现了 35.6~35.8 dB 的平坦小信号增益,以及输入与输出反射系数均能达到小于 -11 dB 的性能。

图 4 小信号 S 参数

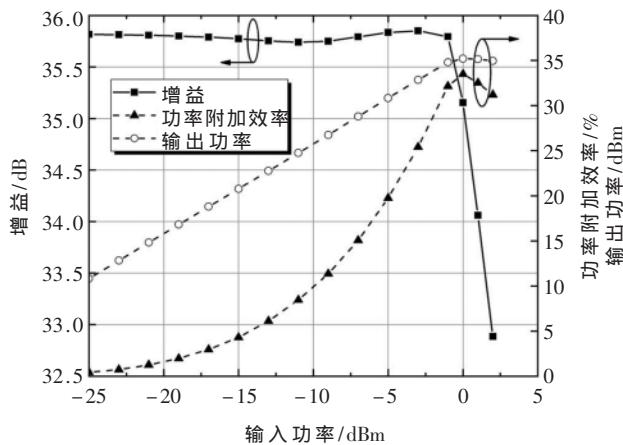

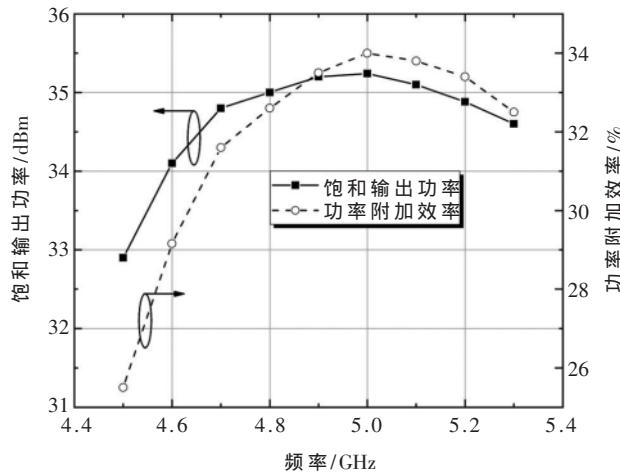

图 5 给出了在中心频率下的单音谐波平衡仿真情况,当输入功率为 0 dBm 时,功放取得 33.5% 的峰值功率附加效率(Power-Added Efficiency, PAE)与 35.2 dBm 的输出功率,且由于本文有意在第一级偏置电路中引入稍大的线性化电容而使该级功放管出现增益延展现象,利用类似预失真的机理进而补偿二、三级在大信号状态下的增益压缩,这样再结合 RC 负反馈就能将整体功率增益起伏控制在 0.2 dB 以内。鉴于一般实物功放的高频段性能下降较严重,所以在设计时会优先考虑偏高频的输出能力。通过图 6 可见,在 4.8~5.1 GHz 带宽内,级联功放能实现优于 35 dBm 的饱和输出功率与对应不低于 32.5% 的 PAE。

图 5 增益、功率附加效率和输出功率随输入功率变化曲线

#### 4 结论

针对工信部提出适用于 5G 方案所规划的 4.8~5.0 GHz

图 6 不同频点处的饱和输出功率和功率附加效率

频段,本文采用基于片外 LC 巴伦的三级伪差分功放架构,可抑制芯片有源层及基板到地孔寄生电感的影响,并结合有源自适应偏置网络与 RC 负反馈技术,通过 ADS 仿真验证了所设计的 HBT 功放在输入、输出匹配良好的前提下能实现 35.8 dB 的高线性增益与不低于 35 dBm 的饱和输出功率,可满足实际中微基站工作的要求,并为后续工程流片奠定了基础。

#### 参考文献

- [1] LEE J, TEJEDOR E, RANTA-AHO K, et al. Spectrum for 5G: global status, challenges, and enabling technologies[J]. IEEE Communications Magazine, 2018, 56(3): 12–18.

- [2] 池保勇,余志平,石秉学.CMOS 射频集成电路分析与设计[M].北京:清华大学出版社,2006.

- [3] LI W Y, DING Y, LUO H A broadband power amplifier applied in GSM/TD-SCDMA/WLAN system[C]. 15th International Conference on Wired/Wireless Internet Communication. St. Petersburg, Russia, 2017: 261–270.

- [4] 李缉熙.射频电路工程设计[M].鲍景富,唐宗熙,张彪,译.北京:电子工业出版社,2011.

- [5] BAKALSKI W, SIMBURGER W, THURINGER R, et al. A fully integrated 5.3-GHz 2.4-V 0.3-W SiGe bipolar power amplifier with 50-Ω output[J]. IEEE Journal of Solid-State Circuits, 2004, 39(7): 1006–1014.

- [6] BAEK S, AHN H, NAM I, et al. A linear InGaP/GaAs HBT power amplifier using parallel-combined transistors with IMD3 cancellation[J]. IEEE Microwave and Wireless Components Letters, 2016, 26(11): 921–923.

(收稿日期:2020-04-14)

#### 作者简介:

彭林(1995-),男,博士研究生,主要研究方向:射频、微波及毫米波单片集成电路与组件。

## 版权声明

经作者授权，本论文版权和信息网络传播权归属于《电子技术应用》杂志，凡未经本刊书面同意任何机构、组织和个人不得擅自复印、汇编、翻译和进行信息网络传播。未经本刊书面同意，禁止一切互联网论文资源平台非法上传、收录本论文。

截至目前，本论文已经授权被中国期刊全文数据库（CNKI）、万方数据知识服务平台、中文科技期刊数据库（维普网）、DOAJ、美国《乌利希期刊指南》、JST 日本科技技术振兴机构数据库等数据库全文收录。

对于违反上述禁止行为并违法使用本论文的机构、组织和个人，本刊将采取一切必要法律行动来维护正当权益。

特此声明！

《电子技术应用》编辑部

中国电子信息产业集团有限公司第六研究所