# 12 V 电源平面对 DDR4 信号的影响

林楷智,宗艳艳,孙龙,田民政,马骏驰

(浪潮电子信息产业股份有限公司,山东 济南 250101)

**摘要:** 随着互联网的高速发展,5G 时代已经到来,数据的传输速率越来越高,对服务器板卡的研发是个新一轮的挑战。内存的发展从 DDR3 到现在已经广泛使用的 DDR4,其工作电压已降为 1.2 V,而 DDR4 信号的上升沿及下降沿低至百皮秒量级。为确保数据的传输速率以及传输的准确性,DDR4 传输线上的串扰不容忽视。以服务器项目中 PCB 主板的 DDR4 传输线为研究对象,首先设计不同的主板叠层模型,利用不同的叠层结构来控制 DDR4 所在信号层的远端参考层,然后通过调用 Sigrity 工具仿真和实际测试分析不同叠层模型下的测试结果。结果显示,远端参考 12 V 电源平面会对 DDR4 信号造成超过几十毫伏量级的串扰,而 12 V 电源层与信号层之间加入地层屏蔽后,串扰电压显著减小。

**关键词:** DDR4;远端参考平面;仿真分析;叠层;Sigrity

中图分类号: TN402

文献标识码: A

DOI: 10.16157/j.issn.0258-7998.209804

中文引用格式: 林楷智,宗艳艳,孙龙,等. 12 V 电源平面对 DDR4 信号的影响[J]. 电子技术应用, 2020, 46(8):68–71, 76.

英文引用格式: Lin Kaizhi ,Zong Yanyan ,Sun Long ,et al. Analysis of the effect of 12 V power plane on DDR4 signal[J]. Application of Electronic Technique ,2020 ,46(8):68–71 ,76.

## Analysis of the effect of 12 V power plane on DDR4 signal

Lin Kaizhi ,Zong Yanyan ,Sun Long ,Tian Minzheng ,Ma Junchi

(Inspur Electronic Information Industry Co., Ltd., Jinan 250101 ,China)

**Abstract:** With the rapid development of the Internet, the 5G era has arrived and the data transmission rate is getting higher, which is a new challenge to the server research. The memory development has upgraded from DDR3 to DDR4, its operating voltage has reduced to 1.2 V, and the rising edge of the DDR4 signal has dropped to 100 picoseconds. In order to ensure the transmission rate and accuracy of the signal, the crosstalk on the DDR4 transmission line cannot be ignored. This paper adopts the DDR4 transmission line on the motherboard of the server project. Firstly, different motherboard stack models have been designed, and different stackups are used to change the remote reference layer of DDR4. Then the experiment result under different stackups through simulation by Sigrity tools and actual testing has been analyzed. The result shows that the far reference to the 12 V power plane will cause crosstalk of more than tens of millivolts to the DDR4 signal. After adding the ground plane shield between the 12 V power layer and the signal layer, the crosstalk voltage is significantly reduced.

**Key words:** DDR4;far reference plane ;simulation analysis ;stackup ;Sigrity

## 0 引言

随着互联网的高速发展,近年来人工智能以及云服务成为互联网主要热门方向。信号的频率以吉赫兹为单位,数据的传输速率要求越来越高,数据的存储需要更大容量的内存,数据的处理需要计算能力更强的 CPU、GPU,这对服务器研发来说是一个巨大的考验。与传统个人计算机不同的是,服务器具有更高的稳定性、更强的计算力、更强的扩展性、更强的协同工作能力等。这样就对读取和存储数据的 DDR 总线提出了更高要求。

存储系统是高性能服务器的重要的数据存储中心,对系统的性能有决定性的影响。为了满足云计算的高带宽数据读取存储的需求,DDR 信号的主频率不断提高,

信号的上升沿及下降沿的时间间隔越来越短,主板上同层并行的 DDR 传输线密度越来越大,DDR 传输线与其他平面层间隔甚至要比同层走线的间隔要小很多。根据电磁场理论,当信号线的间距较小时会发生边缘场的耦合,从而表现出一根信号线的能量耦合到邻近信号线上的现象,业界将其称之为串扰。串扰可能导致数据传输丢失和传输错误,或者更严重的电路误触发现象,此时服务器系统就无法正常工作。DDR4 模块作为服务器系统最重要的存储部分,控制 DDR4 信号的串扰是至关重要的。

因此,如何减小信号的串扰已经成为服务器研发的研究热点。张海涛等人研究了高频信号的回流和电源层的设计,结合仿真实验给出减小串扰的叠层设计<sup>[1]</sup>。严

锦荣等人研究了 DDR4 的码间干扰以及串扰问题, 提出了一种既定数据率下的通道误码率眼图的求解方法, 具有重要的实用价值<sup>[2]</sup>。王怀亮等人利用链路统计分析算法实现了 DDR4 数据误码率眼图的预测, 能够快速有效地预测串扰对 DQ 数据误码率眼图的影响<sup>[3]</sup>。周子翔等人详细介绍了 DDR4 信号总线的信号完整性因素, 包括 DDR4 的串扰, 对 DDR4 的眼图有很深刻的研究<sup>[4]</sup>。孔庆亮等人从 DDR4 实际布局布线出发, 介绍了 DDR4 布局布线方面的部分关键点及注意事项, 对 DDR4 传输线的布局有很大帮助<sup>[5]</sup>。本文主要是用 Cadence 软件研究当 DDR4 传输线远端参考 12 V 电源平面层时, 对 DDR4 传输线的影响。结果表明, 当 DDR4 信号远端直接参考 12 V 电源平面层时, 会在 DDR4 传输线上产生超过 10 mV 的串扰噪声; 加地层屏蔽后, DDR4 传输线上几乎检测不到串扰噪声。

## 1 串扰理论分析

根据电磁场理论, 当信号沿传输线传播时, 信号路径和返回路径之间将产生电力线, 围绕在信号路径和返回路径导体周围也有磁力线圈。这些场并未封闭在信号路径和返回路径之间的空间内, 而是会延伸到周围空间。把这些延伸出去的场称为边缘场。当在边缘场很强的区域布传输线时, 就会引起附近传输线上电流或者电压的变化。将产生边缘场的传输线称为攻击线, 而被干扰的传输线称为受害线。

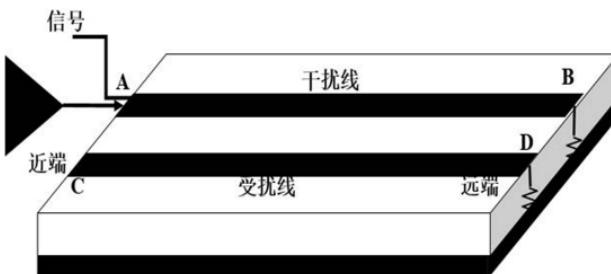

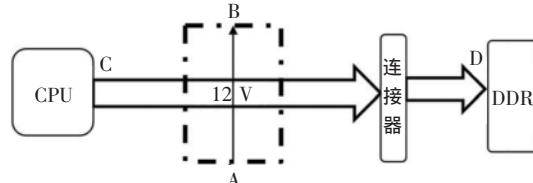

当攻击线边缘场的电磁耦合形成耦合电感和耦合电容, 就会在相邻的受害线上产生串扰噪声。容性耦合产生耦合电流, 感性耦合产生耦合电压。图 1 所示是一个典型的串扰模型, 其中 AB 传输线为攻击线, CD 传输线为受害线, 在信号传输过程中 AB 传输线上的信号就会通过容性耦合与感性耦合的形式耦合到 CD 传输线上。通常将受害线上 C 端测得的电压称为近端串扰电压, 将 D 端测得的电压称为远端串扰电压。

图 1 两条并行传输线近端远端串扰

事实上, 在实际高速电路系统中被干扰线也影响着干扰线, 两者相互干扰。互感耦合和互容耦合作为引起串扰的基本元素, 感应电压和感应电流可以通过以下公式计算:

$$V_n = L_m \frac{dI}{dt} \quad (1)$$

$$I_n = C_m \frac{dV}{dt} \quad (2)$$

其中,  $L_m$  为耦合电感,  $C_m$  为耦合电容,  $V_n$  和  $I_n$  分别为在受害线上产生的耦合电压和耦合电流。

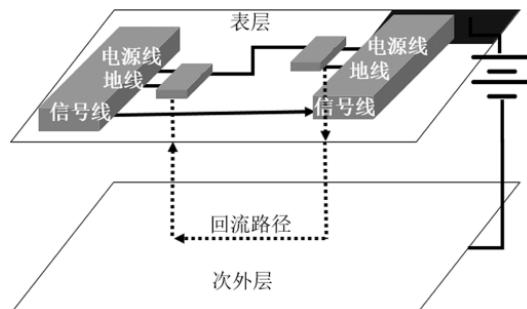

同样的理论也适用在电源与信号线的串扰场景。图 2 为一般信号的回流路径, 其中 L1 层是信号线, 而 L2 层就作为信号线的回流的一部分。作为回流路径的平面, 通常称为参考面。一般以 GND 为参考面, 有时候参考面也可以是电源, 因为直流电源与 GND 之间有大量电容作为交流连接通路。

图 2 信号回流路径

根据图 2 的传输线结构, 参考平面即信号回流路径, 如果参考平面上有较大的噪声电压和电流就比较容易耦合到信号线上。电源对信号的串扰, 以前比较关注供电电源的影响, 因为在芯片端会引入类似同步开关噪声的问题。但以下要分析的是非供电电源对信号的串扰影响。

在进行相应分析时, 应该避免只考虑噪声源为动态电压的电容耦合, 而忽略了噪声源为动态电流的电感耦合。

## 2 基于实际案例进行仿真

某服务器项目 PCB 主板设计中, 布线评估如果可以允许 DDR 远端参考 12 V, 就可以减层从而降低成本。所以需要提供详细的仿真分析报告以评估可行性。

### 2.1 场景概述

需要进行远端参考 12 V 的可行性分析。如果叠层设计为 12 层和 14 层两种, 如表 1 所示, 其中 S 代表信号, G 代表地层即返回路径, P12V 代表 12 V 电源层。14 层叠层去掉 L6、L9 两个地层即得到 12 层叠层, 对比两种叠层下 12 V 平面对 DDR 走线的影响。

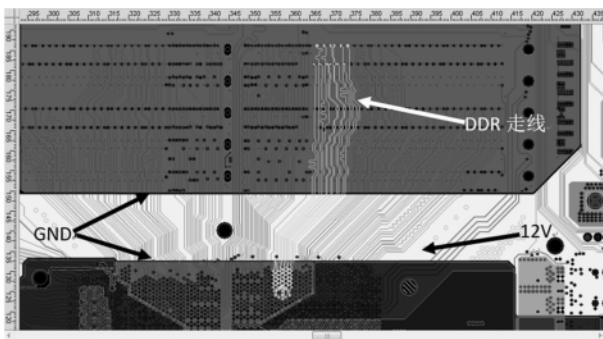

以 L5 层信号线为研究对象, 14 层的叠层中 L5 层与两个 GND 层相邻, 即 L5 的信号线参考完整 GND。12 层的叠层中, L5 层信号线近端参考 GND 远端部分参考 12 V 网络, 此信号层与近端与远端的距离比约为 1:3。图 3 中同时显示 L5 和 L6, L6 作为 DDR 走线的远端参考层, 中间是 12 V 网络, 两边是 GND 平面。

### 2.2 模型建立

此 12 V 链路为电源主通路, 电流较大, 负载较多,

表 1 去 L6、L9 层前后叠层

| 14L | Type | 12L | Type  |

|-----|------|-----|-------|

| TOP | S    | TOP | S     |

| L2  | G    | L2  | G     |

| L3  | S    | L3  | S     |

| L4  | G    | L4  | G     |

| L5  | S    | L5  | S     |

| L6  | G    | 移除  | 以介质填充 |

| L7  | P12V | L6  | P12V  |

| L8  | P12V | L7  | P12V  |

| L9  | G    | 移除  | 以介质填充 |

| L10 | S    | L8  | S     |

| L11 | G    | L9  | G     |

| L12 | S    | L10 | S     |

| L13 | G    | L11 | G     |

| BOT | S    | BOT | S     |

图 3 12 V 电源平面与一组 DDR 信号线

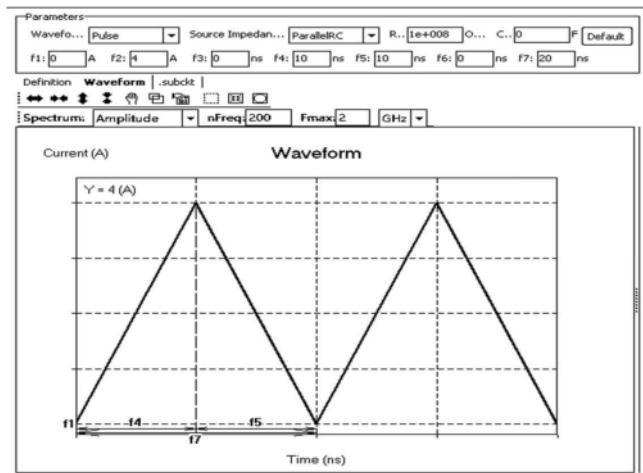

再加上考虑到12 V平面高频电容非常少，所以电源平面上会存在高频电流。结合主板的负载情况，可以得到一个合理的较差电流源模型，如图4所示。即幅值为4 A，周期为20 ns的三角波。

图 4 电流源模型

利用 Cadence 的 Sigrity 系列软件，可以方便地导入 PCB 文件，并抽取板级无源模型，包括信号端口和电源端口<sup>[6-7]</sup>。Sigrity 可以抽取如 S 参数等通用模型，也可以

70 欢迎网上投稿 [www.ChinaAET.com](http://www.ChinaAET.com)

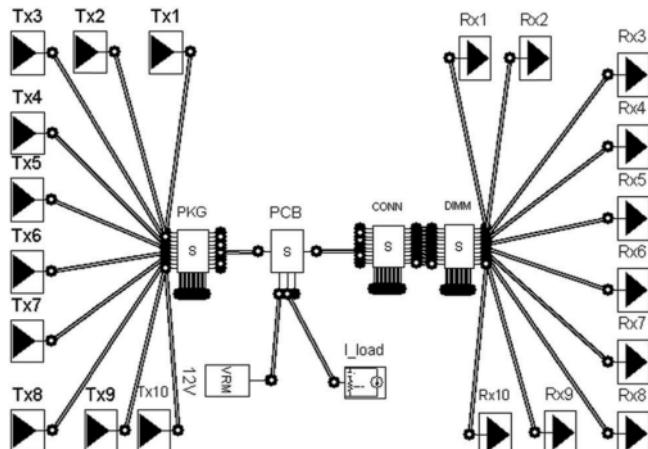

使用其更精简高效的自有模型格式。此案例中，通过 Sigrity 软件抽取了 DDR4 信号从 CPU 端到 DDR 端的无源网络模型，并包含 12 V 电源的源端和负载端端口，如图 5 所示，A 和 B 分别为电源的源端方向和负载端方向，C 为 CPU 端，D 为 DDR 端。

图 5 无源模型框图

再将 CPU、DDR 以及连接器模型导入 Sigrity 软件，就可以搭建仿真框图，如图 6 所示。

图 6 Sigrity 仿真框图

### 2.3 仿真结果分析

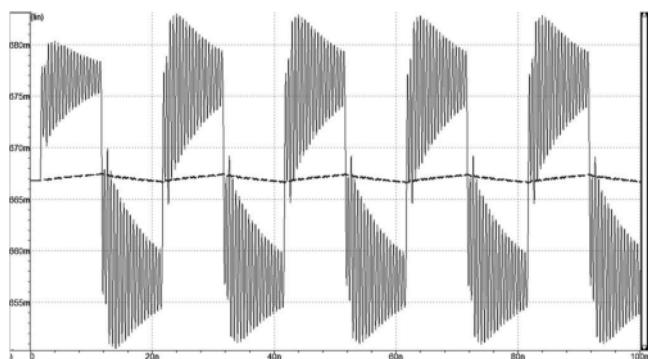

分别针对 14 层和 12 层设计，按照如上仿真流程进行仿真对比。每种叠层进行两种场景的仿真，即全“1”码和 PRBS 码。虽然实际上电源的串扰可能是不定期出现的，但是为了仿真到较差情况，可以以周期信号触发。

仿真设置为全“1”码，仿真时间 100 ns(以保证可以清晰看到串扰周期性)，电流源如图 4 所示。信号流向为 CPU 向 DIMM 写入数据。DDR 接收端的仿真结果如图 7 所示，其中虚线为 14 层设计的仿真波形，串扰幅值在

图 7 两种叠层全“1”码的仿真波形

1 mV 左右, 实线为 12 层设计的仿真波形, 串扰幅值约为 35 mV。

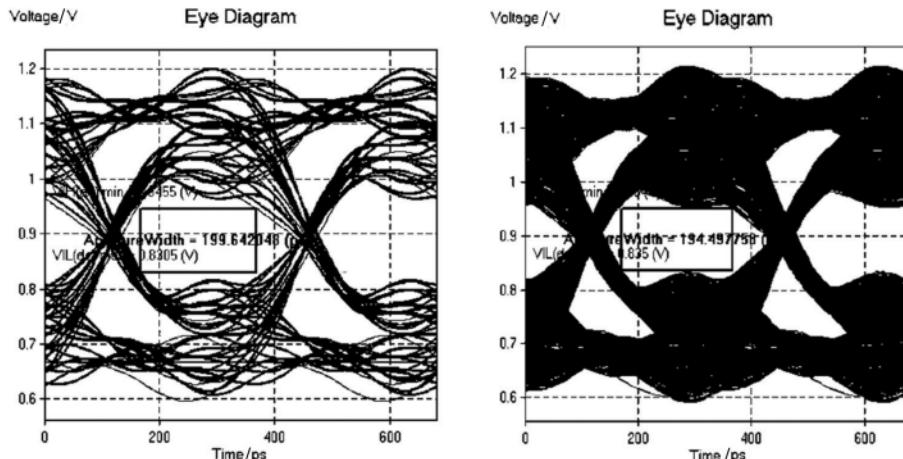

仿真码型设置为 PRBS, 速率 2 933 Mb/s, 仿真时间 500 ns(保证有明显的周期串扰, 且仿真显示已接近全“1”码时的串扰幅值), 电流模型如图 4 所示, 信号流向为 CPU 向 DIMM 写入数据。DDR 接收端仿真结果如图 8 所示, 左侧为 14 层的仿真结果, 右侧为 12 层的仿真结果。

由图 8 可以得到眼高和眼宽的裕量对比, 如表 2 所示。

从全“1”码的仿真结果显示, 远端参考 12 V 的场景带来了 35 mV 的串扰。而 PRBS 码进行的眼图仿真显示眼高和眼宽都有明显劣化。

仿真的局限性在于:(1)实际负载较为复杂无法预料最差电流源;(2)仿真虽然纳入 12 V 电源影响, 但由于简化分析对象的原因, 并没有考虑同步开关噪声场景,(仿真工具本身支持);(3)仿真未考虑环境温度影响;(4)由于时间限制仅进行了 500 ns 瞬态仿真。

图 8 两种叠层 PRBS 码型仿真结果

表 2 两种叠层下 DDR 信号处眼高眼宽

| 叠层  | 眼高要求   | 眼高裕量    | 眼宽要求    | 眼宽裕量     |

|-----|--------|---------|---------|----------|

| 12L | 115 mV | 无       | 78.4 ps | 115.6 ps |

| 14L | 115 mV | 约 30 mV | 78.4 ps | 121.6 ps |

但是仍可以结合此仿真结果判断此远端参考 12 V 的设计为高风险。依据:(1)走线长度已经接近芯片厂建议的最长值;(2)仿真显示劣化的程度和趋势比较明显;(3)如上局限性场景都会导致更差的结果。

### 3 测试结果分析

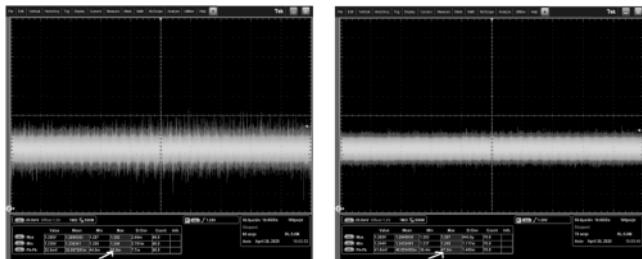

如上两种叠层设计回板, 进行简单的全“1”码测试比较即可看到远端参考 12 V 导致的劣化趋势。

测试仪器泰克高速示波器, 无源探头, 设置带宽为 500 MHz, 采样率设置为 10 GS/s, 横轴设置为 50 μs 每格, 纵轴设置为 20 mV 每格。测试点为接近 DDR 的过孔处, 虽然并非 DDR 的内部, 但考虑到 DDR 的封装参数较小, 此处的测试数据可以作为参考。测试结果显示远端参考 12 V 的 DDR 噪声峰峰值至少比原设计大了 45 mV。如

图 9 所示, 右侧为 14 层的测试结果, 左侧为 12 层的测试结果。分别取同样时间段(比如 1 min)峰峰值的最大值, 右侧显示最大为 47.2 mV, 左侧显示最大为 92.8 mV。

图 9 全“1”码测试

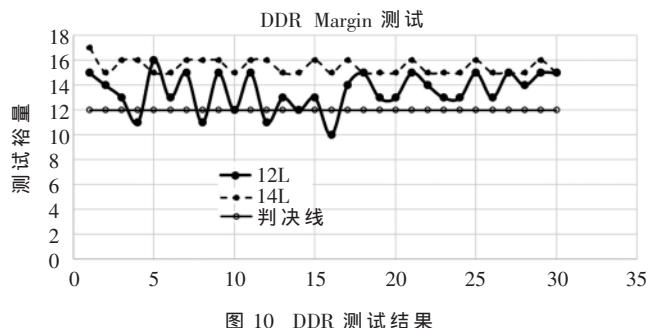

进行常规 DDR 测试, 结果如图 10 所示。横轴表示不同配置、场景或者型号, 纵轴定义测试裕量的判决门限为 12。测试显示远端参考 12 V 的设计 DDR 测试不仅明显差于原设计, 且有多个点低于判决标准。测试结果显示不通过。

测试结果显示, 本实例中的远端参考 12 V 设计测试不通过, 也呼应了仿真分析的高风险结论。

### 4 结论

本文研究了 12 V 电源平面对 DDR4 走线串扰的影响。由于 12 V 路径通常缺少较多的高频滤波电容, 通常视为大噪声电压。而 DDR 为单端并行总线, 单端线无法消除电源的共模串扰。仿真以及实验结果表明:如果 DDR 走线参考 12 V 等大噪声电源平面, 即使是远端参考也足以严重劣化 DDR 信号, 此时产生的串扰, 尤其对于 DDR4 信号是难以接受的。而 12 V 电源层与信号层之间加入 GND 层后, 串扰电压显著减小。设计合理的叠层, 使得 DDR4 信号有较好参考平面, 则串扰可以有效规避。

图 10 DDR 测试结果

### 参考文献

- [1] 张海涛, 赵亦工. 高速 PCB 的叠层设计[J]. 电子工艺技术,

(下转第 76 页)

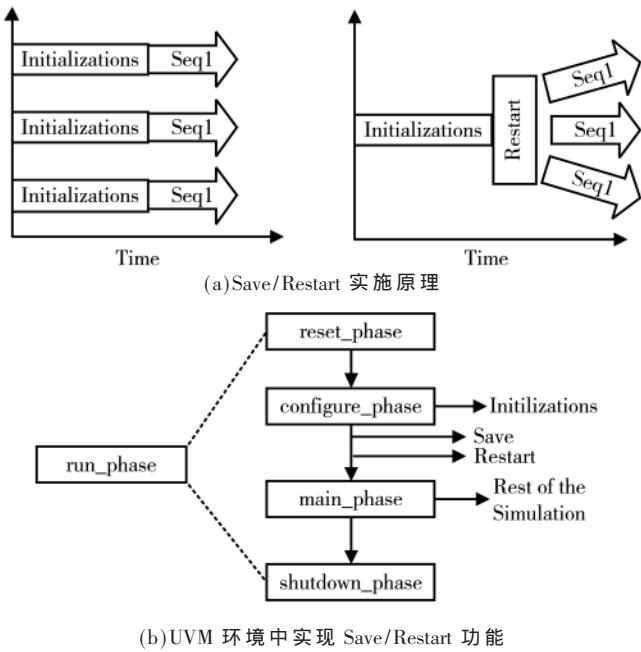

图 6 采用 Save/Restart 实现仿真保存与再次运行

验证人员自己开发的 BFM(Bus Function Model)及验证环境,有以下几个突出的优点:

(1)可以极大地缩短验证环境的开发时间,提升验证效率。一个验证环境若从零开始搭建到功能逐步完善,往往需要数月的时间,而在采用 VIP 后,时间大幅缩短,使得工程师能够专注于 DUT 的功能验证,提升 BUG 定位能力。

(2)VIP 中的检查机制更为全面与细致,可以完整记录每个事务包的处理流程,对于出现问题的报文可以做到其全流程的完整追踪,极大地方便了错误调试。

(3)针对 Cache 一致性相关协议,由于存在众多的场景与状态需要验证,VIP 提供的覆盖率模型更加完整,对于验证的快速收敛有着极大的帮助。

在本文所述验证环境中,由于所选 DUT 并非全新设计且在采用 VIP 进行验证前已使用自主搭建的验证环境进行了完善的功能验证,DUT 趋于稳定,因此采用 VIP

(上接第 71 页)

- 2003, 24(6): 247–250.

- [2] 严锦荣. 基于 DER 的高速链路通道误码率眼图的实现[J]. 电子科技, 2016, 29(5): 30–33, 38.

- [3] 王怀亮, 徐志华, 严锦荣, 等. 基于统计算法的 DDR4 DQ 信号误码率眼图的实现[J]. 电子科技, 2015, 28(7): 124–128.

- [4] 周子翔. 基于 DDR4 高速并行总线的眼图分析[D]. 西安: 西安电子科技大学, 2015.

- [5] 孔庆亮. DDR4 电路设计及布局布线分析[J]. 工业控制计算机, 2020, 33(1): 128–129.

- [6] 邓素辉, 谭子诚, 鄢秋荣, 等. 基于 Cadence 软件高速 PCB

后并未发现很多设计 bug,但对整个项目有如下两点重要贡献:

(1)完整地构造出所有合法 Cache 状态并完成所有类型的请求验证,为之后项目的顺利进行提供方向。方便地构造出之前验证中很难出现的 UPD 状态,并完成包含 WriteCleanPtl 和 WriteBackPtl 报文的随机压力测试,而之前对于此类型报文均只能够进行定向测试。

(2)借助 VIP 强大的随机压力测试激励,在系统验证后期发现一处隐藏很深的设计 bug,阻止了该 bug 逃逸到硅后而造成重大损失。

#### 4 结论

本文所述采用 VIP 搭建的全局数据一致性验证环境,为复杂的 Cache 一致性验证提供了良好的解决方案。验证环境均采用模块化的形式搭建,可以通过配置完成不同规模的验证要求,同时采用 CHI VIP 与 IVD VIP,可以实现从模块级到子系统级甚至系统级的数据一致性验证。利用 VIP 强大的可配置性和完善的信息输出,实现了对自定义互联协议片上网络的验证,同时极大地改善了一致性协议调试能力,提高了验证效率。基于本文所述的验证方法与验证流程,为之后项目中 Cache 一致性相关验证的开展提供了宝贵经验。

#### 参考文献

- [1] 王振江, 周恒钊. 一种验证 Cache 一致性协议的装置及方法: 中国, CN107368434A[P]. 2017-11-21.

- [2] 张强. UVM 实战[M]. 北京: 机械工业出版社, 2014.

- [3] Save restart and dynamic test flows in UVM[R]. Cadence, 2020.

(收稿日期: 2020-06-20)

#### 作者简介:

范君健(1993-), 男, 硕士研究生, 主要研究方向: 微处理器设计与验证。

晁张虎(1989-), 男, 硕士研究生, 主要研究方向: 微处理器设计与验证。

杨庆娜(1986-), 女, 硕士研究生, 主要研究方向: 微处理器设计与验证。

设计的信号完整性仿真[J]. 实验室研究与探索, 2017, 36(12): 116–120.

- [7] 覃婕, 阎波, 林水生. 基于 Cadence Allegro 的高速 PCB 设计信号完整性分析与仿真[J]. 现代电子技术, 2011, 34(10): 169–171, 178.

(收稿日期: 2020-06-22)

#### 作者简介:

林楷智(1977-), 男, 本科, 高级工程师, 主要研究方向: 服务器架构设计。

宗艳艳(1982-), 通信作者, 女, 本科, 中级工程师, 主要研究方向: 服务器架构设计。

孙龙(1986-), 男, 硕士, 中级工程师, 主要研究方向: 信号完整性、电源完整性。

## 版权声明

经作者授权，本论文版权和信息网络传播权归属于《电子技术应用》杂志，凡未经本刊书面同意任何机构、组织和个人不得擅自复印、汇编、翻译和进行信息网络传播。未经本刊书面同意，禁止一切互联网论文资源平台非法上传、收录本论文。

截至目前，本论文已经授权被中国期刊全文数据库（CNKI）、万方数据知识服务平台、中文科技期刊数据库（维普网）、DOAJ、美国《乌利希期刊指南》、JST 日本科技技术振兴机构数据库等数据库全文收录。

对于违反上述禁止行为并违法使用本论文的机构、组织和个人，本刊将采取一切必要法律行动来维护正当权益。

特此声明！

《电子技术应用》编辑部

中国电子信息产业集团有限公司第六研究所