# 一种基于 FPGA 的多路 HD-SDI 测试系统

钱宏文, 王毅, 刘会

(中国电子科技集团公司第五十八研究所, 江苏 无锡 214072)

**摘要:** 针对目前工业现场 HD-SDI 测试环境搭建复杂、成本高、SDI 传输特性测量难度大的特点和需求, 设计和开发了一种基于 FPGA 的多路 HD-SDI 测试系统。首先通过 FPGA 读取存储在 SD 卡中的图像数据, 然后将读取的数据缓存在 DDR3 中, 最后通过 FPGA 解析和处理后发送给外部的 SDI 串化器和 SDI 线缆驱动器, 完成多路 HD-SDI 标准图像的输出。实验结果表明, 该测试系统满足 HD-SDI 传输协议的标准和要求, 可用于模拟不同场景下的测试环境和标定现场, 并且还具有操作简单、适用性广的优点。

**关键词:** 高清数字接口(HD-SDI); DDR3; 串化器; 线缆驱动器

中图分类号: TN402

文献标识码: A

DOI: 10.16157/j.issn.0258-7998.200290

中文引用格式: 钱宏文, 王毅, 刘会. 一种基于 FPGA 的多路 HD-SDI 测试系统[J]. 电子技术应用, 2020, 46(8): 121-125.

英文引用格式: Qian Hongwen, Wang Yi, Liu Hui. Multi-channel HD-SDI test system based on FPGA[J]. Application of Electronic Technique, 2020, 46(8): 121-125.

## Multi-channel HD-SDI test system based on FPGA

Qian Hongwen, Wang Yi, Liu Hui

(China Electronics Technology Group Corporation No.58 Research Institute, Wuxi 214072, China)

**Abstract:** Aiming at the problems in the present industrial field HD-SDI test such as the test environment building complex, high cost, SDI transmission characteristics measurement is difficult, this paper designs and develops a multi-channel HD-SDI test system based on FPGA. Firstly, the image data stored in SD card is read through FPGA, and then the data is cached in DDR3. Finally, it is sent to external SDI serializer and SDI cable driver after FPGA analysis and processing, so as to achieve the output of multi-channel HD-SDI standard image. The experimental results show that the test system meets the standard and requirements of HD-SDI transmission protocol, and can be used to simulate the test environment and calibration site in different scenarios, and has the advantages of simple operation and wide practicality.

**Key words:** HD-SDI; DDR3; serializer; cable driver

## 0 引言

串行数字接口(Serial Digital Interface, SDI)是由美国电影与电视工程学会(The Society of Motion Picture and Television Engineers, SMPTE)制定的协议标准, 通过利用同轴电缆来传输非压缩的数字视频信号。目前, 按照视频的分辨率和传输速率不同主要分为三种: 标清视频(SD-SDI)、高清视频(HD-SDI)和 3G 视频(3G-SDI)<sup>[1]</sup>, 如表 1 所示。

HD-SDI 接口协议是由 SMPTE292M 标准制定的, 用于传递 YCrCb(4:2:2)的串行数字信号。HD-SDI 支持 1.485 Gb/s 和 1.485/1.001 Gb/s 两个比特率, 通常用于传输 720p 或 1080p 分辨率的视频。它采用无损非压缩的传输技术<sup>[2]</sup>, 优点是经过编码后的 HD-SDI 信号能够在同轴线缆上传输 1080P 的高清视频信号, 连接方式简单、延迟小、图像无压缩、显示效果清晰。

HD-SDI 因为具有分辨率高、动态范围广以及在白

表 1 三种 SDI 标准的常见参数列表

| 视频质量   | 协议标准      | 传输速率                     | 宽高比  | 分辨率                      |

|--------|-----------|--------------------------|------|--------------------------|

| SD-SDI | SMPTE259M | 270 Mb/s                 | 4:3  | 480i<br>576i             |

| HD-SDI | SMPTE292M | 1.485 Gb/s<br>1.483 Gb/s | 16:9 | 720p<br>1 080i<br>1 080p |

| 3G-SDI | SMPTE424M | 2.97 Gb/s                | 16:9 | 1 080p                   |

(“p”表示逐行扫描, “i”表示隔行扫描)

平衡、对比度、亮度等方面的优劣性, 使之成为广播电视、高清成像及显示设备的主要接口, 应用范围更加广泛。与此同时, 高分辨率必然要更高的数据带宽进行传输, 高数据带宽对传输信号的实时性和传输误码率提出了更高的要求。本文针对工业现场 HD-SDI 测试环境搭建复杂、成本高、HD-SDI 传输特性测量难度大的特点和需求, 设计和开发了一种基于 FPGA 的多路 HD-SDI 测

试系统。经过测试和验证系统性能稳定、结构简洁、使用灵活方便。

## 1 HD-SDI 传输原理

### 1.1 HD-SDI 数据传输格式

HD-SDI 接口包含两个 10 bit 的数据流,当没有经过压缩的 4:2:2 数字视频采用 HD-SDI 标准协议传输时,1 个数据流用于传输亮度信号(Y),另一个被用于传输色度信号分量(Cr 和 Cb)。每一个像素都是由 Y 和 Cr 或 Cb 构成。

行作为 HD-SDI 传输视频数据结构的基本单位,当在传输一行的视频信号时,等同于传输数据图像的一个水平行,HD-SDI 的数据行是由两个区组成的:视频有效区和行消隐区,行消隐区指的是从 EAV 开始至 SAV 结束<sup>[3]</sup>,行的数据流组成如图 1 所示。

由图 1 可见,HD-SDI 数据流中不仅包含了图像的有效数据,还具有一些特征数据和用于校验的数据,特征数据主要是指包含 SAV 和 EAV、行信号以及 CRC 校验码。EAV 的基准码既表明了上一个有效视频信息的结束,也代表下一行数据水平消隐区的开始。基准码(SAV)表明了水平消隐区的结束,也代表了有效视频区的开始。

图 1 显示的是 HD-SDI 中一个数据流的行格式,另外一个数据流和它具有完全相同的行格式。除此之外,两个数据流也一定要完全的同步,具体是需要两个数据流的行消隐区、SAV、EAV 有效视频区都要完全对齐。

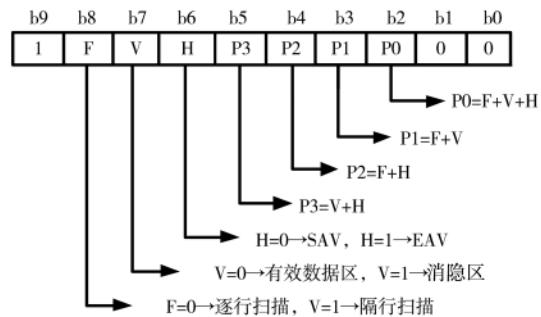

EAV 区域由四个字节组成,第一个字节全为 1,第二和第三字节数据全为 0,第四字节通常表示为 XYZ,该字节具有行数据的很多特征信息。第四字节的构成如图 2 所示。

XYZ 字节中的 b6 位为 H 位,它代表了这个四字节的定时基准码是 EAV 或者是 SAV。当 H 为 1 时,基准码为 EAV;当 H 为 0 时,则为 SAV。b8 即 F 位代表扫描图像的方式为隔行扫描还是逐行扫描。b7 即 V 位是标志数据,当 V 为 1 时则代表处于消隐区,当 V 为 0 时则代表处于有效数据区。XYZ 的其他位数据用于错误保护<sup>[4]</sup>。

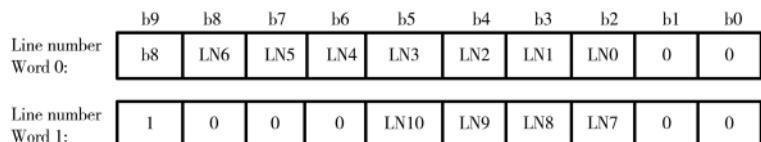

在 EAV 字节后边的两个字节数据则包含了行的数据信息 LN, LN 行数据格式如图 3 所示。

HD-SDI 的 LN 两个数据流中都有相应的行,并且这两个数据流对应的行信息也一定要相互匹配和对齐。行号是由 1 开始,其最大值是由 HD-SDI 图像的格式所决

图 2 EAV 的第四个字节格式

图 3 LN 行数据格式

定的。LN 紧跟其后的两个字节则代表了一个数据帧对之前一行数据的 CRC 校验码(循环冗余校验码)。HD-SDI 协议制定的规则是由接收其使用的 CRC 校验码来检测数据传输中的错误信息。出现错误信息后,便于检测互联设备中错误的链路以方便修复或替换<sup>[5]</sup>。HD-SDI 信号中 CRC 校验码的计算方程式:

$$CRC = x^{18} + x^5 + x^4 + 1 \quad (1)$$

该 CRC 方程式所计算的数据量是指从该行的第一个有效视频字节到下一行 LN 的第二个字节。并且,SAV 和水平消隐区不包含在 CRC 计算式的范围之中。

SAV 与 EAV 的数据格式类似,SAV 和 EAV 的不同之处是 SAV 的 XYZ 中的 H 位始终等于 0,紧随在 SAV 之后的数据,即首个有效视频区域后的数据,一般叫作采样零。

### 1.2 HD-SDI 编码方式

根据 HD-SDI 的协议标准可知,SDI 的数据流中不含有时钟信息,SDI 的原始数据采用 NRZ(归零码)编码格式<sup>[6]</sup>。由于只含视频数据不含时钟信号,因而 NRZ 的码流中非常容易出现连续的“0”或“1”数据,连续的长串“0”及“1”会导致数据流信号中含有的低频信号分量所占比例更高,以至于电平跳变数量变少导致时钟信息缺乏。为避免这种问题出现,HD-SDI 的信道编码方式根据 SMPTE 协议规定,使用非归零码<sup>[7]</sup>。非归零码按照多项式对数据流进行加扰处理,加扰后多项式为:

$$G(x) = (x^9 + x^4 + 1)(x + 1) \quad (2)$$

加扰后的串行数据流中连续“0”或“1”就变得很少,

| EAV |     |     |     | LN |    | CRC  |      | Blank or HANC Data | SAV |     |     |     | Active Video |    |     |    |     |        |       |  |

|-----|-----|-----|-----|----|----|------|------|--------------------|-----|-----|-----|-----|--------------|----|-----|----|-----|--------|-------|--|

| 3FF | 000 | 000 | XYZ | L0 | L1 | CRC0 | CRC1 | Blank or HANC      | 3FF | 000 | 000 | XYZ | Cb0          | Y0 | Cr0 | Y1 | ... | Cr1919 | Y1919 |  |

图 1 HD-SDI 数据流的行结构图

# 嵌入式技术

## Embedded Technology

电平的上下跳变信息会变得多样和变化,方便在接收端进行时钟信息的提取,这就是SDI信号传输的基本原理和方法。

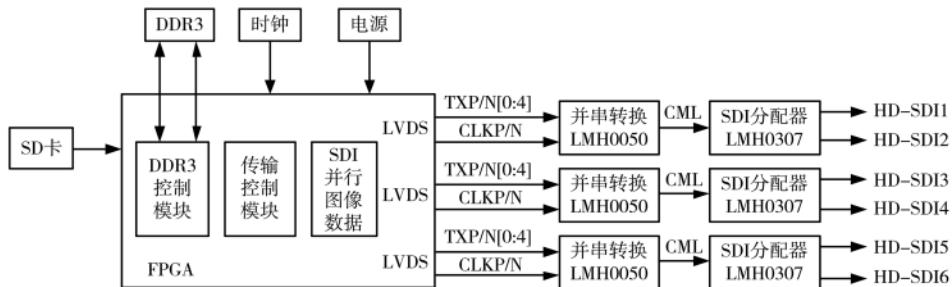

### 2 系统设计

多路HD-SDI测试系统,主要由FPGA控制器、SDI线缆驱动器、SDI串化器、DDR3、SD卡以及时钟和电源组成,系统整体框图如图4所示。

整个硬件的主要功能是:首先通过FPGA接收和读取外部SD卡中存储的图片信息缓存到DDR3中,然后通过并串转换电路将FPGA接收的并行数据转化为串行SDI数据,最后通过线缆驱动器将串化后的SDI数据输出外接75Ω的BNC接口。

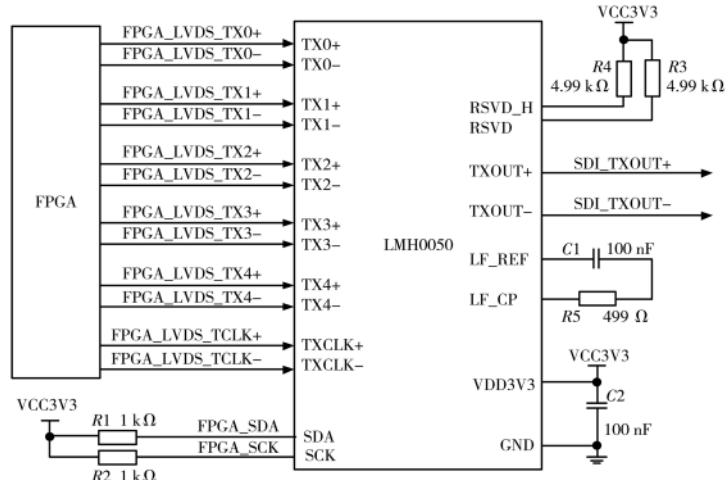

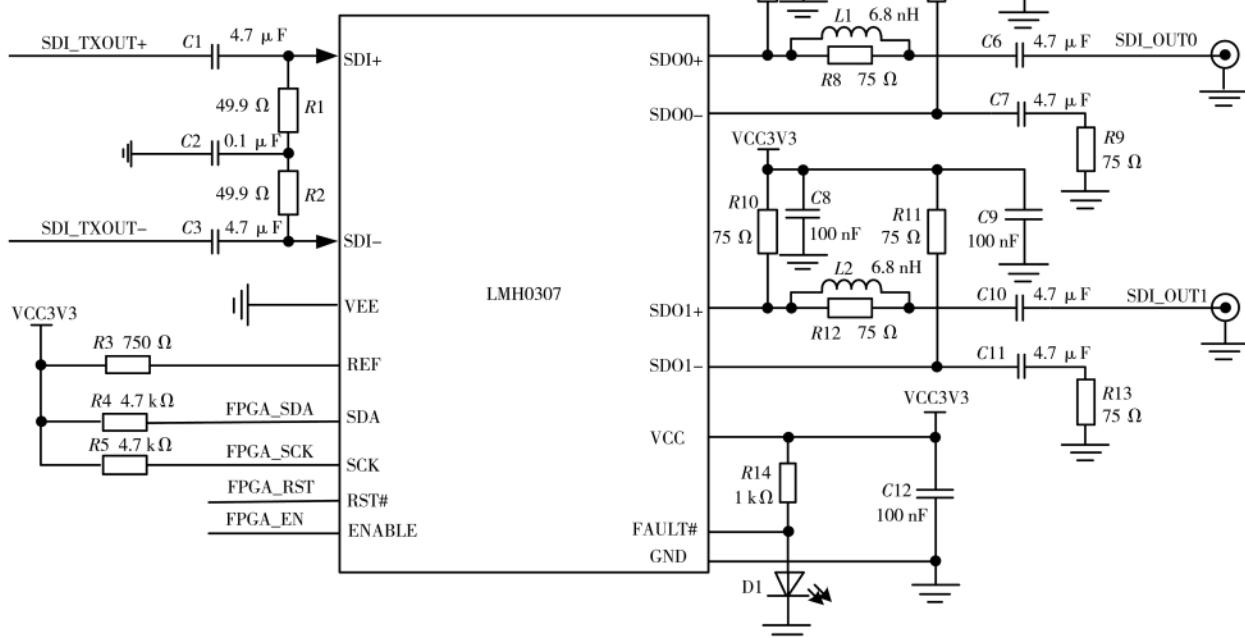

并串转换电路和FPGA之间数据的传输主要由5bit的LVDS数据和1路CLK时钟组成,互联方式采用直流耦合,电平标准统一为LVDS(低电压差分信号),其硬件原理图如图5所示。

线缆驱动电路是为了提高输出的SDI串行数据的质量和传输距离,因为SDI信号在通过同轴线缆长距离的传输时,就会导致其高频成分衰减过大。因此,需要增加线缆驱动器来减少高频信号的衰减,改善接收到视频信号的品质。

本次设计采用TI公司的LMH0307驱动芯片,该芯片是具有双路输出能力的线缆驱动器,不但能够自适应地调整高频增益,而且还能实现由CML电平转化为LVPECL标准电平,实现电平和阻抗匹配,从而能够获得传输距离远、输出质量较高的HD-SDI信号。线缆驱动

图4 多路HD-SDI测试系统框图

图5 并串转换电路原理图

电路的硬件设计原理图如图6所示。

核心器件FPGA选用Xilinx的Kintex-7系列,为了考

图6 线缆驱动电路原理图

# 嵌入式技术

## Embedded Technology

虑成本和使用的扩展性,选用基于 SRAM 配置的 XC7K325T 器件,该器件包含了 326 080 个可编程逻辑块、840 个 DSP Slice、16 020 Kb 的可编程 BlockRAM 及可编程端口、10 个 CMT、16 个 GTX 等模块、500 个可用 IO 可选择配置为 LVCMOS、LVTTL、LVPECL、LVDS 等多种电平接口。本次设计中主要用到了 LVDS 电平标准接口,作用是把 DDR3 中的并行差分数据传输到外部的 HD-SDI 串化器进行转化,并对并行视频信号进行协议的解析和封装以及定时和数据校验,并且本次设计中也使用和验证了 GTX 内部通过 IP 核进行串化和解串的功能,均已得到实现和验证。

DDR3 SDRAM 选则镁光(Micron)公司的 MT41K256-M16TW 器件,该器件的核心频率和工作时钟均设置为 400 MHz。数据时钟采用双边沿采样速率为 800 MHz。因此,DDR 的数据速率为:800 MHz(数据时钟)×16(数据位宽)×4(DDR3 数量)×80%(读写效率)=40.96 Gb/s。

传输 1 路的 1 080p@30Hz 图像需要的数据带宽为:1 920×1 080×8 bit×3×30=1.49 Gb,本次设计最大同时可支持 12 路的 HD-SDI 图像输出,所需总数据带宽为 1.49 Gb×12=17.9 Gb,总数据带宽小于 DDR3 的读写数据速率带宽,因此采用 DDR3 帧缓存方案可以满足 HD-SDI 系统传输带宽的需求。

### 3 测试与验证

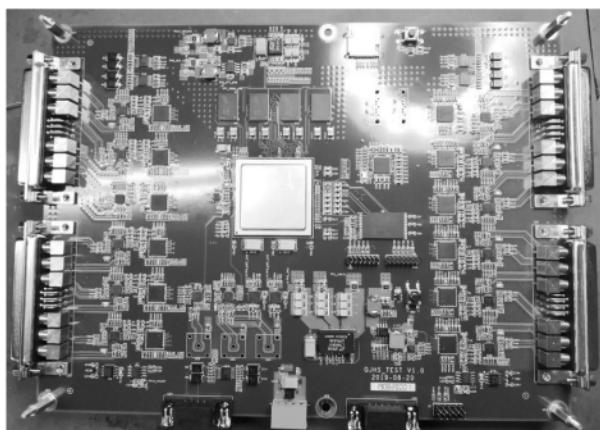

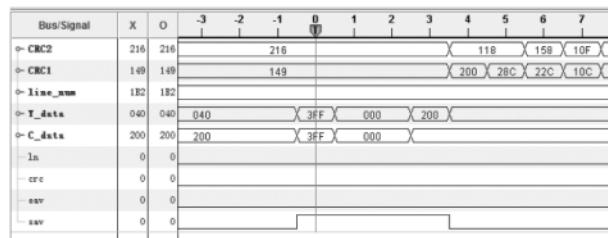

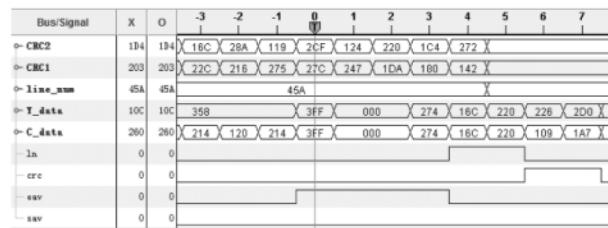

多路 HD-SDI 测试系统,既可以利用 FPGA 内部生成彩条模板,也支持将 SD 卡中的图像导入作为图像源激励,将程序下载至 FPGA 内,通过 Xilinx 的逻辑分析仿真软件可以看到通过该装置成功发送完成最多 12 路的图像的波形和寄存器状态。发送完成后,能够通过 HD-SDI 接口的视频采集盒进行视频图像的采集然后使用显示屏进行显示。设计和开发的测试系统如图 7 所示,发送 HD-SDI 数据的行启始和行结束时序波形如图 8 和图 9 所示。

将已知标定参数的六路外场实验图片(360°环向)存储在 SD 卡中,利用该测试系统进行验证。将产生的 6 路 HD-SDI 信号传送至全景拼接视频采集系统上,

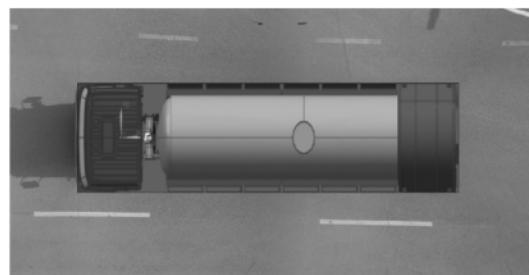

图 7 多路 HD-SDI 测试系统

图 8 行起始 (SAV=1) 时序

图 9 行结束 (EAV=1) 时序

然后将接收后的图像通过采集盒外接显示器进行图像显示,接收后的图像结果显示如图 10 所示(图中含驾驶车辆模型),验证了本次测试系统能够满足 HD-SDI 视频传输的设计要求。

图 10 多路 HD-SDI 测试结果

### 4 结论

本文利用 FPGA 实现了多路 HD-SDI 测试系统的设计和开发,经过开发和测试验证该系统能够满足 HD-SDI 视频传输的标准和要求,可用于模拟不同场景下的测试环境和标定现场,该测试系统具有操作简单方便、成本低、适用性广的优点,具备一定的参考和实践价值。

### 参考文献

- [1] 徐大鹏.HD-SDI 视频嵌入式图像采集设计[J].计算机测量与控制,2015,23(9):3214.

- [2] 孙偲晟.FPGA 的 SD/HD/3G-SDI 的图像环路测试装置设计[J].单片机与嵌入式系统应用,2019(11):69-73.

- [3] SMPTE292M,television-bit-serial digital interface for high-definition television systems[S].1998.

- [4] Society of Motion Picture and Television Engineers.Proposed SMPTE standard for television 1920×1080 image sample structure,digital timing reference sequences for multiple picture rates[G].2003.

- [5] 吴俊霖.基于 FPGA 的 HD-SDI 信号传输与处理[D].成都:

西南交通大学, 2011.

[6] 朱超. 基于 FPGA 的 SDI 视频格式转化系统设计[D]. 长春: 中国科学院研究生院, 2010.

(收稿日期:2020-04-10)

## 作者简介：

钱宏文(1975-),男,本科,研究员级高级工程师,主要

研究方向:集成电路应用和微系统领域设计。

王毅(1991-),男,硕士,工程师,主要研究方向:图像处理、DSP 和 FPGA 应用等方面的数字硬件开发与研究。

刘会(1988-),女,硕士,工程师,主要研究方向:视频分析、图像处理等相关方面的FPGA软件开发与设计。

(上接第 120 页)

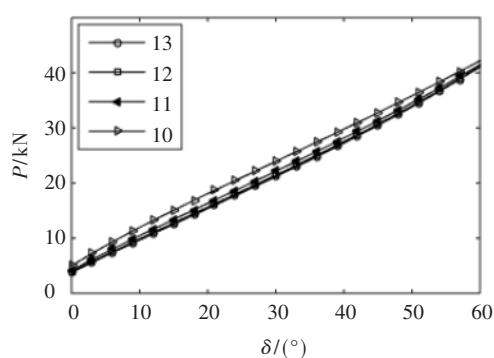

图 11  $a/d=7/3$  时, 拉力  $P$  与倾角  $\delta$  的关系

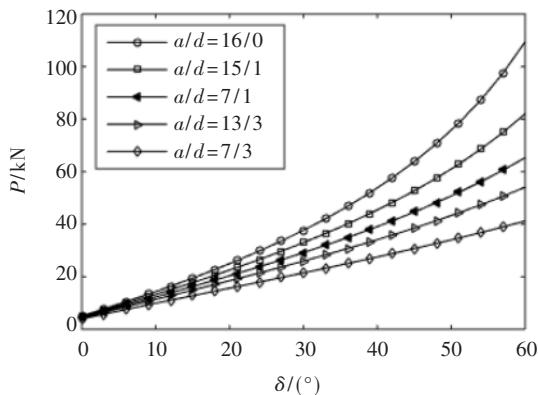

第 10~13 段组塔抱杆  $\delta$  对  $P$  影响如图 11 所示,  $P$  随  $\delta$  增大而增加; 铁塔越高时,  $P/\delta$  斜率与预应力将越大; 当  $\delta < 15^\circ$  时, 拉力  $P < 20$  kN。第 12 段, 当  $a/d$  分别为 16/0, 15/1, 7/1, 13/3, 7/3 时,  $\delta$  对  $P$  影响如图 12 所示, 比值  $a/d$  越大,  $\delta$  对  $P$  影响越大, 即  $P/\delta$  斜率极剧增大; 当  $a/d = 7/3$  时,  $P/\delta$  斜率小且线性度好。因此, 选取  $\delta < 15^\circ$  和  $a/d = 7/3$  时,  $P/\delta$  斜率较小。第 10~13 段的拉线拉力  $P < 20$  kN, 拉绳许用拉力为  $P_s = 98.7$  kN, 则安全系数  $k = P_s/P \approx 5$ , 可保证使用安全性。

图 12  $a/d=16/0, 15/1, 7/1, 13/3, 7/3$  时,  $P$  与  $\delta$  的关系

### 3.2 拉力与倾角监测系统应用

以第 12 段组塔为例, 当期望抱杆  $\delta=10^\circ$  和  $a/d=7/3$  时, 吊件重量  $G=14.7 \text{ kN}$ , 由式(1)、式(3)、式(4)和式(6)分别得到控制绳静张力  $F=4.45 \text{ kN}$ , 起吊绳拉力  $T=$

18.12 kN, 牵引绳张力  $T_c=9.61$  kN, 受力侧单根绳所受拉力  $P=13.27$  kN, 实际安全系数  $k=7$ , 完全满足设计要求。在图 8 中的应用监测平台软件中, 设置倾角阈值  $\delta=15^\circ$ , 拉线许用应力为 98.7 kN。在界面中实时显示 4 根拉线拉力值和倾角角度。拉绳拉力, 受力侧为 13.75 kN 和 13.69 kN; 非受力侧为 5.45 kN 和 5.39 kN; 倾角为  $10.6^\circ$ 。拉力与倾角监测值与设计值非常接近, 满足工程需求。

4 结论

本文针对传统的 ISIB 抱杆系统进行信息化智能化改造,基于物联网技术设计一套无线传输的抱杆倾角与拉力实时监测系统,以提升 ISIB 施工工艺的安全性。该系统已在福建某线路工地试用,工程应用结果表明在确定了倾角和拉力的优化阈值后,使用该系统可实时掌握倾角与拉力状态,可更直观地指导 ISIB 施工工艺的抱杆调节设置,提升该施工工艺的可靠性与效率。

## 参考文献

- [1] 赵世兴,李新民,张存有.750kV 送电线路铁塔内悬浮外拉线抱杆施工工艺与控制[J].中国电力,2009,42(6):89-91.

- [2] 张珂,周焕林,徐金城,等.某内悬浮外拉线抱杆倾角角度的安全性分析[J].特种结构,2015,32(4):44-47.

- [3] 王光祥,吴开贤,景文川,等.内悬浮抱杆的优化设计[J].四川电力技术,2010,33(4):46-47.

- [4] 孙云,陈宏学.抱杆的受力计算研究[J].湖北电力,2009,33(6):27-29.

- [5] 汪瑞,周焕林,秦大燕,等.扣塔组立用抱杆的非线性有限元分析[J].钢结构,2012,27(6):54-57.

- [6] 丁仕洪,周焕林,叶建云,等.某大跨越高塔抱杆的非线性有限元静力分析[J].特种结构,2011,28(3):46-49.

- [7] 李庆林,莫衍毅,褚玉杰.内悬浮(外)拉线抱杆分解组塔索具受力计算的通用图表法[J].电力建设,2013,34(10):124-128.

- [8] 张姗,刘笑凯,王超,等.基于国产化平台监控软件的设计与实现[J].电子技术应用,2018,44(10):140-143.

- [9] 邱欢,乔坤.基于物联网系统的 NOMA 与 SWIFT 结合的研究[J].电子技术应用,2018,44(9):17-21.

(收稿日期:2019-12-04)

## 作者简介：

黃明祥(1971-),男,本科,高级工程师,主要研究方向:电网智能化建设策略与方法。

## 版权声明

经作者授权，本论文版权和信息网络传播权归属于《电子技术应用》杂志，凡未经本刊书面同意任何机构、组织和个人不得擅自复印、汇编、翻译和进行信息网络传播。未经本刊书面同意，禁止一切互联网论文资源平台非法上传、收录本论文。

截至目前，本论文已经授权被中国期刊全文数据库（CNKI）、万方数据知识服务平台、中文科技期刊数据库（维普网）、DOAJ、美国《乌利希期刊指南》、JST 日本科技技术振兴机构数据库等数据库全文收录。

对于违反上述禁止行为并违法使用本论文的机构、组织和个人，本刊将采取一切必要法律行动来维护正当权益。

特此声明！

《电子技术应用》编辑部

中国电子信息产业集团有限公司第六研究所