# 多系统 FPGA 远程更新系统的设计与实现

郝国锋,朱琛,顾晓雪

(中国电子科技集团公司第五十八研究所,江苏 无锡 214072)

**摘要:**为了解决多系统 FPGA 远程更新的局限性,提出了一种基于 SoC 的多系统 FPGA 远程更新系统设计方法。应用以太网协议实现了上位机与 SoC 控制系统的交互,SoC 芯片控制加载流程实现多系统 FPGA 远程更新。通过实际测试,验证了新方法的可行性、正确性。该方法有效解决了传统更新方法操作复杂、距离短、时间长等缺点,对工程应用具有重大意义。

**关键词:**多系统;SoC;FPGA;远程更新

中图分类号: TN74

文献标识码: A

DOI:10.16157/j.issn.0258-7998.200259

中文引用格式: 郝国锋,朱琛,顾晓雪. 多系统 FPGA 远程更新系统的设计与实现[J]. 电子技术应用, 2020, 46(8): 129–131, 136.

英文引用格式: Hao Guofeng, Zhu Chen, Gu Xiaoxue. Design and implementation of multi-system FPGA remote update system[J]. Application of Electronic Technique, 2020, 46(8): 129–131, 136.

## Design and implementation of multi-system FPGA remote update system

Hao Guofeng, Zhu Chen, Gu Xiaoxue

(China Electronics Technology Group Corporation No.58 Research Institute, Wuxi 214072, China)

**Abstract:** In order to solve the limitation of multi system FPGA remote update, a design method of multi-system FPGA remote update system based on SoC is proposed. Ethernet protocol is applied to realize the information interaction between the upper computer and SoC control system, and SoC chip controls the loading process to realize the remote update of multi system FPGA. The feasibility and correctness of the new method are verified by practical test. It effectively solves the shortcomings of traditional updating methods, such as complex operation, short distance and long time, and has great significance for engineering application.

**Key words:** multi-system; SoC; FPGA; remote update

## 0 引言

FPGA(Field Programmable Gate Array)即现场可编程门阵列,具有资源丰富、接口资源多、并行逻辑处理能力强、可重复在线编程等特点,FPGA 高效而灵活的处理方式使其在军事工业、工业控制、人工智能等很多领域得到广泛应用<sup>[1-2]</sup>。Zynq 系列 SoC 芯片作为 Xilinx 公司的全可编程片上系统,集成了 ARM Cortex A9 和 Kintex-7 系列 FPGA,处理速度高至 1 GHz,丰富的逻辑资源及强大的处理器在系统控制中起到关键作用<sup>[3]</sup>。

传统的 FPGA 更新方法采用串行配置边界扫描(JTAG)来访问芯片并对 FPGA 的配置 Flash 进行编程,该方法受限于更新速度和操作距离,仅适用于本地更新<sup>[4-5]</sup>。在多片 FPGA 的大型设备中,JTAG 更新方法需要将每片 FPGA 连接到 JTAG 下载电缆进行程序更新,因此这种方法效率低下,局限性极大。装备于军事设备及置于人工不能操作的严苛环境下的设备中,传统的更新方式不能完成任务需求。为了解决这些问题,FPGA 远程更新已经有相关文献进行了研究,一种方法是利用 FPGA 内部的 MCU 软核进行相应的设计实现,在该方法中 FPGA 的 MCU

软核依存于 FPGA 配置程序中,需要预先加载程序,如果远程更新失败,整个系统面临瘫痪的风险<sup>[4]</sup>。另一种方法是利用 ARM 或 DSP 作为加载控制器,该方法具有电路结构复杂、成本高、实现难度较大等缺点<sup>[6-8]</sup>。鉴于传统更新方式及现存方法的局限性,本文设计了一种基于 SoC 的多系统 FPGA 远程更新系统,并通过工程实现。

## 1 系统设计

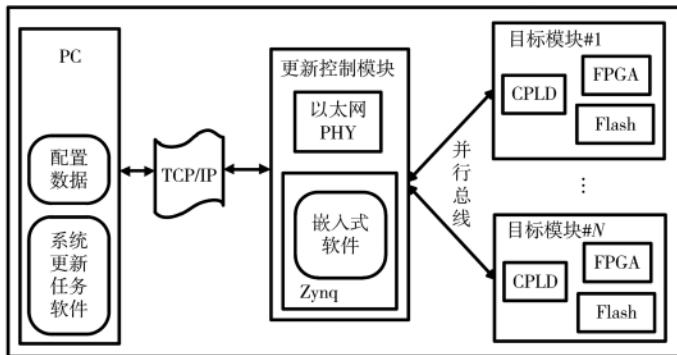

本设计中实现多系统远程更新功能需要管理计算机、多系统更新控制模块、目标模块、系统更新控制软件(包括上位机软件和嵌入式软件)四个部分,其系统组成框图如图 1 所示。

(1)管理计算机(PC):包括上位机开发环境和网络端口,通过系统更新控制软件对控制模块下发指令及配置数据,并在界面上显示目标模块的更新过程状态,实现远程传输更新控制。

(2)更新控制模块:即通过以太网接收管理计算机(PC)下发指令及数据并进行相应目标更新模块信息转发,实现对更新目标在线更新控制。

(3)目标模块(FPGA):即接收到控制模块下发的需要

图 1 远程更新控制系统框图

更新的数据及命令，完成数据加载及校验，目标模块的更新控制核心为 CPLD，通过 CPLD 控制逻辑实现配置 Flash 的读写操作。

(4) 系统更新控制软件：用于控制多系统远程更新任务。

### 1.1 硬件设计

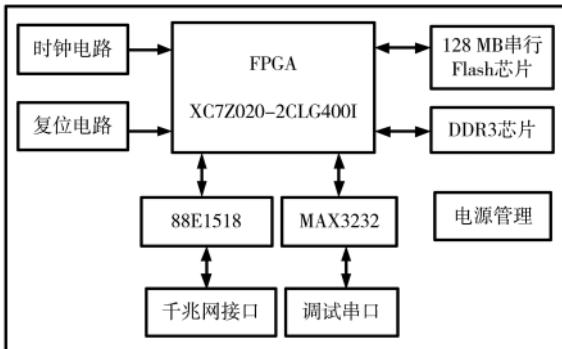

该系统的硬件设计包括多系统更新控制模块及目标模块两部分的硬件设计，模块之间通过同步并行总线连接，实现信息传递及握手。多系统更新控制模块硬件架构如图 2 所示。

图 2 更新控制模块硬件框图

模块选用 XILINX 公司的 Zynq-7000 系列 SoC 芯片作为主控芯片，型号为 XC7Z020-2CLG400I。片内的两个高速的 ARM 处理器核，每个处理器核的运算速度均可达到 2.5 DMIPS/MHz，运行频率最大 800 MHz，内置 USB 2.0 接口、CAN 2.0 接口、SPI 接口、UART 接口以及 PCI-e、高速以太网接口等外部接口<sup>[9]</sup>。在 ARM 核内可以运行 Linux 操作系统，给设计和性能提升提供保障。以太网 PHY 芯片选用 88E1518，具备网络自适应能力。

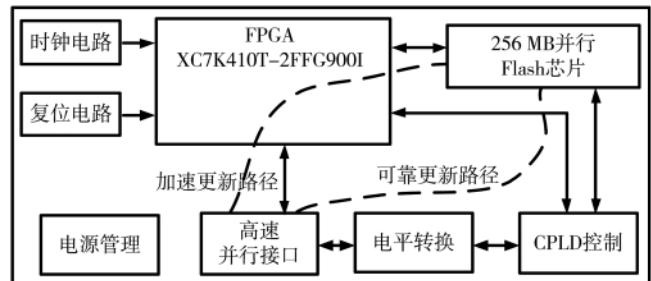

目标模块硬件框图如图 3 所示，设计了两条并行 Flash 更新路径、加速更新路径和可靠更新路径。加速更新路径包含高速并行接口、K7 系列 FPGA 和并行 Flash，由 K7 系列 FPGA 作为 Flash 控制器，该路径具备数据处理效率高、节约更新时间等特点。可靠更新路径包括高速并行接口、电平转换电路、CPLD 控制电路和并行 Flash，

图 3 更新目标模块硬件框图

由 Xilinx 公司型号为 XC2C384-7TQ144 的 CPLD 芯片作为 Flash 控制器，该路径选用非易失的 CPLD，不会因为系统更新失败导致系统崩溃，具备可靠更新的特点。

### 1.2 Flash 控制器设计

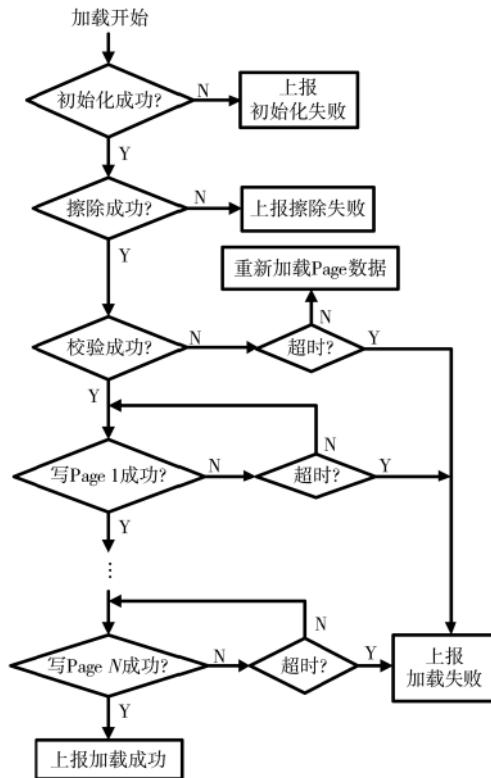

针对上文提到的两条更新路径，分别在 K7 系列 FPGA 和非易失 CPLD 内设计了 Flash 控制器，两个控制器的 Flash 控制流程一致，区别在于并行数据接收处理部分。控制器主要完成并行数据接收、命令解析、更新数据分包、校验、并行 Flash 控制等功能，控制逻辑流程如图 4 所示。

图 4 Flash 控制器控制流程图

Flash 控制器接收到更新命令后开始 Flash 初始化操作。初始化过程中会对 Flash 芯片进行读 ID 操作，用于检验 Flash 芯片状态信息并上报；初始化成功后进行擦除操作，本文设计根据更新文件的大小选择合适的擦除空间进行扇区擦除，节省擦除时间；擦除成功后控制器接收下发的更新数据并进行校验，校验成功的数据包启

# 嵌入式技术

## Embedded Technology

动 Flash 写操作,校验不成功的数据包丢弃,上报丢包结果并启动重发机制;为最大效率写入 Flash 选用了页写入方式,直到更新文件数据全部写入 Flash 中,并上报更新结果。

### 1.3 更新控制软件的设计与实现

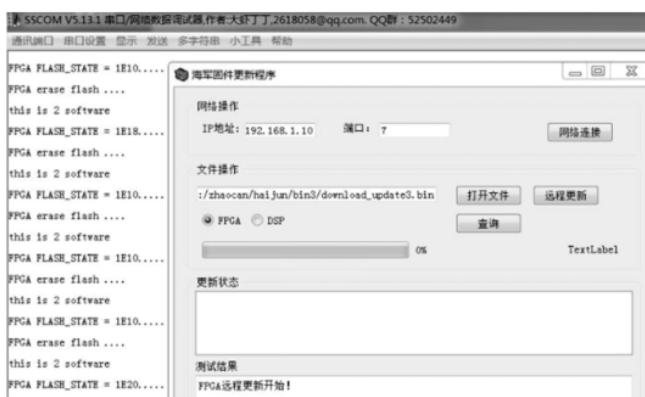

系统更新控制软件分为两部分:第一部分是系统更新任务软件(客户端应用程序),是在上位机端进行开发的人机界面,该软件控制整个更新流程,软件界面如图 5 所示;第二部分功能软件(嵌入式驱动程序),该软件在嵌入式操作系统 Linux 上使用内核 API 函数进行开发,该部分软件主要针对功能硬件进行操作,实现内核启动、接口驱动等特定功能。

图 5 系统更新任务软件界面

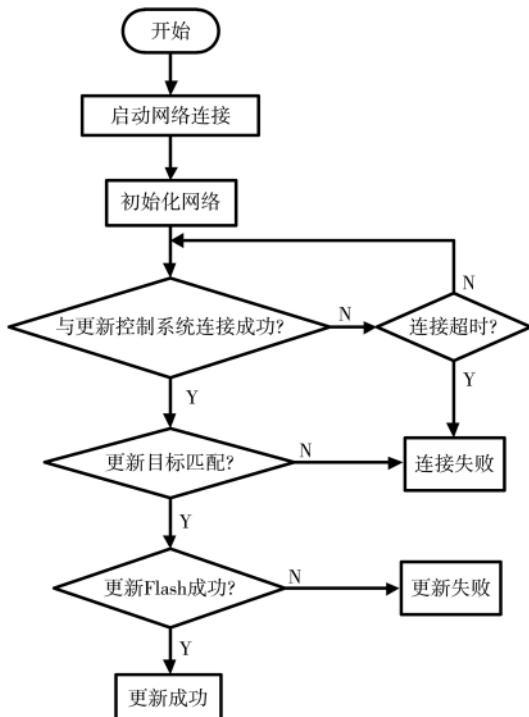

系统更新任务软件流程图如图 6 所示。

系统更新控制软件加载后立即初始化网络控制器,

图 6 系统更新任务软件流程图

启动以太网加载传输接口服务,设置好 IP 和端口号,初始化网络服务,与远程更新控制系统建立连接;管理计算机(PC)发起文件发送请求后,远程更新控制系统确认是远程更新命令并接收更新文件报文信息,并对接收报文进行校验;根据其需要更新的目标模块信息将报文发送至待更新的目标模块内;更新目标模块内 Flash 控制器进行 Flash 擦除及读写操作,Flash 成功更新后回复指令,加载完毕。

客户端软件作为操作及显示终端,可在客户端软件选择需更新的配置文件信息,实时在终端显示网络状态、传输报文结果、更新目标模块信息等内容。

### 2 测试验证与改进

系统更新控制软件执行更新流程完成后,重启更新成功的模块并连接 JTAG 捕捉新更新程序的版本号,验证了加载的正确性,捕捉界面如图 7 所示。

| update_final    | 1        |  |          |

|-----------------|----------|--|----------|

| NO_before[31:0] | 07e30814 |  | 07e30814 |

| NO_now[31:0]    | 07e3b00a |  | 07e3b00a |

图 7 更新验证捕捉界面

以 10 MB 更新文件为例,该系统更新单片 FPGA 文件的时间开销为 70 s(包括擦除时间 30 s),通过下载器应用 JTAG 更新时间达到 220 s<sup>[10-11]</sup>,新更新方法较 JTAG 的更新方法能缩减大量时间。实际应用中通过以太网通信方式同时更新了 5 片 FPGA,时间开销没有大幅度增加,较本地更新方法更方便灵活。

在性能提升上本文设计的更新系统还存在有待改进之处,远程更新的时间开销集中在以太网传输和 Flash 写入两部分。以太网传输时间取决于网络环境以及功能软件的网络吞吐率,提高功能软件处理效率及稳定性,能更大程度提高传输效率;通过提高 Flash 控制器的时钟频率、优化代码效率能提高 Flash 的写入效率。

### 3 结论

本文提出的利用以太网作为通信方式,基于 SoC 芯片实现的多系统 FPGA 远程更新系统设计方法,解决了传统更新方法效率低、距离短、工程需求难以满足等缺点。由于 Zynq 系列 SoC 的设计具有灵活性等特点,更便于远程更新系统性能提升,因此本文提出的方法在实际工程应用中具有重要意义。

### 参考文献

- [1] 吴冬冬,杨晓君,张佩珩.一种 FPGA 的远程系统升级方法[J].计算机工程与应用,2006,18(12):86-87.

- [2] 秦兴,王文,李为健,等.基于 FPGA 的硬件可重构数控系统的研制[J].仪器仪表学报,2002,23(3):407-408.

- [3] 李正轩,费树岷.基于 Zynq-7000 FPGA 的高速信号采集

(下转第 136 页)

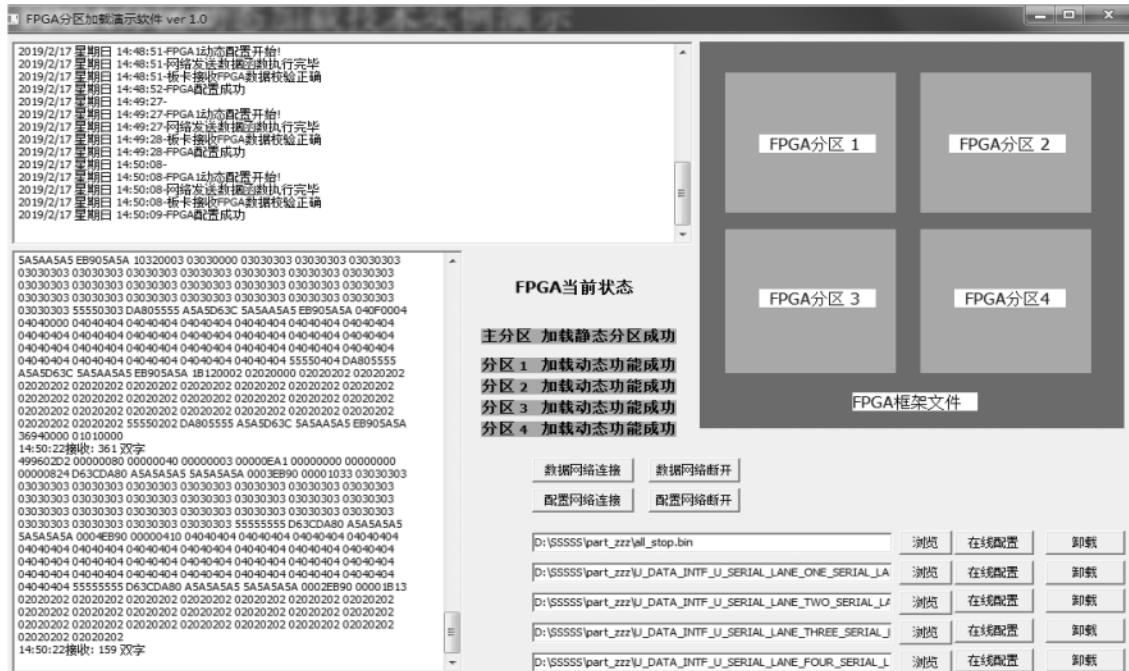

图 7 系统动态重构验证结果

- [3] 王彬, 刘友永. 微波统一测控系统的发展趋势及建议[J]. 无线电工程, 2017, 47(4): 44–48.

- [4] 赵秋明, 王龙飞, 肖丹, 等. 一种新型软件无线电重构加载方法研究[J]. 电视技术, 2013, 37(19): 87–90.

- [5] 熊璐. 基于 CPCI 的动态可重构系统设计与实现[J]. 现代电子技术, 2016, 39(8): 104–107.

- [6] 朱道山. 基于 RapidIO 的 FPGA 远程更新系统设计与实现[J]. 雷达科学与技术, 2017, 15(5): 543–547.

- [7] 张永乐, 王永勇, 郑炜. 一种基于 FPGA 的在线程序升级方案[J]. 电子技术应用, 2017, 43(3): 48–50, 54.

(上接第 131 页)

- 处理平台[J]. 单片机与嵌入式系统应用, 2016, 16(1): 44–47.

- [4] 康嘉, 程鹏, 杨坤, 等. FPGA 自动加载系统设计实现[J]. 现代电子技术, 2013, 36(24): 125–127.

- [5] 葛飞, 何辅云, 夏玉宝. FPGA 被动并行配置控制器的研究与实现[J]. 合肥工业大学学报(自然科学版), 2008(4): 531–533.

- [6] 管武, 王健, 秦霆镐, 等. 基于 ARM 的远程重构通信控制模块的设计[J]. 微计算机信息, 2009, 25(2): 1–3.

- [7] 张晖, 谢凯年. 一种 ARM+DSP 协作架构的 FPGA 验证实现[J]. 电子技术应用, 2007, 33(2): 116–117.

- [8] 朱道山. 基于 RapidIO 的 FPGA 远程更新系统设计与实现[J]. 雷达科学与技术, 2015, 13(5): 543–547.

- [8] 周晖, 黄英, 吴海洲, 等. 统一测控系统新一代综合基带设计研究[J]. 雷达科学与技术, 2018, 16(1): 87–92, 98.

- [9] 张晓明. 便携式数字阵列控制同步和链路测试系统实现[J]. 现代雷达, 2015, 37(4): 43–45.

- [10] 郑百衡, 朱慧惠, 刘盛利, 等. 新型多通道通用信号处理平台设计[J]. 电子技术应用, 2019, 45(10): 109–111.

(收稿日期: 2020-04-28)

#### 作者简介:

王松明(1986-), 男, 硕士, 工程师, 主要研究方向: 数字信号处理、微系统技术。

- [9] 陆佳华. 嵌入式系统软硬件协同设计实战指南: 基于 Xilinx Zynq[M]. 北京: 机械工业出版社, 2013.

- [10] 黄勇. 一种新型的 FPGA 快速动态配置和远程加载技术[J]. 通信技术, 2013, 46(12): 93–96.

- [11] 汪灏, 张学森. 一种基于串行方式的 FPGA 远程加载电路[J]. 电子科学技术, 2016, 3(2): 171–173.

(收稿日期: 2020-04-02)

#### 作者简介:

郝国锋(1984-), 男, 硕士研究生, 工程师, 主要研究方向: 软件无线电技术、可重构硬件。

朱琛(1988-), 男, 硕士研究生, 工程师, 主要研究方向: FPGA 逻辑设计。

顾晓雪(1981-), 女, 硕士研究生, 工程师, 主要研究方向: 数字电路设计、LabVIEW 自动测试系统设计。

## 版权声明

经作者授权，本论文版权和信息网络传播权归属于《电子技术应用》杂志，凡未经本刊书面同意任何机构、组织和个人不得擅自复印、汇编、翻译和进行信息网络传播。未经本刊书面同意，禁止一切互联网论文资源平台非法上传、收录本论文。

截至目前，本论文已经授权被中国期刊全文数据库（CNKI）、万方数据知识服务平台、中文科技期刊数据库（维普网）、DOAJ、美国《乌利希期刊指南》、JST 日本科技技术振兴机构数据库等数据库全文收录。

对于违反上述禁止行为并违法使用本论文的机构、组织和个人，本刊将采取一切必要法律行动来维护正当权益。

特此声明！

《电子技术应用》编辑部

中国电子信息产业集团有限公司第六研究所