# 基于以太网的信号处理平台动态重构设计

王松明

(中国西南电子技术研究所,四川 成都 610036)

**摘要:**信号处理平台通常采用“FPGA+DSP+ARM”架构实现特定的信号处理功能,随着技术的发展,越来越多的工程应用要求信号处理平台具备动态重构功能。介绍了一种基于以太网的动态重构设计方案,该方案可以实现信号处理平台上多个FPGA和DSP动态更新,同时不需要以往方案中的配置存储器,配置时间短,能够满足多种场景下的应用需求。该方案已经在多个实际工程项目中验证,取得了理想的实验效果,具备非常高的移植性和扩展性。

**关键词:**动态重构;FPGA;DSP;以太网

中图分类号: TN791

文献标识码: A

DOI:10.16157/j.issn.0258-7998.200341

中文引用格式:王松明.基于以太网的信号处理平台动态重构设计[J].电子技术应用,2020,46(8):132-136.

英文引用格式:Wang Songming. Dynamic reconfiguration design of signal processing platform based on Ethernet[J]. Application of Electronic Technique, 2020, 46(8): 132-136.

## Dynamic reconfiguration design of signal processing platform based on Ethernet

Wang Songming

(Southwest China Institute of Electronic Technology, Chengdu 610036, China)

**Abstract:** The signal processing platform usually uses FPGA+DSP+ARM architecture to achieve specific signal processing functions, with the development of signal processing technology, more and more engineering applications require signal processing platform to have dynamic reconfiguration capacity. This paper introduced a design of dynamic reconfiguration based on Ethernet, which can realized the dynamic update of multiple FPGA and DSP on the signal processing platform. At the same time, it did not need the configuration memory in previous design, and the configuration time is short, which can meet the application requirements in various scenarios. The design has been verified in many practical projects, and has achieved ideal experimental results, with high portability and scalability.

**Key words:** dynamic reconfiguration; FPGA; DSP; Ethernet

## 0 引言

随着电子技术的发展,以“FPGA+DSP+嵌入式处理器”为核心的信号处理平台需要基于资源动态重组设计思想采用开放式、标准化的通用架构,按用户需求对平台进行资源重组,实现系统功能的可重构,以满足在设备资源有限情况下工作模式多样化、灵活配置的用户需求<sup>[1-3]</sup>。资源动态重组是指通过监控管理平台接口对所有信号处理平台进行统一管理,根据规划确定当前任务所需的设备和链路,配置相应的信号处理平台。这种方式要求信号处理平台之间通过高速总线进行数据交互,具备开放式的业务数据和监控数据传输特性。

针对FPGA和DSP动态重构,国内相关文献提出了多种解决方案,包括DSP EMIF总线<sup>[4]</sup>、CPCI总线<sup>[5]</sup>、RapidIO<sup>[6]</sup>、串口<sup>[7]</sup>等。这些方案在配置效率、设备成本、重构灵活性等方面都存在明显的不足。针对这一问题,考虑到平台本身就有接入以太网的需求以及嵌入式处理器和FPGA广泛共存于信号处理平台中<sup>[8-10]</sup>,本文提

出了基于以太网的信号处理平台动态重构设计方案。该方案利用信号处理平台功能单元在线可重构特性,在多任务协同监控管理平台实时调度下,通过以太网配合信号处理平台上的嵌入式处理器对FPGA和DSP实现任务功能和参数的动态重构,同时支持FPGA部分重构和全局重构,形成功能可定义的硬件板卡,在节省硬件资源和降低设备成本的基础上实现系统所需的硬件资源动态重组,并且可以通过资源动态备份实现信号处理系统的高可靠性。

## 1 资源可动态重构系统体系架构

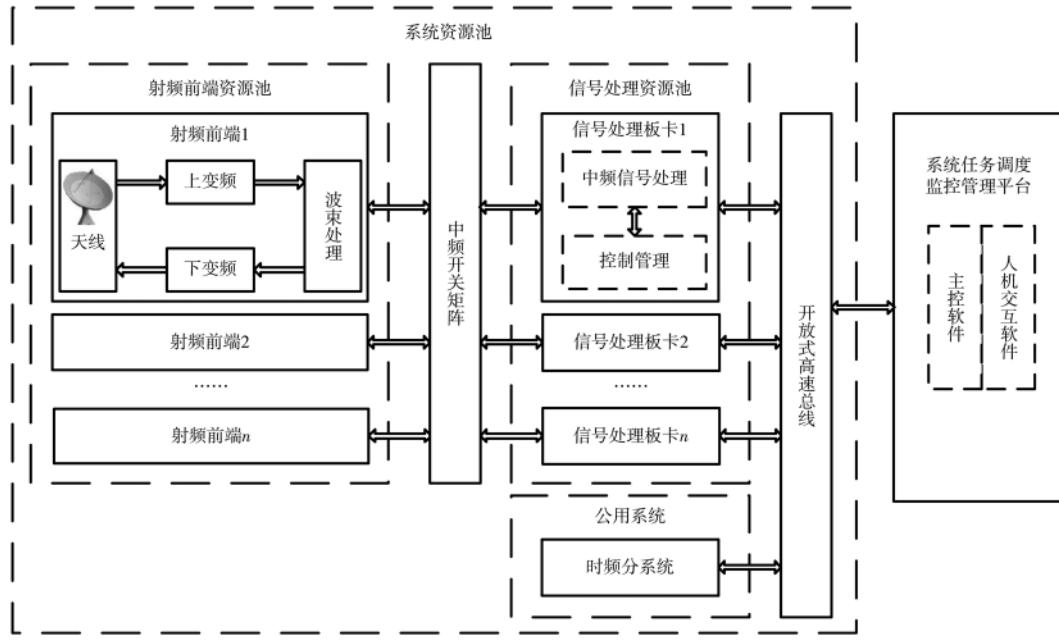

信号处理系统资源动态重组以通用数字化射频前端资源池和信号处理资源池为基础,以网络管理调度为支撑,对应的系统资源池架构如图1所示。所有资源以共享方式统一管理,用户根据不同任务的需求在监控管理平台进行资源调度和安全管理。

系统开机后,监控管理平台首先对资源池设备完整性进行检查,用户可通过人机交互界面查看设备状态信

图 1 资源可动态重构系统体系架构

息。系统完成自检功能后,用户通过人机交互界面向主控软件发起任务,主控软件根据任务需求和资源数量及状态在资源池中进行资源动态配置,未配置的资源可作为系统备份或者用于新任务功能加载。任务运行过程中主控软件实时监控各模块运行状态,模块故障时切换到备份模块运行,保证系统运行可靠性。

## 2 信号处理平台动态重构设计

### 2.1 信号处理板卡架构

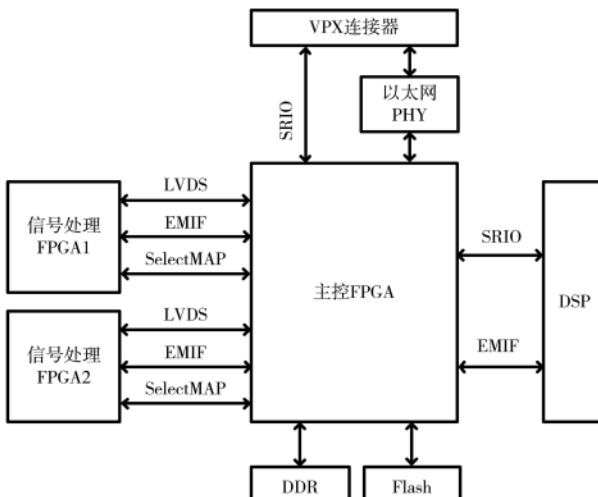

基于开放式高速总线 VPX 标准的通用信号处理板卡如图 2 所示,其中 FPGA1、FPGA2 实现数字上下变频及后续信号处理功能,DSP 完成滤波器参数计算、信号调制与解调等功能,DDR 用于存储程序运行过程中的数据、监控管理平台下发的指令等信息,Flash 用于存放主控 FPGA 的 Bootloader、处理器文件系统以及应用程序。主

控 FPGA 选择 Xilinx Zynq 系列 FPGA,它包含集成了以太网网口、DDR 控制器等外设的双核 ARM 处理器系统 (Processing System, PS) 和可编程逻辑 (Programmable Logic, PL),同时具备处理器软件可编程性和 FPGA 硬件可编程性的特点。

### 2.2 动态重构设计

#### 2.2.1 动态重构功能方案

主控 FPGA 是实现信号处理平台动态重构的核心,当系统需要重新加载或部分加载功能时,监控管理平台通过以太网先将配置数据发送到主控 FPGA,PS 接收配置数据缓存到 DDR 中并对数据进行校验。配置数据接收完成且校验无误之后,主控 FPGA 通知监控管理平台配置数据接收完成。监控管理平台接收到该信息后发送配置指令,主控 FPGA 从 DDR 中读取配置文件后加载到 FPGA 和 DSP 中,FPGA 和 DSP 执行新的配置程序,完成板卡动态重构。

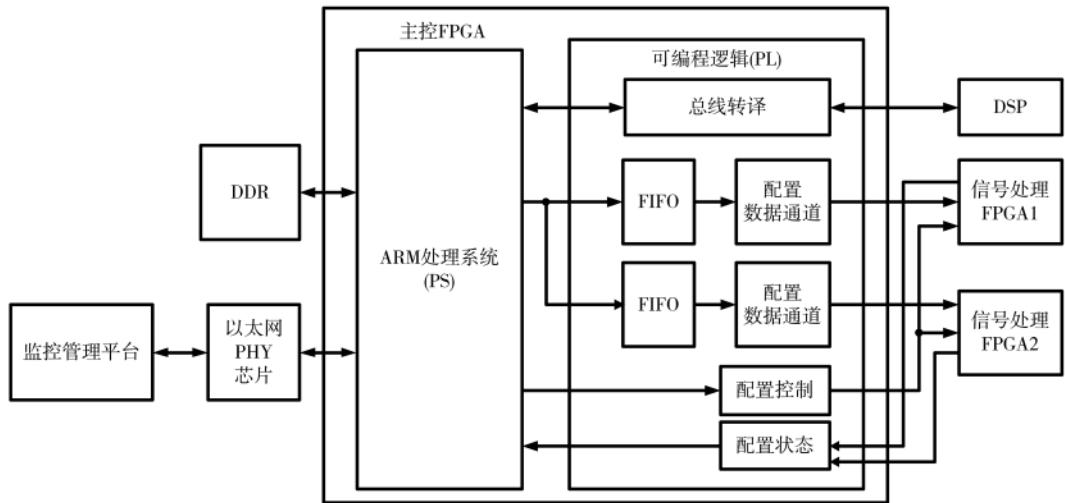

主控 FPGA 实现动态重构功能模块方案如图 3 所示,其中 PS 主要完成以太网协议处理,PL 设计包含 FPGA 动态配置逻辑、DSP EMIF 总线控制逻辑。FPGA 动态配置逻辑主要包括 FPGA 配置控制、被配置 FPGA 状态上报、FPGA 配置时序实现。

#### 2.2.2 PS 设计

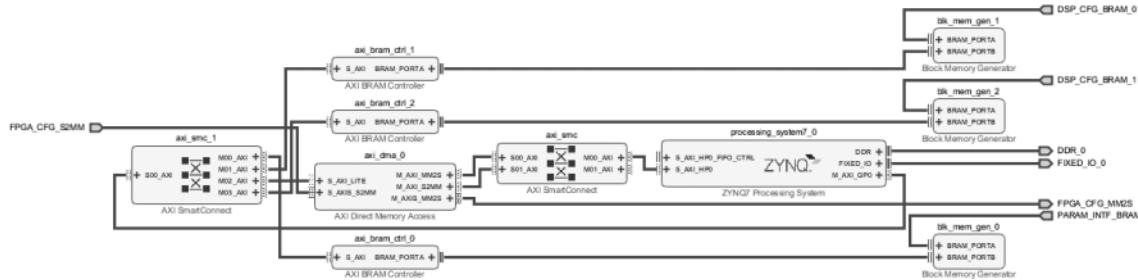

Xilinx 提供了嵌入式处理器系统级封装,在其开发工具 Vivado 中搭建基于以太网的信号处理平台动态重构 FPGA 工程 PS 部分设计如图 4 所示。PS 主要包含 1 个 ARM 处理器系统模块、1 个 AXI-DMA 模块、3 个 AXI BRAM Controller 模块、3 个双口 RAM 模块和 2 个 AXI SmartConnect 模块等,其中 AXI SmartConnect 模块实现一个或多个 AXI 主器件与一个或多个 AXI 从器件的高速

图 2 VPX 通用信号处理基带板卡

图 3 动态重构功能模块方案

图 4 动态重构 FPGA 工程 PS 部分设计

互联。

考虑 FPGA 全局重构文件往往比较大,在选择相应的 PS 与 PL 通信接口时选择具有最高数据吞吐率的 AXI-HP 接口,辅以 AXI-DMA 将 AXI 接口转换成逻辑设计相对更简单的 AXI-Stream 接口,并以中断的形式进行数据交互。FPGA 动态配置工作流程如下:

(1) 监控管理平台与主控 FPGA 建立 TCP/IP 连接,其中主控 FPGA 为 TCP Server,而监控管理系统为 TCP Client。监控管理平台发送配置文件到主控 FPGA,主控 FPGA 接收配置文件并存入 DDR 中。

(2) 主控 FPGA 中 PS 通过双口 RAM 通知 PL 开始进行 FPGA 配置并指明配置哪一个 FPGA,以及是全局重构还是部分重构。PL 接收到全局重构命令后复位 FPGA,待 FPGA 完成配置复位后状态机进入配置数据传输状态。若是部分重构则无需复位 FPGA,状态机直接进入配置数据传输状态。

(3) 主控 FPGA 中 PS 与 PL 建立 DMA 通道,PS 从 DDR 中读取相应的配置文件后将数据写入 PL 对应的 FIFO 中。

(4) PL 查询 FIFO 空满状态,FIFO 非空则读取数据并写到相应 FPGA 的配置接口。配置过程启动后,若 10 s 内没有配置数据传输且 FPGA 配置管脚 DONE 为低,PL 通过 GPIO 通知 PS 配置超时并退出配置过程。

(5) PL 将配置状态通过双口 RAM 实时通知 PS,监控管理平台可通过以太网读取配置状态,判断全局配置或者局部配置是否成功。

DSP 配置文件相对较小,使用具有中等吞吐率的 AXI-GP 接口。由于双口 RAM 不能直接挂在 AXI 总线上,借助 AXI BRAM Controller,PS 将数据写入双口 RAM 中,DSP 可以通过 EMIF 总线译码方式访问双口 RAM 读取数据从而实现 DSP 动态重构。

鉴于 PS MIO 资源有限,考虑后续设计需要,使用双口 RAM 实现 PS 与 PL 之间动态重构控制、动态重构状态、板卡健康管理、工作状态等信息交互。

### 2.2.3 PL FPGA 动态重构设计

FPGA 动态重构是指根据功能逻辑是否需要切换将 FPGA 区域划分成动态重构区和静态区,动态重构区的逻辑电路功能根据需要进行切换,而静态区逻辑电路功能一直保持不变。

动态重构技术在进行区域划分方案时,首先要根据 FPGA 的功能划分明确重构区域的数量和任务,分析各区域包括 Slice、RAM、时钟、DSP48、通信接口等在内的资源需求,明确各类资源的最大使用量限制和禁止使用的资源类型。然后,结合静态区的资源需求,进行 FPGA 芯片选型及分区规划,并明确各重构区域位置、大小等内容。根据应用的需求,合理制定部分重构区域与静态

# 嵌入式技术

## Embedded Technology

区间的通信接口,特别是时钟信号,由于各重构区域内使用的所有时钟须由静态区提供,前期要清楚当前部分重构区域内所有的时钟需求,保证供应给部分重构区域的时钟信号没有疏漏。

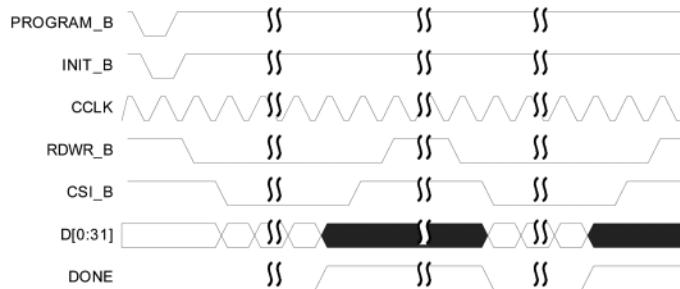

考虑到部分重构模式下配置接口只支持 JTAG、ICAP、Slave Serial、Slave SelectMap 和 BPI async mode 几种模式,其中 Slave SelectMap 是速度最快的配置方式,所以在本设计中选用 Slave SelectMap 来实现 FPGA 的动态配置。

动态重构时序如图 5 所示,上电之后必须先配置 FPGA 一个全局配置文件,完成之后被配置 FPGA 进入用户模式,此时才可以进行 FPGA 部分重构。部分重构过程中不需要复位被配置 FPGA(INIT\_B 信号保持高电平),只要向被配置 FPGA 传输部分重构文件即可。配置接口逻辑拉低 RDWR\_B 表示发起部分重构请求,片选信号 CSI\_B 与配置数据总线 D 对齐。数据传输开始后被配置 FPGA 拉低 DONE 信号表示进入部分重构状态。部分重构文件传输完成后,若校验正确,被配置 FPGA 拉高 DONE,表示部分重构成功。

图 5 Slave SelectMap 模式配置时序图

### 2.2.4 PL DSP 动态重构设计

DSP 加载选择 EMIF 总线引导模式,它从片外存储中读取一个字节到内部 RAM 首地址运行,执行完成之后读取下一个字节并覆盖上一个字节继续运行,以此类推,直到程序运行完成。

如图 4 所示,主控 FPGA 与 DSP 之间用两个双口 RAM 进行 Bootloader 和 DSP 用户程序的配置数据交互。PL 逻辑电路将 DSP EMIF 总线的数据、地址控制等信号映射到双口 RAM 上。主控 FPGA 写入部分配置数据后复位 DSP,DSP 复位完成后通过 EMIF CE3 地址空间访问双口 RAM,从中读取数据搬移到内部 RAM 中并执行。Bootloader 程序引导 DSP 读取其他程序数据并执行,DSP 完成配置过程。系统进行 DSP 动态加载时,只需通过以太网控制主控 FPGA 完成 DDR 中的 DSP 程序二进制文件更新以及 DSP 复位。

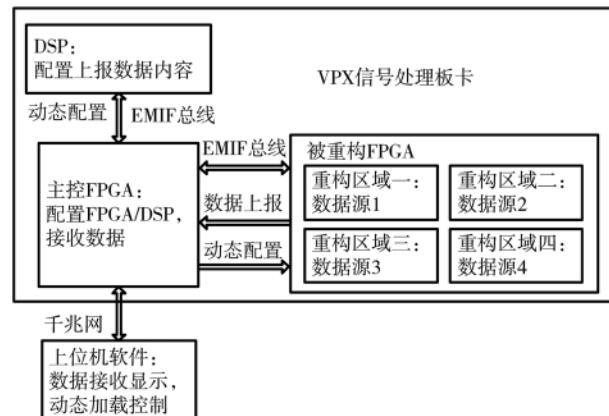

### 3 验证

本文设计了如图 6 所示的验证系统。在被配置 FPGA 中划分 4 个重构区域,4 个重构区域内分别设计一个模块上报数据包到主控 FPGA,数据包的内容由 DSP 通过 EMIF 总线配置。主控 FPGA 收到数据包后通过以太网

图 6 FPGA 动态重构验证方案

发送到工控计算机,工控计算机验证数据包与 DSP 配置的内容是否一致。

验证流程如下:

(1) 系统上电复位后,主控 FPGA 配置被重构 FPGA 全局重构文件,工控计算机通过网络查看配置是否成功并确认当前被重构 FPGA 无任何数据上报。

(2) 主控 FPGA 配置 4 个重构区域,此时由于尚未配置 DSP,故无数据上报。

(3) 主控 FPGA 配置 DSP,DSP 配置成功后被重构 FPGA 开始上报数据包到主控 FPGA,工控计算机可以通过网络查看数据包内容并确认数据包与 DSP 配置的内容是否一致。

(4) 主控 FPGA 可以卸载任意一个重构区域(配置无任何电路的局部重构文件),卸载成功后可通过工控计算机确认被卸载区域是否还有数据包上报。

(5) 遍历 4 个重构区域,卸载后再重新加载,重新加载成功后数据包继续上报,如此反复,确认局部重构配置效果。

验证结果如图 7 所示。同时为了验证本文方法的可行性和可靠性,进行了多次软件烧写实验,烧写过程全部成功,没有出现过错误。

### 4 结论

本系统基于 FPGA 部分重构技术和 DSP 加载技术,通过以太网传输不同的配置文件实现系统的动态重构。测试结果显示,单个器件配置时间不会超过 1 s,具体时间与配置文件大小相关。本设计已经成功应用于多个工程项目中,并取得了很好的效果,对于其他加载速度和实时性要求比较高的 FPGA+DSP 应用系统具有一定的参考价值。

### 参考文献

- [1] 李典,朱亮,汪远玲,等.基于嵌入式云平台的中继卫星系统地面终端站基带池设计技术[J].电讯技术,2019,59(1):13-18.

- [2] 周晖,黄英,吴海洲,等.统一测控系统新一代综合基带设计研究[J].雷达科学与技术,2018,16(1):87-92,98.

图 7 系统动态重构验证结果

- [3] 王彬, 刘友永. 微波统一测控系统的发展趋势及建议[J]. 无线电工程, 2017, 47(4): 44–48.

- [4] 赵秋明, 王龙飞, 肖丹, 等. 一种新型软件无线电重构加载方法研究[J]. 电视技术, 2013, 37(19): 87–90.

- [5] 熊璐. 基于 CPCI 的动态可重构系统设计与实现[J]. 现代电子技术, 2016, 39(8): 104–107.

- [6] 朱道山. 基于 RapidIO 的 FPGA 远程更新系统设计与实现[J]. 雷达科学与技术, 2017, 15(5): 543–547.

- [7] 张永乐, 王永勇, 郑炜. 一种基于 FPGA 的在线程序升级方案[J]. 电子技术应用, 2017, 43(3): 48–50, 54.

（上接第 131 页）

- 处理平台[J]. 单片机与嵌入式系统应用, 2016, 16(1): 44–47.

- [4] 康嘉, 程鹏, 杨坤, 等. FPGA 自动加载系统设计实现[J]. 现代电子技术, 2013, 36(24): 125–127.

- [5] 葛飞, 何辅云, 夏玉宝. FPGA 被动并行配置控制器的研究与实现[J]. 合肥工业大学学报(自然科学版), 2008(4): 531–533.

- [6] 管武, 王健, 秦霆镐, 等. 基于 ARM 的远程重构通信控制模块的设计[J]. 微计算机信息, 2009, 25(2): 1–3.

- [7] 张晖, 谢凯年. 一种 ARM+DSP 协作架构的 FPGA 验证实现[J]. 电子技术应用, 2007, 33(2): 116–117.

- [8] 朱道山. 基于 RapidIO 的 FPGA 远程更新系统设计与实现[J]. 雷达科学与技术, 2015, 13(5): 543–547.

- [8] 周晖, 黄英, 吴海洲, 等. 统一测控系统新一代综合基带设计研究[J]. 雷达科学与技术, 2018, 16(1): 87–92, 98.

- [9] 张晓明. 便携式数字阵列控制同步和链路测试系统实现[J]. 现代雷达, 2015, 37(4): 43–45.

- [10] 郑百衡, 朱慧惠, 刘盛利, 等. 新型多通道通用信号处理平台设计[J]. 电子技术应用, 2019, 45(10): 109–111.

(收稿日期: 2020-04-28)

#### 作者简介:

王松明(1986-), 男, 硕士, 工程师, 主要研究方向: 数字信号处理、微系统技术。

- [9] 陆佳华. 嵌入式系统软硬件协同设计实战指南: 基于 Xilinx Zynq[M]. 北京: 机械工业出版社, 2013.

- [10] 黄勇. 一种新型的 FPGA 快速动态配置和远程加载技术[J]. 通信技术, 2013, 46(12): 93–96.

- [11] 汪灏, 张学森. 一种基于串行方式的 FPGA 远程加载电路[J]. 电子科学技术, 2016, 3(2): 171–173.

(收稿日期: 2020-04-02)

#### 作者简介:

郝国锋(1984-), 男, 硕士研究生, 工程师, 主要研究方向: 软件无线电技术、可重构硬件。

朱琛(1988-), 男, 硕士研究生, 工程师, 主要研究方向: FPGA 逻辑设计。

顾晓雪(1981-), 女, 硕士研究生, 工程师, 主要研究方向: 数字电路设计、LabVIEW 自动测试系统设计。

## 版权声明

经作者授权，本论文版权和信息网络传播权归属于《电子技术应用》杂志，凡未经本刊书面同意任何机构、组织和个人不得擅自复印、汇编、翻译和进行信息网络传播。未经本刊书面同意，禁止一切互联网论文资源平台非法上传、收录本论文。

截至目前，本论文已经授权被中国期刊全文数据库（CNKI）、万方数据知识服务平台、中文科技期刊数据库（维普网）、DOAJ、美国《乌利希期刊指南》、JST 日本科技技术振兴机构数据库等数据库全文收录。

对于违反上述禁止行为并违法使用本论文的机构、组织和个人，本刊将采取一切必要法律行动来维护正当权益。

特此声明！

《电子技术应用》编辑部

中国电子信息产业集团有限公司第六研究所