# 一种低成本 VPX 背板总线测试设备

马力科

(中国电子科技集团公司第十研究所, 四川 成都 610036)

**摘要:** 分析了常见高速串行总线测试方案的优缺点, 针对 VPX 高速背板结构和信号定义特征, 提出了一种低成本的 VPX 背板高速串行总线的测试方法。该方法以 FPGA 为运算核心, 通过巧妙的结构设计和高速串行电路设计, 实现了单次同时测试最多 16 对高速收发通道, 且可进行高速串行总线从物理层、链路层到协议层的信号误码率测试和眼图测试, 每通道测试速率可大于 10 Gb/s。

**关键词:** VPX 背板; 高速串行总线; 信号完整性; 误码率

中图分类号: TN802; TN98

文献标识码: A

DOI: 10.16157/j.issn.0258-7998.200063

中文引用格式: 马力科. 一种低成本 VPX 背板总线测试设备[J]. 电子技术应用, 2020, 46(10): 69–72, 78.

英文引用格式: Ma Like. A low cost test equipment for high speed bus on VPX backplane[J]. Application of Electronic Technique, 2020, 46(10): 69–72, 78.

## A low cost test equipment for high speed bus on VPX backplane

Ma Like

(China Electronics Technology Group Corporation No.10 Research Institute, Chengdu 610036, China)

**Abstract:** The advantages and disadvantages of common high-speed serial bus test schemes are analyzed. Aiming at the characteristics of VPX high-speed backplane structure and signal definition, a low-cost VPX backplane high-speed serial bus test method is proposed. It takes FPGA as the operation core, with ingenious structure design and high-speed serial circuit design, it can test up to 16 pairs of high-speed transceiver channels each time, and can test the signal error rate and eye chart of high-speed serial bus from physical layer, link layer to protocol layer, and the test rate of each channel can be greater than 10 Gb/s.

**Key words:** VPX backplane; high-speed bus; signal integrity; signal error rate

### 0 引言

随着高速数据总线在嵌入式信号处理领域的广泛使用, 嵌入式系统历经了从并行总线 PCI、CPCI、VME、VXS, 到高速串行总线 CPCIE、VPX 的演进。特别是自 2006 年 VITA46 系列 VPX 基本标准规范发布以来, VITA 组织此后又陆续发布了 VITA48 REDI 加固增强机械设计规范, 对 VPX 结构加固和散热进行了规范, 解决了由于模块性能提高带来的功耗增加问题并提供了相应的风冷和加固导冷措施; 而 VITA65 OpenVPX 规范进一步对 VPX 的机械尺寸、供电方式、散热方式和通信协议进行了规定, 并补充了背板、模块等的标准架构, 真正成为了一种具有开放式架构的信号处理平台。最新的 VPX 规范已更新至 VITA65.1<sup>[1]</sup>。

VPX 由于其平台灵活性、更高的传输带宽和灵活的交换能力, 得到了广泛的推广, 而 VPX 之所以具有如此强大的通信带宽和交换能力, 其核心在于其采用了高速串行数据总线。高速串行总线以低压差分信号传输, 可通过单线 1x 或多线 2x、4x、8x、16x 等方式传输, 且单

线传输速率可覆盖 1.25 Gb/s~12.5 Gb/s 以上<sup>[2]</sup>。当数据信号传输速率达到 Gb/s 数量级以上后, 高速信号完整性设计就是不可忽略的了, 而如何对高速机箱背板的信号完整性进行测试验证, 将是决定系统和设备是否可以可靠使用的关键<sup>[3]</sup>。

针对这一问题, 传统的信号完整性测试方法, 需要若干台价格昂贵的仪器设备测试, 价格超过百万元, 还只能每次测试一对信号线, 测试效率低。本文针对 VPX 高速背板的特征, 提出了一种低成本的 VPX 背板高速串行总线测试方法, 可方便地一次性对多根高速信号线进行物理层、链路层、协议层测试, 更加贴近实际使用环境, 既灵活又节约了成本。

### 1 传统基于仪器的测试方法

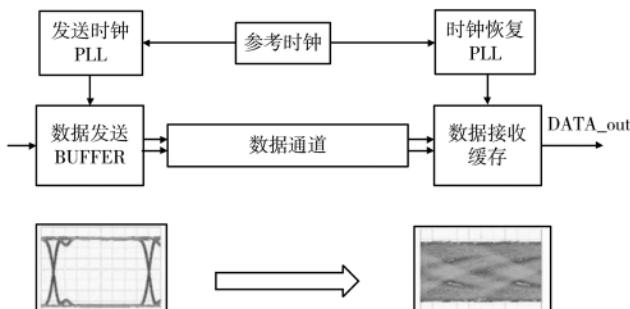

针对高速背板的信号完整性设计, 传统方法使用 ADS 对 PCB 投板前进行设计仿真, 到 PCB 加工完成后且元器件转配之前, 通过 TDR 阻抗测试仪对印制板线路阻抗进行测试, 再到完成电装后, 通过信号源仪器注入数据、高速示波器抓取信号, 并生成眼图测试的全套标准

# 测控技术与仪器仪表 Measurement Control Technology and Instruments

测试流程<sup>[4]</sup>,如图1所示。

图1 典型高速互联系统

以安捷伦提供的高速信号完整性测试方案为例,为了测试一套高速背板信号完整性,需要配备的仪器包括:

(1)DSO90000A 高速示波器,提供 2.5 Gb/s~13 Gb/s 带宽,采样速率 40 GSa/s,眼图测试;

(2)物理层测试系统,测试 TDT、眼图仿真、S 参数模型和时序 RLGC 模型提取;

(3)N4903A J-BERT 误码仪,接收与误码率测试;

(4)协议测试仪,对 PCIE、SRIO 抓包,对协议测试。

这套测试仪器的高速总线测试方法优点在于可以覆盖仿真、测试验证各个方面,可从阻抗一致性、电路传导和反射、信号传输眼图等各个方面对信号完整性进行全面评估。而其缺点在于:

(1)测试验证设备价格超过百万元,价格不菲;

(2)如果对背板上每一对信号线进行测试,测试工作量特别大,最终往往也只能选择抽样测试,测试覆盖率不高;

(3)各种仪器测试和整机使用插入模块后的条件并不一致,单纯测试背板对于从整机上的使用的参考意义有限。

## 2 硬件和软件设计

为了更加直观地对高速背板进行测试,同时更加接近于实际使用情况,本文设计了一款针对 VPX 背板总线测试设备,核心是由两块高速串行总线测试卡组成。

高速串行总线测试卡设计原则包括:

(1)从结构尺寸上考虑,VPX 高速信号线可能存在于机箱任意槽位从 J1~J6 的各个连接器,需保证插槽都可插入该总线测试卡且插拔稳定<sup>[5]</sup>。

(2)从接口电平协议上考虑,VPX 高速背板需兼容包括 AURORA、PCIe、SRIO、JESD204B、万兆网等各种高速串行总线协议<sup>[6~7]</sup>。

(3)从总线链路上考虑,VPX 高速背板需兼容 1x、2x、4x 等多种链路数。

(4)从传输速率上考虑,VPX 高速背板需兼容 1.25 Gb/s、2.5 Gb/s、3.125 Gb/s、5 Gb/s、6.25 Gb/s、8 Gb/s、10.312 5 Gb/s 等多种速率。

根据 VITA65 OpenVPX 规范,当任意一个 J 端连接器选用差分连接器时,规定了 a、b、c、d 行为差分信号接收输入行,e、f、g、h 列为差分信号发射输出列。且一个 J 连接器对应了 4 个 4x 收信号、4 个 4x 发信号,也可以理解为 16 对 1x 收信号、16 对 1x 发信号。只要用户连接器定义按照 VPX 规范定义,就可以使用该设备进行测试。

### 2.1 结构设计

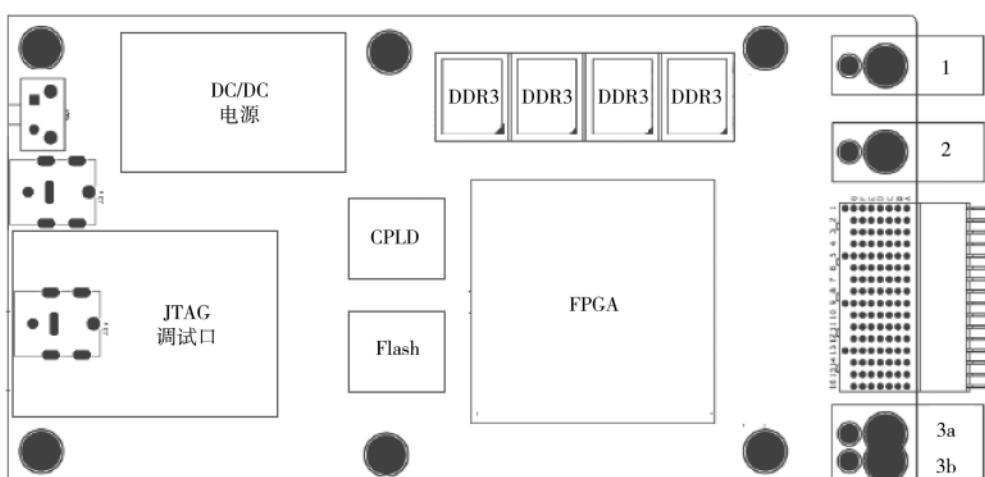

为了高速串行总线测试卡能插入机箱所有槽位从 J1 到 J6 所有连接器,板卡结构外框设计需要限制。

高速串行总线测试卡采用外部供电,而不通过背板 P0 连接器供电,故在背板端只设计一个高速差分连接器。当该差分连接器作为 P1 使用时,这是结构设计以定位销 1 为定位点,同时确定板卡的上板边 X 的位置;当该差分连接器作为 P2 使用时,以定位销 3 靠近差分连接器侧(标注为 3a)为定位点;当该差分连接器作为 P3 时,以定位销 2 为定位点;当差分连接器作为 P4、P5 时,无定位点;当差分连接器作为 P6 时,以定位销 3 远离差分连接器侧(标注为 3b)为定位点,同时确定板卡的下板边 Y 的位置。

按照以上要求进行结构板框设计,高速串行总线测试卡即可插入任意槽位从 J1~J6 的所有连接器。

高速串行总线测试卡设计示意图如图 2 所示。

图2 高速串行总线测试卡设计示意图

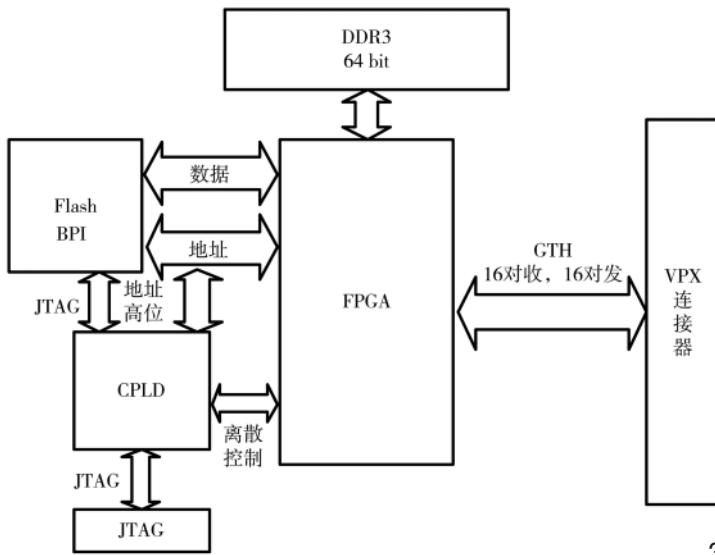

### 2.2 电路设计

高速串行总线测试卡以 FPGA 为处理核心,选用 Xilinx 公司的 Virtex-7 系列 XC7VX690T -2FFG1158。它具有 48 个高速 GTH 接口,最高速率到 10.312 5 Gb/s。选用 2 Gb 容量并行 Flash,用于 FPGA 多版本程序存储。

# 测控技术与仪器仪表

## Measurement Control Technology and Instruments

CPLD 配合完成并行 Flash 高位地址位选择，实现多版本动态可切换。测试结果通过 JTAG 上传到计算机。JTAG 模组选择 Digilent 公司提供的 JTAG-SMT2-NC，不用外接 FPGA 下载电缆，板上通过具有 Type-C 接口的 USB 电缆连接到控制计算机。

高速总线测试卡电路设计框图如图 3 所示。

图 3 电路设计框图

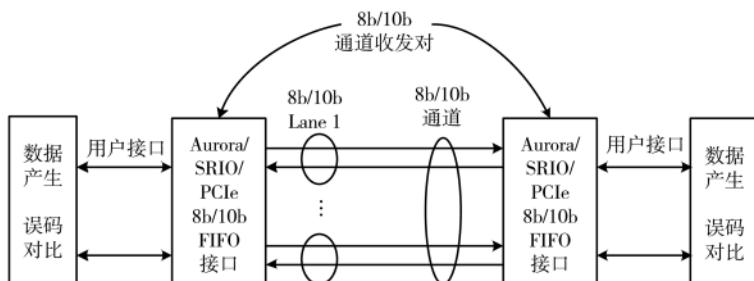

### 2.3 测试软件设计

为了实现从物理层、链路层到协议层的 3 层信号完整性测试，本文考虑在软件上使用 Xilinx 公司提供的 IBERT 高速信号测试 IP 核，对高速信号链路的物理特性和链路特性进行测试，通过 IBERT 图形化界面观察特定链路在特定速率下的数据通信的锁定情况、传输误码率情况。

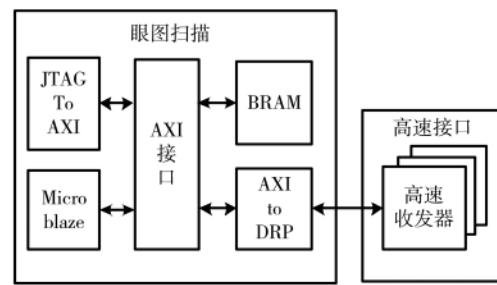

常见的高速串行总线还有 Aurora、SRIO、PCIe 等，利用 Xilinx 提供的 IP 核，产生符合相应协议的测试程序，并通过 Vivado 集成到开发环境中，观察在特定协议、特定传输速率下，通信状态、误码率统计及在线眼图测试，如图 4 所示。

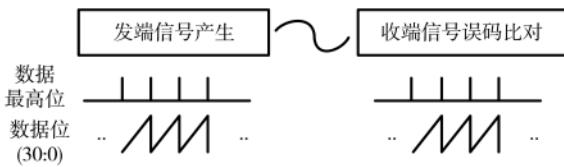

在数据源端，产生 32 位顺序数，并通过高速串行接口 IP 核，将数据送入数据 FIFO，在接收端恢复数据序列，将后一个数和前一个数相减，结果始终为 1，则证明数据无乱序，无错位，数据传输正确，如图 5 所示。

图 4 带协议的高速总线测试框图

图 5 使用顺序数对传输误码率统计

收发两侧都运行同样的 FPGA 程序，可实现收发双向误码率测试。

Vivado 工具提供在线眼图测试方法，在 FPGA 中通过 Microblaze 实现。其实现原理框图如图 6 所示。

图 6 在线眼图测试原理框图

### 3 测试结果

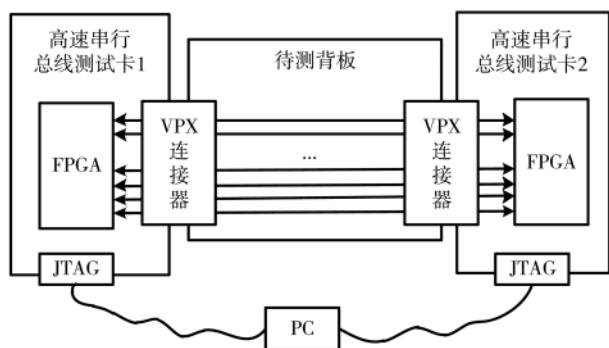

为实现对 VPX 背板的高速串行总线测试，需要配置两块高速串行总线测试卡和两台测试计算机。

首先，根据 VPX 背板接口定义，确定待测高速总线的走向；然后分别将两块高速串行总线测试卡插入对应的两个槽位的被测高速总线的连接器，并确保完全插入。将 USB 连接到测试计算机并开始测试，通过 Xilinx 配套 ChipScope 或 Vivado 软件对两个板卡上通信情况进行监控，如图 7 所示。

图 7 背板测试图

(1) 通过 IBERT 工具，测试背板在 10 Gb/s 条件下的误码率情况，如图 8 所示。可见在高速数据传输速率为 10 Gb/s 情况下，测试数据总数超过 1012，测试误码率为 0。

(2) 使用 Aurora 协议进行传输，在 8x 情况下，传输速率为 10 Gb/s。在高速总线发射端，产生 32 位的顺序数，在接收端恢复并进行误码统计。测

# 测控技术与仪器仪表 Measurement Control Technology and Instruments

| Name            | TX           | RX           | Status      | Bits     | Errors | BER       |

|-----------------|--------------|--------------|-------------|----------|--------|-----------|

| Ungrouped L...  |              |              |             |          |        |           |

| Found Links ... |              |              |             |          |        |           |

| Found 0         | MGT_X0Y12/TX | MGT_X1Y16/RX | 10.000 Gbps | 1.52E12  | 0E0    | 6.577E-13 |

| Found 1         | MGT_X0Y13/TX | MGT_X1Y17/RX | 10.000 Gbps | 1.521E12 | 0E0    | 6.573E-13 |

| Found 2         | MGT_X0Y14/TX | MGT_X1Y18/RX | 10.000 Gbps | 1.522E12 | 0E0    | 6.572E-13 |

| Found 3         | MGT_X0Y15/TX | MGT_X1Y19/RX | 10.000 Gbps | 1.523E12 | 0E0    | 6.568E-13 |

| Found 4         | MGT_X0Y8/TX  | MGT_X1Y20/RX | 10.000 Gbps | 1.523E12 | 0E0    | 6.566E-13 |

| Found 5         | MGT_X0Y9/TX  | MGT_X1Y21/RX | 10.000 Gbps | 1.524E12 | 0E0    | 6.562E-13 |

| Found 6         | MGT_X0Y10/TX | MGT_X1Y22/RX | 10.000 Gbps | 1.524E12 | 0E0    | 6.562E-13 |

| Found 7         | MGT_X0Y11/TX | MGT_X1Y23/RX | 10.000 Gbps | 1.524E12 | 0E0    | 6.561E-13 |

| Found 8         | MGT_X0Y4/TX  | MGT_X1Y24/RX | 10.000 Gbps | 1.525E12 | 0E0    | 6.557E-13 |

| Found 9         | MGT_X0Y5/TX  | MGT_X1Y25/RX | 10.000 Gbps | 1.525E12 | 0E0    | 6.556E-13 |

| Found 10        | MGT_X0Y6/TX  | MGT_X1Y26/RX | 10.000 Gbps | 1.525E12 | 0E0    | 6.555E-13 |

| Found 11        | MGT_X0Y7/TX  | MGT_X1Y27/RX | 10.000 Gbps | 1.513E12 | 0E0    | 6.609E-13 |

| Found 12        | MGT_X1Y24/TX | MGT_X0Y4/RX  | 10.000 Gbps | 1.525E12 | 0E0    | 6.558E-13 |

| Found 13        | MGT_X1Y25/TX | MGT_X0Y5/RX  | 10.000 Gbps | 1.525E12 | 0E0    | 6.557E-13 |

| Found 14        | MGT_X1Y26/TX | MGT_X0Y6/RX  | 10.000 Gbps | 1.525E12 | 0E0    | 6.556E-13 |

| Found 15        | MGT_X1Y27/TX | MGT_X0Y7/RX  | 10.000 Gbps | 1.526E12 | 0E0    | 6.555E-13 |

图 8 IBERT 测试结果

试时间 5 min, 误码统计数为 0, 无误码。

(3) 使用 SRIO 协议进行传输, 在 4x 情况下, 传输速率为 6.25 Gb/s。在高速总线发射端, 产生 32 位的顺序数, 在接收端恢复并进行误码统计。测试时间 5 min, 误码统计数为 0, 无误码。

(4) 使用 PCIe 协议进行传输, 在 8x 情况下, 传输速率为 8 Gb/s。在高速总线发射端, 产生 32 位的顺序数, 在接收端恢复并进行误码统计。测试时间 5 min, 误码统计数为 0, 无误码。

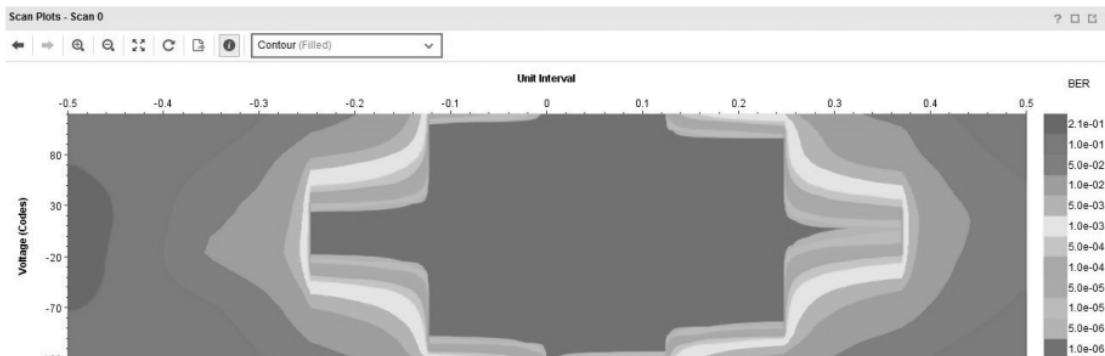

(5) 进行在线眼图测试, 如图 9 所示。高速信号传输的眼宽、眼高均满足 10 Gb/s 高速数据传输要求。

综上所述, 被测背板满足 10 Gb/s 高速数据传输要求, 高速背板总线测试设备也可满足测试需要。

## 4 结论

本文提出的低成本 VPX 背板总线测试设备采用两块以 V7 系列 FPGA 为核心的高速串行总线测试卡, 配合两台测试计算机实现。与传统基于仪器的测试系统相比, 结果如表 1 所示。

本测试设备组成简单, 设计成本不超过 5 万元。测试卡结构设计巧妙, 能插入 VPX 背板每个槽位的从 J1~J6 的所有连接器, 完全能满足在 VPX 系统下所有高速串行总线的测试需求。此外, 还可以实现对 Aurora、SRIO、PCIe 等多种协议的高速总线测试, 使得测试更贴近于用户实际使用。

## 参考文献

- [1] VITA Standard Organization. ANSI/VITA 65.1—2019 Open-VPX profile tables[S].2019.

- [2] 王剑宇.高速电路设计实现[M].北京:电子工业出版社, 2010.

- [3] JOHNSON H, GRAHAM M.High speed digital design:a handbook of black magic[M].Scitech Publishing, 1993.

- [4] 曹劲.RapidIO 背板信号完整性测试方法[J].电讯技术, 2011, 51(1): 18–22.

- [5] 包利民, 潘奇.VPX 总线技术及其实现[J].电子机械工程, 2012, 28(2): 57–60.

- [6] 李敏, 徐建成, 李键.基于 RocktIO 接口的高速互联应用研究与实现[J].现代电子技术, 2012, 35(6): 11–14.

- [7] 邓豹, 段小虎.基于 VPX 标准的高速处理模块的设计与

图 9 眼图测试结果

表 1 传统测试手段和本测试设备比较

| 项目       | 基于仪器的测试方案                  | 本测试设备                                       |

|----------|----------------------------|---------------------------------------------|

| 组成       | 高速示波器、物理测试仪器、高速误码仪、协议测试仪器等 | 两块高速串行总线测试卡、两台计算机                           |

| 价格       | 上百万元                       | 不高于 5 万元                                    |

| 测试覆盖     | 可测试 VPX 从 J1~J6 所有高速信号     | 可测试 VPX 从 J1~J6 所有高速信号                      |

| 每次测试链路对数 | 一次只能测试一对收发                 | 一次最多测试 16 对收发                               |

| 测试依据     | S 参数、阻抗、眼图误码率等             | 物理层、链路层误码统计、带 Aurora/SRIO/PCIe 等协议误码统计、眼图统计 |

| 是否贴近用户实际 | 否                          | 是                                           |

(下转第 78 页)

- specifications[S].2012.

- [2] ECMA International.Standard ECMA-398 , close proximity electric induction wireless communications[S].2011 .

- [3] 吴湛击.无线通信新协议与新算法[M].北京 : 电子工业出版社 , 2013 .

- [4] 陈磊 , 谈振辉.基于优先级和休眠机制的无线体域网 MAC 协议的能效优化[D].北京 : 北京交通大学 , 2014 .

- [5] SARANG S , DRIEBERG M , AWANG A.Muti-priority based QoS MAC protocol for wireless sensor network[C].2017 IEEE International Conference on System Engineering and Technology , Shah Alam , Malaysia , 2017 .

- [6] IEEE Standards Association.IEEE 802.15.6.wireless body area network[S].2012 .

- [7] KIM B S , Fang Yuguang , WONG T F.Rate-adaptive MAC protocol in high-rate personal area networks[C].2004 IEEE Wireless Communications and Networking Conference.Atlanta ,

(上接第 60 页)

**参考文献**

- [1] 何嘉辉 , 周鹏 , 余晖俊 , 等.电磁驱动大尺寸 MEMS 扫描镜的研究[J].光子学报 , 2017 , 46(1) : 21-28 .

- [2] 胡宗恺 , 饶志宏.高精度数字鉴相技术的 FPGA 实现[J].通信技术 , 2010 , 43(12) : 177-179 .

- [3] 许文浩 , 屈乐乐 , 殷文浩.基于 FPGA 和 DDS 的频率步进信号源的设计与实现[J].数字技术与应用 , 2017(1) : 147 .

- [4] Gu Dawei , Yao Yao , Zhang Dengming , et al.Matlab/Simulink based modeling and simulation of fuzzy PI control for PMSM[J].

(上接第 63 页)

工艺设备可以选择以反射功率或者直流偏压值作为控制目标 , 进行射频功率匹配调节。虽然负载形式和结构不同 , 但自动匹配原理相似。

**6 结论**

通过研究和试验 , 采用本文介绍的射频匹配分析方法 , 对相关电路的设计改进 , 可以为射频功率匹配设计提供指导 , 对设备工艺参数的确定提供较大帮助。

在设备老化 , 工作状态发生变化 , 或者工艺条件比较极端的情况下 , 通过增减旁路电容、补偿电感方法扩大设备匹配能力 , 可以提高设备工艺适用性。

通过给不同工艺预置匹配电容位置 , 可以提高阻抗匹配速度、精度和稳定性 , 降低反射功率 , 提高生产效率 , 有利于提高产品的工艺性能和质量。

(上接第 72 页)

实现[J].航空计算基数 , 2013 , 43(4) : 113-121 .

(收稿日期 : 2020-02-02)

GA , USA.2004 .

- [8] MathWorks.State flow user's guide[Z].MATLAB & Simulink . R2013a , 2013 .

- [9] 夏宇闻 , 韩彬.Verilog 数字系统设计教程[M].北京 : 北京航空航天大学出版社 , 2017 .

- [10] 丁彬勇 , 黄鲁 , 白雪飞.脉冲超宽带通信系统基带单元设计与芯片实现[D].合肥 : 中国科学技术大学 , 2012 .

- [11] 米联电子科技有限公司.XILINX ZYNQ 以太网通篇—— 基于 MZ7X 系列开发板[Z].2018 .

(收稿日期 : 2020-03-03)

**作者简介 :**

汪健(1995-), 男 , 硕士 , 主要研究方向 : 无线通信 MAC 层的设计与实现。

林敏(1974-), 通信作者 , 男 , 博士 , 教授 , 主要研究方向 : 无线通信芯片设计、微电子与固体电子学等 , E-mail : mlin99@shu.edu.cn 。

Procedia Computer Science , 2020 : 166 .

- [5] 陈媛媛 , 刘有耀.FIR 滤波器的 FPGA 设计与实现[J].电子设计工程 , 2017 , 25(24) : 65-69 , 73 .

- [6] 安书董 , 李明 , 王宛人 , 等.基于 FPGA 的低抖动时钟锁相环设计方法[J].航空计算技术 , 2017 , 47(6) : 109-111 .

(收稿日期 : 2020-05-11)

**作者简介 :**

董淑豪(1993-), 男 , 硕士研究生 , 主要研究方向 : MEMS 驱动电路。

吴东岷(1973-), 通信作者 , 男 , 博士 , 研究员 , 主要研究方向 : MEMS 光学成像系统等 , E-mail : dmwu2008@sinano.ac.cn 。

**参考文献**

- [1] 张志.射频电源自动阻抗匹配器的开发和实验研究[D].沈阳 : 东北大学 , 2008 .

- [2] 卢慧.射频阻抗自动匹配方法的研究与实现[D].郑州 : 郑州大学 , 2017 .

- [3] 郑珍 , 王海 , 周渭 , 等.AD8302 型相位差测量系统的设计[J].电子科技 , 2005(11) : 48-52 .

(收稿日期 : 2020-05-31)

**作者简介 :**

赵英伟(1971-), 男 , 工程硕士 , 高级工程师 , 主要研究方向 : 半导体工艺设备。

张文雅(1982-), 男 , 本科 , 高级工程师 , 主要研究方向 : 半导体工艺设备。

郝晓亮(1979-), 男 , 本科 , 高级工程师 , 主要研究方向 : 半导体工艺设备。

**作者简介 :**

马力科(1982-), 通信作者 , 男 , 硕士 , 高级工程师 , 主要研究方向 : 信号处理平台及嵌入式系统开发 , E-mail : medona\_cn@163.com 。

## 版权声明

经作者授权，本论文版权和信息网络传播权归属于《电子技术应用》杂志，凡未经本刊书面同意任何机构、组织和个人不得擅自复印、汇编、翻译和进行信息网络传播。未经本刊书面同意，禁止一切互联网论文资源平台非法上传、收录本论文。

截至目前，本论文已经授权被中国期刊全文数据库（CNKI）、万方数据知识服务平台、中文科技期刊数据库（维普网）、DOAJ、美国《乌利希期刊指南》、JST 日本科技技术振兴机构数据库等数据库全文收录。

对于违反上述禁止行为并违法使用本论文的机构、组织和个人，本刊将采取一切必要法律行动来维护正当权益。

特此声明！

《电子技术应用》编辑部

中国电子信息产业集团有限公司第六研究所