# 低电压差分信号长线传输的优化设计

陈晓敏<sup>1</sup>,薛志超<sup>2</sup>,张志龙<sup>2</sup>,文 丰<sup>1</sup>,袁小康<sup>1</sup>

(1.中北大学 电子测试技术国家重点实验室,山西 太原 030051;

2.中国运载火箭技术研究院空间物理重点实验室,北京 100076)

**摘要:**针对影响信号完整性的噪声与衰减进行分析与验证,硬件物理层采取预加重与均衡处理技术、同时进行阻抗匹配优化并设计双重电气隔离,提升信号传输质量。软件链路层进行两级乒乓形式缓存设计以优化传输效率;改进基于 CRC 校验的反馈重传机制,保证系统实现数据检错重传功能,能适应更多链路异常情况。经验证,优化后在传输长度为 100 m 时系统可满足 180 Mb/s 的高可靠传输,满足工程应用技术要求。

**关键词:**低电压差分信号;信号完整性;预加重;乒乓操作;反馈重传机制

中图分类号: TN914

文献标识码: A

DOI:10.16157/j.issn.0258-7998.200521

中文引用格式: 陈晓敏, 薛志超, 张志龙, 等. 低电压差分信号长线传输的优化设计 [J]. 电子技术应用, 2020, 46(11): 104–108.

英文引用格式: Chen Xiaomin, Xue Zhichao, Zhang Zhilong, et al. Optimal design of long-line transmission with low voltage differential signal[J]. Application of Electronic Technique, 2020, 46(11): 104–108.

## Optimal design of long-line transmission with low voltage differential signal

Chen Xiaomin<sup>1</sup>, Xue Zhichao<sup>2</sup>, Zhang Zhilong<sup>2</sup>, Weng Feng<sup>1</sup>, Yuan Xiaokang<sup>1</sup>

(1.National Key Laboratory for Electronic Measurement Technology , North University of China , Taiyuan 030051 , China ;

2.Key Laboratory of Space Physics, China Academy of Launch Vehicle Technology , Beijing 100076 , China)

**Abstract:** The noise and attenuation that affect the signal integrity are analyzed and verified. The hardware physical layer adopts pre-emphasis and equalization processing technology. The impedance matching optimization and double electrical isolation are designed to improve the signal transmission quality. At the software link layer, a two-level ping-pong buffer is designed to optimize transmission efficiency. The feedback retransmission mechanism based on cyclic redundancy check is improved to ensure that the system realizes the function of data error detection and retransmission, and can adapt to more abnormal link conditions. It has been verified that when the optimized transmission length is 100 m, the system can achieve a high reliable transmission of 180 Mb/s, which meets the technical requirements of engineering applications.

**Key words:** low voltage differential signal; signal integrity; pre-emphasis; ping-pong; feedback retransmission mechanism

## 0 引言

在实际工程试验环境中,飞行器的多种传感器及图像数据需要通过穿舱差分电缆传输至地面测控台<sup>[1]</sup>,因此对于数据在穿舱差分电缆中的传输长度、可靠性有很高要求。基于以上应用场合,对低电压差分信号传输链路硬件物理层与软件链路层分别做优化设计,所有设计模块及信息处理均在 FPGA 平台上实现,FPGA 在单时钟周期可执行多个任务,与单片机相比 FPGA 对数据响应与处理速度更快,在高速数据处理方面有很大优势<sup>[2]</sup>。

## 1 系统总体概述

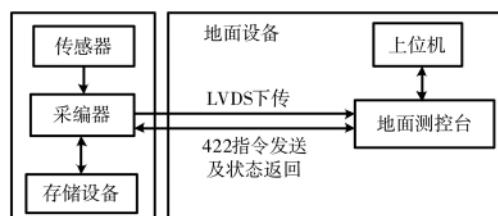

高速数据传输系统主要由采编器、地面测控台以及传输设备三部分构成。传输介质采用全信的 QX2539 双绞屏蔽电缆,以 20 m 为最小单元,通过多级电连接器连接。地面设备与采编器通过 RS-422 双向链路和 LVDS

单向链路实现指令发送、状态接收及数据下载功能, LVDS 下行链路用于实时数据监测和存储器数据事后下载。图 1 所示为系统原理图。

图 1 系统原理框图

## 2 信号完整性分析

### 2.1 噪声耦合

噪声常以耦合方式对电路产生干扰,有电容耦合、

感应耦合等。在选择传输介质时放弃使用同轴线缆,转而采用屏蔽双绞线,尽可能降低外界对系统的串扰影响,因为双绞线物理结构使两根单线与地端阻抗、与干扰源端耦合电容基本一致,由此在传输线上产生同等的共模干扰,差分传输可有效抑制共模干扰<sup>[3]</sup>。同时双绞线扭转结构形成多个相等间距的小“环路”,在磁场环境中互感电动势在相邻的“环路”方向相反,互感电动势一正一负相互抵消,有效消除感应耦合<sup>[4]</sup>。

## 2.2 传输衰减

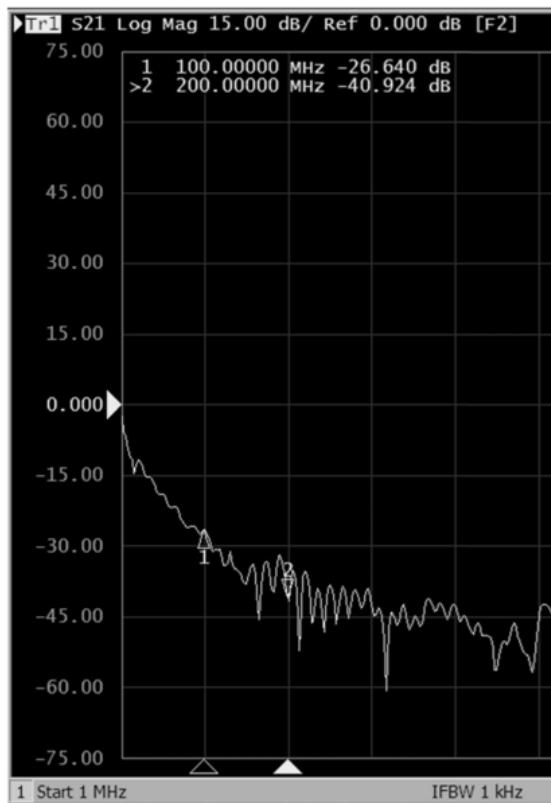

双绞屏蔽电缆可抑制串扰,是长线传输系统较为理想的传输线,但双绞线本质上是有损传输线<sup>[5]</sup>,设计所用全信 QX2539 电缆,特性阻抗为  $100 \Omega$ ,衰减特性为  $29.7 \text{ dB}/100\text{m}@100\text{MHz}$ ,利用 E5061B 网络分析仪进行实际测量,在 100 MHz 情况下 100 m 电缆衰减为 26.64 dB,如图 2 所示。

图 2 全信电缆 100 m 衰减曲线

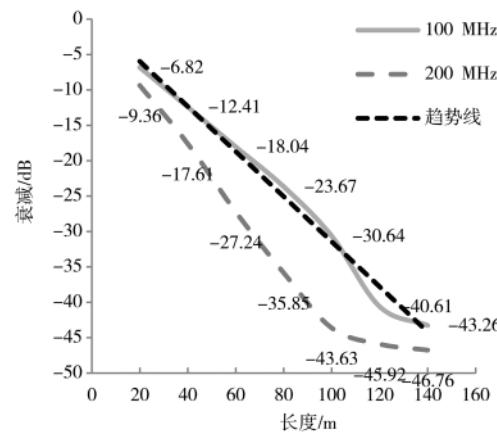

引起信号衰减的一个主要因素是电缆长度,但衰减不仅与距离有关,由于信道阻抗的存在,随着传输频率的增加,信号高频分量衰减加大,且不恰当的端接也会引起过量的衰减<sup>[6]</sup>,此处需通过测试来验证 J14H 连接器对组合电缆的影响。在 100 MHz 和 200 MHz 码率下,运用网络分析仪测试不同组合长度电缆的衰减,绘制衰减曲线,如图 3 所示。已知双绞线的传输损耗和信号码率的二次方根与传输距离的乘积为正比关系<sup>[7]</sup>,根据图中衰减曲线可以看出,当码率固定,在百米以内传输损耗与电缆长度基本为正比关系,说明 J14H 连接器的使用对组合电缆中信号衰减的影响微乎其微,可不做考虑。

图 3 电缆衰减曲线

## 3 硬件电路优化

### 3.1 电路总体设计

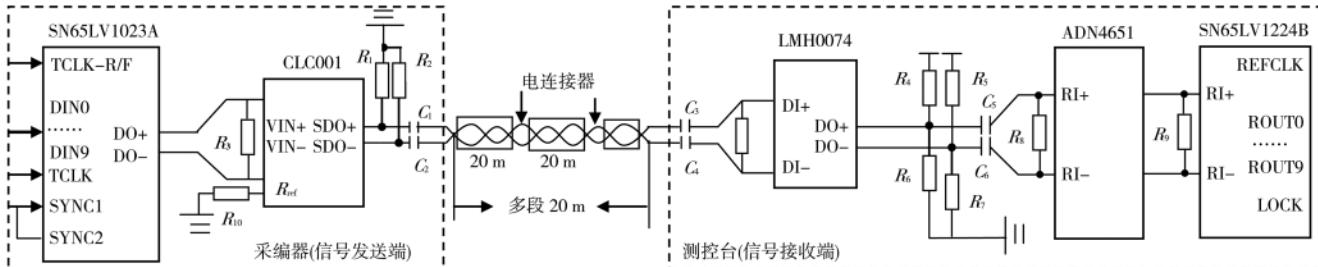

LVDS 信号传输满足数百兆比特每秒传输速率要求<sup>[8]</sup>,以系统码率 180 Mb/s 为前提,选用 TI 公司研发的串行解串器组合 SN65LV1023 和 SN65LV1224 芯片来搭建电路,工作频率在 100 Mb/s~660 Mb/s 之间,SN65LV1023A 可以将 10 位并行 TTL 数据信号和 1 位 TTL 时钟信号转化为一对 LVDS 串行差分信号,SN65LV1224B 解串器利用数据与时钟恢复技术,将串行输入的高速 LVDS 信号解码。图 4 为传输电路总体设计,信号发送端由串行器与驱动器构成,接收端的三个功能芯片依次为均衡器、隔离缓冲器与解串器,由  $C_3$ 、 $C_4$  和  $C_5$ 、 $C_6$  隔直电容隔离开,如图 4 所示。

图 4 LVDS 传输链路总体设计

# 嵌入式技术

## Embedded Technology

此处选用较大容值电容(设计中选用的容值为 4.7  $\mu$ F)可保证信号的损失较小。

### 3.2 阻抗匹配优化

采用源端端接与终端端接匹配阻抗以削弱信号反射造成的影响,已知双绞线特性阻抗 100  $\Omega$ ,当电阻  $R_3$  作为终端匹配电阻,且取值 100  $\Omega$  时,串行数据经由串化器 D0+、D0-引脚输出的信号幅值在电缆驱动器“接收窗口”范围内。 $R_1$ 、 $R_2$ 、 $C_1$ 、 $C_2$  构成 RC 交流耦合负载匹配,有效抑制输出互补信号直流工作点的漂移。电阻  $R_8$  和  $R_9$  并联在信号接收端差分线之间实现源端电阻匹配<sup>[9]</sup>,在 PCB 布板时尽可能地靠近差分输入管脚,减少传导耦合干扰。ADN4651 低压差分信号缓冲器实现 LVDS 传输通道任意位置的插入式隔离,同时缓冲器内部 LVDS 接收端包含故障安全机制,当输入悬空、短路或未驱动时,保证驱动器输出端在逻辑“1”状态,实现电路双重保护<sup>[10]</sup>。

### 3.3 预加重与均衡技术

信号预加重通常有时域与频域两种方法实现,时域预加重技术是将发送信号幅度增大,频域预加重技术则是通过增加高通滤波器以提升信号高频分量的能量来实现<sup>[11]</sup>。优化过程考虑到频域预加重技术在增强信号高频分量的同时也会增强高频噪声,会造成信号发送时近端交互噪声恶化的严重后果,因此选用时域预加重技术。

预加重芯片选用串行电缆驱动器 CLC001,最大输出差分电压 1 000 mV;均衡器 LMH0074 可自动均衡不同传输长度的双绞线,在 125 Mb/s~540 Mb/s 码率范围内可恢复频率为 200 MHz、衰减为 40 B 的信号。全信电缆在 100 MHz 情况下,百米衰减为 29.7 dB(小于 40 dB),因此从理论设计上该电路可以满足 100 m 传输距离时 180 Mb/s(90 MHz)码率的可靠传输。

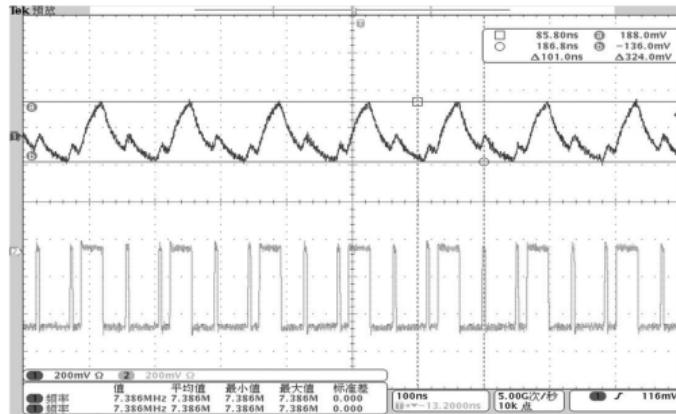

经过百米双绞线传输后信号幅值衰减严重,此时高电平区分不明显,若直接利用 SN65LV1224B 解串会有误码产生。但信号经过自适应均衡器后,恢复了衰减、畸变信号,可明显判断信号处于高电平或低电平,保证解串器顺利完成信号串转并操作。均衡器输入端和输出端波形图对比如图 5 所示。

### 4 软件逻辑优化

通过上述详细措施对低电压差分信号硬件电路做优化后,系统可基本实现指标要求,但恶劣环境、传输速率快以及噪声干扰等因素使得系统容易出现误码或丢数情况,因此嵌入式软件优化不可或缺。

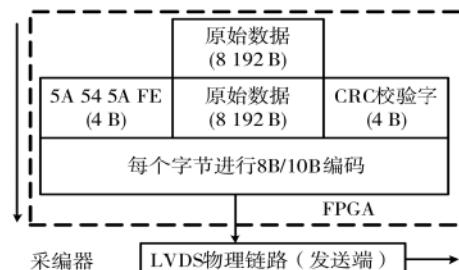

#### 4.1 软件逻辑设计

数据发送端的协议设计分层示意图如图 6 所示,接收端执行相反的过程。有效数据进入采编器 FPGA 后,增加 4 B 包头,并对 8 KB 有效数据进行 CRC 运算,产生的 4 B 校验字续写至数据之后,形成 8 200 B 的数

图 5 均衡器输入端和输出端波形图对比

图 6 收发端协议示意图

据包,对每个字节进行 8 B/10 B 编码保证信号直流平衡<sup>[12]</sup>,并通过 LVDS 物理链路发送出去。对于接收端,首先对每个字节进行 8 B/10 B 解码,重新计算数据区 8 KB 字节的 CRC 校验字,然后执行基于 CRC 校验的反馈重传机制。

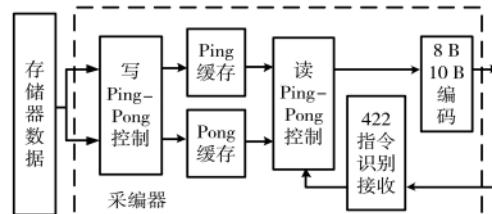

#### 4.2 两级乒乓操作优化设计

软件逻辑设计中通常采用单流水线型结构,以确保各数据包传输互不影响,但总会有部分模块处于空闲状态<sup>[13]</sup>,因此在软件逻辑设计时,发送端与接收端的读、写缓存方式均采用乒乓操作,以提高传输效率。图 7 所示为采编器内部两级 Ping-Pong 操作。采编器主控模块以 8 KB 为一个写入单元用乒乓操作方式将存储数据写入 Ping 缓存、Pong 缓存,发送时也以乒乓形式读取数据发送。假设当前发送的第  $n$  包有效数据来自 Ping 缓存,在发送完第  $n$  包后紧接着发送第  $n+1$  包,即 Pong 缓存中的数据,此时 Ping 缓存中数据存留,预防需要重传情况。

图 7 采编器内部两级 Ping-Pong 操作

利用上位机实时检测传输信息,误码率明显降低,但当链路出现异常时,仍存在小概率的丢包现象。

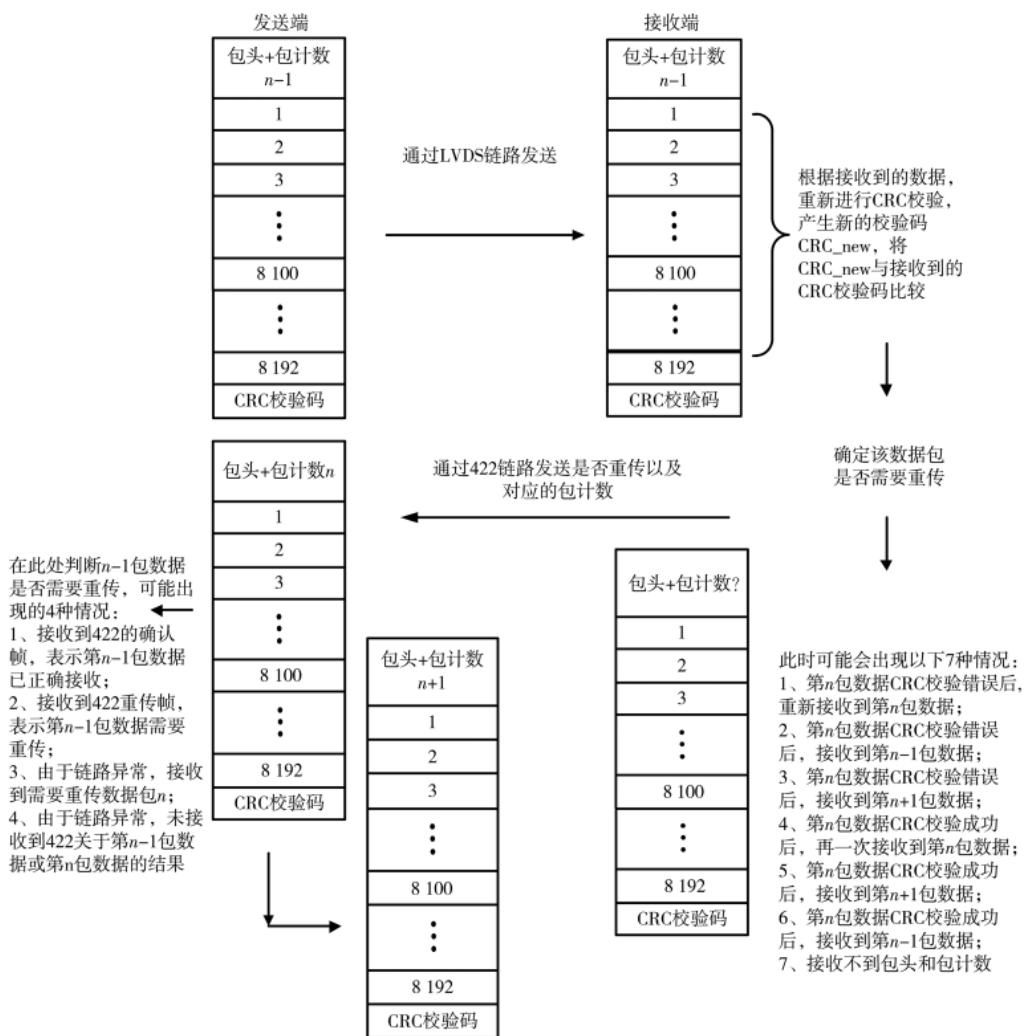

#### 4.3 反馈重传优化

为满足更高可靠性,收发双方添加明确的握手机制。在LVDS传输链路软件协议中增加数据包计数,将4字节帧头优化为“0x5A 0x54 0x5A 0xFX”,其中“0xX”表示包计数,取值范围为0~15,测控台发送的RS-422确认帧或重传帧中也添加包计数,发送过程如图8所示。

发送端依次发送数据包 $n-1, n, n+1$ ,当发送完第 $n$ 包数据的8100个有效数据时,采编器读取接收端发送过来的指令,可能出现图中4种情况,对应解决的软件逻辑如下:若指令内容是关于数据包 $n-1$ ,则RS-422链路无误,采编器可判断指令内容并执行对应传输;若指令内容是关于数据包 $n$ (由于数据包 $n+1$ 还未发送,因此不可能接收到 $n+1$ 数据包的相关信息),表示第 $n-1$ 包数据接收端已正确接收,重新发送当前数据包 $n$ ;若未接收到关于第 $n-1$ 或 $n$ 包数据的指令,此时认为数

据包 $n-1$ 接收端可能未正常接收,因此重新发送数据包 $n-1$ 。

接收端先确认数据包头和包计数正确后,开始接收8KB有效数据,并进行CRC校验,接收端可能出现如图8中所示7种具体情况,对应解决的软件逻辑如下:若第 $n$ 包数据校验错误后,重新接收到第 $n$ 包数据说明传输正常,当接收到第 $n-1$ 包数据时,需再发送数据包 $n-1$ 确认帧,当接收到第 $n+1$ 时,需重新发送数据包 $n$ 重传帧;若第 $n$ 包数据校验正确后,接收到第 $n+1$ 包数据说明传输正常,当再次接收到第 $n-1$ 或 $n$ 包数据时,需再发送数据包 $n$ 确认帧;若接收不到任何包头和包计数,则发送当前准备接收数据包的包计数和重传帧。

采编器与测控台之间有了握手,通过包计数来完成数据对齐处理,避免了丢包现象发生,同时测控台FPGA软件会将采编器错误识别422指令计数、测控台重新发送422指令计数、重传次数等返回给上位机,方便判断链路质量情况。

图8 发送端与接收端的交互过程示意图

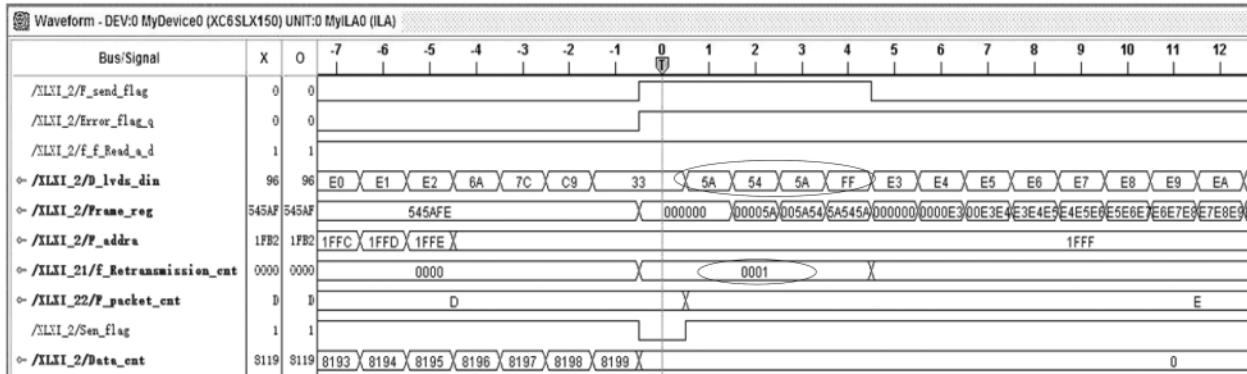

图 9 实时抓取仿真图

## 5 可靠性验证与分析

利用测控台、采编器和数据存储设备,结合100 m 电缆搭建闭环系统,同时利用高低温箱模拟恶劣温度环境进行测试。为验证反馈重传功能,上位机产生递增数作为存储设备有效数据,并控制低电压差分信号通信开始,在传输过程中采用 ISE 仿真工具实时抓取关于 LVDS 接收端主控制模块关于帧标志 Frame\_reg、错误重传标志 Error\_flag\_q、重传计数 Retransmission\_cnt 等信号,如图 9 所示。当 Error\_flag\_q 为上升沿时启动反馈重传,Retransmission\_cnt 重传计数自加,此时帧头为“0x5A 0x54 0x5A 0xFF”,即重传包计数为“0xF”,有效数据为递增数据,实现反馈重传功能。

软件发送端设置不同速率进行多次试验,误码率情况如表 1 所示,从表中可以看出,随着传输速率增大,误码率也增大,在 CRC 校验机制更新后,虽占用一定传输带宽,但大大提高传输可靠性,当传输速率达到 300 Mb/s 时,由于反馈重传次数增多,实际传输速率会降低。

表 1 误码率测试情况

| 理论值/<br>(Mb/s) | CRC 校验前         |                       | CRC 校验后         |                       |

|----------------|-----------------|-----------------------|-----------------|-----------------------|

|                | 传输速率/<br>(Mb/s) | 误码率/%                 | 传输速率/<br>(Mb/s) | 误码率/%                 |

| 120            | 119.99          | 0                     | 119.98          | 0                     |

| 180            | 179.98          | $2.51 \times 10^{-6}$ | 179.97          | 0                     |

| 240            | 239.56          | $4.73 \times 10^{-6}$ | 239.39          | $1.62 \times 10^{-6}$ |

| 300            | 298.53          | $7.28 \times 10^{-6}$ | 297.74          | $4.59 \times 10^{-6}$ |

## 6 结论

通过软硬件优化相结合,有效地解决了低电压差分信号传输短板,幅值预加重措施提升传输质量,两级乒乓操作提升传输效率,反馈重传机制的改进保证了可靠性,使系统可适应更多链路异常情况。

## 参考文献

- [1] 张宇.基于 FPGA 的光电转换式高速长距离可靠传输技术的研究与实现[D].太原:中北大学,2019.

- [2] 许艳,孟令军.基于 STM32+FPGA 的存储控制系统优化

设计[J].兵器装备工程学报,2019,40(10):142-145,160.

- [3] 雷武伟,文丰,刘东海,等.基于 LVDS 的高可靠性远距离数据传输设计[J].电子技术应用,2019,45(6):130-134.

- [4] 鲁伟.微弱信号远距离传输特性分析与应用[D].合肥:合肥工业大学,2019.

- [5] 方炜,任勇峰,储成群,等.低电压差分信号远距离通信电缆参数估计[J].科学技术与工程,2018,18(19):209-212.

- [6] 冯锦亭.高速数据传输板卡设计及关键技术研究[D].长春:吉林大学,2017.

- [7] 濮建福,赖晓敏,田文波,等.高速串行传输系统信号幅值衰减研究[J].上海航天,2016,33(2):82-86.

- [8] 李北国,杨圣龙,李辉景.基于 FPGA 的 LVDS 高可靠性传输优化设计[J].电子技术应用,2018,44(8):78-81,85.

- [9] 张波,李杰,张海鹏,等.基于 FPGA 的 LVDS 传输链路的可靠性设计[J].电子器件,2018,41(5):1237-1241.

- [10] BRAND THOMAS.电流隔离 LVDS 接口[J].电子产品世界,2019,26(2):20-21,26.

- [11] 张晓雷,贾晓晓,赵冬青,等.基于 CPCI 总线通用测试设备设计[J].仪表技术与传感器,2020(3):26-30.

- [12] 何基,蒲杰,孙伟,等.JESD204B 中的 8B/10B 编码器设计[J].电子世界,2019(2):110-112.

- [13] 文丰,张宇,吴瑞华.基于 4 bit-CRC 反馈网络的高速 LVDS 传输优化设计[J].兵器装备工程学报,2019,40(9):108-113.

(收稿日期:2020-06-17)

## 作者简介:

陈晓敏(1995-),女,硕士研究生,主要研究方向:电路与系统设计、测试测量技术及仪器。

文丰(1977-),通信作者,男,教授,主要研究方向:微系统集成技术、传感器测量技术研究,E-mail:nucwenfeng@163.com。

## 版权声明

经作者授权，本论文版权和信息网络传播权归属于《电子技术应用》杂志，凡未经本刊书面同意任何机构、组织和个人不得擅自复印、汇编、翻译和进行信息网络传播。未经本刊书面同意，禁止一切互联网论文资源平台非法上传、收录本论文。

截至目前，本论文已经授权被中国期刊全文数据库（CNKI）、万方数据知识服务平台、中文科技期刊数据库（维普网）、DOAJ、美国《乌利希期刊指南》、JST 日本科技技术振兴机构数据库等数据库全文收录。

对于违反上述禁止行为并违法使用本论文的机构、组织和个人，本刊将采取一切必要法律行动来维护正当权益。

特此声明！

《电子技术应用》编辑部

中国电子信息产业集团有限公司第六研究所