# 一种新型的采用电流转向电荷泵的快速锁定小数分频锁相环

区健川<sup>1</sup>,蔡良伟<sup>1</sup>,徐渊<sup>2</sup>,陈享<sup>1</sup>,廖嘉雯<sup>1</sup>

(1.深圳大学 电子与信息工程学院,广东 深圳 518600;2.深圳技术大学 大数据与互联网学院,广东 深圳 518600)

**摘要:** 基于SMIC 0.13 μm 工艺设计了一款工作电压为1.5 V 的模拟整数分频锁相环(Phase Locked Loop, PLL), 提出了一种能有效解决电荷分流、提高开关速度的新型电流转向电荷泵, 同时基于环形差分反相器设计了具有低相位噪声特点的压控振荡器。在整数分频锁相环基础上, 加入MASH3 结构的数字Σ-Δ 调制器(Delta Sigma Modulation, DSM) 实现了一种数模混合的快速锁定小数分频锁相环, 能在输入参考频率为26 MHz 下输出频率范围0.8 GHz~2.0 GHz, 具有低噪声、低频率步进和快速锁定等优点。

**关键词:** 锁相环; 小数分频; DSM; 快速锁定

中图分类号: TN911.8; TN431.1

文献标识码: A

DOI: 10.16157/j.issn.0258-7998.200525

中文引用格式: 区健川,蔡良伟,徐渊,等. 一种新型的采用电流转向电荷泵的快速锁定小数分频锁相环[J]. 电子技术应用, 2020, 46(12): 61–66.

英文引用格式: Ou Jianchuan, Cai Liangwei, Xu Yuan, et al. A new fast-locking fractional frequency division phase-locked loop using current steering charge pump[J]. Application of Electronic Technique, 2020, 46(12): 61–66.

## A new fast-locking fractional frequency division phase-locked loop using current steering charge pump

Ou Jianchuan<sup>1</sup>, Cai Liangwei<sup>1</sup>, Xu Yuan<sup>2</sup>, Chen Xiang<sup>1</sup>, Liao Jiawen<sup>1</sup>

(1. College of Electronics and Information Engineering, Shenzhen University, Shenzhen 518600, China;

2. College of Big Data and Internet, Shenzhen Technology University, Shenzhen 518600, China)

**Abstract:** Based on the SMIC 0.13 μm process, an analog integer frequency PLL with 1.5 V working voltage is designed, and a new type of current steering charge pump that can effectively solve the charge shunt and improve the switching speed is proposed. At the same time, a voltage controlled oscillator with low phase noise is designed based on the ring differential inverter. On the basis of the integer frequency-division PLL, the digital DSM with MASH3 structure is added to realize a digital-analog mixed fast-locked decimal frequency-division phase-locked loop, which can be the output frequency range from 0.8 GHz to 2.0 GHz at 26 MHz, and has the advantages of low noise, low frequency stepping, and fast lock.

**Key words:** phase locked loop; fractional-n; Delta Sigma modulation; fast locking

## 0 引言

在窄带物联网(Narrow Band Internet of Things, NB-IoT) 的片上系统(System on Chip, SoC) 中, 需要实现数字基带电路和射频(Radio Frequency, RF) 电路的集成, 而PLL 作为时钟恢复电路、频率合成器、相位偏移减小电路的重要部分也被广泛集成于SoC 中。对于NB-IoT 收发机模块中, 接收机需要本地频率源振荡频率与发射机载波频率之间的高度同步, 所以时钟模块中PLL 对相位噪声和锁定时间有严格的要求, 以符合NB-IoT 通信要求。目前对于NB-IoT 的PLL 主要研究方向是实现快速锁定和低相位噪声的频率输出, 而且有较小的可调输出频率步进和低电压工作以满足功耗要求<sup>[1]</sup>。

在文献[2]中, 为加快锁定时间设计了一种特性结构

的电荷泵。当锁相环开始跟踪频率和相位时, 这种电荷泵输出时的电流和锁相环带宽会相对减少, 以加快锁定时间, 但并没有进行对压控振荡器(Voltage Controlled Oscillator, VCO) 优化。对于设计低相位噪声的PLL 来看, 优化VCO 是必不可少的, 在文献[3]中, 设计了用于锁相环的电流饥饿型COMS VCO, 从而大大降低输出噪声, 能有效提高锁相环的稳定性。

对于小数分频部分, 文献[4]中通过对比四种传统的DSM(MASH3、MASH4、SLDSM4、SLDSM5), 从相位噪声、分数阶激励和设计复杂性的综合评估中, 得出最适合本设计需求的是MASH3 结构。

本文针对PLL 在RF 电路中低噪声和快速锁定等应用, 提出了一款电流转向电荷泵技术实现快速锁定锁相

环的方法。同时参考了文献[5]的 VCO 结构,增加输出缓存单元以获得更低的相位噪声。在整数分频的基础上,又加入了 MASH3 结构的数字 DSM 模块,使锁相环实现了小数分频的功能。

在 NB-IoT 芯片的收发机中,锁相环除了提供基带的工作频率外,还要为发射机和接收机提供符合 NB-IoT 通信要求的 890 MHz~1 780 MHz 的本振频率。本文所设计的锁相环能在工作电压 1.5 V 和参考频率 26 MHz 下,输出频率范围 0.8 GHz~2.0 GHz,频率步进为 396 Hz,并且具有低噪声( $-78 \text{ dBc}/\text{Hz}$ @1MHz)和快速锁定时间(少于 2.0  $\mu\text{s}$ )的优点。

### 1 锁相环电路架构设计和基本原理

#### 1.1 架构设计

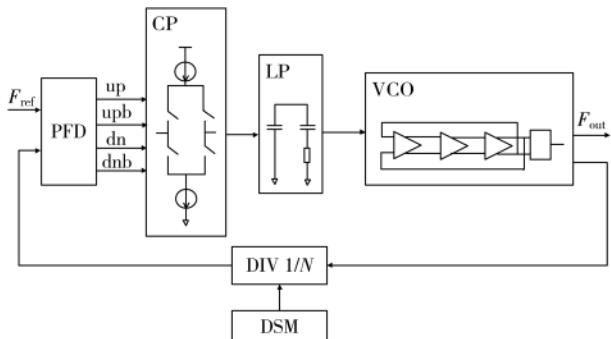

锁相环是一种利用相位同步产生的电压,去调谐压控振荡器以产生目标频率的负反馈控制系统,本锁相环的整体架构如图 1 所示。

图 1 锁相环整体框架图

本 PLL 是由鉴频鉴相器、电荷泵、环路滤波器、压控振荡器和分频器组成的负反馈控制电路,实现输出信号频率  $F_{out}$  对输入信号频率  $F_{ref}$  的自动跟踪。鉴频鉴相器的功能是通过比较分频器输出频率相位  $\theta_{div}$  和参考频率相位  $\theta_{ref}$  的频率差和相位差,并转化为电压信号  $V_c$ ,  $V_c$  在环路滤波器后,控制着 VCO 输出高频信号。

#### 1.2 电流转向电荷泵

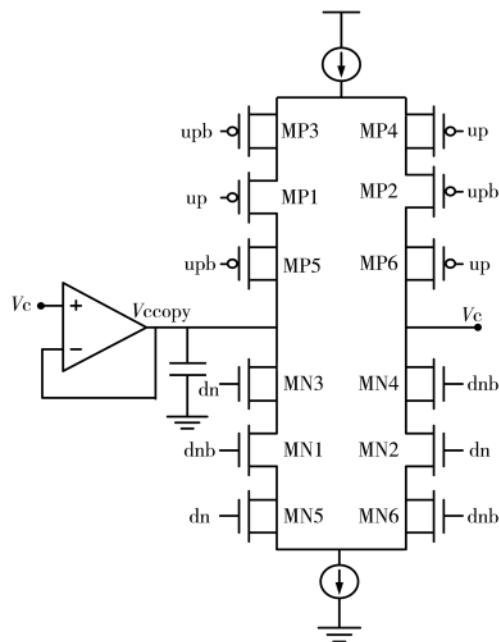

图 2 是本文所使用基于漏极开关电流源结构的电流转向电荷泵。这种电荷泵能有效解决电荷分流、提高开关速度,并且几乎是所有电荷泵结构中速度最快的一种。同时由于电荷泵所流入电源的电流和地的电流能够不断保持稳定,因此该结构的电荷泵的电源串扰也是较少的<sup>[6]</sup>。

在原来只有单路的漏极开关电荷泵电路( $upb$ ,  $V_c$ ,  $dn$ )中,通过加上一个单位增益缓冲器(U1)和以相反信号控制开关组成另外一路镜像电路( $up$ ,  $Vccopy$ ,  $dn$ ),构成了本文的电流转向电荷泵。单位增益缓冲器 U1 的作用是使其输出  $Vccopy$  不断地跟踪电荷泵的压控电压  $V_c$  的电位输出,所以在镜像两端的 MOS 管控制开关无论是闭合还是打开,PMOS 与 NMOS 管的两电流源漏极始

图 2 电流转向电荷泵

终通过一组开关与输出端  $V_c$  或单位增益缓冲器的输出端  $Vccopy$  连通,因而电流源能维持开启状态。在需要电流源对输出端充电或者放电时电流源电流就不用从 0 mV 开始增加到指定值,而是直接以指定的电流值工作。因此能极大地提高这种电荷泵的开启和关闭的速度,当然这种结构设计的代价是会有静态电流产生,也相应增加功耗。

MOS 器件在 MOS 管断开与开的瞬间,会因为沟道电荷注入而导致产生电压误差。例如当 MOS 管断开后,沟道电荷  $Q_{ch}$  会通过源和漏端流出,这种现象称为沟道电荷注入。

为了减轻沟道电荷注入效应对电路精度的影响,抵消电荷注入,增加了如图 2 所示源漏短接的 MOS 管(MP3、MP4、MP5、MP6、MN3、MN4、MP5、MP6)虚拟开关。由于分别由两反相时钟控制,当 MP2 断开后,MP4、MP6 立即导通。由于沉积在 MP2 管上的沟道电荷可以被 MP4、MP6 吸收,保证了控制电压  $V_c$  的稳定性和精准性。

#### 1.3 压控振荡器

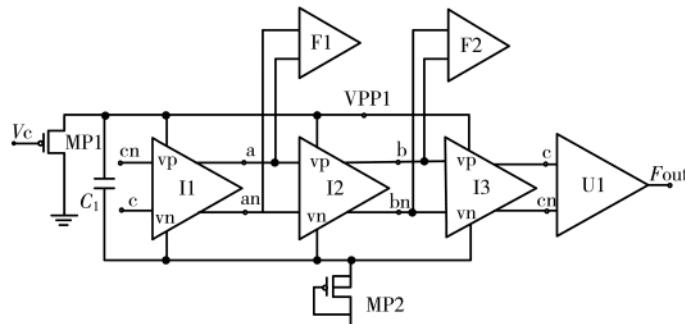

本文使用的压控振荡器是一种基于差分反相器单元的环形振荡器,对于 LC 振荡器,环形振荡器不需要电感,所以占用面积小和集成度高,此外频率的调节范围较大。如图 3 所示,本 VCO 电路由差分反相器单元 I、负载匹配单元 F 和输出缓冲单元 U 组成。

本压控环形振荡器包含三个差分反相单元,由于第三个反相器单元 I3 连接到了一个差分输出缓存器 U1,因此增加了 F1、F2 负载匹配单元以平衡输出负载。在本 VCO 的设计中,通过增加负载单元 F1 和输出缓存单元,能有效降低 VCO 的相位噪声。

图 3 压控环形振荡器

由于环形振荡器输出的是两路差分输出的模拟振荡信号,且输出波形振幅会随输出频率的增加而衰减,因此需要把这对差分模拟信号转化为单端数字方波信号。

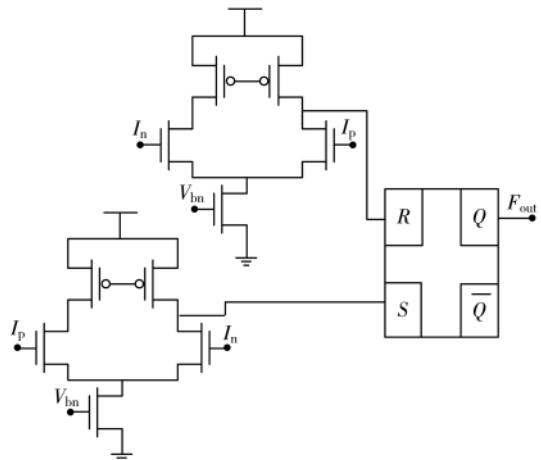

图 4 是由两个差分运算放大器和一个 RS 寄存器组成的输出缓存单元。通过设计这样的输出缓存单元能有效将模拟信号转换成占空比 50% 和振幅 1.5 V 的标准数字方波。

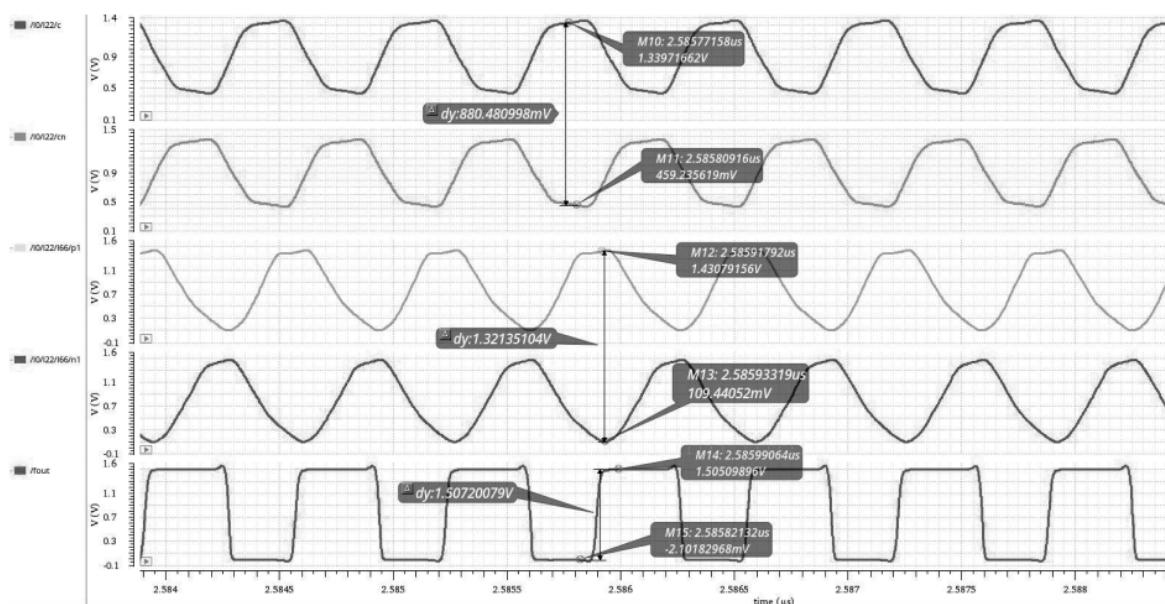

图 5 是使用了 Cadence Virtuoso 仿真的 VCO 输出差分单元输出曲线,第一行和第二行是环形振荡器的模拟输出,振幅仅 0.88 V。在经过一对运算放大器后,输出振幅是 1.32 V,再把信号输入到输出缓存单元,最终使输出为满振幅 1.50 V、占空比 50% 的标准数字方波。

#### 1.4 DSM 调制器

##### 1.4.1 DSM 结构

在小数  $N$  分频锁相环中,DSM 和可编程分频器配合控制 DIV 模块对 VCO 伪随机地分频。PLL 的分频比在 DSM 调制器作用下发生随机整数变化,并且在频域上把量化的噪声不断推向高频处,然后使用环路滤波器把高频噪声过滤掉,最终在 DSM 调制器的作用下,PLL 实际输

图 4 输出缓存单元

出频率的平均值为非整数,从而实现 PLL 的小数分频。

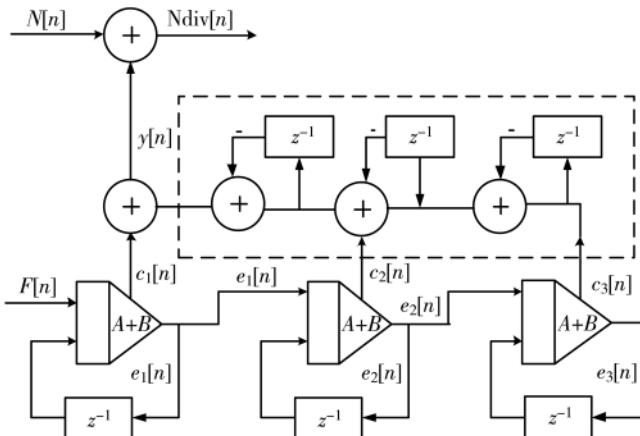

本 DSM 模块使用如图 6 所示的 MASH3 结构,它是由 3 个一阶累加器级联而成的。参考频率  $F_{ref}$  作为其时钟。在 MASH3 结构中,各个一阶累加器的进位输出函数为:

$$\begin{cases} c_1[n] = e_1[n] \times (1-z^{-1}) + F[n] \\ c_2[n] = e_2[n] \times (1-z^{-1}) - e_1[n] \\ c_3[n] = e_3[n] \times (1-z^{-1}) - e_2[n] \end{cases} \quad (1)$$

其中, $F[n]$  为小数输入, $c[n]$  为进位, $e[n]$  为误差信号,根据式(1)得:

$$\Delta N[n] = c_1[n] + c_2[n] \times (1-z^{-1}) + c_3[n] \times (1-z^{-1})^2 \quad (2)$$

展开式(2)括号中各项,合并后得:

$$\Delta N[n] = e_3[n] \times (1-z^{-1})^3 + F[n] \quad (3)$$

由式(3)可看出,后面两级可抵消第一级的噪声,剩下最后一级的噪声,但是这个经过  $(1-z^{-1})^3$  高通项整形后的噪声,它的频谱被极大程度挤压到高频项,所

图 5 VCO 输出差分单元仿真

图 6 MASH3 结构的 DSM 模块

以使用三阶 MASH 结构的 DSM 对噪声信号的整形效果更好。

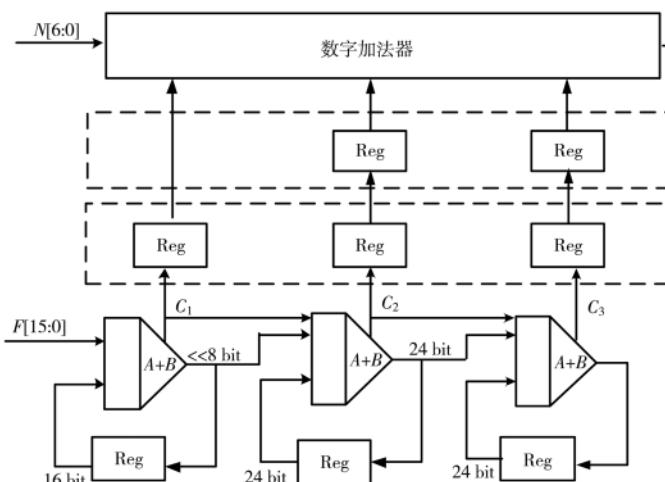

如图 7 所示,本 DSM 模块是三阶的 MASH 结构,主要通过编写 Verilog HDL 代码综合的数字电路模块。本

图 7 DSM 电路图

文设计的数字 MASH3 结构的第一阶加法器和寄存器的位宽为 16 bit,第二阶和第三阶加法器和寄存器位宽为 24 bit,从而保证了最小 396 Hz 的输出频率步进和优秀的噪声整形能力。

为了避免每个累加器之间的进位延迟会降低整个电路的工作速度,本设计使用了若干的 4 bit 超前进位加法器来组成 16 bit 和 24 bit 的全加器。

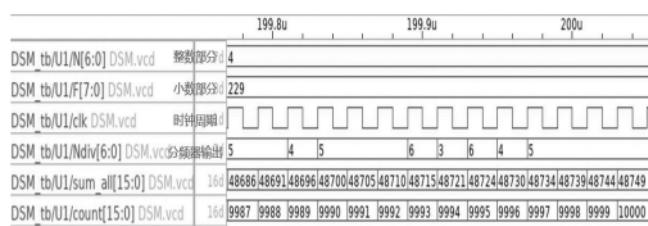

#### 1.4.2 DSM 仿真分析

利用 VCS 对 DSM 的数字模块进行仿真,设置整数  $N$  为 4,小数  $F$  为 229,所以理论小数输出应为  $229/255=0.89$ (小数  $F$  输入位宽为 8 bit)。在 DSM 的 RTL 代码中加入 sum 和 count 测试代码,sum 用于将每个周期分频器输出的  $Ndiv$  进行累加,count 是每个时钟的累加。仿真结果如图 8 所示,在仿真进行时, $Ndiv$  不断输出在 4.89 附近的整数输出,随着  $Ndiv$  的计算周期增加,输出平均值不断接近 4.89 的理论输出。虽然 DSM 输出仍是整数,但是在足够长的周期内,使整数输出的平均值不断接近理论 4.89 的小数输出。

#### 2 锁相环性能指标

##### 2.1 小数分频锁定时间

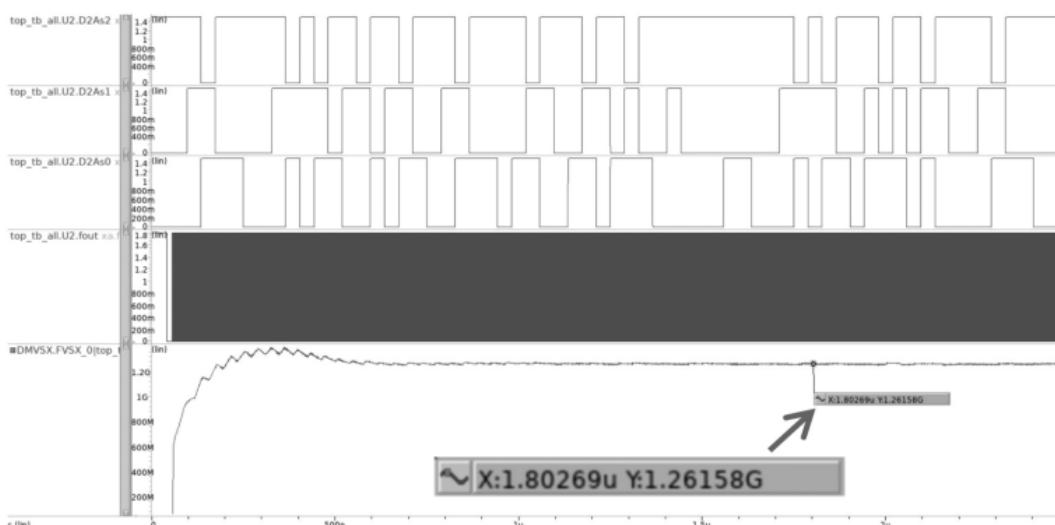

使用 Synopsys 的 VCS-XA 数字模拟混合仿真环境对 PLL 电路进行仿真,设置时钟周期 26 MHz,分频比是 48.5225 倍,即理论输出频率为 1 261.585 MHz。实际仿真的波形如图 9 所示,最下面两行分别是  $F_{out}$  输出波

图 8 DSM 仿真图

图 9 锁相环数模混合仿真图

# 微电子技术

## Microelectronic Technology

形和  $F_{\text{out}}$  输出频率，在仿真到  $1.8 \mu\text{s}$  时候，频率输出为  $1261.580 \text{ MHz}$ ，完成锁相环的锁定。若取  $1.8 \mu\text{s} \sim 10 \mu\text{s}$  的时间段，可对输出频率稳定性进行观察，计算该时间段输出频率平均值为  $1261.110 \text{ MHz}$ ，与理论输出频率偏差为  $0.04\%$ 。

### 2.2 相位噪声与 VCO 增益

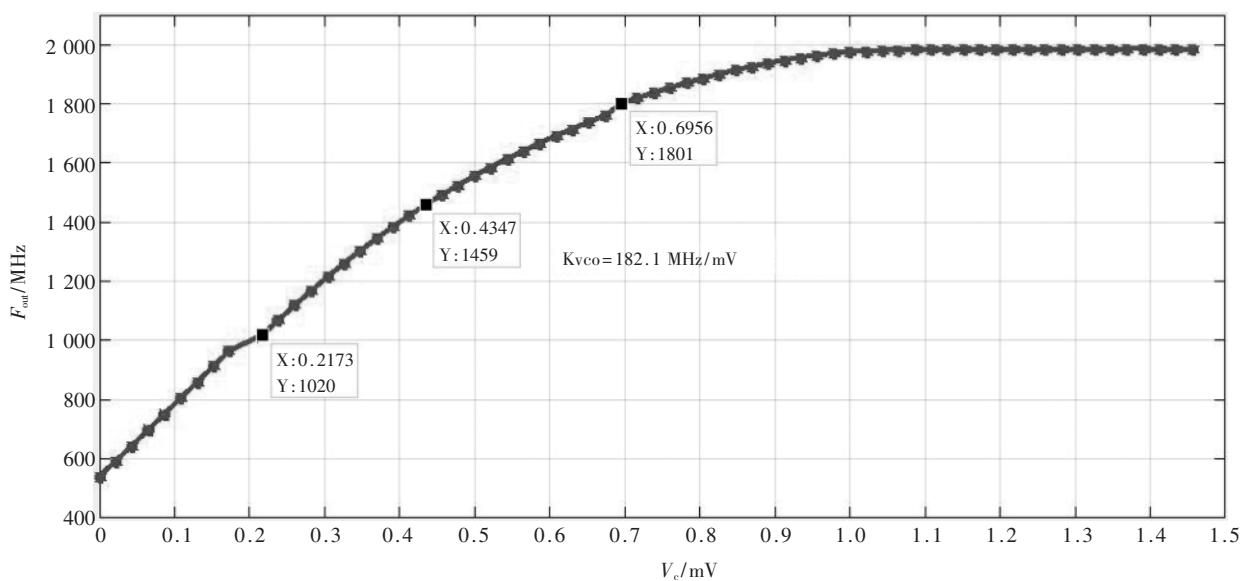

图 10 是 VCO 的增益  $K_{\text{vco}}$  曲线，本 VCO 的压控电压  $V_c$  在  $0.2 \text{ V} \sim 1.2 \text{ V}$  之间变化，频率的变化范围为  $0.3 \text{ GHz} \sim 2.5 \text{ GHz}$ ，在  $0.2 \text{ V} \sim 1.2 \text{ V}$  之间的频率增益  $K_{\text{vco}}$  为  $207.9 \text{ MHz/mV}$ 。

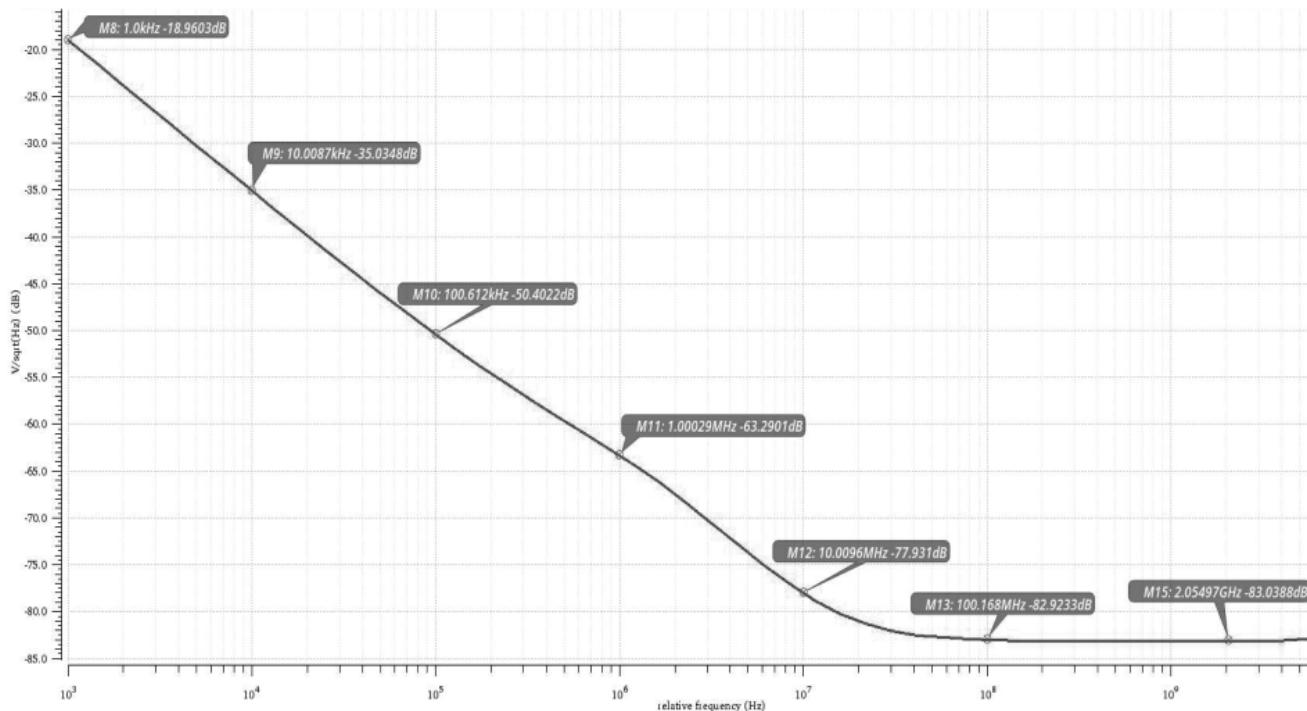

使用 Cadence Virtuoso 对 VCO 进行相位噪声的仿真，结果如图 11 所示。当工作在  $1 \text{ MHz}$  时，相位噪声  $-78 \text{ dBc/Hz}$ 。当工作在  $1 \text{ GHz}$  时，相位噪声仅为  $-146 \text{ dBc/Hz}$ 。PLL 中通过设计能加快电流转向的电荷泵和低相位噪声、高频率增益的 VCO，从而保证了整个锁相环环路稳定性，加快锁定时间。

### 2.3 锁相环对比

其他文献中小数分频锁相环与本文中的小数分频锁相环的性能对比如表 1 所示，文献[7-8]使用了与本设计相似的 COMS 工艺，但相位噪声和锁定时间差于本

图 10 VCO 增益曲线

图 11 VCO 相位噪声仿真

表 1 与其他小数分频锁相环性能对比

| 参数     | 工艺/<br>nm | 电源<br>电压/V | 输出频率<br>范围/GHz | 相位噪声/<br>$\text{dBc} \cdot \text{Hz}^{-1}$ | 锁定<br>时间/ $\mu\text{s}$ |

|--------|-----------|------------|----------------|--------------------------------------------|-------------------------|

| 文献[7]  | 180       | 1.8        | 1.5~4.5        | -93.8@1MHz                                 | 8                       |

| 文献[8]  | 130       | 1.2        | 2.1~5.1        | -123@1MHz                                  | 4                       |

| 文献[9]  | 65        | 1.0        | 1.9~2.7        | -120@1MHz                                  | 12                      |

| 文献[10] | 65        | 1.2        | 1.3~2.65       | -90@1MHz                                   | 8                       |

| 本文     | 130       | 1.5        | 0.8~2.0        | -79@1MHz                                   | 2                       |

PLL。对于文献[9~10]使用了更先进的 65 nm 工艺,输出频率两者和本文 PLL 相近,也同时具有较好的相位噪声,但锁定时间慢于本设计。可见,本文的小数分频锁相环是同时具有低相位噪声和快速锁定的优势。

### 3 结论

本文 PLL 是在整数分频锁相环的基础上,通过加入了 MASH3 结构的数字 DSM 使锁相环具有小数分频的功能,且最小输出频率步进为 396 Hz。另外设计了一款电流转向电荷泵,且在电荷泵中加入电荷注入抵消结构,加快了电荷泵的充放电速度和增加 PLL 的动态稳定性。在 VCO 的设计中,使用了有较高输出增益的环形差分反相器,同时增加了负载单元和输出缓存单元有效降低了相位噪声。通过这些模块的优化和环路匹配,最终本小数分频 PLL 能在 2  $\mu\text{s}$  内完成锁定最高 2.0 GHz 的输出频率,并且输出 1 GHz 时相位噪声仅为 -146 dBc/Hz。

### 参考文献

- [1] CHEN X , CAI L W , XU X , et al.A 0.13um low phase noise and fast locking PLL[C].IEEE Advanced Information Technology , Electronic and Automation Control Conference , 2019 : 1468~1471.

- [2] HSIEH F J , KAO S K .Fast locking PLL with all-digital locked-aid circuit[C].IEEE International Conference of Electron Devices and Solid-State Circuits , 2010 : 1~4.

- [3] SAW S K , NATH V .A low power low noise current starved

CMOS VCO for PLL[C].IEEE International Conference on Computing , Communication Automation , 2015 : 1252~1255.

- [4] ZHOU B , LI Y , ZHAO F .Noise and spur comparison of delta-sigma modulators in fractional-N PLLs[J].Journal of Electronic Testing , 2019 , 35 : 917~923.

- [5] AMER A G , IBRAHIM A I , RAGAI H F .A novel current steering charge pump with low current mismatch and variation[C].IEEE International Symposium on Circuits and Systems .Montreal , 2016 : 1666~1669.

- [6] 刘姗姗,万培元,李建军,等.1.5 GHz Serdes 低抖动锁相环的设计[J].中国科技论文,2015,10(2):130~133,138.

- [7] 林鑫.基于小数 N 分频的电荷泵锁相环研究与设计[D].深圳:深圳大学,2017.

- [8] MANAS H K , TARUN K B .A fast automatic frequency and amplitude control LC-VCO circuit with noise filtering technique for a fractional-N PLL frequency synthesizer[J]. Microelectronics Journal , 2016 , 52 : 134~146.

- [9] LEE Y , KIM S , SHIN H .Design of a 1-V 3-mW 2.4-GHz fractional-N PLL synthesizer in 65nm CMOS[C].IEEE International SoC Design Conference , 2017 : 230~231.

- [10] UN K-F , QI G Z , YANG S H , et al.A 0.12-mm<sup>2</sup> 1.2 to 2.4 mW 1.3 to 2.65 GHz fractional-N bang-bang digital PLL with 8- $\mu\text{s}$  settling time for multi-ISM-band ULP radios[J].IEEE Transactions on Circuits and Systems I: Regular Papers , 2019 : 3307~3316.

(收稿日期:2020-06-19)

### 作者简介:

区健川(1992-),男,硕士研究生,主要研究方向:集成电路设计。

蔡良伟(1964-),男,硕士,教授,主要研究方向:智能信息处理和智能计算。

徐渊(1978-),男,博士,副教授,主要研究方向:FPGA 和 ASIC 设计。

(上接第 60 页)

- [17] JI L , TANG L , LI X W .Design of a VCO for rubidium atomic frequency standard[C].Proceedings of the 2014 Symposium on Piezoelectricity , Acoustic Waves , and Device Applications .IEEE , 2014 .

(收稿日期:2020-08-03)

### 作者简介:

王淼儿(1997-),通信作者,女,硕士研究生,主要研究方向:嵌入式系统研究,E-mail:wangmiao1520@163.com。

姚燕(1978-),女,博士,副教授,主要研究方向:自动测控技术。

## 版权声明

经作者授权，本论文版权和信息网络传播权归属于《电子技术应用》杂志，凡未经本刊书面同意任何机构、组织和个人不得擅自复印、汇编、翻译和进行信息网络传播。未经本刊书面同意，禁止一切互联网论文资源平台非法上传、收录本论文。

截至目前，本论文已经授权被中国期刊全文数据库（CNKI）、万方数据知识服务平台、中文科技期刊数据库（维普网）、DOAJ、美国《乌利希期刊指南》、JST 日本科技技术振兴机构数据库等数据库全文收录。

对于违反上述禁止行为并违法使用本论文的机构、组织和个人，本刊将采取一切必要法律行动来维护正当权益。

特此声明！

《电子技术应用》编辑部

中国电子信息产业集团有限公司第六研究所