# 基于 FPGA 的图像压缩编解码系统设计

任 静 , 李菁菁 , 刘云飞

(南京林业大学 信息科学技术学院 , 江苏 南京 210037)

**摘要:** 针对图像处理的实时性要求, 设计了一种基于 FPGA 的图像压缩编解码系统。该系统包括实时图像采集、JPEG 压缩以及 UART 传输等功能。采用 Altera 公司的 DE 系列开发板, 应用 Verilog HDL 硬件描述语言对 D5M 摄像头进行配置, 完成图像采集。在图像压缩模块, 重点对 2D-DCT 变换进行改进。在基于 Chen 算法的基础上采用二分频信号控制器, 减少了加法器的调用, 实现其快速运算, 进而完成图像压缩功能。在 URAT 传输模块, 主要完成串行通信与并行通信间的转换。测试表明, 图像的压缩比达到 26.3:1, 其均值信噪比大于 40 dB, 压缩后的视觉效果良好, 符合设计要求。

**关键词:** FPGA ; JPEG 压缩算法 ; RS\_232 ; D5M 摄像头

中图分类号: TP391

文献标识码: A

DOI: 10.16157/j.issn.0258-7998.200532

中文引用格式: 任静 , 李菁菁 , 刘云飞 . 基于 FPGA 的图像压缩编解码系统设计 [J]. 电子技术应用 , 2020 , 46(12) : 111-115.

英文引用格式: Ren Jing , Li Jingjing , Liu Yunfei . Image compression coding and decoding system based on FPGA [J]. Application of Electronic Technique , 2020 , 46(12) : 111-115.

## Image compression coding and decoding system based on FPGA

Ren Jing , Li Jingjing , Liu Yunfei

(College of Information Science and Technology , Nanjing Forestry University , Nanjing 210037 , China)

**Abstract:** Aiming to real-time requirement of image processing, an image compression coding and decoding system based on FPGA is designed. The system includes real-time image acquisition, JPEG compression and UART transmission. The D5M camera is configured by Verilog hardware description language to acquire image. We focus on improving two-dimension discrete cosine transformation(2D-DCT) design flow in the image compression module. The dual frequency signal controller is adopted to reduce the call of adder based on the Chen algorithm and realize its fast operation. The test shows that the compression ratio of the image is 26.3:1, and the average signal-to-noise ratio is more than 40 dB. The visual effect of the compressed image is good, which meets the design requirements.

**Key words:** FPGA ; JPEG compression algorithm ; RS\_232 ; D5M camera

## 0 引言

数字化处理后的图像, 其所随带的信息量是庞大的, 这将严重影响到图像的存储与传输。因此, 图像压缩具有重要的现实意义<sup>[1-2]</sup>。而在实际的工程需求中, 由于图像数据量的巨大以及对于处理实时性的要求, 如果单纯依靠软件来实现图像的处理往往非常耗时。为此, 采用能够并行处理的硬件实现可以大大加快数据处理的速度, 且在程序设计时具有更高的灵活性。

本设计以 FPGA 开发平台作为整个系统的控制核心, 由 I<sup>2</sup>C 总线进行实时图像获取, 并将它实时转换为 RGB 格式的图像数据。利用 JPEG 算法分别对 Y、Cb、Cr 分量实现编码处理, 应用 Verilog HDL 硬件语言编程, 大大加快处理速度。压缩后的数据码流通过 RS\_232 串口传输给 PC, 最终导入 MATLAB 中进行解压缩和恢复

图像。

## 1 系统总体框架

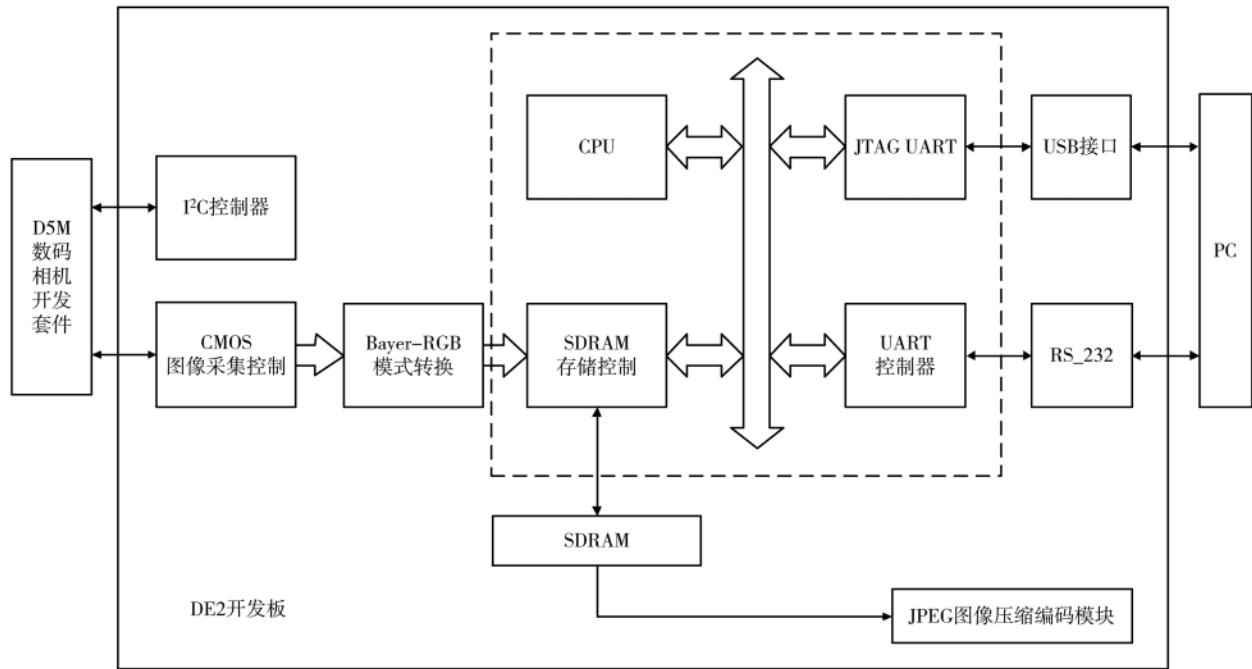

本设计采用 Altera 公司提供的 DE2 开发平台, 其中, 核心的 FPGA 芯片为 CycloneII 系列的 EP2C35F672。此外, 设计还包含 TRDB\_D5M 摄像机开发套件(MT9P001)和 UART 串口等。该系统主要由三个部分构成: 实时图像采集、JPEG 压缩以及数据传输模块。最后, 送至 PC 端的数据通过 MATLAB 进行解压缩操作, 重建图像。其硬件平台的系统结构如图 1 所示。

## 2 图像采集模块设计

在图像采集模块中, 首先采用 TRDB\_D5M 摄像头来获取实时图像数据, 其配置是通过 I<sup>2</sup>C 总线来控制实现的, 除此之外, 本模块还包含图像色彩空间由 Bayer 格式向 RGB 格式的转换以及图像存储部分。

图 1 系统总体结构框图

## 2.1 图像格式转换模块

图像格式转换模块采用插值算法, 将每四个像素合并为一个新的像素值, 并调用两个 RAM-based(移位寄存器)实现数据的缓存, 实现相邻两行数据的同步输出<sup>[3]</sup>。最终, 实时地将原始 Bayer 格式转换为标准 RGB 格式。

## 2.2 图像缓存模块

图像缓存模块采用 DE2 开发板自带的一块 8 MB 的 SDRAM 作为图像的缓存。由于 DE2 开发板只有一片 16 bit 的 SDRAM, 需要通过设计 Sdram\_Control\_4Port 控制模块实现 32 bit 的 SDRAM 的模拟扩充, 进行两个读写操作。

## 3 JPEG 压缩模块设计

本设计选取 JPEG 算法进行图像压缩, 应用自顶向下的方法设计不同的功能模块, 并采用 Verilog HDL 编程实现系统功能。主要包括图像预处理、DCT 变换、量化 Zigzag 扫描以及熵编码和码流组装模块。

### 3.1 DCT 变换模块

直接进行二维离散余弦变换将消耗大量的资源, 在 FPGA 上几乎无法实现<sup>[4-5]</sup>。可以采用将 2D-DCT 变换分解为两次 1D-DCT 变换的方法来实现, 那么, 提高 1D-DCT 变换的速度则是提高 2D-DCT 变换速度的关键所在。目前 FPGA 实现中使用比较广泛的有 Loeffier 算法和 Chen 算法, 而后者拥有更好的规则结构和较准确的精度且计算速度优于其他算法。因此, 本文以 Chen 算法为理论基础进一步对一维 DCT 模块进行了优化设计。

一维 DCT 变换可表示为:  $Y = XC^T$ , 其中,  $X$  为  $8 \times 8$  像素矩阵,  $C$  为变换核矩阵。则  $Y$  可以展开为下面的形式:

$$\begin{aligned}y_{00} &= c_1(x_{00}+x_{07}) + c_1(x_{01}+x_{06}) + c_1(x_{02}+x_{05}) + c_1(x_{03}+x_{04}) \\y_{01} &= c_2(x_{00}-x_{07}) + c_4(x_{01}-x_{06}) + c_5(x_{02}-x_{05}) + c_7(x_{03}-x_{04}) \\y_{02} &= c_3(x_{00}+x_{07}) + c_6(x_{01}+x_{06}) - c_6(x_{02}+x_{05}) - c_3(x_{03}+x_{04}) \\y_{03} &= c_4(x_{00}-x_{07}) - c_7(x_{01}-x_{06}) - c_2(x_{02}-x_{05}) - c_5(x_{03}-x_{04}) \\y_{04} &= c_1(x_{00}+x_{07}) - c_1(x_{01}+x_{06}) - c_1(x_{02}+x_{05}) + c_1(x_{03}+x_{04}) \\y_{05} &= c_5(x_{00}-x_{07}) - c_2(x_{01}-x_{06}) + c_7(x_{02}-x_{05}) + c_4(x_{03}-x_{04}) \\y_{06} &= c_6(x_{00}+x_{07}) - c_3(x_{01}+x_{06}) + c_3(x_{02}+x_{05}) - c_6(x_{03}+x_{04}) \\y_{07} &= c_7(x_{00}-x_{07}) - c_5(x_{01}-x_{06}) + c_4(x_{02}-x_{05}) - c_2(x_{03}-x_{04})\end{aligned}$$

将偶数行和奇数行分成两组以进一步简化运算步骤, 可以表示为如下的矩阵乘法形式:

$$\begin{aligned}\begin{bmatrix}y_{k0} \\ y_{k2} \\ y_{k4} \\ y_{k6}\end{bmatrix} &= \begin{bmatrix}c_1 & c_1 & c_1 & c_1 \\ c_3 & c_6 & -c_6 & -c_3 \\ c_1 & -c_1 & -c_1 & c_1 \\ c_6 & -c_3 & c_3 & -c_6\end{bmatrix} \begin{bmatrix}x_{k0}+x_{k7} \\ x_{k1}+x_{k6} \\ x_{k2}+x_{k5} \\ x_{k3}+x_{k4}\end{bmatrix} \\ \begin{bmatrix}y_{k1} \\ y_{k3} \\ y_{k5} \\ y_{k7}\end{bmatrix} &= \begin{bmatrix}c_2 & c_4 & c_5 & c_7 \\ c_4 & -c_7 & -c_2 & -c_5 \\ c_5 & -c_2 & -c_7 & c_4 \\ c_7 & -c_5 & c_4 & -c_2\end{bmatrix} \begin{bmatrix}x_{k0}-x_{k7} \\ x_{k1}-x_{k6} \\ x_{k2}-x_{k5} \\ x_{k3}-x_{k4}\end{bmatrix}\end{aligned}$$

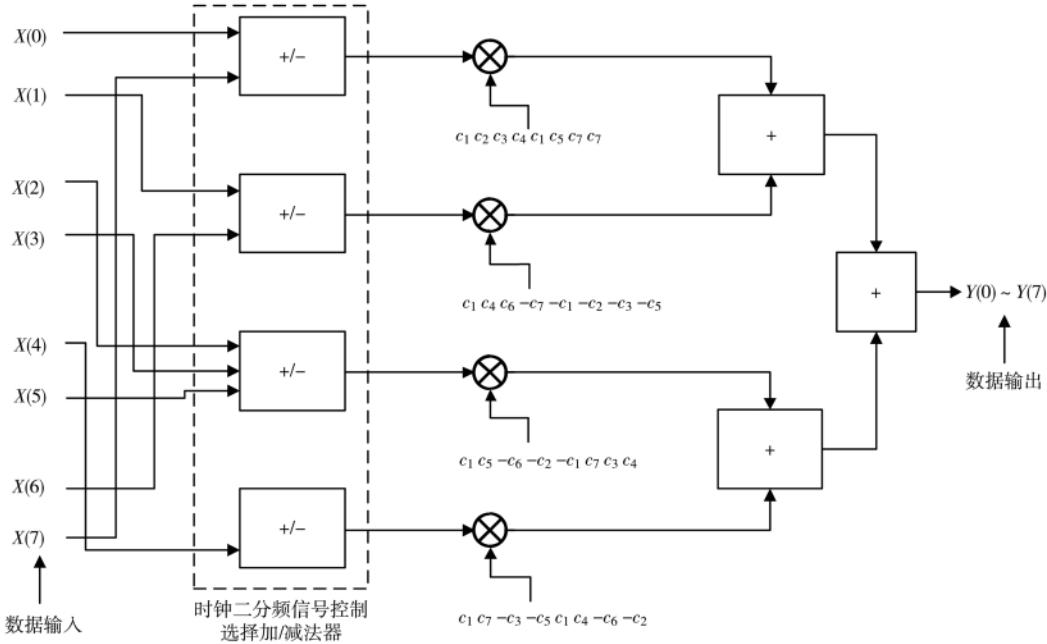

简化操作后的矩阵, 8 点 DCT 变换需要 32 次乘法运算和 32 次加法运算<sup>[6]</sup>。经过观察, 其偶数行对应的输入均为数据相加, 奇数行均为数据相减。利用这一规律, 本文在 Chen 算法的基础上增加时钟二分频信号控制器来进行优化, 当输入数据进入时, 依次在前后两个时钟周期, 分别选择加法器和减法器, 当时钟二分频信号处于低电平时, 调用减法器进行运算, 反之, 则进行加法运算。其结构图如图 2 所示, 通过时钟二分频信号控制选择可以减少加/减法器的调用。由图可知, 本文算法的 1D-DCT 变换共有 16 次乘法运算和 20 次加法运算, 进

图 2 一维 DCT 变换结构图

一步节约了逻辑资源,加快运行速度。从中可以发现,DCT 的乘法运算量减半,而且算法结构规则,可以并行计算。

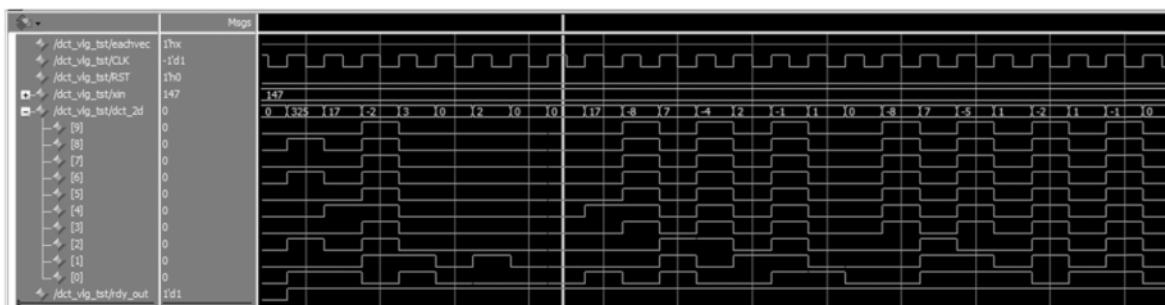

选取图像中的一组  $8 \times 8$  矩阵,JPEG 压缩的操作过程是各自对其 Y 分量、Cr 分量和 Cb 分量进行压缩。因各分量压缩操作步骤相同,这里仅选取 Y 分量的矩阵系数作为测试数据,将其依次输入到 DCT 变换模块中,以验证此模块的正确性。图 3 为 2D-DCT 模块 Modelsim 仿真波形图,计算结果对比如表 1 所示。

比较两种仿真结果可以发现,本设计的 Modelsim 仿真结果与 MATLAB 计算的理论值几乎相同,只存在很小的误差。产生误差的原因主要是为抵消运算数据的放大而进行高位截取所引起的,其结果影响较小,可以忽略不计。

### 3.2 量化 Zigzag 编码模块

实现量化的过程可分为两步:首先将 DCT 系数按照一定的比例缩小,然后对缩小后的矩阵系数进行四舍五入并取整<sup>[7]</sup>。由于对变换后的矩阵进行除法操

表 1 计算结果对比

| 输入待测数据 |     |     |     | MATLAB 计算结果 |        |        |       | Modelsim 计算结果 |     |     |    |

|--------|-----|-----|-----|-------------|--------|--------|-------|---------------|-----|-----|----|

| 174    | 174 | 174 | 173 | 214.5       | 49.22  | -2.73  | 19.66 | 217           | 50  | -2  | 19 |

| 173    | 172 | 171 | 169 | -10.25      | -0.91  | 0.59   | -6.08 | 10            | 1   | 1   | -6 |

| 173    | 173 | 173 | 172 | 34.63       | -24.68 | 10.82  | 12.96 | 35            | -25 | 11  | 13 |

| 172    | 170 | 170 | 169 | 4.96        | -2.82  | 15.01  | -5.82 | 5             | -3  | 14  | 6  |

| 173    | 172 | 172 | 172 | -6.34       | -3.98  | 7.48   | -9.5  | -6            | -4  | 8   | -9 |

| 172    | 170 | 170 | 169 | 2.32        | -2.86  | 4.85   | 9.91  | 2             | -3  | 5   | 10 |

| 172    | 172 | 171 | 171 | 8.12        | -10.71 | 4.11   | 3.43  | 8             | -11 | 4   | 4  |

| 170    | 170 | 170 | 168 | -15.36      | 9.95   | 5.44   | 6.31  | -15           | 10  | -5  | 6  |

| 171    | 170 | 170 | 170 | -11.75      | 6.02   | -0.43  | -0.68 | -11           | 6   | 0   | -1 |

| 171    | 170 | 169 | 166 | -14         | 9.89   | -4.96  | -1.2  | -14           | 10  | -5  | -2 |

| 170    | 170 | 170 | 169 | 4.38        | 8.92   | -8.09  | 2.2   | 4             | 9   | -8  | 3  |

| 170    | 169 | 167 | 163 | 3.91        | -7.01  | -14.46 | 1.9   | 4             | -7  | -14 | 2  |

| 171    | 170 | 168 | 170 | 1.01        | -2.72  | 1.85   | -1.68 | 1             | -3  | 2   | -2 |

| 170    | 168 | 165 | 158 | 0.38        | 2.26   | -3.48  | -4.38 | 0             | 2   | -3  | -5 |

| 171    | 170 | 169 | 169 | -0.12       | 1.92   | 0.9    | 2.71  | 0             | 2   | 1   | 3  |

| 169    | 166 | 163 | 147 | 4.01        | -0.78  | -3.55  | -2.22 | 4             | 0   | -4  | -2 |

作相对复杂,而对量化值取倒数后再进行乘法运算,可以实现同样的功能。因此,本设计采用乘法器替代除法

图 3 2D-DCT 功能波形图

# 嵌入式技术

## Embedded Technology

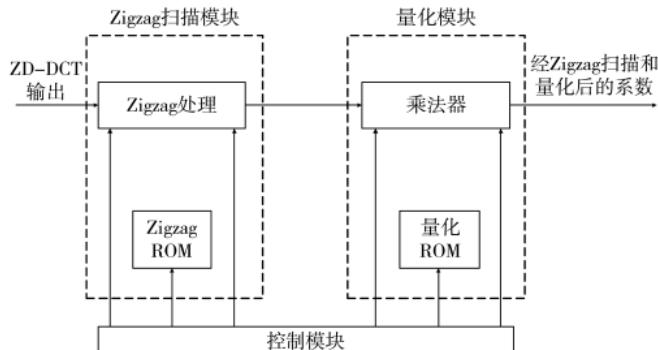

操作,进一步提高运算速度。同时,采用量化和Zigzag扫描相结合的方式,其设计框图如图4所示。首先对DCT系数和存放在ROM中的量化表进行Zigzag扫描,再送入乘法器中对应相乘从而完成量化操作。这样的设计方法可以更有效地缩短计算时间,加快硬件的运算速度。

图4 量化与Zigzag排序设计框图

本设计采用JPEG专家组推荐的亮度和色度量化<sup>[8]</sup>,它可以适用于绝大多数图片,且与理论上最佳量化表相比,效果几乎是一样的。同时,采用官方推荐的量化表可以大大提高了效率,减少运算。

### 3.3 熵编码模块

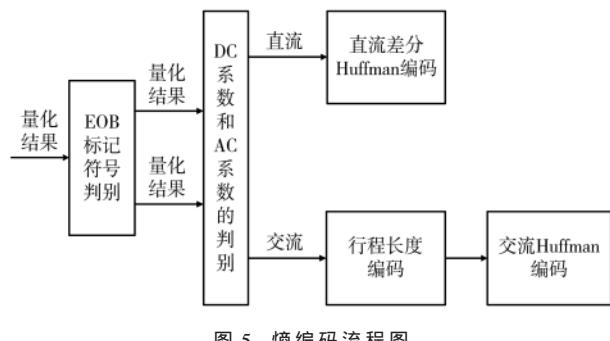

熵编码的实现可分为三步进行,首先对EOB的位置进行检测;其次,对矩阵中的直流(DC)系数和交流(AC)系数进行判别;最后,实现DC系数差分Huffman编码以及对AC系数先进行行程长度编码再进行交流Huffman编码<sup>[9]</sup>。完成以上操作后即可得到最终的编码结果,其熵编码模块的流程图如图5所示。

### 4 UART 传输模块

UART是一种异步收发传输器,它将要传输的数据在串行通信与并行通信之间加以转换,即将并行输入信号转成串行输出信号,广泛应用于数字通信领域。它可以与各种标准的串行接口相连接,如RS232、RS485等<sup>[10]</sup>。

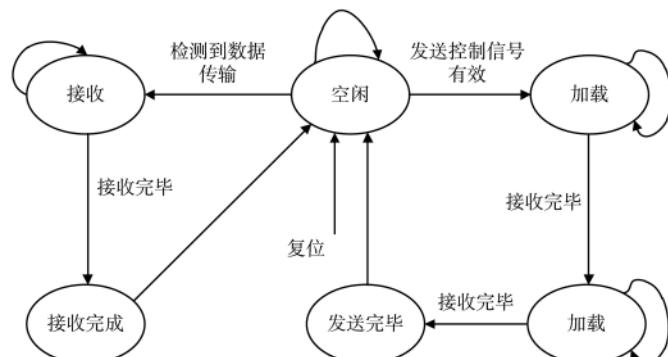

UART内核是整个模块的核心,也是设计最为复杂的部分。当接收数据时,UART内核模块控制波特率发

图5 熵编码流程图

生器产生使能信号,使移位寄存器在波特率时钟的作用下能够采集RS\_232输入信号并保存数据。当发送数据时,UART内核模块会按照待发送数据产生相对应的参数(数据位、停止位、校验位等),先将待发送数据加载到其内部寄存器,再使移位寄存器在波特率模式下将数据串行输出到RS\_232口<sup>[11-12]</sup>。UART内核模块接收和发送数据的过程如图6所示。

图6 UART内核状态图

## 5 实时图像压缩系统的验证

### 5.1 图像压缩结果与分析

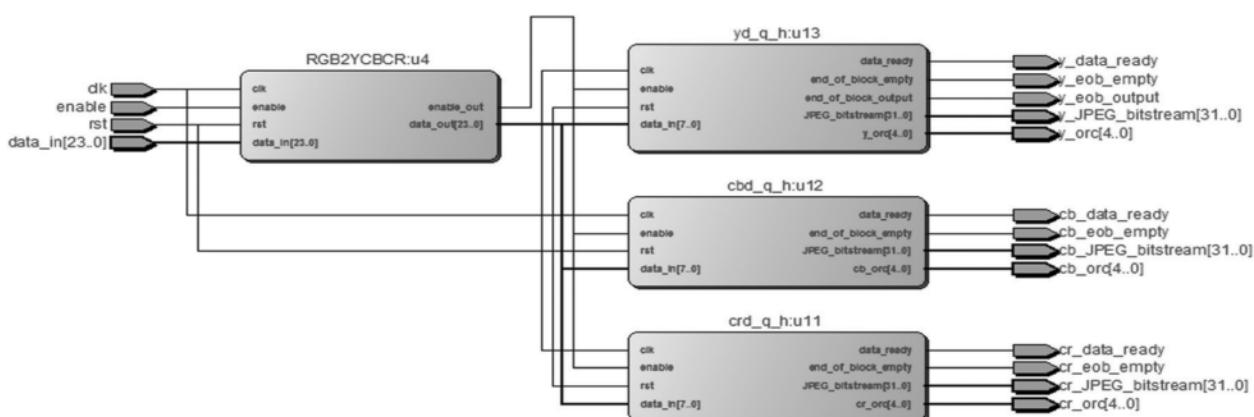

本设计在Quartus II软件中利用Verilog高级硬件描述语言,按照模块化设计思想将JPEG编码器的顶层模块分为RGB2YCbCr、yd\_q\_h、cbd\_q\_h和crd\_q\_h这几个模块。图7为JPEG编码器的RTL框架图。

图7 图像压缩模块 RTL 级视图

分别对改进前后的 2D-DCT 模块进行编译综合,选取芯片为 EP2C35F672C6。通过观察编译综合报告,可以看出改进前后的资源消耗情况,如表 2 所示。改进后的算法资源消耗减少,从 9%降到 7%。此外,优化后的模块设计时最高工作时间频率为 140 MHz,完成 DCT 变换总共需要 157 个时钟周期,约为 1.121 ms,能够达到实时性的要求。

表 2 算法改进前后资源消耗情况

|        | Total Logic Elements | Logic Registers |

|--------|----------------------|-----------------|

| 陈氏算法   | 3 025                | 726             |

| 本文改进算法 | 2 471                | 503             |

## 5.2 系统测试结果与分析

D5M CMOS 传感器 MT9P001 实时抓取的植物图像如图 8 所示,图像清晰,大小为 640×480,约 900 KB。压缩后的数据经 MATLAB 解压缩后的图像如图 9 所示,大小为 34.2 KB。压缩比为 26.3,重建后图像峰值信噪比为 53.396 9 dB,因此本文采取的压缩算法在减少数据量的同时,也保证了图像的重建质量。同时,通过观察图 9 可以发现,压缩后的图像依旧保持了较好的视觉质量,并没有出现明显块效应且较好地保存了植物的特征。

图 8 原始图像

图 9 压缩后的图像

整个系统的硬件测试平台如图 10 所示。

图 10 硬件设计平台

## 6 结论

本设计选用 DE2 开发板作为硬件实现平台,配置了 D5M 摄像头的相关模块,并完成了图像的采集以及压缩功能,体现了硬件良好的并行性。应用 Nios II 软核处理器实现整个系统的控制并通过 RS\_232 串口与 PC 进行

传输通信。最后,将编译好的功能成文件下载到 FPGA 芯片中,实现图像的采集和压缩,并将串口输出的码流进行整理,最终在 PC 上显示出来,恢复图像效果良好。

本文设计的核心是 JPEG 压缩算法,重点分析了 2D-DCT 变换模块,在 Chen 算法的基础进行了改进。采用二分频信号控制器,依次对输入信号进行加减运算,实现其快速算法。对比发现,改进后的算法资源消耗减少,从 9%降到 7%,更利于硬件的快速处理。同时,量化 Zigzag 扫描模块将量化与 Zigzag 扫描部分结合操作,在实现量化操作前先将 DCT 系数和量化步长进行重排,从而减少功能实现所需时间,进一步加快了运行速度。测试结果表明,整个系统性能良好,其图像压缩比为 26.3:1,数据量有较大减少且保证了压缩后图像的视觉效果,符合预期的设计目标。

## 参考文献

- [1] 王红伟.浅谈数字图像处理技术的应用现状与发展前景[D].曲阜:曲阜师范大学,2014.

- [2] MUDDHASANI V, WAGH M D. Bilinear algorithms for discrete cosine transforms of prime lengths[J]. Signal Processing, 2006, 86(5): 2393–2406.

- [3] 马玲玲,刘云飞,顾敏明,等.远程数字图像监控系统的 FPGA 实现[J].电子技术应用,2013,39(6): 70–73.

- [4] 苏阳.基于 FPGA 的二维 DCT/IDCT 高速设计与实现[J].武警工程大学学报,2014(2): 38–42.

- [5] 张慧慧.基于 FPGA 的 JPEG 压缩编码器的设计与实现[D].太原:中北大学,2017.

- [6] EL-SHARKAWY M, ESHMAWY W. A fast 8×8 pruned DCT algorithm[J]. Digital Signal Processing, 1996, 6(3): 145–154.

- [7] 朴圣龙.基于 FPGA 的 JPEG 图像压缩算法实现[J].哈尔滨:哈尔滨工程大学,2013.

- [8] 赵擎天,尉广军,张自宾.基于 DSP Builder 的 JPEG 静态图像压缩算法的实现[J].电子技术应用,2011,37(6): 35–37.

- [9] 刘庆,陈金强,于沛玲.基于 FPGA 的高速二维 DCT 变换的研究与实现[J].计算机工程与科学,2012(3): 103–107.

- [10] 叶林朋.基于 FPGA 的通用异步接收/发送器设计与实现[J].科技资讯,2007(15): 92–93.

- [11] 杨宗国,李艳萍.基于 FPGA 的 UART 模块的设计[J].现代电子技术,2009(2): 19–22.

- [12] 于志翔.基于 FPGA 的 UART 设计与实现[J].电子测量技术,2015(3): 77–81.

(收稿日期:2020-06-22)

## 作者简介:

任静(1994-),女,硕士研究生,主要研究方向:测试及信号处理。

李菁菁(1995-),女,硕士研究生,主要研究方向:测试及信号处理。

刘云飞(1962-),通信作者,男,博士,教授,主要研究方向:信号处理,E-mail:lyf@njfu.edu.cn。

## 版权声明

经作者授权，本论文版权和信息网络传播权归属于《电子技术应用》杂志，凡未经本刊书面同意任何机构、组织和个人不得擅自复印、汇编、翻译和进行信息网络传播。未经本刊书面同意，禁止一切互联网论文资源平台非法上传、收录本论文。

截至目前，本论文已经授权被中国期刊全文数据库（CNKI）、万方数据知识服务平台、中文科技期刊数据库（维普网）、DOAJ、美国《乌利希期刊指南》、JST 日本科技技术振兴机构数据库等数据库全文收录。

对于违反上述禁止行为并违法使用本论文的机构、组织和个人，本刊将采取一切必要法律行动来维护正当权益。

特此声明！

《电子技术应用》编辑部

中国电子信息产业集团有限公司第六研究所