# 基于 FPGA 的 PPM 调制解调系统设计

侯 欢 ,施洪生

(北京交通大学 电气工程学院 ,北京 100044)

**摘要:** 针对旋转件参数的测试及传输,提出了一种基于 FPGA 红外数据传输的 PPM 调制解调系统的设计,并且在数据传输过程中加入了 CRC 校验,增加了数据传输过程的准确性。设计采用了 Altera (Intel) 的 Cyclone10 系列的 10CL016YU256C8 芯片,具有高速、高带宽、高容量等特点,适用于高速数据通信。通过 Quartus II 开发平台,用 Verilog HDL 硬件描述语言编写相应的调制、解调以及 CRC 校验程序。介绍了 4PPM 调制、解调的算法,以及 CRC-CCITT 校验码的算法,并通过 Modelsim 对系统进行了时序仿真,仿真结果验证了设计的正确性。

**关键词:** PPM 调制解调 ;CRC 校验 ;FPGA ;Verilog HDL

中图分类号 : TN919

文献标识码 : A

DOI : 10.16157/j.issn.0258-7998.200984

中文引用格式: 侯欢,施洪生. 基于 FPGA 的 PPM 调制解调系统设计[J]. 电子技术应用, 2021, 47(2): 92–96.

英文引用格式: Hou Huan, Shi Hongsheng. Design of PPM modulation and demodulation system based on FPGA[J]. Application of Electronic Technique, 2021, 47(2): 92–96.

## Design of PPM modulation and demodulation system based on FPGA

Hou Huan ,Shi Hongsheng

(School of Electrical Engineering ,Beijing Jiaotong University ,Beijing 100044 ,China)

**Abstract:** For the test and transmission of rotating parts parameters, a design of a PPM modulation and demodulation system based on FPGA infrared data transmission is proposed, and a CRC check is added in the data transmission process, which increases the accuracy of the data transmission process. This design uses Altera (Intel)'s Cyclone10 series 10CL016YU256C8 chip, which has the characteristics of high speed, high bandwidth, high capacity, etc., suitable for high-speed data communication. Through the Quartus II development platform, it uses Verilog HDL hardware description language to write the corresponding modulation, demodulation and CRC verification programs. The paper introduces the algorithm of 4PPM modulation and demodulation, as well as the algorithm of CRC-CCITT check code, and carries on the timing simulation to the system through Modelsim. The simulation result verifies the correctness of the design.

**Key words:** PPM modulation and demodulation ;CRC check ;FPGA ;Verilog HDL

## 0 引言

在数字电路设计中,现场可编程门阵列(Field Programmable Gate Array,FPGA)技术得到越来越广泛的应用,特别是在通信领域。对于 FPGA 处理器之间的通信,一般采用传统的有线连接,例如 UART、CAN 等方式。可当 FPGA 处理器之间存在相对运动(即一个 FPGA 处理器在旋转侧,而另一个在固定侧)时,传统有线通信方法会带来不便,而无线通信恰好适用于此情况。将基于 FPGA 的 PPM 调制解调无线数据通信技术应用在风机齿轮箱应力测试中,可以规避传统有线式齿轮箱测量的种种风险<sup>[1]</sup>,并且可以简化复杂的滑环工装设计,更加准确地对齿轮箱应力进行测试,同时也可将此技术应用于其他旋转器件的信号测试场合,例如,在数控机床技术中对其卡盘在不同转速下的夹紧力性能进行实时监测;在航空航天技术中对其航空发动机旋翼的应力、

扭矩等进行测试。

随着无线通信技术的不断发展,无线通信的方式也不断出现,其中各种方式的误码率、抗干扰能力和传输速率也不同,为了提高数据传输的速率和抗干扰能力,本设计采用光电耦合的无线数据传输方式,其具有良好的抗干扰能力,它利用光波作为载波对信号进行传输,可以达到很高的传输速率,在光无线通信领域中,保证一定的速率下,要求传输功率尽可能小。脉冲位置调制(PPM)是一种正交调制方式,相比于传统的开关键控(OOK)调制,它具有更高的光功率利用率和频带利用率,并能进一步提高传输信道的抗干扰能力<sup>[2]</sup>。且基于 FPGA 的脉冲位置调制(PPM)可以在高转速、数据量大的旋转件中快速、可靠地传输测量到的数据,因而本设计采用基于 FPGA 的脉冲位置调制(PPM)方式。

## 1 系统整体结构

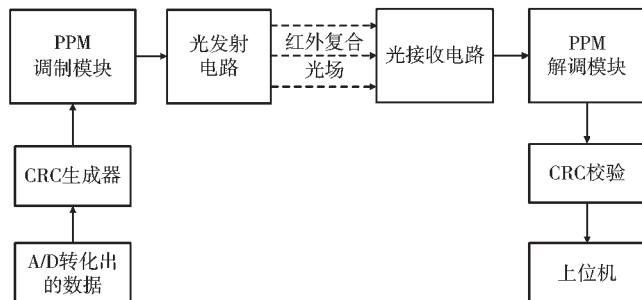

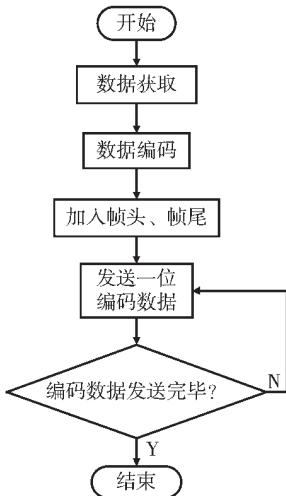

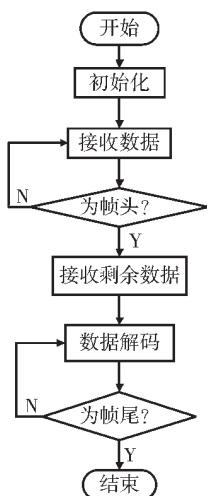

本设计由旋转侧数据的采集和发送以及固定侧数据的接收和处理两部分组成,其中发送侧包括PPM调制电路的实现,接收侧包括PPM解调电路的实现。发送侧是将A/D转化后的数据通过CRC生成器加入CRC校验码,再通过PPM调制模块转化为PPM脉冲信号,最后通过发送电路的红外发射二极管以光的形式发送出去。接收侧是将接收电路中的红外接收头接收到的数据通过PPM解调模块将数据解码出来,再将数据进行CRC校验,最后将数据传给上位机进行显示和处理。系统整体设计流程如图1所示,图2为发送数据流程图,图3为接收数据流程图。

图1 系统整体结构

图2 发送数据流程图

图3 接收数据流程图

## 2 PPM调制系统设计及仿真

PPM调制的编码方式是将输入的 $n$ 位二进制数据映射在脉冲位置调制一帧的 $L(L=2^n)$ 个时隙中,即在 $L$ 个时隙中对应的第 $l$ 个时隙发送一个光脉冲信号<sup>[2]</sup>, $l$ 代表的是时隙的位置数。

### 2.1 PPM调制系统设计

PPM调制是将输入数据转化为不同时隙位置的脉冲,此过程可以用一个计数器来进行计数,从而在不同时隙输出脉冲的过程<sup>[2]</sup>。以时钟脉冲作为一个标准的时间间隔,将计时过程转换成一个计数的过程。计数模块在时钟的上升沿开始计数,当计数数据与二进制调制数

据相等时就在相应的时隙输出高电平,其余时隙输出低电平,由此得到一个不同周期内不同位置上出现脉冲的波形。

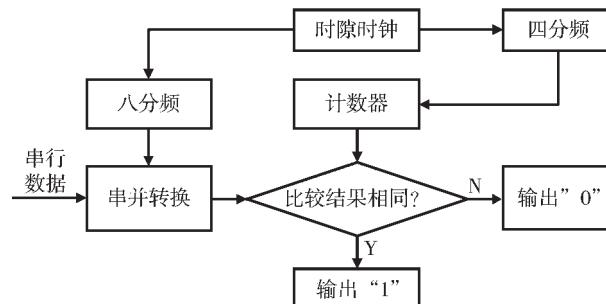

在程序设计中PPM调制思路如下,将系统时钟分别进行四分频和八分频,其中四分频时钟是计数器的时钟信号,八分频时钟是串并转换的时钟信号。串行数据经过串并转换模块转化为并行数据,根据系统所需要的4PPM,将系统时钟信号经过四分频器转化为周期为4的计数器,把串并转换输出的数据和计数器数据输入到比较器模块中进行比较,如果两者相同则输出高电平,反之输出低电平。最后经过一个脉冲成形模块输出窄脉冲,这样可以减小邻近信道对其的干扰。图4是PPM调制Verilog流程图。

图4 PPM调制Verilog流程图

本设计是对4PPM调制系统的设计,因此需要将A/D转化出来的数据进行串并转换,使这些数据转换为两位一组的数据,此部分是实现PPM调制的关键。串并转换可以通过移位寄存器来实现,本设计的思路是:先将第一位进入系统的数据缓存到寄存器中,等到第二个数据进来后,在下一个时钟的上升沿到来时将这两位数据同时输出。其主要代码如下:

```

always @(posedge clk_8 or negedge nRST)

if( !nRST )

begin

dat <= 0;

dat1 <= 0;

end

else

begin

dat <= {dat[1:0],InDat};

dat1 <= dat;

end

assign OutDat = count[0]==1? dat:dat1;

```

### 2.2 PPM调制仿真

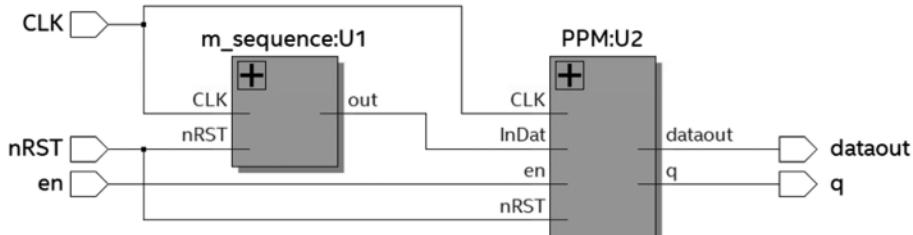

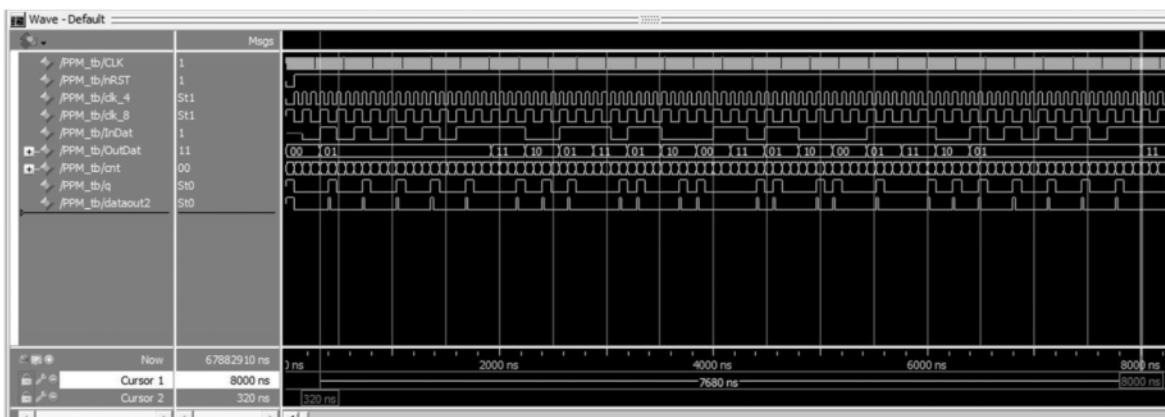

PPM调制的顶层设计就是将调制部分的所有模块都拼接在一块,最终来实现调制的功能。由于本设计是将A/D转换后的数据作为PPM调制模块的输入数据,因此编写Verilog代码来产生一个随机的m序列来代替A/D转换后的数据,最后在顶层设计中将m序列发生器

和 PPM 调制模块连接到一起形成完整的 PPM 调制系统。4PPM 调制 RTL 级图如图 5 所示。4PPM 调制仿真图如图 6 所示。

在图 6 的 4PPM 调制仿真中, 截取其中一段如图所示, PPM 调制系统输入的数据为 InDat(0x55、0x79、0xd8、0xd8、0x55、0x79), 其中 0x79(0111\_1001)经串并转换后变为 01、11、10、01 四组数据, 4 位计数器依次计数 00、01、10、11, 当串并转换后的数据与计数器的数值相等时, 输出数据 q 就为高电平, 得到输出的 q 之后, 再将其高电平的宽度缩小为原来的四分之一, 这样可以减小邻近信道对其的干扰。由此得到了最终的 4PPM 调制波形 dataout。在图 7 中, 输入 0x79 时间段中, 经过了 8 个八分频时钟, 输入数据依次为 01、11、10、01, 在与计数器值 count 相比较后, 分别在 4 个时隙的第二个位置、第四个位置、第三个位置、第二个位置输出了一个脉冲, 这刚好与 PPM 调制原理一致, 从而证明了系统设计的正确性。

### 3 PPM 解调系统设计及仿真

#### 3.1 PPM 解调系统设计

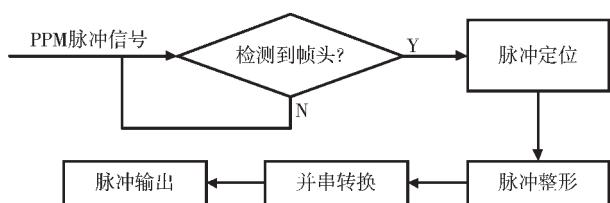

PPM 解调可以由 PPM 调制的逆向思路来实现, 在 FPGA 解调过程中首先要提取帧同步信号, 本设计中采用在数据的头和尾分别插入特殊的帧头和帧尾, 以此来判断数据的起始位和终止位。进入 FPGA 的是有一定规律的脉冲信号, 检测到帧头后, 再确定脉冲在一帧数据中所占据的时隙位置。

4PPM 的编码格式为: 00 对应 1000; 01 对应 0100; 10 对应 0010; 11 对应 0001, 一帧 PPM 数据由帧头 SOF

(0111)、n 个字节的数据以及帧尾 EOF(1101)组成, 一般每帧数据有 1 到 16 个字节, 而且两帧数据之间的时间间隔是任意的。

表 1 PPM 数据帧格式

|           |        |        |     |           |

|-----------|--------|--------|-----|-----------|

| SOF(0111) | 一个字节数据 | 一个字节数据 | ... | EOF(1101) |

|-----------|--------|--------|-----|-----------|

本设计中, 首先每 16 个时钟周期采集 1 位 PPM 信号(din), 所以需要一个 16 位的计数器 count0; 解码 2 bit 需要采到 4 位 din 信号, 因此需要一个 3 位的计数器 count1; 完成一个完整的 8 位信号, 需要解码 2 bit 数据 4 次, 所以还需要一个 3 位的计数器 count2。其次, 用移位寄存器将输入的 8 位数据进行暂存以便对其进行读取, 与此同时, 输出的 8 bit 数据是 2 bit 数据输出累加到 8 bit, 所以也需要移位寄存器对输出数据进行暂存。设计一个 4 位寄存器 reg1 对输入的数据进行移位操作, 一个 8 位寄存器 reg2 对输出的数据进行暂存, 等待 8 bit 移满, 就进行数据的输出; 最后需要设计一个状态机来判断是否进行解码, S0 表示没有收到帧头, 处于未工作状态; S1 表示收到帧头, 开始进行解码。图 7 是 PPM 解调 Verilog

图 7 PPM 解调 Verilog 流程图

图 5 4PPM 调制 RTL 级图

图 6 4PPM 调制仿真

流程图。

在 PPM 解调过程中, 将最后解调出的数据以 8 位数据的形式进行数据的输出, 所以需要一个 8 位寄存器对数据进行缓存, 等 8 位数据移满后将数据输出。其主要代码如下所示:

```

case(reg1)

d_00:reg2<={2'b00,reg2[7:2]};

d_01:reg2<={2'b01,reg2[7:2]};

d_10:reg2<={2'b10,reg2[7:2]};

d_11:reg2<={2'b11,reg2[7:2]};

default:reg2<=reg2;

endcase

```

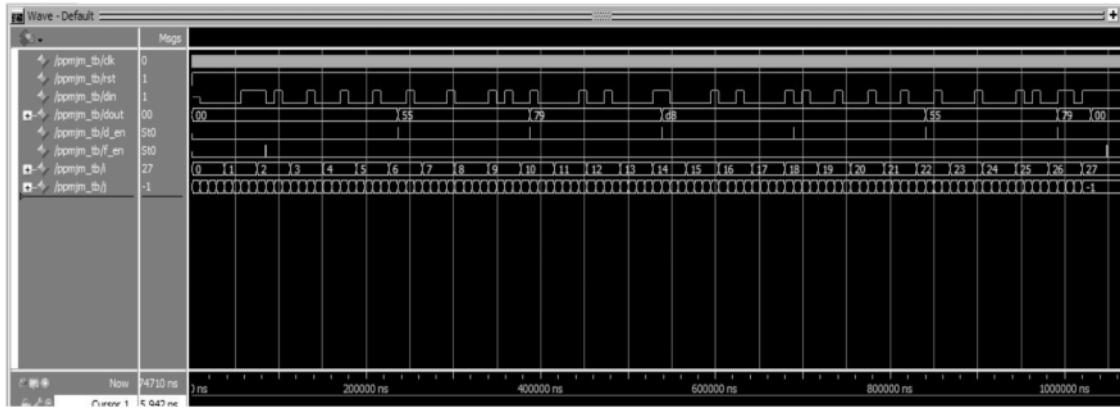

### 3.2 PPM 解调仿真

在进行 PPM 解调系统的仿真之前, 首先需要编写测试文件, 然后将各个模块加入到工程中<sup>[3]</sup>。测试文件通过读取 "F:/PPM1.txt" 的文件中的数据作为 PPM 脉冲数据输入到解调系统中, 其中 PPM 脉冲输入数据如图 8 所示, 4PPM 解调仿真图如图 9 所示。

```

PPM1.txt - 记事本

文件(F) 编辑(E) 格式(O) 查看(V) 帮助(H)

0000 //无效输入

0111 //帧头

0100 //01

0100 //01

0100 //01

0100 //01"输出数据0101_0101; 55

0100 //01

0010 //10"

0001 //11"

0100 //01"输出数据0111_1001; 79

1000 //00"

0010 //10"

0100 //01"

0001 //11"输出数据1101_1000; d8

1000 //00"

0010 //10"

0100 //01"

0001 //11"输出数据1101_1000; d8

0100 //01"

0100 //01"输出数据0101_0101; 55

0100 //01"

0010 //10"

0001 //11"

0100 //01"输出数据0111_1001; 79

1101 //帧尾

```

图 8 PPM 脉冲输入数据

图 9 4PPM 解调仿真图

由图 9 可以看出, 解调出来的数据为 0x55、0x79、0xd8、0xd8、0x55、0x79, 与输入的数据一致, 而且输出的数据都是在输出数据有效标志位高电平之后输出下一个字节的数据。由此验证了代码功能的正确性。

### 4 CRC 生成器及 CRC 校验

在红外数据传输过程中, 由于存在较多的干扰源, 因此数据传输的过程中容易发生错误。采用 CRC 校验进行差错控制, 可以比较正确可靠地实现红外数据传输<sup>[4]</sup>。首先将 A/D 转换后的数据生成 CRC 码, 将 CRC 码加入到 A/D 转换后的数据后面一起进入到调制模块, 将调制出来的 PPM 数据经过发射电路发送出去, 之后将红外接收头接收到的数据进行 CRC 码校验。这样可以保证红外传输部分的数据更加可靠。本设计将 CRC 校验码的 Verilog 实现方法展现出来。

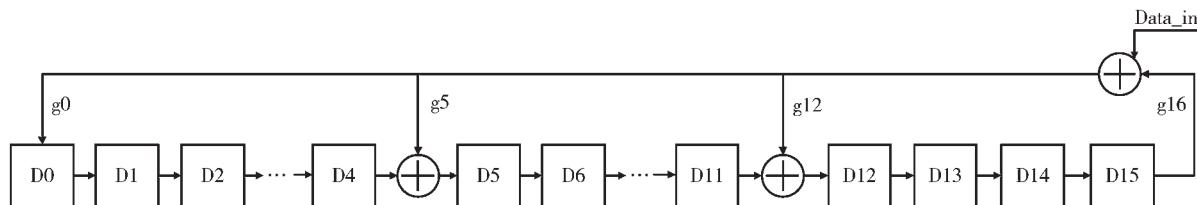

由于 CRC-CCITT 的生成多项式  $G(X)$  为  $x^{16}+x^{12}+x^5+1$ , 输入数据用多项式表示为  $C(X)$ , 将  $C(X)$  左移  $R$  位, 用  $C(x) \times 2^R$  除以生成多项式  $G(x)$  得到的余数就是校验码<sup>[7]</sup>。根据 CRC 校验码的生成原理, 采用模二除法在程序设计中得到 CRC 码。其结构图如图 10 所示。在接收侧的 CRC 校验是一边接收数据一边进行校验, 当把数据都接收完毕后, 最终得出的 CRC 校验码与固定的 CRC 值进行比较, 如果两者相同则接收到了正确的数据, 反之则接收到的数据有误。

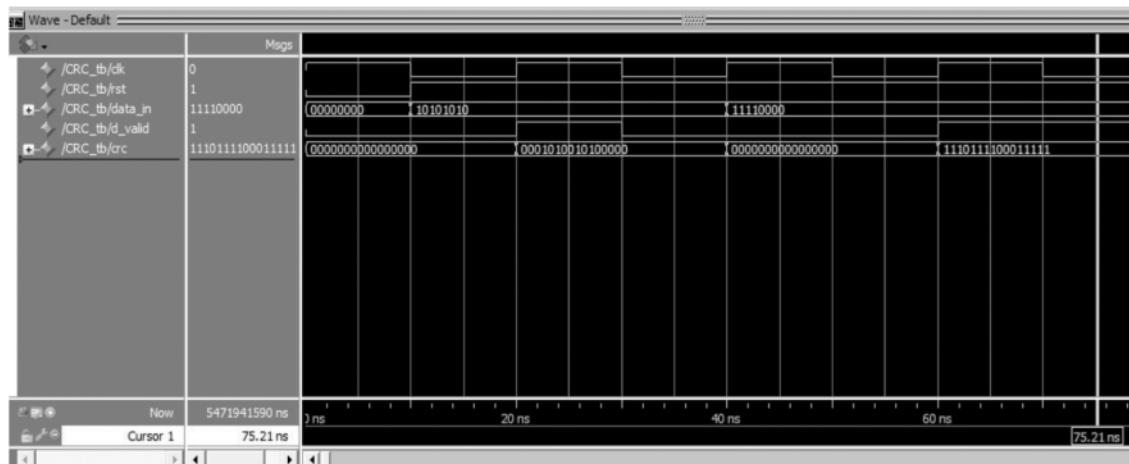

在测试文件中输入数据为 10101010 和 11110000, 最终得到的 CRC 码生成器仿真结果如图 11 所示, 为 0001010010100000 和 111011100011111, 与用理论计算结果一致, 因此确定了此电路设计的可行性。

### 5 结论

本文通过研究 PPM 调制解调的原理, 设计了基于 FPGA 的 PPM 调制解调系统, 详细论述了调制解调系统的程序设计原理以及 CRC 校验码的实现。用 Verilog HDL 硬件描述语言编写了 PPM 调制代码、PPM 解调代码和 CRC 校验代码, 并在 Modelsim 中进行了联合仿真, 从仿真结果可以看出 PPM 调制解调系统设计的正确性。加入了 CRC 校验, 提高了后续实际应用中数据传输

图 10 CRC 电路结构图

图 11 CRC 码生成器仿真图

的可靠性。

实际应用中与仿真必定会有偏差，在后续实用化中还需要对其进行完善与改进。

参考文献

- [1] 王明军,王大伟,崔博.风电机组齿轮箱损坏及防护措施[J].

风能产业,2014(4):26-29.

- [2] 何攀,李晓毅,侯倩,等.基于 FPGA 的 PPM 调制解调系

统设计[J].现代电子技术,2010,33(9):52-54.

- [3] 陈铁.基于 FPGA 无线光通信 PPM 调制解调的设计[J].

信息技术,2015(2):151-154.

- [4] 方俊,吕杨.基于纠错码的红外数据传输[J].云南大学学

报(自然科学版),2009(S1):88-90.

- [5] 朱乐君,张江鑫.基于 FPGA 的无线光通信 PPM 调制系统

的设计[J].光通信技术,2006(12):59-61.

- [6] 李一兵,雷洪玉,殷潜.基于 CPLD 的 PPM 调制与解调系

统设计[J].信息技术,2004(1):71-72.

[7] 蒋冠宇,蒋泰,邓家明.一种超高频RFID读写器的设计与实现[J].大众科技,2015(2):6-9.

- [8] 隆志远,陈仁文,朱莉娅.一种基于 FPGA 的旋转机械非接触双向红外信号传输系统的实现[J].传感技术学报,2011,24(4):559-563.

- [9] 丁德强,柯熙政.大气激光通信 PPM 调制解调系统设计与仿真研究[J].光通信技术,2005(1):50-52.

- [10] 仵宗钦,刘鹏.基于 FPGA 的高速脉冲位置调制激光通信系统设计[J].激光杂志,2015(8):124-127.

(收稿日期:2020-10-09)

作者简介

侯欢(1994-),女,硕士研究生,主要研究方向:嵌入式技术、无线数据测试及传输、风电机齿轮箱应力测试。

施洪生(1975-),男,博士,副教授,主要研究方向:油液磨粒在线测试技术开发、风机齿轮箱应力测试与寿命评估等。

[View Details](#) | [Edit](#) | [Delete](#)

(上接第 91 页)

- [7] REHMAN M U, CHEN X, PARINI C G, et al. Evaluation of a statistical model for the characterization of multipath affecting mobile terminal GPS antennas in sub-urban areas[J]. IEEE Transactions on Antennas and Propagation, 2011, 59(1): 60-67.

(2): 1084–1094.

(收稿日期:2020-07-07)

#### 作者简介：

周文辉(1982-),男,硕士,工程师,主要研究方向:电子对抗试验。

## 版权声明

经作者授权，本论文版权和信息网络传播权归属于《电子技术应用》杂志，凡未经本刊书面同意任何机构、组织和个人不得擅自复印、汇编、翻译和进行信息网络传播。未经本刊书面同意，禁止一切互联网论文资源平台非法上传、收录本论文。

截至目前，本论文已经授权被中国期刊全文数据库（CNKI）、万方数据知识服务平台、中文科技期刊数据库（维普网）、DOAJ、美国《乌利希期刊指南》、JST 日本科技技术振兴机构数据库等数据库全文收录。

对于违反上述禁止行为并违法使用本论文的机构、组织和个人，本刊将采取一切必要法律行动来维护正当权益。

特此声明！

《电子技术应用》编辑部

中国电子信息产业集团有限公司第六研究所