# 应用于导航 SoC 的专用 DMA 的设计 \*

秦爽<sup>1,2</sup>, 李健<sup>1</sup>, 杨颖<sup>1</sup>, 陈杰<sup>1</sup>

(1. 中国科学院微电子研究所, 北京 100029; 2. 中国科学院大学, 北京 100049)

**摘要:** 卫星导航技术以及社会的快速发展使得高精度定位的需求越来越大。随着导航系统和频点的增加, 导航模块中需要处理的数据量越来越大。通用 DMA(Direct Memory Access)控制器无法完成大量通道的传输, 采用中央处理器(CPU)传输需要占用 CPU 大量的时间。应用于导航片上系统(SoC)的专用 DMA 支持全系统全频点的导航通道的数据搬移, 经过测试验证, DMA 搬移相同通道数的数据所需要的时钟周期为 CPU 的三分之一, 有效提高了 CPU 的效率。在设计中采用了低功耗优化技术, 优化后 DMA 模块动态功耗降低至原来的 15%。

**关键词:** 导航; SoC; DMA

中图分类号: TN492

文献标识码: A

DOI: 10.16157/j.issn.0258-7998.200909

中文引用格式: 秦爽, 李健, 杨颖, 等. 应用于导航 SoC 的专用 DMA 的设计[J]. 电子技术应用, 2021, 47(3): 27–30.

英文引用格式: Qin Shuang, Li Jian, Yang Ying, et al. Design of dedicated DMA applied to navigation SoC[J]. Application of Electronic Technique, 2021, 47(3): 27–30.

## Design of dedicated DMA applied to navigation SoC

Qin Shuang<sup>1,2</sup>, Li Jian<sup>1</sup>, Yang Ying<sup>1</sup>, Chen Jie<sup>1</sup>

(1. Institute of Microelectronics of the Chinese Academy of Sciences, Beijing 100029, China;

2. University of Chinese Academy of Sciences, Beijing 100049, China)

**Abstract:** The rapid development of satellite navigation technology and society has made the demand for high-precision positioning increasingly large. With the increase of navigation systems and frequency points, the amount of data that needs to be processed in the navigation module is increasing. The general DMA(Direct Memory Access)controller cannot complete the transmission of a large number of channels, and the transmission using the CPU requires a lot of CPU time. The dedicated DMA applied to the navigation system on chip(SoC) supports the data movement of the navigation channel of the whole system and the whole frequency point. After testing and verification, the clock cycle required by the DMA to move the same channel number of data is one-third of the CPU One, effectively improving the efficiency of the CPU. Low-power optimization technology is used in the design, after optimization, the dynamic power consumption of the DMA module is reduced to 15% of the original.

**Key words:** navigation; SoC; DMA

## 0 引言

随着社会的发展, 卫星导航已经广泛应用到人类社会的很多方面, 如无人机、物联网、车辆导航以及物流等<sup>[1]</sup>, 对导航定位的精度要求也越来越高。目前的导航 SoC 主要采用 CPU 来完成导航模块的数据搬移工作, 随着导航系统和频点的增加, 搬移大量导航通道的数据将占用 CPU 大量的时间。而且 CPU 频繁地轮询检测各个通道的状态将使 CPU 的低功耗设计变得极为复杂。梁科等人设计了一款通用 DMA, 该 DMA 能有效提高数据传输效率, 但是它最多支持 8 个通道, 无法满足导航应用要求<sup>[2]</sup>。张路煜等人设计的 DMA 使用了专用数据通路, 虽然避开了 AHB 总线, 能进行多路并行传输, 但是会使

SoC 内部时序复杂<sup>[3]</sup>。本文设计了一种专用于导航 SoC 的 DMA, 它能高效的完成大量通道的数据搬移<sup>[4–11]</sup>。

## 1 导航 SoC 系统

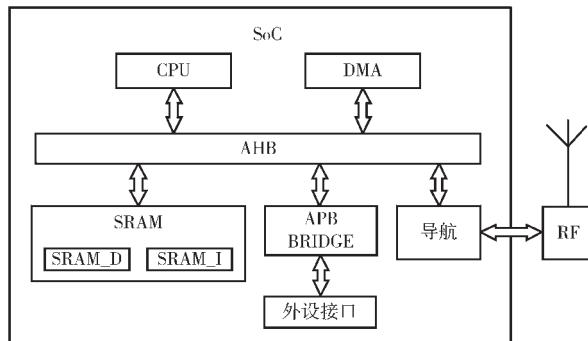

基于先进微控制器总线体系结构(Advanced Microcontroller Bus Architecture, AMBA)总线的导航 SoC 总体结构图如图 1 所示。

导航 SoC 主要包括处理器、DMA、存储模块、导航模块以及外设接口。各 IP 核之间通过 AMBA 总线进行通信, 其中处理器、DMA、存储模块和导航模块通过高级高性能总线(Advanced High Performance Bus, AHB)协议通信, 外设接口连在外围总线(Advanced Peripheral Bus, APB)上。四大全球卫星导航系统各有几十颗卫星, 每颗卫星会发射多个频点的信号。随着导航 SoC 支持的信号增加, 导航模块需要搬移和处理的数据也越来越多, 支持全系统

\* 基金项目: 国家重点研发项目(2019YFB2204200)

图 1 导航 SoC 总体结构

全频点的导航 SoC 需要处理数百个通道的数据。通用 DMA 无法支持数百通道的数据搬移,而传统的 CPU 搬移数据方式效率会越来越低。本设计中采用的专用 DMA 可以不经过 CPU 直接将导航通道中的数据搬移到静态随机存取存储器(Static Random-Access Memory, SRAM)中,这样 CPU 可以直接读取 SRAM 中的数据进行处理。

DMA 主要完成导航通道中两类数据的搬移工作,一类是跟踪模块中相干累加值,相干累加值 1 ms 更新一次,这类数据的传输称为 DUMP 传输。CPU 根据相干累加值的计算结果调节跟踪环路的参数。另一类是用于伪距和载波观测值,此值更新频率为 1~20 Hz,这类传输称为 TIC 传输。CPU 根据观测量计算用户的时间、位置、速度等信息。DUMP 和 TIC 均有标志位,当标志位有效时表示数值已更新。为了保证数据不缺失,每隔 0.1 ms 轮询检测所有信号所有通道的 DUMP 标志位,如果标志位有效,则搬移该通道 DUMP 数据。同样,每隔 2 ms 检测 TIC 标志位,如果标志位有效,则 DMA 将完成所有信号所有通道的 TIC 数据的搬移。

## 2 专用 DMA 设计

### 2.1 专用 DMA 总体结构

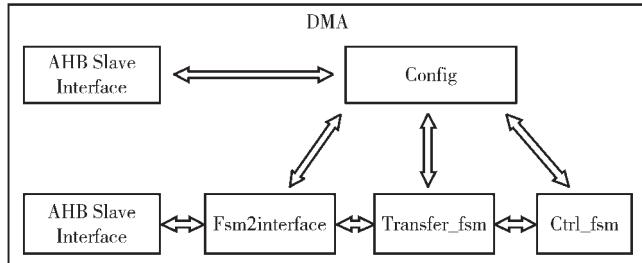

专用 DMA 的总体结构如图 2 所示。

图 2 专用 DMA 总体结构

专用 DMA 主要由 AHB 主机接口、AHB 从机接口、配置模块、控制状态机、传输状态机以及状态机转接口六个部分组成。在 AHB 总线上,DMA 既是主机又是从机。它通过 AHB 主机接口读写导航模块数据并将其存储到 SRAM 中,而处理器通过 AHB 从机接口对 DMA 进

行配置。配置模块将处理器的配置寄存并分发到其他各个模块。控制状态机和传输状态机主要负责控制 DMA 的数据搬移。状态机转接口模块主要负责数据缓存和提供总线数据和地址。

在 DMA 的 RTL 级代码设计过程中使用低功耗设计方法。常用的低功耗设计技术有并行处理、流水线、资源共享、操作数隔离以及门控时钟等方法。在 DMA RTL 代码设计过程主要使用了资源共享和门控时钟的低功耗优化方法<sup>[12~14]</sup>。

### 2.2 配置模块

DMA 的工作状态可以由处理器进行配置。DMA 是否工作以及工作时进行哪些通道的数据检测和搬移都可以通过处理器进行配置。

处理器对 DMA 的配置数据经过 AHB 从机接口进入 DMA 之后先在配置模块进行寄存,然后由配置模块分发到其他各个部分。处理器也可以通过读取特定地址来获取当前 SRAM 的写入地址。

### 2.3 控制状态机

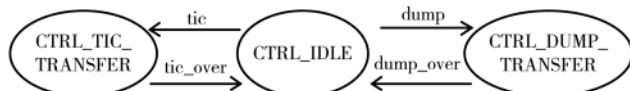

控制状态机主要控制 DMA 进入不同的传输模式,总共有三个状态,CTRL\_IDLE 表示初始状态或者正在等待,CTRL\_DUMP\_TRANSFER 表示正在进行 DUMP 传输,CTRL\_TIC\_TRANSFER 表示正在进行 TIC 传输,状态转移图如图 3 所示。

图 3 控制状态机状态转移图

此模块中有两个计数器,一个 DUMP 计数器,一个 TIC 计数器,这两个计数器用来计算等待时间。每隔 0.1 ms 进行一次 DUMP 传输,即进入 CTRL\_DUMP\_TRANSFER 状态。每隔 2 ms 进行一次 TIC 传输,即进入 CTRL\_TIC\_TRANSFER 状态。其他时候在 CTRL\_IDLE 状态进行等待。

### 2.4 传输状态机

当控制状态机控制 DMA 进行 DUMP 或者 TIC 传输之后,传输状态机开始工作。它控制 DMA 进行不同的检测和传输工作。

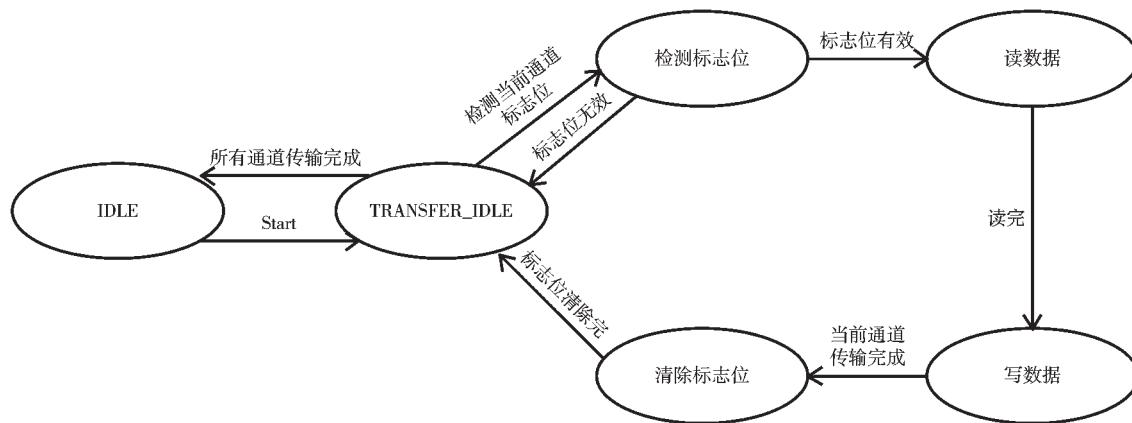

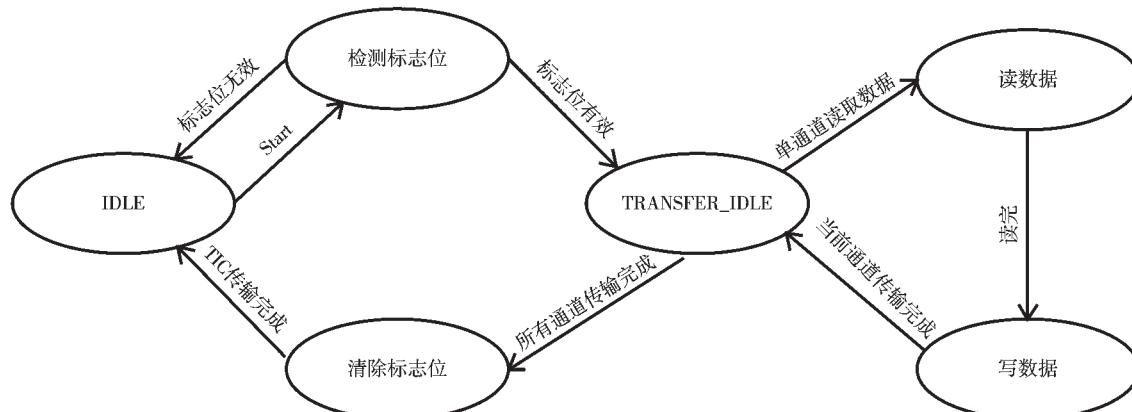

对于 DUMP 模式,状态机转移图如图 4 所示。DMA 将轮询检测导航模块中的各个通道的标志位,如果标志位有效,则将该通道的数据搬移到 SRAM 中,并清除该通道的标志位,然后继续检测下一通道。如果标志位无效,则不进行任何操作,继续检测下一个通道。如果所有的通道全部检测并传输完毕,则传输状态机向控制状态机发送完成信号,控制状态机进入 CTRL\_IDLE 状态,等待下一次传输。

对于 TIC 模式,状态机转移图如图 5 所示。DMA 将先检测 TIC 标志位,如果标志位有效,则将导航模块中

图 4 DUMP 模式时传输状态机状态转移图

图 5 TIC 模式时传输状态机状态转移图

所有开启的通道中 TIC 数据搬到 SRAM 中，传输完成后清除 TIC 标志位。如果 TIC 标志位无效或者所有通道上数据传输完成，则传输状态机向控制状态机发送完成信号，退出 TIC 传输状态。

## 2.5 AHB 接口

DMA 模块有两个 AHB 接口，一个主机接口，一个从机接口。DMA 通过主机接口经过 AHB 总线读取导航模块的数据，将其缓存到移位寄存器中，待写状态时将数据写到挂载在 AHB 总线上的 SRAM 中。从机接口使 DMA 可以作为 AHB 总线上的从机，这样 CPU 就可以通过 AHB 总线对 DMA 寄存器进行配置<sup>[15]</sup>。

## 3 测试

DMA 模块使用 Verilog 语言编写，采用 TSMC 90 nm 工艺进行综合验证。时钟约束为 200 MHz，面积为 40 345  $\mu\text{m}^2$ 。使用 Primetime PX 工具进行功耗分析，在 DMA 设计过程中，使用了低功耗设计方法，其中寄存器插入时钟门控电路的比例为 99.41%。表 1 为优化后与优化前功耗对比。

由表 1 可知低功耗优化方法使 DMA 模块的功耗降低至 15%。

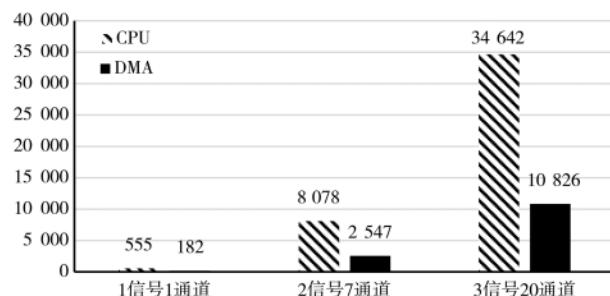

在导航 SoC 中对 DMA 模块进行数据搬移测试。CPU1 分别对 GNSS 模块和 DMA 模块进行配置使其进行不同通道数的数据搬移，另外采用 CPU1 直接搬移相同配置

表 1 低功耗优化与非低功耗优化 DMA 模块功耗对比 (mW)

|                     | 低功耗优化    | 非低功耗优化                 |

|---------------------|----------|------------------------|

| Net Switching Power | 0.021 65 | $4.110 \times 10^{-7}$ |

| Cell Internal Power | 0.266 9  | 2.191                  |

| Cell Leakage Power  | 0.057 58 | 0.064 01               |

| Total Power         | 0.346 1  | 2.255                  |

的导航数据作为对比。测试结果如图 6 所示。

图 6 不同配置下数据搬移周期对比

由于 GNSS 模块与 AHB 总线不在同一个时钟域，因此 DMA 和 CPU 在读取 GNSS 模块数据时需要进行握手操作，因此读取一个 GNSS 模块中的数据需要花费 10 个

周期。在计算 CPU 搬移数据所需要的周期时不考虑进入中断和中断返回的开销。由图 6 可知, 相同通道数的配置下, DMA 搬移数据所需要的周期数为 CPU 的三分之一, 且 DMA 在进行数据搬移的过程中不需要 CPU 的干预, 这样就提高了 CPU 的工作效率。

4 结论

本文实现了一款应用于导航 SoC 的专用 DMA，该 DMA 支持全系统全频点导航通道的数据搬移。与传统的 CPU 搬移数据方法进行比较，数据搬移所需要的周期降为 CPU 的三分之一，提高了 CPU 的工作效率。设计中采用了低功耗设计方法，使功耗降低为原来的 15%。

## 参考文献

- [1] 《卫星应用》编辑部.2019年中国卫星应用若干重大进展[J].卫星应用,2020(1):8-13.

- [2] 梁科,李国峰,王锦,等.通用多通道高性能 DMA 控制器设计[J].天津大学学报,2008(5):621-626.

- [3] 张路煜,李丽,潘红兵,等.SoC 系统中多端口 DMA 控制器的设计[J].电子测量技术,2014,37(9):32-36.

- [4] 张美迪,马胜,雷元武.基于 AXI 协议的 DMA 接口的设计与验证[C].第二十一届计算机工程与工艺年会暨第七届微处理器技术论坛论文集,2017:10.

- [5] 张路煜.支持并行传输的多端口 DMA 控制器设计[D].南京:南京大学,2014.

- [6] 吴瑶裔.基于 AMBA 总线的 DMA 控制器的设计[D].长沙:湖南大学,2012.

- [7] HUANG Z,ZHANG S,GAO H,et al.A configurable multiplex data transfer model for asynchronous and heterogeneous

(上接第 26 页)

- [7] WANG R J , Li Xiang , LING C X , et al. Pelee : a real-time object detection system on mobile devices[C]. Conference on Neural Information Processing Systems. arXiv : 1804.06882 , 2018.

- [8] ZHANG J N , ZHOU J J , WU J F , et al. SDChannelNets : extremely small and efficient convolutional neural networks[J]. IEICE Transactions on Information and Systems , 2019 , 102 (12) : 2646–2650.

- [9] MA N , ZHANG X , ZHENG H T , et al. Shufflenet V2 : practical guidelines for efficient cnn architecture design[C]. Proceedings of the European Conference on Computer Vision (ECCV) , 2018.

- [10] BOTTOU L , CURTIS F E , NOCEDAL J. Optimization methods for large-scale machine learning[J]. SIAM Review , 2016 , 60(2) : 16M1080173.

- [11] SUTSKEVER I , MARTENS J , DAHL G , et al. On the importance of initialization and momentum in deep learning[C]. Atlanta: International Conference on Machine Learning , 2013 : 1139–1147.

FPGA accelerators on single DMA device[J].*Microprocessors and Microsystems*, 2020, 77: 103174.

- [8] KATZ D J, GENTILE R. 嵌入式媒体处理[M]. 北京: 电子工业出版社, 2007.

- [9] 吕广秋, 李伟, 陈韬, 等. 一种面向密码 SoC 的高性能全双工 DMA 设计[J]. 计算机工程, 2020, 46(5): 167-173, 180.

- [10] 张帅. 一种支持多种传输模式的 DMA 主机模块设计与实现[D]. 长沙: 国防科学技术大学, 2014.

- [11] 王俊, 应忍冬. 嵌入式音频处理器中 DMA 控制器的设计[J]. 信息技术, 2011, 35(3): 42-46.

- [12] 姬强. 基于时钟门控技术对内存控制模块的 RTL 级功耗优化[D]. 西安: 西安电子科技大学, 2017.

- [13] 包志家. 大规模集成电路低功耗技术分析[J]. 数字通信世界, 2017(12): 63, 279.

- [14] 王凯龙. 基于通用 DMAC IP 的功耗分析及优化[D]. 西安: 西安电子科技大学, 2019.

- [15] ARM. Arm AMBA 5 AHB protocol specification[EB/OL]. (2015-10-30)[2021-01-15]. <https://developer.arm.com/documentation/ihj0033/bb/>.

(收稿日期:2020-09-18)

---

### 作者简介：

秦爽(1996-),男,硕士研究生,主要研究方向:数字集成电路设计。

李健(1981-),男,博士,副研究员,主要研究方向:超大规模集成电路设计。

杨颖(1982-),女,博士,副研究员,主要研究方向:卫星导航算法。

- [12] IOFFE S ,SZEGEDY C.Batch normalization :accelerating deep network training by reducing internal covariate shift[C]. Lille :International Conference on Machine Learning ,2015 :448–456.

- [13] SRIVASTAVA N ,HINTON G ,KRIZHEVSKY A,et al. Dropout:a simple way to prevent neural networks from overfitting[J].The Journal of Machine Learning Research ,2014 ,15(1) :1929–1958.

- [14] LEE C Y,XIE S ,GALLAGHER P ,et al.Deeply–supervised nets[C].San Diego :Artificial Intelligence and Statistics ,2015 :562–570.

- [15] SANDLER M ,HOWARD A ,ZHU M ,et al.Inverted residuals and linear bottlenecks ;mobile networks for classification, detection and segmentation[EB/OL].(2018–01–13)[2020–08–13].<http://arxiv.org/abs/1801.04381>.

(收稿日期:2020-08-13)

### 作者简介：

倪伟健(1995-),男,硕士研究生,主要研究方向:图像处理。

秦会斌(1961-),通信作者,男,教授,博士研究生导师,主要研究方向:电路与系统,E-mail:hangdian198@sina.com。

## 版权声明

经作者授权，本论文版权和信息网络传播权归属于《电子技术应用》杂志，凡未经本刊书面同意任何机构、组织和个人不得擅自复印、汇编、翻译和进行信息网络传播。未经本刊书面同意，禁止一切互联网论文资源平台非法上传、收录本论文。

截至目前，本论文已经授权被中国期刊全文数据库（CNKI）、万方数据知识服务平台、中文科技期刊数据库（维普网）、DOAJ、美国《乌利希期刊指南》、JST 日本科技技术振兴机构数据库等数据库全文收录。

对于违反上述禁止行为并违法使用本论文的机构、组织和个人，本刊将采取一切必要法律行动来维护正当权益。

特此声明！

《电子技术应用》编辑部

中国电子信息产业集团有限公司第六研究所