# 多通道低相噪同步频率源设计

胥伟, 潘明海, 张艳晴

(南京航空航天大学 电子信息工程学院, 江苏 南京 211106)

**摘要:** 针对数字射频存储器(Digital Radio Frequency Memory, DRFM)系统在进行对外部输入信号采集时, 对高稳频率源需求问题, 提出了一种基于两级锁相环的多通道低相噪同步频率源设计方法, 实现了 6 路在 2.26~2 600 MHz 范围内任意频率信号输出。通过线性叠加的方法, 理论分析了锁相环中相位噪声的模型, 并根据相位噪声的来源进行优化设计。最后对频率源电路杂散和相位噪声进行测试, 测试结果表明该频率源电路输出 1.25 GHz 频率时的杂散抑制优于 -60 dBc, 相位噪声抑制优于 -104.91 dBc/Hz@500kHz。

**关键词:** 频率源; 锁相环; 相位噪声; 杂散

中图分类号: TN95

文献标识码: A

DOI: 10.16157/j.issn.0258-7998.200921

中文引用格式: 胥伟, 潘明海, 张艳晴. 多通道低相噪同步频率源设计[J]. 电子技术应用, 2021, 47(3): 97-101, 114.

英文引用格式: Xu Wei, Pan Minghai, Zhang Yanjing. Design of multi-channel low phase noise synchronous frequency source[J]. Application of Electronic Technique, 2021, 47(3): 97-101, 114.

## Design of multi-channel low phase noise synchronous frequency source

Xu Wei, Pan Minghai, Zhang Yanjing

(School of Electronic Information Engineering, Nanjing University of Aeronautics and Astronautics, Nanjing 211106, China)

**Abstract:** In order to meet the requirement of high stability frequency source when DRFM(Digital Radio Frequency Memory) system collects external input signals, a design method of multi-channel, low phase noise synchronous frequency source based on two-stage PLL is proposed in this paper. Six channels of arbitrary frequency signal output in the range of 2.26~2 600 MHz are realized. Through the method of linear superposition, the phase noise model of PLL is analyzed theoretically, and the optimal design is carried out according to the source of phase noise. Finally, the spurious and phase noise of the frequency source circuit are tested. The test results show that the spurious suppression is better than -60 dBc and the phase noise suppression is better than -104.91 dBc/Hz@500kHz when the frequency source circuit outputs 1.25 GHz frequency.

**Key words:** frequency source; phase locked loop; phase noise; spurious

## 0 引言

DRFM 系统在产生雷达欺骗干扰回波时, 需要一个高稳定度的频率源信号用于对外部输入信号的采集与重构。作为 DRFM 系统关键技术之一, 频率源一旦出现偏差, 整个系统将无法正常工作。当前, 最主要的频率源产生技术包括直接数字合成<sup>[1-2]</sup>以及锁相环频率合成<sup>[3-4]</sup>, 直接数字合成技术一般结构相对复杂, 且很容易输出较高的杂散<sup>[5]</sup>, 而锁相环技术相对已比较成熟, 且在设计时会考虑加入环路滤波器, 因此能有效地过滤相位噪声。此外, 锁相环技术频率源电路的结构较为简单, 且能输出低相噪、高稳定度的频率信号<sup>[6]</sup>。本文将采用锁相环频率合成技术进行设计。

## 1 锁相环的基本原理

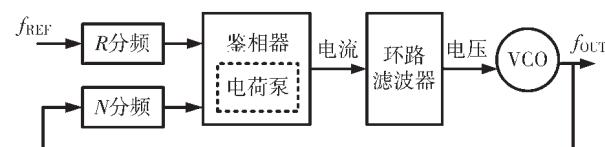

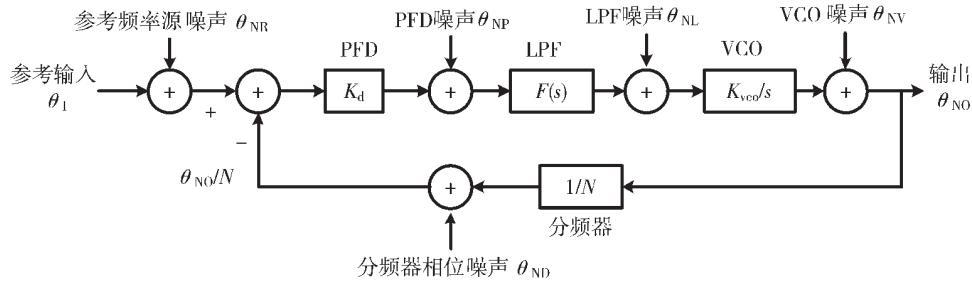

负反馈系统的锁相环通常由鉴相器、电荷泵、环路滤波器、压控振荡器(VCO)、分频器等组成<sup>[7]</sup>, 如图 1 所示。鉴相器对经过 R 分频的参考频率信号与经过 N 分

图 1 锁相环工作原理框图

频的锁相环输出信号进行比较并产生两者的相位误差信号; 电荷泵将相位误差信号转变为与此成比例的电流信号; 低通环路滤波器对电荷泵输出电流积分以产生对应的电压信号; VCO 根据输入电压信号输出对应的频率<sup>[8-9]</sup>。

## 2 锁相环相位噪声理论分析

### 2.1 相位噪声的定义

锁相环稳定工作时, 其自身的非线性效应能有效抑制输出信号振幅波动, 但是其相位波动无法抑制。因为相位波动的存在, 锁相环输出信号在时域上的过零点间

隔不再均匀,造成频率信号的“抖动”。“抖动”的存在会使部分功率产生频偏,中心频谱周边产生的边带,即为相位噪声<sup>[10]</sup>。

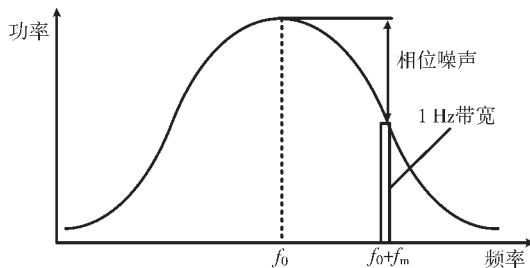

相位噪声定义为一个频偏上的噪声功率与输出信号载波功率的比值,一般将其归一化到1 Hz带宽,如图2所示,单位为dBc/Hz。则相位噪声计算公式为<sup>[11]</sup>:

$$P_{\text{noise}}(\Delta f) = 10 \log \left( \frac{P_{\text{sideband}}(f_0 + \Delta f, 1 \text{ Hz})}{P_{\text{carrier}}} \right) \quad (1)$$

图2 相位波动谱密度

## 2.2 频率源相位噪声对采样性能影响

频率源信号的性能会严重影响ADC器件,对高速信号的采集,会造成采样值严重偏离理想采样值,破坏采样的时序。

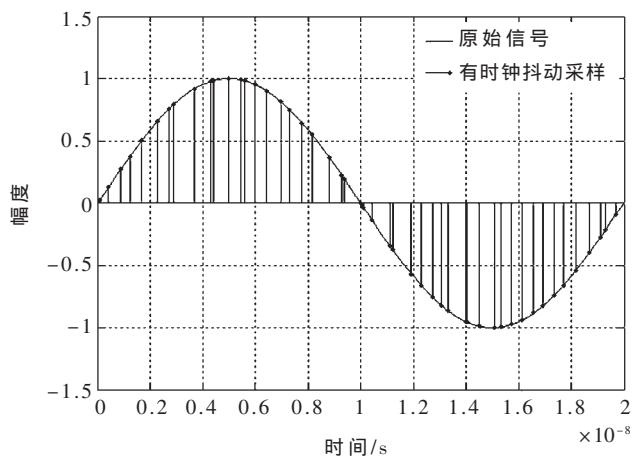

当频率源相位噪声较高时,频率源会存在随机性“抖动”,假设时钟抖动量为 $\Delta T$ ,此时的频率源信号为:

$$s(t)_{\text{jitter}} = A_s \sin(2\pi f_s(t + \Delta T)) \quad (2)$$

采样时刻会发生一定的随机偏移,偏移量为 $\Delta T$ ,此时的采样位置不再确定,ADC器件对输入信号进行非均匀采样,采样输出如图3所示。

图3 有相位噪声时钟采样

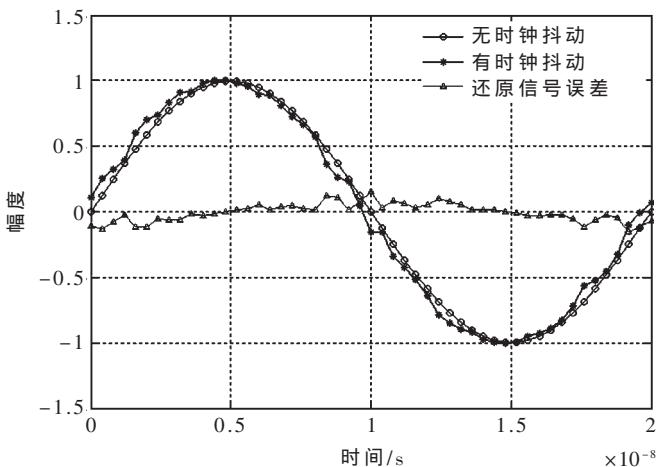

数据采集完成以后,若以无“抖动”的频率源重构采样信号时,结果如图4、图5所示。

从时域图4中可以得出,信号重构时出现了明显的畸变。从频域图5中可以得出,信号杂散性能显著恶化。如果采用更高的采样速度,那么由抖动时钟引入的噪声将更加明显。因此在ADC采样系统孔径抖动确定时,一

图4 均匀频率时域重构

图5 均匀频率频域重构

个高稳定度的频率源是系统稳定性的重要保证。

## 2.3 锁相环相位噪声理论

锁相环系统是一个非线性的系统,但是当锁相环的鉴相器频率为环路带宽的10~20倍时,可将其近似认为是一个线性系统<sup>[12]</sup>。线性系统条件下通过传输函数分析各个模块对整个环路相位噪声产生的影响。假设锁相环路中各个模块产生的是互不相关的加性噪声,锁相环噪声线性模型如图6所示。

该锁相环路的开环增益为:

$$H(s) = \frac{K_d K_{\text{vco}} F(s)}{Ns} \quad (3)$$

式中, $K_d$ 为鉴相器增益, $K_{\text{vco}}$ 为压控振荡器灵敏度, $F(s)$ 为环路滤波器的传输函数, $N$ 为分频比。

锁相环路总的相位噪声为参考频率源相位噪声、鉴相器相位噪声、环路滤波器相位噪声、压控振荡器相位噪声和分频器相位噪声的总和,即为:

$$e_{\text{NO}}(\omega) = \left[ \theta_{\text{NR}}^2 + \frac{1}{k_d^2} \theta_{\text{vco}}^2 + \theta_{\text{FD}}^2 \right] \left| \frac{NH(j\omega)}{1+H(j\omega)} \right|^2 +$$

图 6 锁相环噪声模型

$$\begin{aligned} & \left[ \frac{K_{vco}}{s} \theta_{NL}^2 + \theta_{NV}^2 \right] \left| \frac{1}{1+H(j\omega)} \right|^2 \\ & = [S_{NR}(\omega) + S_{NP}(\omega) + S_{ND}(\omega)] \left| \frac{NH(j\omega)}{1+H(j\omega)} \right|^2 + \\ & [S_{NL}(\omega) + S_{NV}(\omega)] \left| \frac{1}{1+H(j\omega)} \right|^2 \end{aligned} \quad (4)$$

由于锁相环路中采用的是低通滤波设计,故开环传递函数  $H(s)$  和闭环传递函数  $NH(s)/(1+H(s))$  都具有低通特性,而  $1/(1+H(s))$  具有高通特性。所以除了 VCO 噪声源具有高通特性外,其余噪声源都具有低通特性。对于低通特性的噪声,环路带宽越小,噪声抑制能力越强;而高通特性的噪声,环路带宽越大,噪声抑制能力越强。因此,为了均衡的抑制噪声,环路带宽选择确定在两种噪声谱密度线的交叉点。

## 2.4 各模块相位噪声模型分析

### 2.4.1 参考频率源相位噪声分析

假设一个具有相位噪声的正弦波时钟信号为:

$$x(t) = A \sin(2\pi f_c t + \theta(t)) \quad (5)$$

因而周期抖动可表示为  $J_d = \theta(t)/2\pi f_c$ 。

因为周期抖动噪声  $J_d << \pi/2$ ,故式(5)可简化为:

$$x(t) = A \sin(\omega_c t) + A \theta(t) \cos(\omega_c t) \quad (6)$$

因此式(6)的频谱可表示为:

$$S_c(f) = \frac{A^2}{4} [\delta(f-f_c) + \delta(f+f_c)] + \frac{A^2}{4} [\delta_\theta(f-f_c) + \delta_\theta(f+f_c)] \quad (7)$$

其中,  $\delta_\theta(f)$  是  $\theta(t)$  的频域表示。

因此可以得到时钟信号的相位噪声功率谱密度函数为:

$$S_{NR}(\omega) = \frac{\pi A^2}{4} [\delta_\theta(\omega - \omega_c) + \delta_\theta(\omega + \omega_c)] \quad (8)$$

从式(8)看出,减小参考频率抖动,可减小输出信号相位噪声。

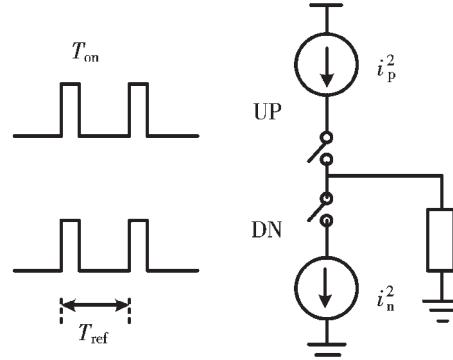

### 2.4.2 鉴相器等效输出相位噪声

鉴相器等效噪声模型如图 7 所示。

$$i_o(t) = i_p(t) \times UP(t) + i_n(t) \times DN(t) \quad (9)$$

由于式(9)中两项原理相同,故取其中一项进行分析,并对其取傅里叶变换可得:

$$S_p(f) = S_{ip}(f) * S_{UP}(f) \quad (10)$$

$$S_{ip}(f) = a + \frac{1}{|f|^\beta} \quad (11)$$

图 7 鉴相器等效噪声模型

$$S_{UP}(f) = \sum_{n=-\infty}^{+\infty} a_n^2 \delta(f - nf_{ref}) \quad (12)$$

$$a_n = \frac{\sin(n\omega_{ref} T_{on}/2)}{n\pi} \quad (13)$$

$$S_p(\omega) = a \cdot \sum_{n=-\infty}^{+\infty} a_n^2 + b \cdot \sum_{n=-\infty}^{+\infty} \frac{a_n^2}{|\omega - nf_{ref}|^{2\beta}} \quad (14)$$

从上式得出,提高鉴相器频率  $f_{ref}$  可减小相位噪声。

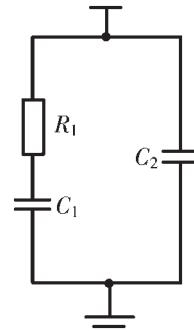

### 2.4.3 环路滤波器相位噪声分析

二阶无源环路滤波器模型如图 8 所示,电容  $C_2$  将电荷泵输出电流转换成直流电压,并通过滤除电压纹路,改善振荡器输出信号的寄生调制,同时  $R_1$ 、 $C_1$  支路能有效提高环路稳定性。

环路滤波器的开环传递函数为:

$$H_{open}(s) = \frac{K_d K_{vco} b}{N C_1} \times \frac{s + \omega_z}{s^2(s + \omega_p)} \quad (15)$$

式中  $\omega_z$  和  $\omega_p$  分别是开环传递函数的零点和极点,  $b$  是电容比,  $\omega_z = \frac{1}{R C_1}$ ,  $\omega_p = \left( \frac{C_1}{C_2} + 1 \right) \omega_z = (b+1) \omega_z$ ,  $b = \frac{C_1}{C_2}$ 。

无源二阶环路滤波器的相位噪声功率谱密度为:

$$S_{NL}(\omega) = \left| \frac{b}{b+1} \frac{1}{s/\omega_p + 1} \right|^2 \cdot 4KTRB \quad (16)$$

式中  $K$  为玻尔兹曼常数,  $T$  为温度值,  $B$  为带宽,  $R$  为电阻值。从式(16)得出,降低电阻  $R$ ,能够降低环路滤波器的相位噪声。

图 8 二阶无源环路滤波器模型

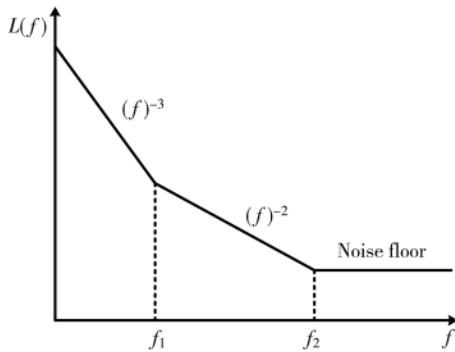

## 2.4.4 VCO 相位噪声分析

VCO 的相位噪声模型如图 9 所示,该模型主要分成三个区:与偏移频率三次方成反比的  $1/f^3$  区;与偏移频率平方成反比的  $1/f^2$  区;与偏移频率无关的噪底区。接近载波功率的  $1/f^3$  区的相位噪声在工作时会被抑制,而 VCO 的输出噪声主要来自  $1/f^2$  区。

图 9 VCO 相位噪声曲线

$1/f^2$  区相位噪声功率谱密度为<sup>[13]</sup>:

$$S_{\text{NV}}(\omega) = 10 \log \left[ \frac{2FkT}{P} \left( \frac{\pi\omega_0}{Q\omega} \right)^2 \right] \quad (17)$$

式中,  $F$  是一个实验参数, 表示的是晶体管对相噪的影响。 $k$  为玻尔兹曼常数,  $T$  为绝对温度,  $P$  为载波功率,  $Q$  为谐振腔  $Q$  值。

从式(17)看出, 提高 VCO 的载波功率, 即提高 VCO 的输出幅值, 同时降低  $K_{\text{vco}}$ , 能够降低 VCO 在  $1/f^2$  区的相位噪声。

## 2.4.5 分频器相位噪声分析

$N$  分频器可在其他条件不变的情况下改变 VCO 的输出频率, 并且可改变鉴相频率, 提高输出频率分辨率。

由于  $N$  分频存在, 输出端会引入噪声  $\theta_{\text{NO}}/N$ , 则:

$$\left( \theta_{\text{NR}} - \frac{\theta_{\text{NO}}}{N} - \theta_{\text{ND}} \right) \frac{K_d F(s) K_{\text{vco}}}{s} = \theta_{\text{NO}} \quad (18)$$

整理可得:

$$\theta_{\text{NO}} = NG(s)(\theta_{\text{NR}} - \theta_{\text{ND}}) \quad (19)$$

其中:

$$G(s) = \frac{NH(s)}{1+H(s)} \quad (20)$$

故分频器相位噪声谱密度为:

$$S_{\text{NO}}(\omega) = N^2 [S_{\theta_{\text{NR}}}(\omega) - S_{\theta_{\text{NO}}}(\omega)] G(j\omega)^2 \quad (21)$$

显然, 输出噪声因为  $N$  分频器而起到倍频的效果。在低频偏时,  $G(j\omega) \approx 1$ , 且  $S_{\theta_{\text{NR}}}$  远大于  $S_{\theta_{\text{NO}}}$ , 输出噪声会增加近  $20\log N$ 。因此  $N$  分频器的值不宜太大, 如果  $N$  太大, 可以提高输入参考频率或者多级锁相环来降低  $N$  分频带来的影响。

## 2.5 相位噪声改善措施

频率源最重要的性能指标之一就是相位噪声, 综合上述分析, 降低各模块相位噪声措施如下:

(1) 输入参考时钟: 采用高性能的恒温晶振作为参考频率源输入, 并且可采用两级锁相环的设计, 第一级锁相环在外部恒温晶振驱动下, 为第二级锁相环提供高稳、低相噪的参考时钟;

(2) 鉴相器: 提高鉴相频率可以减小输出信号相位噪声;

(3) 环路滤波器: 降低电阻  $R$ , 可减小相位噪声;

(4) VCO: 提高 VCO 的输出幅值, 降低  $K_{\text{vco}}$  能够改善其相位噪声性能;

(5) 分频器: 采用更高的频率信号作为参考时钟, 或者采用多级锁相环结构, 减小分频系数  $N$ , 以改善分频器的相位噪声性能。

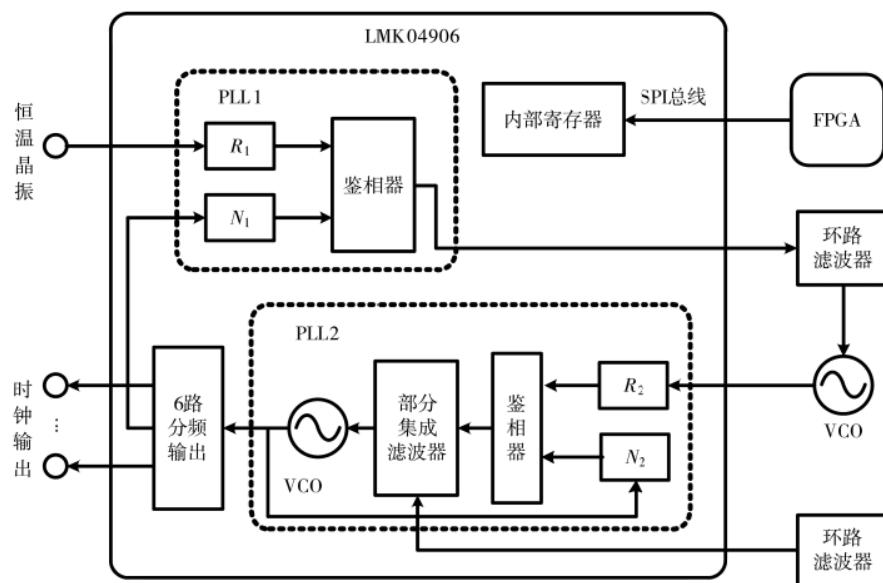

## 3 频率源器件选型与方案设计

本频率源设计最核心的器件是锁相环芯片, 该器件选用 TI 公司的时钟管理芯片 LMK04906, 它具有双锁相环结构, 可工作于双锁相环和单锁相环两种模式, 能实现 6 路差分或者 12 路单端在 2.26~2 600 MHz 范围内的任意同步频率输出, 相位检测器速率可达 155 MHz, 相位噪声底低至 -227 dBc/Hz, 能够保证高稳频率信号的输出。

控制器采用一片 Xilinx Spartan-6 FPGA 芯片通过 SPI 总线完成 LMK04906 芯片内部寄存器的配置。

参考输入是外部给 PLL 的参考时钟信号, 该信号会直接影响输出信号的性能, 故采用高稳定度的恒温晶振作为参考输入。

本设计采用两级锁相环结构, 如图 10 所示, 增加第一级锁相环的目的是为第二级锁相环提供高稳定度、低相噪的参考频率。第一级锁相环的环路滤波器为保证恒温晶振输入的性能而采用窄带设计, 第二级锁相环的环路滤波器为保证 VCO 输出相噪性能而采用宽带设计。在此结构下, 频率源可输出多路与参考输入同相位的信号。

## 4 实验测试结果

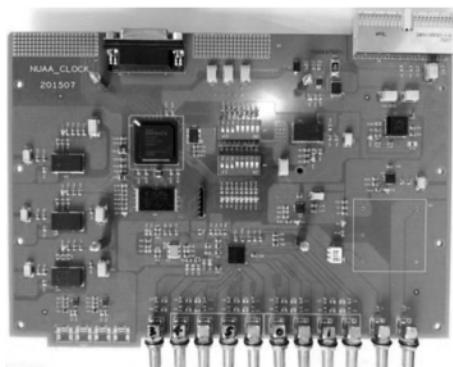

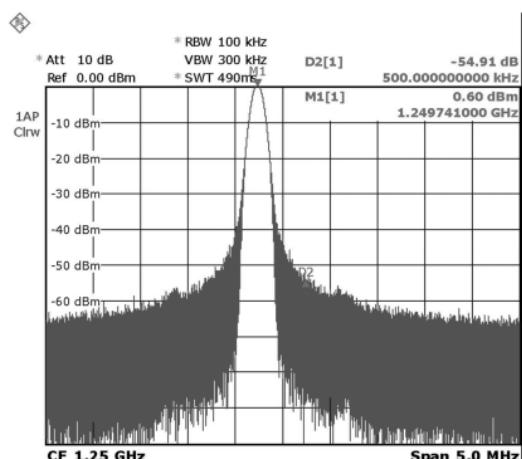

多通道同步频率源设计采用 6 阶 PCB 层叠设计, 实物加工板卡如图 11 所示。

通过罗德与施瓦茨的频谱仪 FSL6 对设计的频率源电路输出信号进行杂散和相位噪声测试分析, 实测采用高稳定度、低相噪的 10 MHz 恒温晶振作为第一级锁相环的参考频率输入。

PLL2 环路带宽内基底相位噪声由式(22)估算可得<sup>[14]</sup>:

$$N_f = N_{\text{@1Hz}} + 20 \log N + 10 \log f_{\text{pdf}} \quad (22)$$

式中,  $N_{\text{@1Hz}}$  表示 PLL2 的归一化相位噪声底, LMK04906 器件  $N_{\text{@1Hz}}$  的值为 -227 dBc/Hz;  $N$  表示分频系数;  $f_{\text{pdf}}$  表示鉴相频率。

根据相位噪声改善措施进行优化设计, 设置  $N$  分频为 250,  $f_{\text{pdf}}$  为 10 MHz, 则频率源基底相位噪声理论值为<sup>[15]</sup>:

$$\begin{aligned} N_f &= -227 + 20 \log 250 + 10 \log 10 000 000 \\ &= -109.42 \text{ dBc/Hz} \end{aligned} \quad (23)$$

图 10 频率源设计方案

图 11 频率源硬件实物图

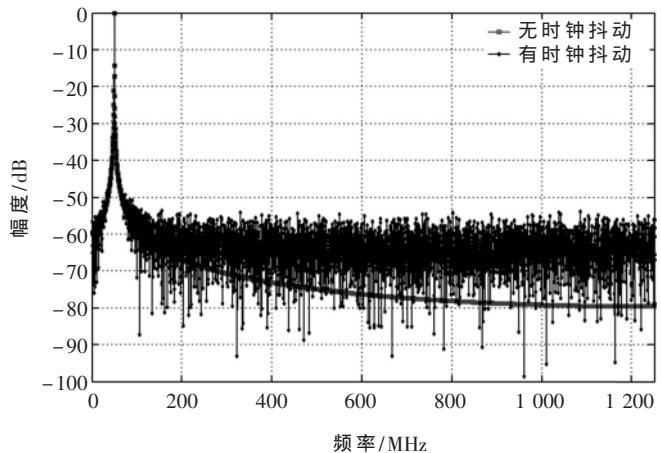

从实际测试结果图 12 看出,当频率源电路输出中心频率为 1.25 GHz 信号时,频率信号杂散抑制优于-60 dBc/Hz,在 500 kHz 频偏处的相位噪声为:

$$\begin{aligned} N(500 \text{ kHz}) &= -54.91 - 10 \log(\text{RBW}) \\ &= -104.91 \text{ dBc/Hz} \end{aligned} \quad (24)$$

图 12 频率源 1.25 GHz 输出频谱

相位噪声的实测值与基底相位噪声理论值接近,偏差部分可能来自频率源电路中外部噪声输入引起的恶化。

## 5 结论

本文针对数字射频存储系统中,对 ADC 采样频率源的实际需求,设计出基于两级锁相环技术的频率源电路,能够实现 2.26~2 600 MHz 范围内任意频率信号的输出,且根据实验测试结果表明,该频率源输出信号在稳定性、低相噪方面具有非常优异的性能,完全满足本系统的设计指标,具有切实的应用价值。同时,该频率源电路成本低、控制灵活,为雷达电子对抗等诸多领域提供了一个高性能的频率源解决方案。

## 参考文献

- [1] 汤衡, 何善亮, 陈杨. 一种改进超四算法的 DDS 设计[J]. 电讯技术, 2020, 60(3): 344~349.

- [2] 杨阳, 陶建中, 万书芹, 等. 基于精确频率控制字的高速 DDS 电路设计与实现[J]. 电子设计工程, 2020, 28(3): 5~8, 13.

- [3] Zou Wei, Ren Daming, Zou Xuecheng. A wideband low-jitter PLL with an optimized Ring-VCO[J]. IEICE Electronics Express, 2020, 17(3).

- [4] 刘琨, 李铁虎, 张俊安. 高速宽带锁相环的相位噪声影响研究[J]. 微电子学, 2019, 49(4): 467~470, 476.

- [5] 尹波, 张帅, 张新, 等. 汽车防撞雷达频率源的相位噪声分析[J]. 雷达科学与技术, 2018, 16(6): 667~670, 675.

- [6] 李璐. 低抖动宽频时钟合成模块设计[D]. 成都: 电子科技大学, 2020.

- [7] 杜云飞. 用于时钟信号发生的锁相环电路的设计[D]. 哈尔滨: 哈尔滨工业大学, 2015.

- [8] 周宇轩. 2.5GSPS 高分辨率数据采集系统时钟电路设计[D]. 成都: 电子科技大学, 2016.

- [9] 邹勤丽. 一种高速电荷泵锁相环的设计与实现[D]. 上海: 上海交通大学, 2014.

- [10] Liu Li, Liu Yangguang, Zhang Xiaomin, et al. Low phase noise and quasi-tunable millimeter-wave generator using a passively InAs/InP mode-locked quantum dot laser[J]. Optoelectronics Letters, 2020, 16(6).

- [11] 沈晓唯. 锁相环环路滤波器对输出信号相位噪声的影响[D]. 上海: 上海交通大学, 2009.

- [12] 李炜. 锁相环电路的设计及相位噪声分析[D]. 天津: 天津大学, 2005.

- [13] 汪瀚. 基于锁相环结构的频率综合器芯片电路设计[D]. 合肥: 中国科学技术大学, 2014.

(下转第 114 页)

验大纲要求的 10%，满足固化等效模型参数的要求。将期望试验 1 和期望试验 2 的截获接收机灵敏度代入等效模型后，可分别得到被截获距离为 4.1 km 和 29.5 km。

### 3 结论

本文研究的雷达被截获距离的等效模型方法已应用于某型雷达的低截获性能评估和鉴定考核中。利用了机场地面和空中试飞的多次试验数据，通过迭代优化的方式，建立了被截获距离的等效模型。被截获距离等效模型的正确性、可行性已在实际试验中得到了初步的检验。等效模型具有一定的通用性，可推广应用到数据链等射频信号的被截获距离测试。在等效模型的推导过程中，各种系统损耗和大气衰减需要准确测算和标定，必要时需要单独进行建模和验证。下一步，需要在更多的试验实践中进行数据积累，完善等效模型，提高模型的准确度。

### 参考文献

- [1] VANKAYALAPATI N, KAY S. Asymptotically optimal detection of low probability of intercept signals using distributed sensors[J]. IEEE Transactions on Aerospace and Electronic Systems, 2012, 48(1): 737–748.

- [2] 王国玉, 汪连栋, 阮祥新, 等. 雷达对抗试验替代等效推算方法与模型[C]. 中国电子学会电子对抗分会第十二届学术年会论文集, 2001: 199–205.

- [3] KOOKAMARI F H, NOROUZI Y, NAYEBI M M. Using a moving aerial platform to detect and localise a low probability of intercept radar[J]. IET Radar Sonar & Navigation, 2017, 11(7): 1062–1069.

- [4] SACHIN A R, AMBAT S K, HARI K V S. Analysis of intra-pulse frequency modulated low probability of interception radar signals[J]. Sadhana, 2017, 42(7): 1–14.

- [5] TANG B, TANG J, PENG Y. Low probability of interception of an advanced noise radar waveform with Linear-FM[J]. IEEE Transactions on Aerospace and Electronic Systems, 2013, 49(2): 1351–1356.

- [6] VANHOY G, SCHUCKER T, BOSE T. Classification of LPI radar signals using spectral correlation and support vector machines[M]. Kluwer Academic Publishers, 2017.

- [7] 韩俊, 陆晓飞, 吕明久, 等. 相位编码调频步进信号及其性能分析[J]. 雷达科学与技术, 2018, 16(4): 371–377.

- [8] 谢飞, 周德召, 胡磊力, 等. 红外搜索跟踪系统探测距离缩比测试方法[J]. 电光与控制, 2019, 26(4): 90–94.

- [9] 赵晔, 张丹萌, 曹屹. 海面电磁缩比测量的替代模型[J]. 探测与控制学报, 2017, 39(3): 26–31.

- [10] 赵辉. 预警机雷达天线辐射特性的缩比模型测试法[J]. 微波学报, 2014(S1): 318–321.

- [11] PHILLIP E P. Detecting and classifying low probability of intercept radar (Second Edition)[M]. Artech House, Boston and London, 2009.

- [12] 李品, 窦泽华. 时差无源定位测高性能分析[J]. 现代雷达, 2019(8): 38–40.

- [13] 史忠亚, 吴华, 沈文迪, 等. 考虑射频隐身的雷达功率自适应管控方法[J]. 现代雷达, 2017, 39(10): 6–10.

- [14] 曾小东. 机载雷达高度表被截获性能分析[J]. 现代雷达, 2019, 41(6): 20–22.

- [15] HUA W U, ZHONG Y S, WEN D S, et al. Radar LPI performance assessment method based on extended G-GIFSS algorithm[J]. Systems Engineering and Electronics, 2017, 39(6): 1256–1260.

(收稿日期: 2020-09-04)

### 作者简介:

曾小东(1985-), 男, 硕士, 高级工程师, 主要研究方向: 信号与信息处理、航空电子与射频隐身。

(上接第 101 页)

- [14] 代传堂. 一种宽带低相噪频率合成器的设计方法研究[J]. 电波科学学报, 2018, 33(6): 746–751.

- [15] 宋雪莹, 崔永俊, 张祥, 等. 基于 DDS+PLL 的低相噪频率合成器设计[J]. 电子器件, 2019, 42(4): 947–952.

(收稿日期: 2020-09-21)

### 作者简介:

胥伟(1995-), 男, 硕士, 主要研究方向: 射频系统设计与仿真。

潘明海(1962-), 男, 博士, 教授, 博士生导师, 主要研究方向: 射频仿真与信号处理。

张艳晴(1997-), 女, 硕士, 主要研究方向: 雷达信号识别与分选。

## 版权声明

经作者授权，本论文版权和信息网络传播权归属于《电子技术应用》杂志，凡未经本刊书面同意任何机构、组织和个人不得擅自复印、汇编、翻译和进行信息网络传播。未经本刊书面同意，禁止一切互联网论文资源平台非法上传、收录本论文。

截至目前，本论文已经授权被中国期刊全文数据库（CNKI）、万方数据知识服务平台、中文科技期刊数据库（维普网）、DOAJ、美国《乌利希期刊指南》、JST 日本科技技术振兴机构数据库等数据库全文收录。

对于违反上述禁止行为并违法使用本论文的机构、组织和个人，本刊将采取一切必要法律行动来维护正当权益。

特此声明！

《电子技术应用》编辑部

中国电子信息产业集团有限公司第六研究所