# 混合集成技术代际及发展研究\*

朱雨生<sup>1</sup>,施 静<sup>2</sup>,陈 承<sup>1</sup>

(1.中国电子科技集团公司第四十三研究所 微系统安徽省重点实验室,安徽 合肥 230088;

2.陆军炮兵防空兵学院,安徽 合肥 230039)

**摘要:**混合集成技术是一种将零级封装直接组装封装为1~3级封装模块或系统,以满足航空、航天、电子及武器装备对产品体积小、重量轻、功能强、可靠性高、频率宽、精密度高、稳定性好需求的高端封装技术。从20世纪70年代至今,混合集成技术历经了从厚薄膜组装到多芯片组件(MCM)、系统级封装(SiP)、微系统集成等阶段。它始终专注于微观器件与宏观器件的联结,是一种融合设计、材料、工艺、工程、实验的多学科持续创新技术。通过分析研究不同时期混合集成技术的工艺特征、技术要点和典型产品,通过归纳与总结首次提出混合集成技术代际划分,同时根据不同代际的技术特征与趋势,对下一代混合集成技术的发展方向进行预测。

**关键词:**混合集成电路;混合集成技术;厚薄膜工艺;微系统;代际

中图分类号: TN452

文献标识码: A

DOI:10.16157/j.issn.0258-7998.200869

中文引用格式: 朱雨生,施静,陈承. 混合集成技术代际及发展研究[J]. 电子技术应用, 2021, 47(4): 36–45.

英文引用格式: Zhu Yusheng, Shi Jing, Chen Cheng. Research on intergenerational and development of hybrid integration technology[J]. Application of Electronic Technique, 2021, 47(4): 36–45.

## Research on intergenerational and development of hybrid integration technology

Zhu Yusheng<sup>1</sup>, Shi Jing<sup>2</sup>, Chen Cheng<sup>1</sup>

(1.The 43rd Research Institute of CETC, Anhui Key Laboretory of Microsystems, Hefei 230088, China;

2.Army Artillery Air Defense Academy, Hefei 230039, China)

**Abstract:** Hybrid integration technology is a kind of high-end packaging technology that directly encapsulates zero level devices into 1~3 level modules or systems to meet the requirements of small volume, light weight, strong function, high reliability, wide frequency, high precision and good stability for aerospace, electronic and weapon equipment. Since the 1970s, hybrid integration technology has gone through the stages from thick/thin film assembly to multi chip module(MCM), system level packaging(SiP), micro system integration and so on. It always focuses on the connection between micro-devices and macro-devices, which is a continuous innovation technology of multi-disciplinary integration for design, material, technics, project, experiment. In this paper, by analyzing and studying the process characteristics, key points and typical products of hybrid integration technology in different periods, the development of hybrid integration technology is divided into four generations by induction and summary. Meanwhile, according to the technical characteristics and trends of different generations, it also tries to predict the development direction of the next generation of hybrid integration technology.

**Key words:** hybrid integrated circuit; hybrid integration technology; thick/thin film; system in package; generations

## 0 引言

混合集成电路(HIC)原定义是由半导体集成工艺与厚膜(包括LTCC/HTCC,下同)/薄膜工艺结合而制成的集成电路,按GJB-2438《混合集成电路通用规范》:“由两个或两个以上下列元件的组合,并且其中至少有一个是有源器件:(a)膜集成电路;(b)单片集成电路;(c)半导体分立器件;(d)片式、印刷或淀积在基片上的无源元件。”<sup>[1]</sup>混合集成技术即为实现混合集成电路的技术。相

对于单片集成电路,它设计灵活,工艺方便,便于快速研制、多品种小批量生产;并且其元件参数范围宽、精度高、稳定性好,可以承受较高电压和较大功率。但随着基于硅基TSV技术引发的3D IC变革、日渐成熟SoC技术领域快速扩张、PCB级产品的组装密度和可靠性提升、低成本和商业化消费电子的突飞猛进,混合集成电路传统优势不断被挑战,所以混合集成技术也在不断进步和发展,已远超出厚薄膜电路范畴,但也带来了涵义和内容的模糊化。第一、二代混合集成技术已经建立从设计、材料、工艺到后续封装、试验、应用等十分完善的

\* 基金项目: 国防科工局基础科研项目(CKY201910B006)

技术体系,其典型指标(线宽/线间距、多层层数、I/O密度)基本稳定;而三、四代技术(功能一体化封装、3D组装、微纳组装)正在突飞猛进。为了迎合不断发展的信息装备小型化、轻量化、高速化、多功能化的市场需求,混合集成技术也在升级换代,以更好地发挥灵活、快速、低成本、实用性强的技术优势。混合集成技术是电子技术的一个分支,工艺技术与产品应用本身具有一体两面性,所以混合集成的代际发展与电子科技的五次技术浪潮<sup>[2]</sup>(微电子学、射频/无线、光电子学、MEMS、量子器件)两者相辅相成,互相促进形成今天的电子行业。

## 1 混合集成电路技术代际发展

混合集成技术本质上是一种高集成度、高性能和高可靠的先进封装技术,它由设计、仿真、集成、制造、检测技术构成,自20世纪60年代以来,形成了一、二、三代技术,并正向第四代发展。通过混合集成技术可以有效地解决一、二、三代半导体材料不兼容问题;解决运算、存储、射频、光电、MEMS、传感等半导体工艺不兼容问题;大幅提升产品质量与寿命,是有源、无源器件和功能器件实现高密度、小型化与高可靠的一体化封装手段。

总的来说,混合集成技术的发展历程是功率密度、组装密度、集成密度、功能性、可靠性等不断发展提升的过程;也是实现代表品种不断推陈出新,功能提升再提升的过程,更是满足不同时期高新武器装备需求的过程。

### 1.1 第一代混合集成电路技术

20世纪六七十年代开始,由于军事和宇航工业领域的迫切需求,在厚薄膜电路的基础上,开展了基于厚薄膜基板的混合集成电路研制,以实现电子设备的微型化。混合集成电路(HIC)就是来源于该形态,指以厚薄膜基板为承载,在基板上集成阻容器件,然后将其他分立无源元件和有源元件芯片(主要是成品)进一步组装到基板上形成的电路。第一代混合集成电路的整体特征可以归结为成品芯片、非气密封装、焊接工艺、有源和无源混装等特点。第一代混合集成电路相对当时的单片封装具有较大提升,而且建立了早期混合集成电路的基本特征。第一代混合集成代表产品有点火器、电源等,典型性能是:功率密度约为5 W/in<sup>3</sup>,组装密度为40 IO/cm<sup>2</sup>,使用寿命为10年左右。由于处于可靠性技术建立初期,体系化的可靠性技术未建立,也没有气密性封装要求。第一代产品相对同时期其他封装,具有集成度高、功率大、体积小的特征。目前依然有少量民品供应商采用第一代混合集成电路技术生产加热、点火、传感等功率或特种电路产品。图1所示为第一代混合集成技术代表产品HLS DC-DC变换器<sup>[3]</sup>。

### 1.2 第二代混合集成技术

第一代混合集成技术满足了当时的需求,但在集成密度和可靠性上优势不明显,在其基础上结合裸芯片组装工艺和金属气密封装工艺的发展,混合集成电路开始向第二代转变。第二代混合集成电路产品出现在20世

图1 第一代混合集成技术代表产品(HLS DC-DC 变换器)

纪80年代,发展于90年代,成熟于21世纪初期;采用的典型工艺有多层厚膜基板、裸芯片组装、多芯片焊接、金丝/铝丝键合、激光无源/有源调阻、气密封装等。主要是通过厚薄膜工艺进步实现线宽/线间距降低、布线层数的大幅增长;采用裸芯片工艺减少组装面积;采用全金属气密封装提升可靠性。典型产品(如DC/DC变换器)功率密度约为43 W/in<sup>3</sup>,组装密度为200 IO/cm<sup>2</sup>,使用寿命约为18年。

#### 1.2.1 多层厚膜基板技术

随着介质及通孔材料的发展,厚膜(含LTCC/HTCC)由单层布线向厚膜多层布线发展,通过叠层交联、通孔填充等技术实现了多层电路的互联,同时导体的线宽/线间距大幅下降,部分工艺与半导体工艺技术同步发展。通过多层厚膜技术发展为后续裸芯片组装等打下基础。通常在二代混合集成技术体系中表面印刷厚膜可以满足10层布线;线宽/间距100 μm/100 μm;LTCC/HTCC厚膜满足50层布线;线宽/间距75 μm/75 μm、通孔直径75 μm。

#### 1.2.2 裸芯片组装技术

裸芯片是封装的最小尺寸,采用裸芯片直接组装可以大幅减少组装面积,提升组装密度,从而减小产品的尺寸及重量。尤其是多个裸芯片贴装及键合到一个腔体内效果更加显著,混合集成技术正是由于引入具有最小芯片体积的裸芯片而得到了快速的发展及应用。通常在二代混合集成技术体系中采用裸芯片组装比采用成品器件可以减少50%面积和70%的重量。

#### 1.2.3 多芯片焊接技术

由于混合集成技术核心是有源和无源的一体化封装,内部器件相对较多,组装工艺要求高。裸芯片多芯片焊接以及基板和芯片多层次一次焊接技术是重要工艺;通过采用热风回流焊、推板回流焊、红外回流焊等,可以满足多芯片焊接要求,实现关键器件75%以上焊接面积;结合陶瓷基板高导热系数对产品的功率密度提升显著。难点是基板类器件与芯片类器件之间的体积差大于100倍,不同基板导热系数差距大于10倍;再加上焊料厚度差异和可观的一次焊接数量,都对混合集成的焊接提出苛刻要求;所以多芯片多器件多层次一次焊接是二代混合集成技术代表性技术之一。

#### 1.2.4 金丝/铝丝键合技术

金丝热压超声键合和铝丝超声键合是与裸芯片工艺

配套的工艺技术,二代混合集成重点是通过设备和工艺优化在混合集成电路中实现多芯片键合参数的兼容性,多线径、金丝/铝丝、楔焊/球焊的集成,通过25~500 μm这种宽范围的线径,基本覆盖了产品内部互联的需求,大幅提升了混合集成技术的灵活性与兼容性,是技术能力重要体现之一。通常在二代混合集成技术体系中键合工序为关键工序,采用SPC统计过程控制,CPK>1.33。

### 1.2.5 激光无源/有源调阻技术

在二代混合集成技术中一般采用激光代替砂轮或喷砂方式调阻,提高了效率和精度,提升了技术适应性。更加重要的是混合集成产品内部的厚膜电阻是集成在基板上的,不用披釉和封装,可以进行二次调阻;所以激光有源调阻在产品组装完成后进行二次修调,通过对产品加电同时对预设电阻进行精密修调,可以直接改变产品参数精度,进一步消除了各分立器件波动误差形成的累积误差,降低了因裸芯片无法全性能测试和元器件自身精度范围对最终产品的影响,是集成器件数量大幅提升同时保障最终产品一致性的关键。通常二代混合集成产品的输出精度可以修调至电压2‰、电流5‰、频率5‰。

### 1.2.6 全金属气密封装技术

随着混合集成电路应用于各种苛刻的环境,对于可靠性要求不断提高,并需要满足小型化导热、防潮、抗震需求,气密性封装成为混合集成技术标准工艺之一,尤其是全金属气密封装几乎是二代混合集成电路的标准配置。主要封口方式有:平行缝焊、储能焊、锡封焊等;气密封装为裸芯片等内部器件提供了良好环境,是产品长期可靠性的重要保障;并且满足了机械支撑和质量追溯的要求。通常在二代混合集成技术体系中密封性要达到 $R_1 \leq 5 \times 10^{-3} \text{Pa} \cdot \text{cm}^3/\text{s}(\text{He})$ 内部水汽含量<5 000 ppm,这是产线重要能力指标<sup>[4]</sup>。

### 1.2.7 混合集成技术标准建设

随着第二代混合集成技术的发展,我国的混合集成技术发展迎来了重要里程碑——GJB2438—1995《混合集成电路通用规范》发布实施,其中明确规定了K、H等产品质量保证等级,尤其是H级军标工艺基线奠定混合集成发展的基石。随后于2003年又发布了GJB2438A—2002《混合集成电路通用规范》,再一次把混合集成的内涵和定义明确阐述。

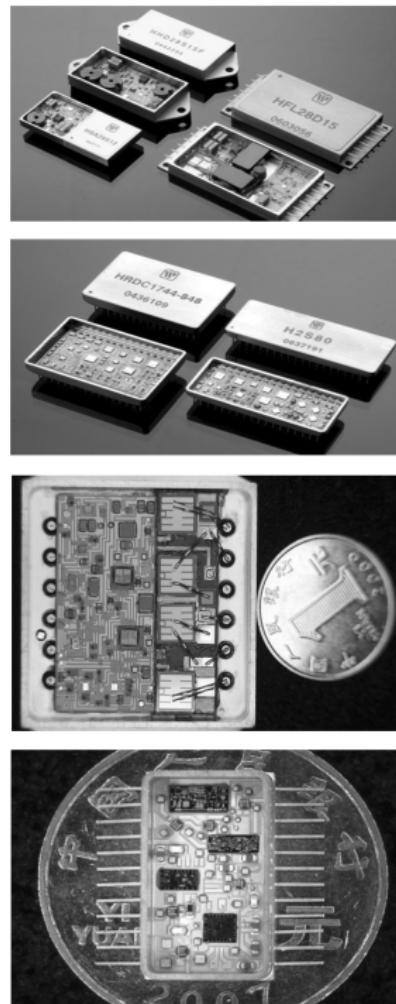

第二代混合集成技术开始普遍采用EDA软件进行设计和辅助生产,也开展了部分类型的仿真和产品数字化,这也是二代产品的特征之一。同时在设备数控化、生产线贯标、筛选检验等方面都建立了完善的体系,自二代混合集成电路技术真正形成了一套流程化、规范化、制度化的体系。部分代表产品如图2所示。

第二代混合集成技术依然是当前混合集成技术的主要技术组成,其产品占据混合集成的主流,大量应用于高可靠的功率电路、精密电路、其他电路等,仅其代表产品军用DC/DC及滤波器、脉宽调制器、基准源和精密

图2 第二代混合集成技术代表产品

(DC/DC 变换器、轴角转换器、调宽和 T/R)

变换器的年产量已超过50万只,在民品方面汽车控制、IGBT等用量更是极大。并且由于其典型性特征,第二代混合集成往往被认为是混合集成的全部,这是外界的误解。但是不可否认二代混合集成技术奠定了技术特征,目前依然广泛应用于市场上各类产品,未来也将是新一代混合集成的重要组成。

### 1.3 第三代混合集成技术

随着武器装备发展需求的不断提升,混合集成技术向着多工艺融合、更高密度集成、高频高效、一体化和高可靠发展,进而产生第三代混合集成技术。第三代混合集成产品发展于21世纪初期,目前已相对成熟。其主要特征表现为MCM-C/D多层布线、一体化封装、射频与MEMS器件、梯度温度焊接、金带/铝带键合、激光气密封装、数字化设计仿真、K级生产过程控制和超长储存寿命等。产品的典型参数有功率密度约为75 W/in<sup>3</sup>,组裝密度达到500 IO/cm<sup>2</sup>,使用寿命可以达到32年<sup>[5]</sup>。

#### 1.3.1 MCM-C/D 一体化封装技术

LTC/C/HTCC与薄膜工艺结合作为封装载体,可以实

现多层布线与高密度互连布线融合,同时也有利于制作各种不同用途的腔体。这样形成的一体化封装实现了高密度集成、寄生电容和电感减少、信号耗损减少,有利于信号的高速传输,并改善其高频性能<sup>[6]</sup>,最终实现更高的密度、更强的功能、更多的I/O、更低的功耗、更小的延迟、更快的速度的系统性能<sup>[7]</sup>。陶瓷一体化封装的尺寸相对全金属气密封装可以减少30%以上,这类封装已经大量应用到无线通信、雷达、卫星通信方面,例如美国F-22战斗机有源电扫阵列由采用LTCC制作的2 000个低功率X波段收/发(T/R)组件构成<sup>[8]</sup>。

### 1.3.2 射频与MEMS器件

第三代混合集成技术重要需求之一是射频与MEMS产品。射频芯片(Radio Frequency, RF)是能发射高频交流变化电磁波的芯片,它具有功率大、频率高、对组装界面敏感等特征,一般采用二、三代半导体材料,表面有空气桥构件等,它与功分器、放大器、环形器共同组成射频电路。微机电系统(Micro Electro Mechanical Systems, MEMS)是集成了电子电路和机械部件的微型系统,将处理热、光、磁、化学、生物等新兴结构和器件通过微电子工艺及其他微加工工艺制造在芯片上,并通过与电路的集成和相互间的集成来构筑复杂的微型系统,它与运算、存储、通信器件共同组成MEMS电路。这类功能性裸芯片因其自身特征,芯片须采用表面非接触组装、低空洞焊接、低应力粘接、高精度组装等工艺保障最终性能。通常在三代混合集成技术体系中可以覆盖100 GHz以下的频率要求,组装精度可以达到 $3\sigma \pm 15 \mu\text{m}$ 。

### 1.3.3 梯度温度焊接技术

采用工艺温度由高到低方式进行产品组装是通用性工艺要求,也是业界的共识;但是由于混合集成技术面向的是大量有源和无源器件在一个封装体的集成,而且器件种类多,封装结构复杂;研制生产又是小批量、多品种模式,所以梯度温度焊接作为一种保障可实施性和组装合格率的重要手段,被作为三代混合集成的重要手段,一般会采用280 °C、230 °C、183 °C三个梯度,结合共晶焊、回流焊以及新的焊接工艺如真空热风回流焊、真空气相回流焊等,能够有效保障特定芯片5%以下空洞率要求的保障。焊接层级达到4~5层,焊接器件大于300个。

### 1.3.4 金带/铝带键合技术

带状键合不是三代发展的技术,但是在三代开始普遍应用。随着产品功率与电流的增长,对于互连线的截面积要求大幅提升,而芯片厚度却在不断下降、芯片材质也有调整、导体和镀层厚度无法大幅提升。丝状键合在承流能力、弧度、高度、键合压力方面都已经不适应需求变化。结合新的工艺设备、检验能力提升,金带/铝带键合成为三代混合集成的通用工艺之一。虽然由于其形状限制,键合带相对键合丝方向灵活性较差,但它可以在键合界面不用大幅调整的情况下,通过增加键合面积

达到低压力、大功率、低弧度、多层次互联的目的。进一步说,由于带相对丝来说有更好的接触面和更小的转弯角,可以实现多芯片连续键合、多层次复合键合、包裹键合等。通常在三代混合集成技术中铝带键合通流可以达到100 A,金带宽度大于200 μm。

### 1.3.5 激光气密封装技术

由于三代混合集成电路的封装体材质、形状、尺寸和应用有较大调整,因此常规的平行缝焊等无法完全满足,采用激光缝焊成为通用工艺之一。例如铝或者铝硅材质的封装体,必须采用激光方式。异性构件的封装体越来越多,增加的加强筋和多面体必须采用激光封装。还有激光局部加热锡封工艺,以及激光加强封口工艺等。激光气密封装还包括激光检漏等新式无损检漏手段。通常在三代混合集成技术体系中激光封焊的气密性可以达到 $R_1 \leq 5 \times 10^{-5} \text{Pa} \cdot \text{cm}^3/\text{s}(\text{He})$ ,封装尺寸达到200 mm×200 mm。

### 1.3.6 数字化设计与仿真技术

随着混合集成技术的发展,内部器件和互联数量急剧提升,而且其采用的元器件、原材料和结构范围广、灵活度大,同时又是多品种、小批量生产,产品既要高可靠又无法进行大量产品反复验证,所以数字化设计与仿真的重要性越来越大。三代混合集成技术一般需要采用基于基线和IP核的数字化的设计理念和科学的过程控制;产品的一次研发成品率、直通率、批次/批量合格率等,也成为三代混合集成线体的重要指标之一。混合集成自二代生产基本实现了生产的数控化,大幅提升了产品一致性和合格率,在三代混合集成时由于元器件数量大幅增加(二代上限200只器件,三代可以达到1 000只)、互联关系增长显著,部分工序必须实施自动化生产,例如贴片、键合等只有采用自动化方可保障产品质量。

### 1.3.7 K级过程控制

混合集成重要应用领域之一是宇航应用,亦即K级产品,所以三代混合集成技术中逐渐完善宇航级(K级)组装规范要求来确保产品的可靠性。在更新的标准GJB2438B-2017《混合集成电路通用规范》中对于宇航应用也更加关注;另外国内航天重点院所制订了一些基于宇航级规范的衍生规范,如一院的LMS、五院的CAST、八院的SAST等。整体上来说,核心的控制内容有过程中X射线拍照、非破坏键合拉力、K级检验标准、多媒体记录、氦气示踪封装、宇高产线建设、加严筛选和产品不同时期指标一致性判定等。长储长寿命技术:在三代混合集成中有一个重要的技术分支,重点应用方向是战略或者长期值班无法更换的应用需求,核心指标之一是32年长期存储质量保障或125 °C 1 000 h全功率寿命老化后的产物可靠性保障。一般通过冗余设计、无机物互联、密封性提升、加严筛选和内部气氛控制等策略保障。

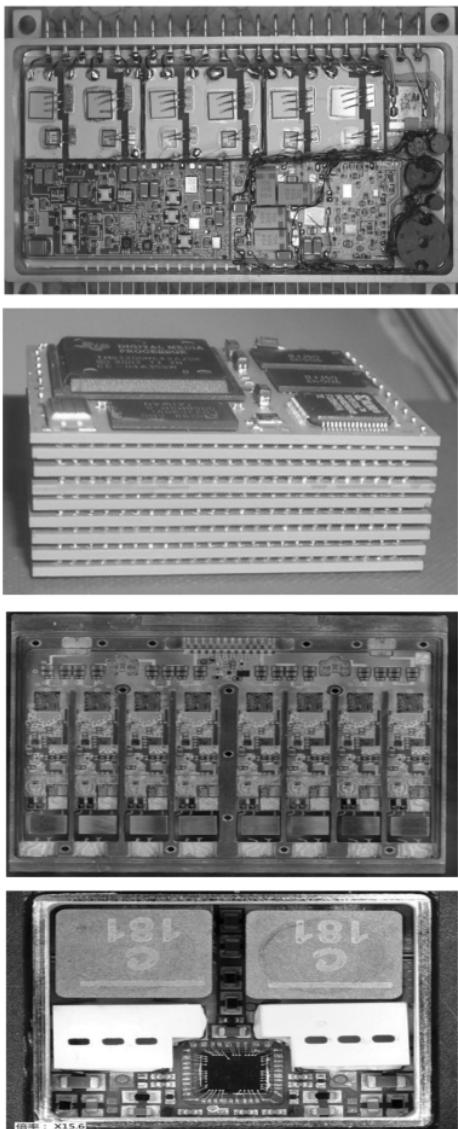

第三代混合集成技术代表产品PCU、MCM、变频组件和功率组件如图3所示。

图 3 第三代混合集成技术代表产品

(PCU、MCM、变频组件和功率组件)

混合集成技术的代际是一个继承与创新的过程,新一代的技术是在前一代的基础上进一步发展的技术平台,所以三代技术完全兼容一、二代技术,并具有新的内涵与特征。但是每一代的进步差距同样显著,也就是说没有三代技术特征的生产线无法稳定、高效地生产三代混合集成电路产品。另外在第三代混合集成技术中引入新的材料或工艺,例如多材料复合封装、抗辐照局部加固、无焊料共晶、全铜互联、结构分析等都是混合集成技术一部分,不再逐一阐述。第三代混合集成技术是当前正在大力发展的混合集成技术,就全国来看,仅仅其代表产品军用 PCU、MCM、射频和 T/R 的年产量已接近 30 万只,在民品方面汽车电子、内置助听器等用量更是极大。由于其采用的一些技术手段是二代混合集成技术中常用的,因此有些产品会被划到二代混合集成技术中,但其先进性不应该被否定。第三代混合集成技术是当前

武器装备用高端元器件的主要技术手段,在一段时期内将大力支持高新武器装备的发展。

#### 1.4 第四代混合集成技术

基于武器装备创新发展的需求,混合集成电路产品在高密度、小型化、高可靠的路径上将继续前进。随着新器件、新材料、新设备、新工艺的不断涌现,混合集成技术向着第四代稳步前进。第四代混合集成于最近几年提出,目前在各个龙头单位逐步开展研究,部分技术已经在产品中应用,也是未来各混合集成厂家竞争的核心。第四代混合集成技术面对的技术挑战包括:宽带隙功率电子器件<sup>[9]</sup>(如 GaN, Al(Ga)N, SiC, GaO, 金刚石)、新式电容器(如高密度沟槽电容器、嵌入式分立硅电容器<sup>[10]</sup>)、超级电感器(硅基微磁集成,柔性立体磁集成,低损耗内冷绕组集成)、3D 异构互联<sup>[11]</sup>(如瞬态液相烧结、纳米金属烧结<sup>[12]</sup>、芯片桥嵌入式互连 EMIB<sup>[13]</sup>、晶胞集成 Chiplet<sup>[14]</sup>等)、综合热管理(如热超材料、真空热隔离和集成微流体<sup>[15]</sup>)。第四代混合集成技术主要特征表现为功率陶瓷一体化封装、3D 打印及 IPD、倒装焊及 TSV 芯片、多维度组装、微纳级组装、激光加工技术、KGD 技术与密封前老炼、数字化工厂、全寿命周期管理等特征。产品的典型参数有功率密度 200 W/in<sup>2</sup>, 组装密度 2 000 IO/mm<sup>2</sup>, 组装精度  $3\sigma \pm 1$  微米, 组装精度, 集成密度: 300%, 使用寿命 32 年。

##### 1.4.1 功率陶瓷一体化封装

混合集成电路三代技术的陶瓷一体化封装主要是基于氧化铝陶瓷,虽然具有体积小、密度高的特点,但是由于材质自身限制,导热能力一直是个瓶颈。第四代混合集成技术结合功率陶瓷材料(主要是氮化铝)制作氮化铝基的 HTCC 多层陶瓷一体化封装,不但保有陶瓷一体化封装的优点,又大幅提升了封装导热能力,为进一步提升封装密度奠定了集成。预计四代混合集成技术封装的导热能力将超过 200 W/m.K(铜金刚石外壳可以达到 500 W/m.K),并且向着大尺寸、多维度、多腔体、高度集成发展(阻容感及射频端口和有源器件)。

##### 1.4.2 3D 打印及 IPD 技术

本文中所指的 3D 打印技术专指采用 3D 打印技术加工混合集成电路的导体、介质、电阻、瓷体、封装等;从技术发展层面来看,3D 打印技术是与混合集成技术一脉相承的,混合集成技术从传统的厚膜印刷即层加法工艺,到四代采用的 3D 打印即颗粒的加法工艺,并进一步发展至未来五代分子级加法工艺(自组装),这是技术创新越来越深入的典型特征。在混合集成中引入 3D 打印是为了四代混合集成电路内埋置、异构形、多维组装的需求,通过 3D 打印把基板、封装、结构件、微流道逐层构成,并进行有源/无源内埋置,从而大幅提升产品的集成密度与灵活性,保障第四代混合集成在功率密度和组装密度方面成倍提升。

### 1.4.3 倒装焊及 TSV 技术

按照 GJB2438B-2017 附录 D “D.5 宇航用电路的禁(限)用工艺和材料,f)禁止使用倒装芯片组装工艺。” ,倒装焊在混合集成电路中应用还待进一步推进,其担心的倒装焊质量和多余物问题都可以通过改进工艺和方法避免,未来倒装焊应该是高密度和多维集成的重要手段。尤其是基于金凸点的热压超声倒装焊,具有组装密度高、灵活性强、稳定性高和无需焊剂的特点,是四代混合集成的重要工艺手段。其中凸点制作一般采用芯片键合植球、基板电镀凸点、晶圆电镀凸点等工艺;焊接采用热压超声或者回流焊。硅通孔 TSV(Through Silicon Via)技术是三维堆叠的核心,目前 TSV 技术应用集中在晶圆级,分立器件也在混合集成电路中应用,TSV 与倒装焊技术结合可以成倍提升组装密度。研究认为在四代混合集成技术中 TSV/TGV、RDL、Find-out、Flip-Chip 都将作为高密度组装的手段得到广泛应用,在新的结构下这些技术的结合,将会保障混合集成成为 SoC 的可靠替代解决方案<sup>[16]</sup>。

### 1.4.4 多维度组装

为实现系统小型化,将大量传统 CMOS 电路、SiC 电路、GaAs 电路、SiGe 电路或者光电子器件、MEMS 器件以及各类无源元件集成到一个封装体内以实现整机系统功能,使单芯片封装进入系统级集成封装就是混合集成微系统 SIP。例如把传感器、MEMS 器件等功能器件与中央处理器(CPU)、数字信号处理器(DSP)、现场可编程门阵列(FPGA)、存储器(Memory)、射频前端、模拟前端、混合信号等集成电路有序地集成在一起,形成强大的混合集成 SIP<sup>[17]</sup>。当在单双面组装面积不够时,组装必然向着多层、多维度方向发展,立体、多面、多腔即是必然需求。在第四代混合集成技术多维度组装中作为一个常规工艺存在。由此也引入集成密度概念替代组装密度,集成密度:通过测量产品内部各个器件(含内部集成)的面积尺寸  $A_i$ ( $i$  表示器件序号),计算出所有器件应占面积

$\sum A_i$ ,将所有器件应占面积之和  $\sum A_i$  与基板有效总投影面积  $C$  作比,即可得产品的集成密度。一般而言四代混合集成 SIP 的集成密度应达到 300%;通过多维度组装大幅提升了混合集成的组装密度也赢得了发展空间,但是也提出了一系列的新挑战,如分立器件检验有效性、多器件一次组装合格率、满足军用级产品环境试验应力等。

### 1.4.5 微纳级组装

随着四代混合集成技术的发展,在产品中开始集成 MEMS 和光学器件。部分 MEMS 器件需要进行多维度组装,并且保证组装精度以实现其功能,包括 X、Y、Z 三个方向的精度、平整度、旋转度等,同时还需要保障组装应力、固化应力、使用应力、筛选应力的稳定。另外由于 MEMS 器件对于阻力很敏感,应提供大尺寸的真空封装等。光电器件(含激光器)需要保障光纤、透镜、光器件的光

路一致性,不论组装或者后续应力影响光路都会导致耦合度的大幅下降,所以其组装设计和精度必须系统设计,尤其在耦合时需要进行微纳级调整,一般而言在特定器件上应满足  $3\sigma \pm 1 \mu\text{m}$  组装精度。其他要求如光学器件的免清洗组装(在单片向混合集成转变时很重要)、激光局部焊接技术、阵列式热沉等,都是实现其功能的通用技术。

### 1.4.6 激光加工技术

激光作为热板、红外、热风的替代具有控制精度高、操作自动化、灵活性强、适应性强、非接触等优点。例如:激光增材封焊技术,适用铝硅外壳和铝碳化硅材料这种因材料特征无法采用常规的平行缝焊或储能焊的外壳,利用激光加热金锡球,喷焊到指定结构的焊缝,通过金锡焊料填缝满足封装要求,具有适应性强、灵活度高、焊接厚度深、机械强度大的特点。其他还有激光倒装焊设备,用于微系统产品返工返修可以精密局部加热,进行单个器件的拆解和再焊接。LTCC/HTCC 导体激光刻蚀技术,通过导体激光修蚀提升布线密度及线条分辨率满足高密度、高频率应用。选择性激光熔化(SLM)技术,在封装体或电流上制作特定器件或结构件。激光加工技术早早地作为调阻、划片与混合集成技术紧密结合,新代际中更将在激光增材和精细加工方面共谱新篇章。

### 1.4.7 KGD 技术与密封前老炼

已知好芯片(Know Good Die,KGD)与产品密封前老炼技术的提出时间都比较早,但是在真正应用方面一直未全面推广。一方面是由于技术本身的原因,如裸芯片老化的保护、晶圆全性能测试和过程防护,密封前产品老化的散热与保护等;另一方面也是由于前几代混合集成电路整体上质量可靠性高且集成度还不够大。随着第四代混合集成技术的发展,混合集成 SIP 中组装的器件数量将急剧增长,多维度组装将严重制约产品的返工返修,产品成本大幅提升带来生产数量的降低及对合格率要求的大幅提升,这些都是将 KGD 与密封前老炼在第四代混合集成电路推广的重要原因。通过在早期进行裸芯片或者未封口电路的老化筛选,剔除早期失效,实现零缺陷目标。

### 1.4.8 数字化工厂

鉴于第四代混合集成技术形成的产品已经达到系统级别,而其品种多、批量小、结构复杂度高,为了保证研制生产的有效性,原则上应建立一个基于数字化制造的完整技术平台,以数字化版图(EBOM)、数字化物料(MBOM)、数字化工艺(PBOM)、数字化工厂(Digital Factory)为核心,打造数字化双胞胎。其中 EBOM、MBOM、PBOM 等构成完整的技术状态,而大量精确的数字化模型通过仿真和虚拟制造完整地模拟实物制造过程,完成结构干涉检测、可制造性设计、人体工学优化等工作,保障产品研制周期和研制成本。由数字化制造工艺仿真出来的数字化产品也是提供系统装备的“数字化原理样机”,保障总体设计和分布制造同步,大幅减少系统装备的研制时间和调试周期。

#### 1.4.9 全寿命周期过程管理

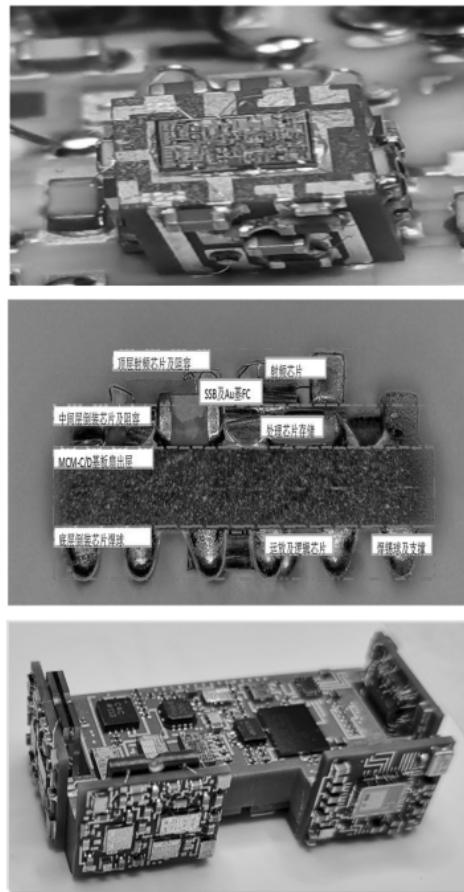

因为四代混合集成复杂度的增长和可靠性要求提升,针对其提出涵盖设计、研制、验证、生产、筛选、评价、售后的全过程全寿命周期工程管理要求。这是一种通过梳理第四代混合集成电路设计制造流程,分析设计制造过程中实现方式和要点进行量化指标分析,基于产品基因组(DNA)概念及离散性分析方法,通过大数据分析采取参数变异分析法和拓扑结构分析法对过程识别做判定<sup>[18]</sup>,最终形成全过程全寿命过程控制的方式。它是智能化设计与数字化工厂结合,是材料、器件、过程综合评价,是智能化单元与寿命预期结合。全周期全寿命管理等新型的设计理念、制造管理、检测理念共同形成混合集成技术革新。第四代混合集成技术代表产品如图4所示。

随着芯片规模的扩大,人们也期望将完整的电子系统集成在一块芯片中,形成系统级芯片(SoC),但由于其研发成本高昂,工艺技术复杂,研制周期较长且需要规模支撑,因此在军工领域的应用受限。而第四代混合集成的主要代表之一混合集成SIP将是SoC的重要补充,重点面向小批量、多品种、快迭代、短周期的高端需求;就像单片封装与二代混合集成的关系一样,应用于不同领域、不同规模、不同需求,目标都是解决半导体器件与通用器件的互联问题。四代混合集成技术相关工艺还包括圆片级封装(WLP)、硅通孔(TSV)、芯片堆叠(Stacked Dies)、封装堆叠(Stacked Packages)、硅圆片堆叠(Stacked Wafers)、埋置基板(Embedded Substrate)、集成无源器件(IPD)等,涉及引线键合(Wire Bonding)、倒装芯片(Flip Chip)、微凸点制造(Micro-bumping)等,代表品种有SIP混合集成微系统、MEMS一体化电路、光电微系统、惯导微系统、集成化导引头等。混合异构集成、CHIPLET也是其发展代表。另外在第四代混合集成技术中引入新的材料或工艺,例如纳米材料应用、石墨烯应用、局部灌封技术、微集成热管等都是混合集成内容一部分,不再逐一阐述。未来一段时期第四代混合集成的可靠性、灵活性、兼容性是军事武器装备发展的有力支撑。

#### 1.5 第五代混合集成技术

技术因需求而存在,以产品为体现,与市场共存亡。当前的深空探测、外星登陆、量子/光子应用、人工智能、束能武器以及高速飞行器等都为混合集成技术未来的发展和提升指明了方向。基于科学技术的发展规律和未来预测,混合集成技术必将以其兼容性、灵活性、可靠性、极端环境适应性在这些领域或其中一部分得以应用。未来已来,预研不远,在新一代技术应用中,预计第五代混合集成通用技术可能有:全超导封装体、无磁/强磁小型化封装、类人感知封装、极限环境工艺(-163 °C~150 °C)、可扩展超级封装、自组装分子封装、相变及记忆金属应用等。下面选取几个代表应用进行预测。

图4 第四代混合集成技术代表产品

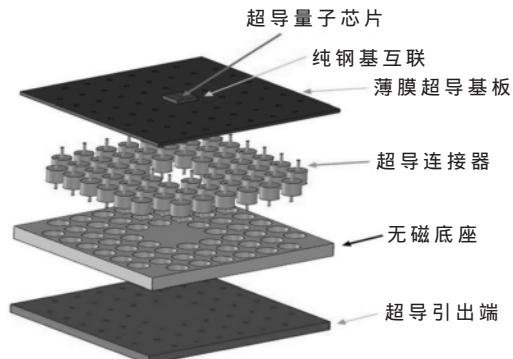

#### 1.5.1 光子/量子封装

随着光子/量子在计算、存储、通信、探测、导航等技术的发展,新的技术倾向于对于单光子/单量子、原子/电子的探测与操控,以量子力学为基础的光子/量子电路不同于传统经典物理。例如低温超导量子计算机,它的处理器需要在30 mK以下的低温环境中才可以稳定工作。因此量子芯片的封装<sup>[19]</sup>设计需要提供高稳定的机械固定,并与制冷源维持良好的热接触,所有连接至芯片的信号线路(信号很微弱)需要超导<sup>[20]</sup>;芯片封装需要提供无磁环境并降低红外辐射噪声以满足测控运算实施。所以以材料技术、超导技术、微波技术、封装技术研究为核心,通过电子设计、量子设计、磁设计、热设计、机械设计等不同学科的融合和交叉,需要攻关的内容包括:超导多层布线技术研究、芯片载板低温匹配性研究、低温陶瓷一体化封装研究、低温气密封装技术研究、高密度低温互联技术研究等;通过第五代混合集成技术可以不断减少量子封装体积,增强工程机量子态稳定时间,提高封装内各类器件混合组态密度,提升量子计算机总体工程可靠性。第五代混合集成可以保障如光子雷达、原子自旋陀螺等在极限环境下通过对光子、原子、电子的测控实现经典物理无法实现的功能。

可扩展封装和超导量子处理器封装如图5所示。

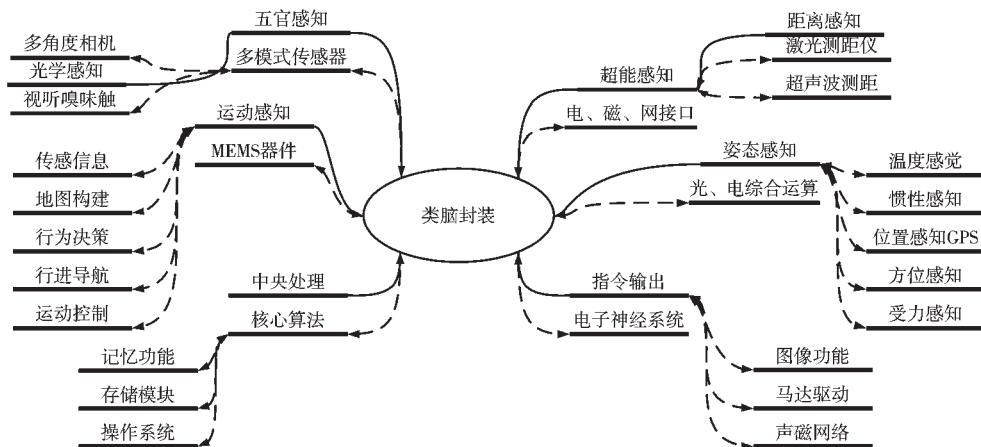

### 1.5.2 类人感知封装

未来科技发展的重要方向之一是人工智能,其中智能设备的核心是类似人体头脑的器件,是整个人工智能的中枢。针对智能设备的“大脑”提供类脑封装极其重要,它既要提供一个如同人头部具有视、听、嗅、味、触的五官七窍的各外部接口,还要具有电、磁、网、超声、激光测距等超能感知的功能,同时提供一个保障该类处理、执行机构的安全载体,这就是类人感知封装。其中MEMS、微电子、光电、通信、存储、处理和生物等技术的交叉融合构成内部系统,通过将处理热、光、电、声、磁、化学、生物信息的器件整合到一个封装内,形成类似人脑功能的总系统是解决的核心,其中系统再集成、多功能接口封装、微纳制造以及软硬结合封装都是重要技术。第五代混合集成技术通过软硬结合的封装技术及多功能接口,保障实现一个小型化、高可靠、全功能的封装环境。类脑封装的架构图如图6所示。

### 1.5.3 极端环境封装

可以预见在不远的将来,人类的足迹将迈向太空深处,所以电子产品满足深空要求将是未来的通用需求之一。在远离太阳辐射的地方,环境温度将下降到-163℃,由于载人环境等可能无法依靠核辐射能保温,对于元器件的要求将会更加苛刻,太空也许会成为理想的组装环

境,混合集成高度灵活的多品种、小批量、高可靠优势正是适用于太空生产、太空应用的特点,可以预见深空探测用器件研产技术,满足极端环境封装(-163℃~150℃)用混合集成将会大展宏图。

随着新的需求与技术发展,未来的封装形式和要求也将日新月异,混合集成技术由于良好的兼容性和灵活性,必将是封装领域的开路先锋和推动力量。随着混合集成技术的发展,第五代混合集成将继续从宏观向微观延伸,做好宏观与微观的联接纽带,其中微观以兼容分子级为主,如分子自组装能力,记忆金属或应变材料都是其中关键;宏观方面在不断解决结构和材料的前提下,将会实现无限拼接封装<sup>[21]</sup>、极端环境应用。通过混合集成技术与量子力学相结合,利用新的设计、材料、设备、环境进行有机融合必将结出更加丰硕成果。

### 2 总结与分析

通过以上对混合集成技术发展历程进行梳理和分析,可见混合集成技术的发展具有显著的代际性,经提炼汇总混合集成技术各个代际的关键参数和应用如表1所示。

综上所述,首先混合集成技术因需求而产生,应需求而进步,为需求而发展。随着半导体芯片的功能化提升和芯片级封装技术进步、PCB级产品的组装密度和可靠性提升、成本低和商业化消费电子的突飞猛进,在半

(a) 可扩展封装

(b) 超导量子处理器封装

图5 第五代混合集成技术预测

图6 类脑封装的架构图

表 1 混合集成电路发展历程

| 代际  | 典型工艺                                                                     | 关键参数                                                                                   | 代表产品                               | 发展年份    | 当前进展            |

|-----|--------------------------------------------------------------------------|----------------------------------------------------------------------------------------|------------------------------------|---------|-----------------|

| 第一代 | 厚薄膜陶瓷基板成品<br>元件组装开板电路                                                    | 功率密度 5 W/in <sup>2</sup><br>组装密度 40 IO/cm <sup>2</sup><br>使用寿命 10 年                    | 点火器<br>加热器                         | 1970 年~ | 民品在用<br>逐步消退    |

| 第二代 | 全金属气密封装<br>裸芯片组装、<br>H 级多器件焊接                                            | 功率密度 40 W/in <sup>2</sup><br>组装密度 40 IO/mm <sup>2</sup><br>使用寿命 18 年                   | 电源模块<br>信号/基准<br>调宽驱动              | 1990 年~ | 军品批量用<br>成熟扩展期  |

| 第三代 | 金属陶瓷一体化封装数字化<br>设计生产、K 级 $3\sigma \pm 15 \mu\text{m}$ 组装精度               | 功率密度 75 W/in <sup>2</sup><br>组装密度 200 IO/mm <sup>2</sup><br>使用寿命 32 年                  | 多通道 T/R 组件<br>长储电路                 | 2010 年~ | 研产同步用<br>批产攻关期  |

| 第四代 | 3D 打印增材结构<br>功能性一体化封装<br>3D 堆叠组装、K+级<br>$3\sigma \pm 1 \mu\text{m}$ 组装精度 | 功率密度 200 W/in <sup>2</sup><br>组装密度 2000 IO/mm <sup>2</sup><br>集成密度 : 300%<br>使用寿命 32 年 | SIP 微系统<br>混合光电组件<br>微惯导组件 MEMS 组件 | 2018 年~ | 研制产品用<br>工艺攻关期  |

| 第五代 | 超导封装<br>无磁/强磁封装<br>超低温组装<br>$3\sigma \pm 100 \text{ nm}$ 组装              | 功率密度 2000 W/in <sup>2</sup><br>集成密度 : 600%<br>-163 °C 长储<br>使用寿命 50 年                  | 光子/量子组件<br>深空探测器件类脑封装              | 2025 年~ | 样品研制用<br>技术论证书期 |

导体集成技术 PCB/FPC 新封装形式的两面夹击下,混合集成看似所占份额逐年降低;同时由于新的混合集成技术包含的内容越来越多,基于各种原因对于新技术提出新名称和种类,掩盖了混合集成技术发展的脉络,甚至有人提出混合集成技术的消亡时间表和关键节点,这是对混合集成技术不理解造成的。混合集成共计发展了三代技术,正在形成四代技术,它是与半导体集成电路发展匹配的先进封装技术,既是半导体集成技术的后道,又是对半导体技术的有益补充,是武器装备小型化、轻量化、高速化、多功能化、智能化、高可靠性的保障。随着混合集成技术的一代代进步,不断把功能性、灵活性、可靠性、适应性提到更高水平,它具有相当宽泛的应用前景,包括新型火箭、卫星、飞船、新一代战略武器、束能武器、高新飞行器等陆、海、空、天、电、磁所有装备领域,未来也必将在电子行业占有不可或缺的席位。

其次,在混合集成技术发展中也存在一些问题,例如界限、范围、代表技术和产品的不清晰,这些并不是核心;而从混合集成技术发展自身考虑,必须改革创新,打破藩篱,例如 GJB2438B 中“D.5 宇航用电路的禁(限)用工艺和材料,f)禁止使用倒装芯片组装工艺。”倒装焊这类与高密度小型化息息相关的工艺不应该一禁了之,而是研究考核评价机制,保障工艺质量,支持它在混合集成电路中的应用。同时在混合集成技术发展的未来,行业的联合及融合很重要,随着工艺复杂度提升,导致工艺技术的实现需要多企业合作,而不是原有的单个企业整体完成;工艺不仅仅是生产商的工作也是设计、设备、材料、生产商联合攻关的结果。其他需要涵盖的工艺还有真空封装以及密封后电镀、导热、加固等工艺技术,这些技术在新的时期已经不同以往,应该进行研究、保障并支持应用。海纳百川,兼容并包,实现 1+1>2,才是混合集成初心与使命。

最后,混合集成是一系列高端先进封装的综合体,从一代到四代,其应用的需求不同,所以内涵不断丰富;与具体封装形式如 DIP 或 LGA 不同,是与半导体工艺发展相辅相成的综合技术。现在的混合集成技术已经是完全可以兼容厚膜、薄膜、LTCC/HTCC、DBC、PCB、FPC、AMB、半导体基板等基板技术;全金属外壳、陶瓷一体化外壳、有机外壳等封装形式;一代半导体硅(Si)、锗(Ge);二代半导体砷化镓(GaAs)、锑化铟(InSb)、磷化铟(InP);三代半导体碳化硅(SiC)、氮化镓(GaN)、氮化铝(AlN)、金刚石、氧化锌(ZnO)等等不同材质的半导体芯片;各类表贴无源器件及结构器件;或者说混合集成技术特征就是把各种材质和特性的元器件、原材料整合。通过混合集成技术的不断创新与持续发展,混合集成电路不断推陈出新,焕发活力。混合集成技术未来更是量子、光子和宏观电路的连接纽带<sup>[22]</sup>。鉴于目前混合集成技术的发展,建议国家对于第一、二代混合集成可以选择性支持,对于第三代混合集成进行工程化支持,重点对于第四代混合集成进行研制平台建设支持,对于第五代混合集成进行预研性支持。

### 3 结语

本文通过提纲挈领的分析混合集成技术的发展过程,提炼关键指标和特征,提出了混合集成技术代际新思路。由分析可见混合集成技术的代际发展过程清晰,代际关系显著。按照代际关系进行混合集成技术的全面梳理,可以改变第一、二代混合集成技术给大家留下的固有印象,展示混合集成技术不断地创新与改进的成果和目标。并通过综合分析及趋势判断,可以预测和引领混合集成未来的方向。

### 参考文献

- [1] GJB-2438B-2017《混合集成电路通用规范》[S].2017.

- [2] TUMMALA R R.Fundamentals of device and systems

- packaging technologies and applications[M]. McGraw Hill , 2019.

- [3] 袁宝山, 冯慧, 门国捷. 混合集成电路技术的发展历程及趋势展望[J]. 数字化用户, 2017(20): 127–128.

- [4] 李浪平, 王正义. 系统级封装(SiP)技术发展与应用综述[J]. 混合微电子技术, 2008, 19(1): 2–10.

- [5] 赵钰. 宇航级混合集成 DC/DC 变换器应用现状与趋势[C]. 中国电子学会第十学术年会, 2008.

- [6] 李浪平. 多芯片组件技术发展和应用综述[J]. 混合微电子技术, 2003(3): 1–7, 28.

- [7] 朱琪. 革命性的框架封装解决方案[J]. 中国西部科技, 2012(12): 12–13.

- [8] 李振亚, 赵钰. 混合集成电路技术发展与展望[J]. 中国电子科学研究院学报, 2009(2): 13–18.

- [9] 李志宏. 微纳机电系统 MEMSNEMS 前沿[J]. 中国科学: 信息科学, 2012(12): 119–135.

- [10] WILSON P R, FERREIRA B, ZHANG J, et al. International technology roadmap for wide bandgap power semiconductors: an overview[J]. IEEE Power Electronics Magazine, 2018, 5 (2): 22–25.

- [11] BUNEL C. High performing wire bondable vertical silicon capacitors for RF power modules[C]. 3D-PEIM Conference, 2016.

- [12] HOU F, WANG W, CAO L, et al. Review of packaging schemes for power module[J]. IEEE Journal of Emerging and Selected Topics in Power Electronics, 2020, 8(1): 223–238.

- [13] DUTT G, MARCZI M, KHALESEV O. Silver sintering die attach—myths and physics[C]. International Workshop on Integrated Power Packaging, 2019.

- [14] MAHAJAN R, SANKMAN R, PATEL N, et al. Embedded multi-die interconnect bridge(EMIB)—a high-density, high-bandwidth packaging interconnect[C]. IEEE/ECTC Proceedings, 2016.

- [15] Samuel Moore. Intel's view of the chiplet revolution[Z]. IEEE Spectrum, 2019.

- [16] SCHULTZ M, YANG F, COLGAN E, et al. Embedded two-phase cooling of large 3D compatible chips with radial channels[J]. Journal of Electronic Packaging, 2016.

- [17] 李振亚, 赵钰. 混合集成电路技术发展与展望[J]. 中国电子科学研究院学报, 2009(2): 13–18.

- [18] ENGLAND L. 3D packaging: a key enabler for further integration and performance[C]. SEMI European 3D Summit, 2017.

- [19] 朱雨生. 厚膜混合集成电路制造过程识别(PID)技术研究[J]. 混合微电子技术, 2013, 24(3): 38–42, 47.

- [20] 刘强. 超导量子器件的制备与可扩展封装方案的研究[D]. 南京: 南京大学, 2017.

- [21] 孔伟成. 基于 transmon qubit 的量子芯片工作环境的研究与优化[D]. 合肥: 中国科学技术大学, 2018.

- [22] Mitsumasa Koyanagi. Heterogeneous 3D integration—Technology enabler toward future super-chip[C]. International Electron Devices Meeting. IEEE, 2013.

(收稿日期: 2020-08-29)

**作者简介:**

朱雨生(1979-), 男, 本科, 研高, 主要研究方向: 混合集成、微电子。

施静(1985-), 女, 本科, 馆员, 主要研究方向: 图书馆学、档案学。

陈承(1990-), 男, 博士, 工程师, 主要研究方向: 集成电路、化合物半导体。

(上接第 35 页)

- neural network[C]. Proceedings of the 25th ACM SIGKDD International Conference on Knowledge Discovery & Data Mining, 2019; 793–803.

- [19] DAMODARAN A, DI TROIA F, VISAGGIO C A, et al. A comparison of static, dynamic, and hybrid analysis for malware detection[J]. Journal of Computer Virology and Hacking Techniques, 2017, 13(1): 1–12.

- [20] SARACINO A, SGANDURRA D, DINI G, et al. Madam: effective and efficient behavior-based android malware detection and prevention[J]. IEEE Transactions on Dependable and Secure Computing, 2016, 15(1): 83–97.

- [21] WANG S, CHEN Z, YU X, et al. Heterogeneous graph matching networks[J]. arXiv preprint arXiv:1910.08074, 2019.

- [22] HODGE V J, AUSTIN J. A survey of outlier detection

methodologies[J]. Artificial Intelligence Review, 2004, 22(2): 85–126.

- [23] JIANG C, COENEN F, ZITO M. A survey of frequent subgraph mining algorithms[J]. The Knowledge Engineering Review, 2013, 28(1): 75–105.

- [24] YAN X, HAN J. gSpan: graph-based substructure pattern mining[C]. 2002 IEEE International Conference on Data Mining, 2002.

(收稿日期: 2021-01-28)

**作者简介:**

朱鹏宇(1993-), 男, 硕士, 工程师, 主要研究方向: 边缘计算、电力通信、人工智能、知识图谱。

蔡新忠(1982-), 男, 硕士, 工程师, 主要研究方向: 电力通信、通信知识库、知识图谱。

徐士元(1987-), 男, 本科, 工程师, 主要研究方向: 电力通信、工程管理。

## 版权声明

经作者授权，本论文版权和信息网络传播权归属于《电子技术应用》杂志，凡未经本刊书面同意任何机构、组织和个人不得擅自复印、汇编、翻译和进行信息网络传播。未经本刊书面同意，禁止一切互联网论文资源平台非法上传、收录本论文。

截至目前，本论文已经授权被中国期刊全文数据库（CNKI）、万方数据知识服务平台、中文科技期刊数据库（维普网）、DOAJ、美国《乌利希期刊指南》、JST 日本科技技术振兴机构数据库等数据库全文收录。

对于违反上述禁止行为并违法使用本论文的机构、组织和个人，本刊将采取一切必要法律行动来维护正当权益。

特此声明！

《电子技术应用》编辑部

中国电子信息产业集团有限公司第六研究所