# 基于负反馈技术的嵌套式直流失调消除电路\*

张芳玲<sup>1</sup>,雷倩倩<sup>1</sup>,张旭东<sup>1</sup>,李弦<sup>2</sup>,李连碧<sup>1</sup>

(1.西安工程大学 理学院,陕西 西安 710000;2.深圳市纽瑞芯科技有限公司,广东 深圳 518000)

**摘要:** 基于 UMC 40 nm CMOS 工艺,设计了一种带有直流失调消除电路(DCOC)的可编程增益放大器(PGA),该 PGA 采用闭环电阻反馈结构,由两级增益单元级联构成。DCOC 电路基于传统的直流负反馈结构,针对多级联的方式,提出了一种嵌套式反馈方法,可降低电路功耗和面积。仿真结果表明,DCOC 在 0~52 dB 的增益变化范围内高通截止频率恒为 10 kHz,相对抑制度恒为 50 dB,且在 0 dB 时可矫正的最大输入失调量为 110 mV。与传统设计方法相比,DCOC 的面积减小近一半。

**关键词:** 直流失调消除;嵌套式反馈;可编程增益放大器

中图分类号: TN722

文献标识码: A

DOI:10.16157/j.issn.0258-7998.201136

中文引用格式: 张芳玲,雷倩倩,张旭东,等. 基于负反馈技术的嵌套式直流失调消除电路[J]. 电子技术应用,2021,47(5):50~53,58.

英文引用格式: Zhang Fangling, Lei Qianqian, Zhang Xudong, et al. A nested DC offset cancellation circuit based on negative feedback technique[J]. Application of Electronic Technique, 2021, 47(5): 50~53, 58.

## A nested DC offset cancellation circuit based on negative feedback technique

Zhang Fangling<sup>1</sup>, Lei Qianqian<sup>1</sup>, Zhang Xudong<sup>1</sup>, Li Xian<sup>2</sup>, LI Lianbi<sup>1</sup>

(1.School of Science , Xi'an Polytechnic University , Xi'an 710000 , China ;

2.Shenzhen Niureixin Technology Co., Ltd., Shenzhen 518000 , China)

**Abstract:** Based on the UMC 40 nm CMOS process, a programmable gain amplifier(PGA) with DC offset cancellation circuit(DCOC) is designed. The PGA adopts a closed-loop resistance negative feedback structure and consists of a cascade of two gain units. DCOC circuit is based on the traditional DC negative feedback structure, a nested feedback method is proposed to reduce the power consumption and area of DCOC circuit. The simulation results show that within the gain variation control range of 0~52 dB, the high pass cutoff frequency and the relative inhibition degree of DCOC are constant at 10 kHz and 50 dB, and the maximum correctable input misalignment at 0 dB is 110 mV. Compared with the traditional design method, the area of DCOC has been reduced by almost half.

**Key words:** DC offset cancellation; nested feedback; programmable gain amplifier

## 0 引言

随着可编程增益放大器(Programmable Gain Amplifier, PGA)放大倍数的增大,尤其在给接收链路提供较大增益时<sup>[1~3]</sup>,直流失调的问题就越来越严重,使得下一级电路处于饱和状态。因此,必须使用直流失调消除电路来解决这一问题。常见的直流失调消除技术有四种,一是交流耦合法<sup>[4~5]</sup>,为了得到低的高通截止频率,需要很大的电阻电容,占用面积大,不易集成;二是数字消除技术<sup>[6~8]</sup>具有极低的高通截止频率,分辨率低,需要额外的量化器和数模转换器,电路实现较复杂;三是前馈消除技术<sup>[9~10]</sup>,由于器件的不匹配等因素,两路的增益不完全相同且这种方法功耗较大;四是直流负反馈消除方

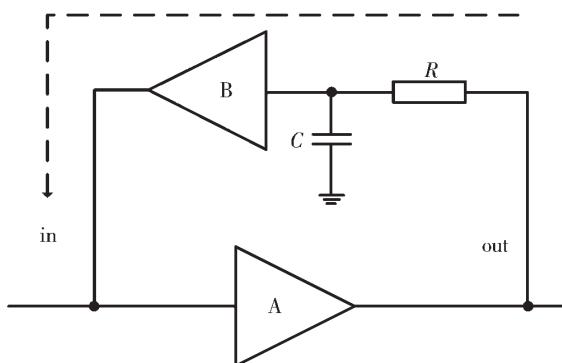

法<sup>[11~15]</sup>,这种方法解决了交流耦合所需要的大电容和数字消除电路的复杂性以及前馈消除方法存在的问题。直流负反馈消除技术如图 1 所示,电阻 R、电容 C 和放大器

图 1 直流负反馈环路

\* 基金项目:深圳市科技计划(KQTD20190929172628244)

大器 B 组成反馈通路, 将输出端 out 检测到的直流失调信号转换成电压或电流反馈到输入端 in, 从而消除直流失调。

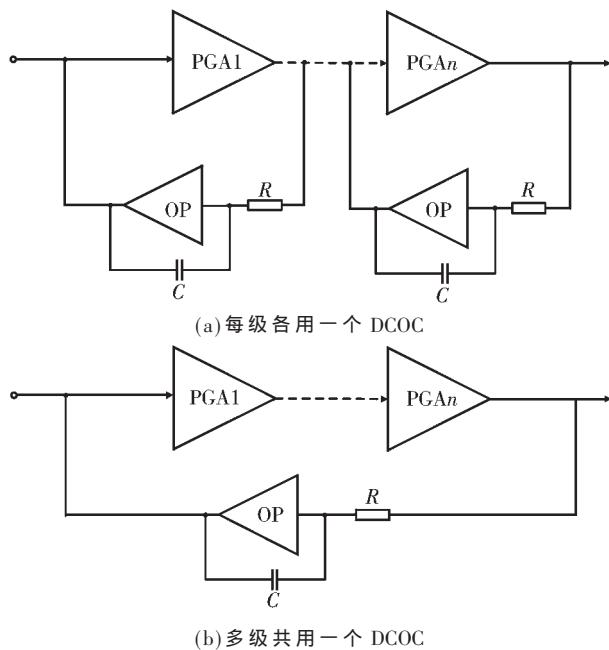

在 PGA 链路中, 通常采用多级级联的方式实现大的可调增益范围。对于多级级联的 PGA 链路, 采用直流负反馈技术消除直流失调的连接方式有两种, 如图 2 所示, 图 2(a)中的每一级 PGA 电路都有一个 DCOC 环路, 而图 2(b)图中采用多级共用一个 DCOC 环路的连接方

图 2 采用直流负反馈技术消除直流失调连接方式

式。图 2(a)中每一级 DCOC 都有一个反馈运放 OP, 增大了电路的功耗<sup>[14]</sup>, 图 2(b)中单级 DCOC 可以简化电路设计和功耗<sup>[10]</sup>, 但为了达到与图 2(a)相同的直流失调消除效果, 需要更大的面积。针对以上两种连接方式存在的不足之处, 本文提出一种改进的直流失调消除方法, 采用了一种嵌套式电路连接方式, 将多个独立的反馈环路通过共用 RC 组成的低通滤波器和运放 OP, 再分别通过反馈电阻反馈到每级 PGA 中, 从而减小电路功耗和面积。

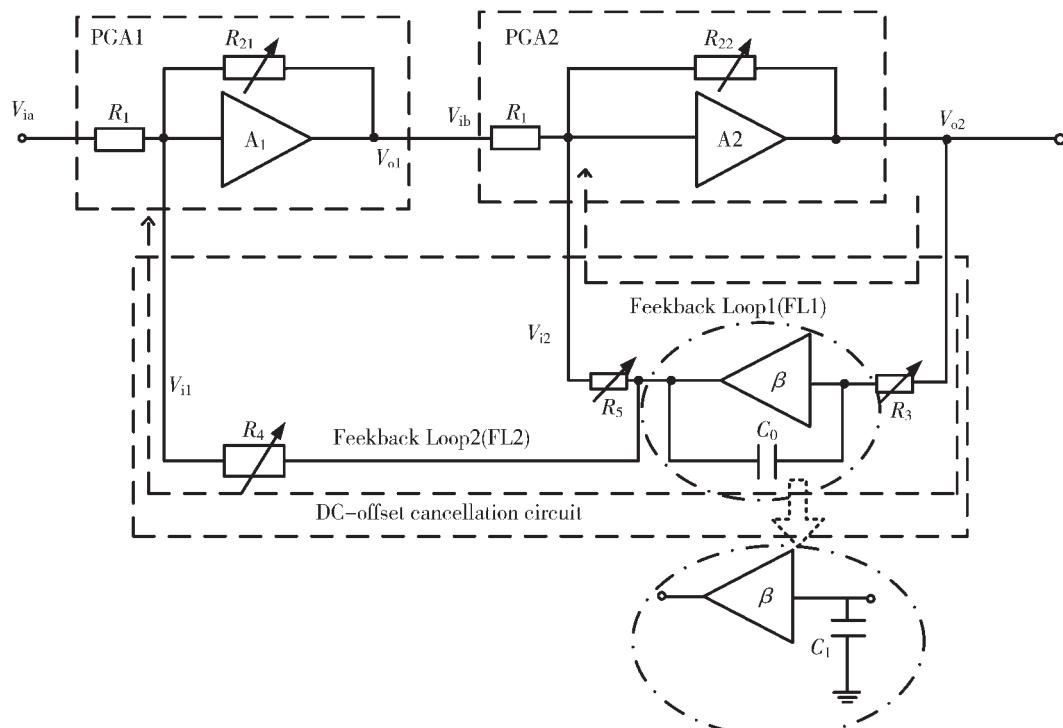

### 1 基于负反馈的嵌套式直流失调电路

嵌套式 DCOC 反馈方式的 PGA 链路如图 3 所示, PGA 电路由两级 PGA1、PGA2 构成, 每级 PGA 均采用开关电阻反馈网络的结构, PGA1 增益变化为 0~26 dB, 第二级增益从 26 dB 变化到 52 dB, 增益步长为 2 dB, 两级级联实现 52 dB 的增益变化范围。图 3 中下方虚线部分为 DCOC 环路, 采用嵌套式反馈的连接方式, 将输出节点  $V_{o2}$  的失调电压通过电阻  $R_3$  和密勒等效电容  $C_1$  组成的低通滤波器检测, 再由运放  $\beta$  进行放大, 一部分通过反馈环路 1(Fl1), 即通过电阻  $R_5$  转换为反馈电流, 注入到第二级的输入端; 另外一部分通过反馈环路 2(Fl2)反馈到第一级 PGA 的输入端。两级共用  $R_3$ 、 $C_0$  和运放增益  $\beta$ , 可变电阻  $R_3$  实现不同高通截止频率的切换。 $C_1$  为密勒等效电容, 等效电容  $C_1$  近似为密勒补偿电容  $C_0$  和运放增益  $\beta$  的乘积。

图 3 中  $V_{ia}$ 、 $V_{ib}$  分别为第一级和第二级的输入信号,  $V_{il}$ 、 $V_{i2}$  是第一级和第二级的反馈信号,  $V_{o1}$ 、 $V_{o2}$  为第一级和第二级的输出信号, 环路 Fl2 和 Fl1 的电压关系式可

图 3 新型嵌套式 DCOC 环路

分别表示为：

$$V_{o1} = V_{il} \left( -\frac{R_{21}}{R_4} \right) + V_{ia} \left( -\frac{R_{21}}{R_1} \right) \quad (1)$$

$$V_{o2} = V_{i2} \left( -\frac{R_{22}}{R_5} \right) + V_{ib} \left( -\frac{R_{22}}{R_1} \right) \quad (2)$$

假设反馈运放  $\beta$  是单级点系统，则：

$$V_{il} = V_{i2} = V_{o2} \cdot \left( \frac{\beta}{1 + \frac{s}{\omega_0}} \right) \quad (3)$$

由图可知：

$$V_{ib} = V_{ol} \quad (4)$$

$$\omega_0 = \frac{1}{R_3 C_1} = \frac{1}{R_3 \beta C_0} \quad (5)$$

$\beta$  为 DCOC 中运放的增益， $\omega_0$  为低通滤波器的截止频率。PGA 和 DCOC 环路的传输函数为：

$$H(s) = \frac{V_{o2}}{V_{ia}} = \frac{-\left(\frac{R_{21}}{R_1}\right)\left(\frac{R_{22}}{R_1}\right) \cdot (s + \omega_0)}{-s + \left(\beta \cdot \left(\alpha \frac{R_{21}}{R_4} - \frac{R_{22}}{R_5}\right) - 1\right) \cdot \omega_0} \quad (6)$$

其中， $\alpha$  为 PGA1 的增益，通常， $\beta \cdot \left(\alpha \frac{R_{21}}{R_4} - \frac{R_{22}}{R_5}\right) \gg 1$ 。因此，高通截止频率可以近似表示为：

$$\omega_c = \left( \beta \cdot \left( \alpha \frac{R_{21}}{R_4} - \frac{R_{22}}{R_5} \right) - 1 \right) \cdot \omega_0 \approx \frac{\alpha \frac{R_{21}}{R_4} - \frac{R_{22}}{R_5}}{R_3 C_0} \quad (7)$$

由式(7)可知，高通截止频率  $\omega_c$  的高低与电阻  $R_{21}(R_{22})$ 、 $R_3$ 、 $R_4$ 、 $R_5$  和电容  $C_0$  的大小有关。对于 PGA1，高通截止频率与  $\alpha$  和  $R_{21}/R_4$  的值有关；PGA2 的高通截止频率与  $R_{22}/R_5$  的值有关，保持  $\alpha(R_{21}/R_4)$  和  $R_{22}/R_5$  电阻比值一定时，高通截止频率保持恒定，即高通截止频率不随 PGA 增益的变化而变化。

由传输函数可知，PGA 的直流抑制度可表示为：

$$H(0) = \frac{\alpha}{\beta \cdot \left( \alpha \frac{R_{21}}{R_4} - \frac{R_{22}}{R_5} \right) - 1} \quad (8)$$

根据式(8)，可以得到  $\beta \cdot \left( \alpha \frac{R_{21}}{R_4} - \frac{R_{22}}{R_5} \right) - 1$  为 DCOC

环路的相对抑制度，可以看出，保持  $\alpha(R_{21}/R_4)$  和  $R_{22}/R_5$  电阻比值一定时环路的相对抑制度具有恒定值，不随 PGA 的增益而变。在电路设计中，可以通过改变  $\beta$  或者电阻比值来得到合适的直流抑制度。

## 2 仿真结果

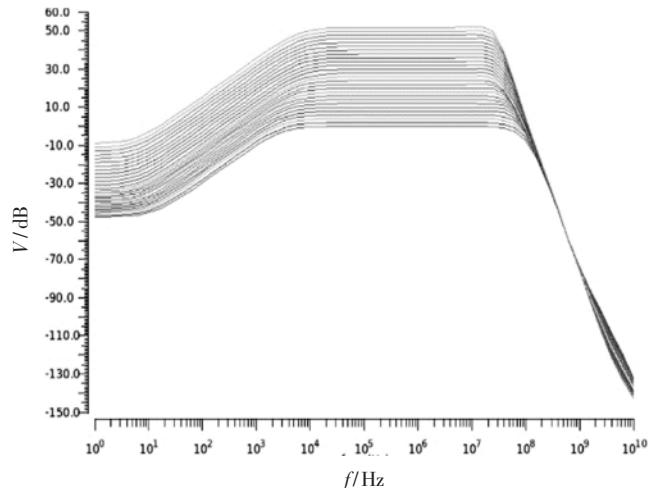

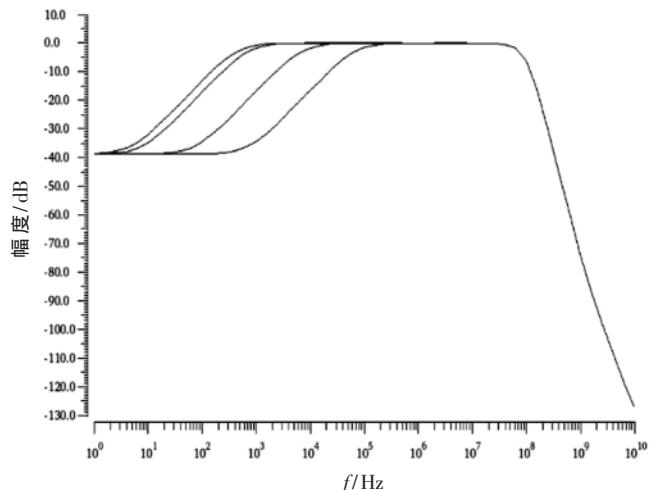

基于 UMC 40 nm CMOS 工艺，对带有嵌套式 DCOC 反馈方法的 PGA 链路进行仿真验证。图 4 为 DCOC 的高通截止频率为 10 kHz 时，PGA 不同增益值的频率响应曲线图，PGA 增益调节范围为 0 dB~52 dB，步长为 2 dB，增益误差小于 0.2 dB，1 dB 带宽大于 20 MHz。此时  $\alpha(R_{21}/R_4)$  和  $R_{22}/R_5$  电阻比值一定，即高通截止频率恒定，不随 PGA 增益的变化而变化，恒为 10 kHz，DCOC 环路的相对抑制度也是恒定的，大于 50 dB。

图 5 为增益在 0 dB 时，调节电阻  $R_3$ ，反馈环路的高

图 4 PGA 频率响应曲线

图 5 相同增益下不同高通截止频率

通截止频率分别为 0.5 kHz、1 kHz、10 kHz、100 kHz 时的频率响应曲线。高通截止频率随信号变化可以进行切换，这样可以同时满足信号完整性和直流失调稳定时间的要求。

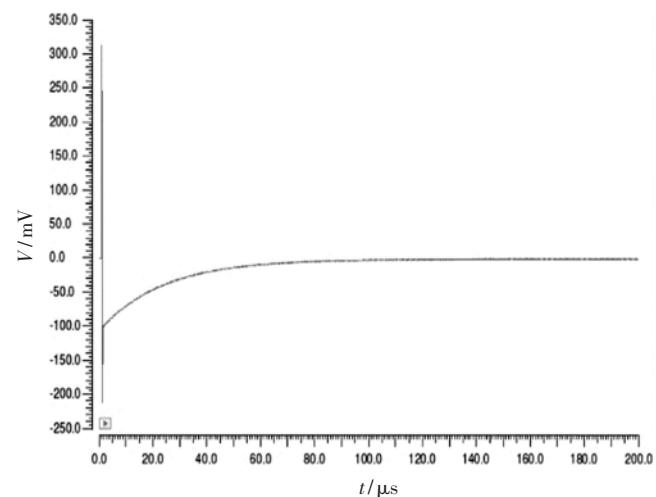

图 6 0 dB 时失调矫正过程

图6为PGA增益为0 dB时,输入端加110 mV失调电压的矫正过程,可以看出,经过DCOC环路矫正后,输出端的直流失调电压小于1 mV。

表1为DCOC的高通截止频率为10 kHz,相对抑制度为50 dB时,采用负反馈结构,三种DCOC环路连接方式的比较。从表可以看出,对于两级级联的PGA链路来说,本文所提出的嵌套式反馈方法与文献[6]、[9]中的方法相比,在优化功耗的同时,可使DCOC环路的面积减小近一半。

表1 DCOC电路中参数的比较

| $\omega_c=10$ kHz     | $R_3/k\Omega$ | $C_0/pF$ | $\beta/\text{个}$ | $R_4/\Omega$ | $R_5/\Omega$ |

|-----------------------|---------------|----------|------------------|--------------|--------------|

| 多环路连接 <sup>[14]</sup> | 580           | 10       | 2                | 40~830 k     | 40~830 k     |

| 单环路连接 <sup>[10]</sup> | 580           | 10       | 1                | 1.08~22 M    | /            |

| 嵌套式连接                 | 580           | 10       | 1                | 4.9~42.16 k  | 40~830 k     |

PGA链路的性能总结如表2所示,PGA输出噪声为67.5  $\mu\text{V}/\sqrt{\text{Hz}}$ ,整个电路在1 V电源电压下功耗为2.7 mW。

### 3 结论

本文在UMC 40 nm CMOS工艺下设计了一种带有DCOC电路的PGA,DCOC环路采用一种嵌套式电路连接方式,可减小电路功耗和面积。仿真结果表明,PGA的增益变化范围为0~52 dB,步长2 dB,增益误差小于0.2 dB,1 dB带宽大于20 MHz,0 dB下IIP3的值为26.8 dBm,噪声为67.5  $\mu\text{V}/\sqrt{\text{Hz}}$ 。加入DCOC环路后,直流失调能够很好地被抑制,整个电路在1 V电源电压下功耗为2.7 mW。

### 参考文献

- JIN J, LIU X, ZHOU J. A 0.25-dB-step, 68-dB-dynamic range analog baseband with digitally assisted DCOC and AGC for multi-standard TV applications[J]. IEEE Transactions on Circuits and Systems II: Express Briefs, 2019, 66(10): 1623~1627.

- MA R, LIU M, ZHENG H, et al. A 77-dB dynamic range low-power variable-gain transimpedance amplifier for linear LADAR[J]. IEEE Transactions on Circuits and Systems II: Express Briefs, 2018, 65(2): 171~175.

- SONG X, LU Z, CAI L, et al. A wideband dB-linear VGA with temperature compensation and active load[J]. IEEE Transactions on Circuits and Systems I: Regular Papers, 2019, 66(9): 3279~3287.

- KUMAR T B, MA K, YEO K S. Temperature compensated dB-linear digitally controlled variable gain amplifier with DC offset cancellation[J]. IEEE Transactions Microwave Theory Techniques, 2013, 61(7): 2648~2661.

- NAMGOONG W. Performance of a direct-conversion receiver with AC coupling[J]. IEEE Transactions on Circuits and Systems II: Analog and Digital Signal Processing, 2000, 47(12): 1556~1559.

- ZHENG Y, YAN J, XU Y P. A CMOS VGA with DC offset cancellation for direct-conversion receivers[J]. IEEE Transactions on Circuits Systems I, Regular Papers, 2009, 56(1): 103~113.

- CHARLON O, LOCHER M, VISSER H, et al. A low-power high-performance SiGe BiCMOS 802.11a/b/g transceiver IC for cellular and Bluetooth coexistence applications[J]. IEEE Journal of Solid-State Circuits, 2006, 41(7): 1503~1512.

- CROLS J, STEYAERT M. A 1.5GHz highly linear CMOS down conversion mixer[J]. IEEE Journal of Solid-State Circuit, 1995, 30(7): 736~742.

- ELAHI I, MUHAMMAD K. IP2 calibration by injecting DC offset at the mixer in a wireless receiver[J]. IEEE Transactions on Circuits and Systems II, 2007, 54(12): 1135~1139.

- LI Q, MA S, YE F, et al. A low-power PGA with DC-offset cancellation in 65 nm CMOS process[C]. 13th IEEE International Conference on Solid-State and Integrated Circuit Technology (ICSICT), 2016: 946~948.

- CHEN T M, CHIU Y M, Wang chuncheng, et al. A low-power fullband 802.11a/b/g WLAN transceiver with on-chip PA[J]. IEEE Journal of Solid-State Circuits, 2007, 42(5): 983~991.

- LEE H D, LEE K A, HONG S. A wideband CMOS variable gain amplifier with an exponential gain control[J]. IEEE Transactions on Microwave Theory and Techniques, 2007, 55(6): 1363~1373.

- RAZAVI B. A 5.2-GHz CMOS receiver with 62-dB image rejection[J]. IEEE Journal Solid-State Circuits, 2001, 36(5): 810~815.

- Chu Xiaojie, Lin Min, Gong Zheng, et al. A CMOS programmable gain amplifier with a novel DC-offset cancellation technique[C]. IEEE Custom Integrated Circuits

表2 PGA电性能指标

| 工艺/nm | 增益变化范围/dB  | IIP3/dBm@0 dB | 噪声/( $\mu\text{V}/\sqrt{\text{Hz}}$ ) | 1 dB 带宽/MHz | DCOC 纠正效果    |                    | 功耗/mW<br>(电源电压 1 V) |

|-------|------------|---------------|---------------------------------------|-------------|--------------|--------------------|---------------------|

|       |            |               |                                       |             | PGA<br>增益/dB | 可矫正的最大<br>输入失调量/mV |                     |

| 40    | 0~52, 步长 2 | 26.8          | 67.5                                  | >20         | 0            | 110                | 2.7                 |

|       |            |               |                                       |             | 26           | 50                 |                     |

|       |            |               |                                       |             | 52           | 3                  |                     |

(下转第 58 页)

两路正交的方波信号同时在 DG444 内与回波信号混频 , 得到多普勒频偏信号的实部与虚部 , 这样采用双路 A/D 转换器同时采样 , 再利用自相关算法 , 即可提取出多普勒频偏 , 最终计算出流速<sup>[15]</sup>。

## 4.2 实验结果

将发射系统、信号接收系统和数字处理系统进行联调，保证硬件以及软件的各个测试点正常工作。设置好层深和层数后，将信号源经衰减器后得到的  $10 \mu\text{V}$  正弦信号接入接收电路，以  $2 \text{ MHz}$  为中频频率，上下调节输入信号的频率，查看系统测得的多普勒频偏。表 1 为不同频率输入信号，采用硬件正交、滤波和软件正交、滤波后测得的多普勒频偏。

表 1 不同频率输入测得的多普勒频偏

| 输入频率      | 硬件正交、<br>濾波多普勒频偏 | 软件正交、<br>濾波多普勒频偏 | (Hz) |

|-----------|------------------|------------------|------|

| 2 000 100 | 97               | 113              |      |

| 2 000 500 | 507              | 481              |      |

| 2 000 100 | 1 002            | 1 034            |      |

| 1 999 900 | 104              | 85               |      |

| 1 999 500 | 497              | 527              |      |

| 1 999 000 | 995              | 983              |      |

经过上述数据分析后,可以看出该多普勒流速仪通过将正交、滤波在硬件上实现和软件上增加信号质量分析,可以使测量的精度显著提高,同时减少了CPU运算的时间,使测量更加快速,能更加广泛地应用在各种小型河流、水渠等。

5 结论

本设计将正交变换、FIR 滤波在硬件电路中实现，硬件电路滤波相比软件滤波效果更加明显，使测量精度显著提升；采用 STM32H743 为主控芯片，在运算处理速度方面以及内存方面有极大提升，同时减少了外扩 SRAM，使电路和软件设计更加简便，节约成本；在提升运算速度的基础上，加入 FFT 算法对回波信号进行质量分析，筛选质量较好的信号，保证了自相关算法对流速计算的精确度。因此，本系统较传统 ADCP 具有更高的精确性以及更快的运行速度。在当前河流资源日趋恶化的情况下，该新型声学多普勒流速剖面仪的成功应用

A decorative horizontal border consisting of a repeating pattern of diamond shapes.

(上接第 53 页)

Conference , 2010 : 1–4.

- [15] ZHENG Y, YAN J, XU Y P.A CMOS VGA with DC offset cancellation for direct-conversion receivers[J].IEEE Transactions Circuits Systems I ,Regular Papers ,2009 ,56(1): 103–113.

(收稿日期:2020-11-20)

为我国水文测量的发展以及改善提供了帮助,促进了对河流领域的研究与探索。

参考文献

- [1] 王槐军.ADCP 技术在水文测验中的应用[J].能源与节能, 2017(8): 165–166, 179.

- [2] 彭飞, 邹冬梅. 浅析 ADCP 测流方法[J]. 民营科技, 2018(10): 54–58.

- [3] 吴炳昭, 李占桥. ADCP 比测试验的统计分析[J]. 海洋测绘, 2010(6): 29–32.

- [4] 唐波, 黄文玲, 张静远. 基于模拟开关的混频器设计[J]. 微型机与应用, 2017, 36(10): 94–95, 98.

- [5] 陈阳. 硅基 CMOS 毫米波开关混频器的研究与设计[D]. 成都: 电子科技大学, 2015.

- [6] 刘彦祥.ADCP 技术发展及其应用综述[J].海洋测绘, 2016(2): 86–89.

- [7] 郑宇凡.浅谈 FFT(快速傅里叶变换)算法及其应用[J].科技展望, 2015, 25(29): 144–147.

- [8] 骆林依, 王英皓, 徐圆飞, 等.基-2 FFT 算法的模块化硬件实现与比较[J].电子产品世界, 2019, 26(2): 31–34.

- [9] 芦潇静.STM32H7 微控制器为物联网设备保驾护航[J].单片机与嵌入式系统应用, 2016, 16(12): 81–85.

- [10] 李占桥, 田志光.两种型号 RDI ADCP 测速精度分析[J].海洋测绘, 2012(6): 32–38.

- [11] 邓新宇.基于 STM32F1 的调幅信号处理电路系统设计研究[J].现代信息科技, 2019, 3(20): 35–37.

- [12] 高伟.声学多普勒流速仪计量检定工作分析[J].水利信息化, 2010(5): 12–16.

- [13] 刘贞文, 杨燕明, 许德伟, 等.海水声速直接测量和间接测量结果分析[J].海洋技术, 2007(4): 44–46.

- [14] 吴晓楷.走航式 ADCP 在引黄济津潘庄线路应急输水测验中的运用[J].海河水利, 2012(3): 65–69.

- [15] 陈中江.海洋监测锚系耦合链通信传输系统研制[D].杭州: 杭州电子科技大学, 2011.

(收稿日期:2020-06-23)

作者简介

张羽(1994-),通信作者,男,硕士研究生,主要研究方向:嵌入式开发、电子测量,E-mail:172585164@qq.com。

李永倩(1958-),男,博士,教授,主要研究方向:信息传感与测量技术。

扫码下载电子文档

作者简介

张芳玲(1996-),女,硕士研究生,主要研究方向:可变增益放大器及直流失调消除电路。

雷倩倩 (1984-), 通信作者, 女, 博士, 副教授, 主要研究方向: 数模混合集成电路, E-mail: leiqianqian@163.com。

扫码下载电子文档

## 版权声明

经作者授权，本论文版权和信息网络传播权归属于《电子技术应用》杂志，凡未经本刊书面同意任何机构、组织和个人不得擅自复印、汇编、翻译和进行信息网络传播。未经本刊书面同意，禁止一切互联网论文资源平台非法上传、收录本论文。

截至目前，本论文已经授权被中国期刊全文数据库（CNKI）、万方数据知识服务平台、中文科技期刊数据库（维普网）、DOAJ、美国《乌利希期刊指南》、JST 日本科技技术振兴机构数据库等数据库全文收录。

对于违反上述禁止行为并违法使用本论文的机构、组织和个人，本刊将采取一切必要法律行动来维护正当权益。

特此声明！

《电子技术应用》编辑部

中国电子信息产业集团有限公司第六研究所