# 一种全国产化捷联惯性导航信号处理平台设计

张 禹,钱宏文

(中国电子科技集团公司第五十八研究所,江苏 无锡 214072)

**摘要:**现代信息化战争对定位定向系统的要求越来越高,捷联惯性导航系统是特种车辆不可或缺的定位定向系统。基于此需求,设计和开发了一种100%国产化率的捷联惯性导航系统信号处理平台,平台同时适配RTLinux操作系统,可应用于车载定位定向系统、机载控制系统、航电系统、便携式基站系统等。经过设计研发和实验测试,该捷联惯性导航系统信号处理平台功能和性能满足使用要求,为国产化捷联惯性导航系统信号处理平台提供了一种解决方案。

**关键词:**捷联惯性导航;国产化;RTLinux

中图分类号: TN02

文献标识码: A

DOI:10.16157/j.issn.0258-7998.200992

中文引用格式: 张禹,钱宏文. 一种全国产化捷联惯性导航信号处理平台设计[J]. 电子技术应用, 2021, 47(5): 102–107.

英文引用格式: Zhang Yu, Qian Hongwen. Design of a national industrialization strapdown inertial navigation signal processing platform[J]. Application of Electronic Technique, 2021, 47(5): 102–107.

## Design of a national industrialization strapdown inertial navigation signal processing platform

Zhang Yu, Qian Hongwen

(China Electronics Technology Group Corporation No.58 Research Institute, Wuxi 214072, China)

**Abstract:** Modern information warfare requires more and more high requirements for positioning and orientation system. Strapdown inertial navigation system is an indispensable positioning and orientation system for special vehicles. Based on this requirement, a signal processing platform of strapdown inertial navigation system with 100% localization rate is designed and developed. The platform is also adapted to RTLinux operating system, which can be applied to vehicle-mounted positioning and orientation system, airborne control system, avionics system, portable base station system, etc. Through design, development and experimental test, the function and performance of the strapdown INERTIAL navigation system signal processing platform meet the operational requirements, providing a solution for the autonomous and controllable localized strapdown inertial navigation system signal processing platform.

**Key words:** strapdown inertial navigation; localization; RTLinux

## 0 引言

为了满足现代战争的需求,车辆在运动中时刻清楚自己所处方位、车辆姿态及行驶速度等信息<sup>[1]</sup>,需要以捷联惯导系统为代表的自主定位定向系统<sup>[2]</sup>。随着人工智能在军事应用的进一步转移<sup>[3]</sup>,国家对武器装备的安全性和独立设计的要求也越来越高。定位定向系统我国虽已建成北斗,但相比于美国的GPS、英国的FIN500、德国的FNA615等导航系统<sup>[4]</sup>的应用和普及,还存在不少差距。同时目前捷联惯性导航系统信号处理平台基本都是采用国外基础软硬件,如美国的赛灵思FPGA、Intel处理器、Windows操作系统。在国产化方面国产化FPGA、国产化CPU、中标麒麟操作系统、锐华、睿思等操作系统虽已完成核心知识产权认证,但还未真正实现大范围的推广应用,武器装备国产化的需求越来越紧迫。

基于以上背景和需求,本文设计开发了一种基于国产化CPU+国产化FPGA平台的捷联惯性导航系统信号处理平台,平台采用100%国产化器件设计,同时适配经过实时性改造的RTLinux操作系统。

### 1 设计准则

#### 1.1 设计思路

针对捷联惯性导航系统信号处理平台产品自主可控和安全可靠的性能要求,兼顾导航自主性、可靠性、稳定性和抗干扰性要求<sup>[5]</sup>,开展设计和研制工作,本次设计主要针对国产化元器件和操作系统为核心进行设计。

元器件的选型方面,考虑国内知名厂家和已经经过认证量产的器件优先选用。核心CPU选择龙芯中科的2K1000,该CPU采用了40 nm CMOS工艺,单片内部集成了2个全流水64位双精度GS264 CPU核心与GPU

图形核心,主频可达1GHz,峰值运算速度为8G flops,二级缓存为256KB,三级缓存为1MB,功耗为1~5W,并支持动态降频和降压<sup>[6]</sup>。同时,该处理器支持64位DDR3控制器,有SATA2.0、USB2.0、PCIE2.0、RGMII、CAN、UART、Local Bus、I<sup>2</sup>C、SPI等丰富的外设接口,可满足更多的场景和接口需求。

FPGA选择中国电子科技集团公司第58研究所的FPGA“亿芯一号”,“亿芯一号”是基于SRAM配置的高密度可编程逻辑阵列电路,包含了128行×52列共6 656个可编程逻辑块、59 904个逻辑单元、64个XtremeDSP Slice、2 880K的可编程Block RAM以及可编程端口、DCM、PDCM等模块,可完美替换赛灵思XC4VLX60系列。

硬件电路的设计以龙芯处理器为核心,在单板上集成CPU等核心处理单元,通过国产化FPGA扩展丰富的对外接口,可实现RS422通信接口、RS232调试接口、存储接口、CAN接口、以太网接口、磁隔离计数接口、GPIO控制接口等。操作系统选用经实时化改造的RTLinux操作系统,主板采用模块化、整体化的设计,实现处理器和操作系统核心软硬件的国产化。

## 1.2 平台组成

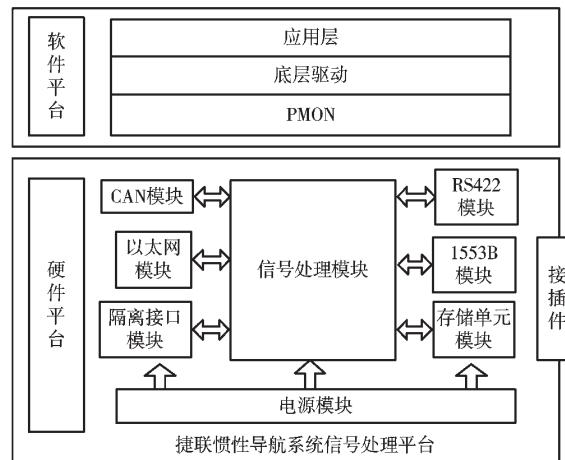

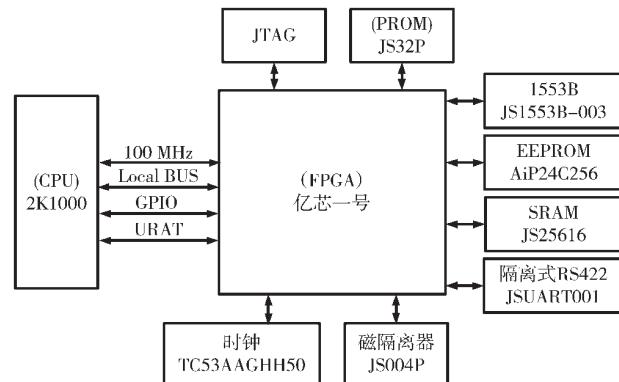

捷联惯性导航系统信号处理平台由电源模块、信号处理模块、存储单元模块、1553B模块、422通信模块、CAN通信模块、以太网模块、隔离接口模块组成(如图1所示)。系统通过PMON实现硬件的初始化与检测,引导操作系统内核;系统软件以RTLinux操作系统作为基础软件平台,在设备驱动层提供支持;开发环境层集成常用的编译工具及各种支持的环境;基础软件层,为后续的应用部署提供支撑。整个平台能够完成捷联导航解算、流程控制、数据和上位机的交互等功能。

## 2 硬件设计

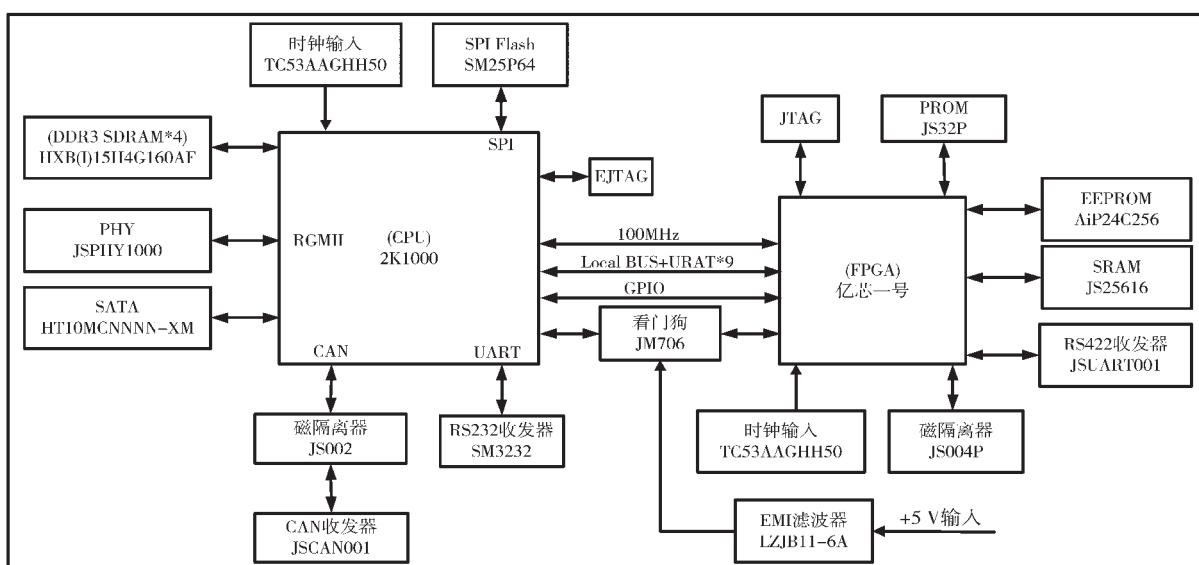

本次设计采用CPU+FPGA的硬件架构,其中CPU选

图1 捷联惯性导航系统信号处理平台组成

用龙芯中科的2K1000型处理器,FPGA选择使用中国电子科技集团公司第58研究所的“亿芯一号”。CPU主要实现系统的数据处理和部分外部接口扩展功能,FPGA主要实现CPU的上电时序控制及其他外设接口的扩展和通信功能,系统整体框图如图2所示。

CPU采用外挂SPI NOR Flash来实现BIOS的引导,CPU对外引出CAN接口、RGMII网络接口、SATA存储接口,CPU和FPGA之间通过localbus总线来进行数据交互。

### 2.1 DDR3 SDRAM 电路

龙芯2K1000处理器内部集成有64位DDR3内存控制器,内存读写规则遵守DDR3 SDRAM行业标准(JESD79-3)。可配置为64/32/16位工作模式,支持命令调度,但不支持ECC。

设计选用4片紫光国芯公司的256×16 Mb DDR3 SDRAM存储器HXI15H4G160AF-13K实现总容量2 GB的内存扩展。该芯片具有16根数据线和15根地址线,

图2 捷联惯性导航系统信号处理平台整体框图

选用标准 DDR3 电源供电和上电时序要求。

## 2.2 以太网接口电路

龙芯 2K1000 处理器的内部集成 2 路 10/100/1 000 Mbps 自适应以太网多媒体控制器接口(Media Access Controller, MAC),两者在逻辑结构上完全相同。双网卡均兼容 IEEE802.3 协议,对外部的 PHY 通过 RGMII 方式实现,支持半双工和全双工的自适应调整、CRC 校验码的自动生成和校验等功能。

网口芯片选用中国电科 58 研究所的千兆 PHY 芯片 JSPHY1000,电路功能兼容 Marvell 公司的 Gigabit 以太网收发器 88E1111,它支持 RGMII、GMII、SGMII 等多种连接模式,能够和龙芯 2K1000 处理器进行对接,用于数据的传输和系统软件升级,网络变压器使用顺络迅达的 LT1303-A 通过磁隔离来提高整个系统的可靠性。

## 2.3 CAN 接口电路

龙芯 2K1000 处理器内部集成了 2 路的 CAN 控制器,控制器通过对 CAN 收发器可以实现 CAN 总线协议和 CAN 数据通信,CAN 总线是由发送数据线 TX 和接收数据线 RX 构成的串行总线,支持发送和接收数据,CAN 总线上的设备支持数据的双向传送,最高传输速率可达 1 Mb/s。

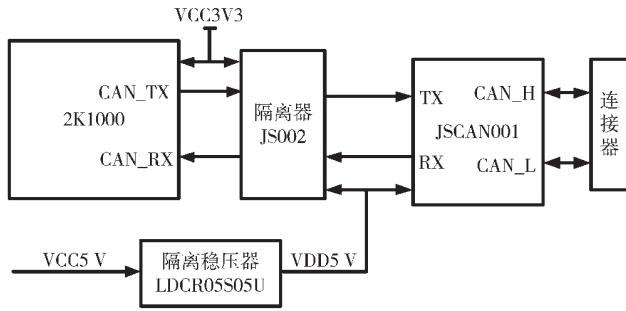

本次设计选用中国电子科技集团公司第 58 研究所的双通道数字隔离器 JS002 实现双向信号的输入输出,该电路与 ADI 公司的 ADuM1201 电路兼容。实现 CAN 信号的隔离传输,电源设计使用新雷能公司的 DC-DC 隔离电源 LDCR05S05U 产生数字隔离器端所需的 5 V 隔离电源为隔离器和 CAN 驱动器提供隔离电源。CAN 收发器使用中国电子科技集团公司第 58 研究所的高可靠现场总线收发器 JSCAN001,提供协议控制器和物理传输介质之间的物理链路,同时该器件输入兼容 3.3 V 和 5 V 电平,通信速率高达 1MBaud,且带有高达  $\pm 6$  kV 的 ESD 保护功能。该电路功能与 Microchip 公司的 MCP2551 功能兼容。CAN 接口的硬件设计框图如图 3 所示。

图 3 隔离 CAN 硬件设计框图

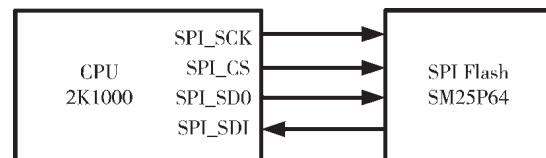

## 2.4 系统启动电路

龙芯 2K1000 处理器支持 LocalIO、SPI、SDIO、NAND 四种系统启动方式,本次设计选用 SPI 启动方式。龙芯 2K1000 处理器集成的 SPI 控制器仅可作为主控端,所连

接的是从设备。对软件来说,SPI 控制器有一段映射到 SPI Flash 的只读 Memory 空间,如果将这段 Memory 空间分配在 0x1fc00000,复位后不需要软件干预就可以直接访问,从而支持处理器从 SPI Flash 启动。

Flash 设计选用深圳国微的 SM25P64 用于 PMON 系统启动,系统启动硬件设计框图如图 4 所示。

图 4 系统启动硬件设计框图

## 2.5 SATA 接口电路

龙芯 2K1000 处理器内部包含有 SATA 控制器,支持 SATA 的 1 代 1.5 Gb/s 和 SATA 的 2 代 3 Gb/s 速率的传输,兼容串行 ATA2.6 和 AHCI1.1 规范,SATA 盘选用鸿泰科技的 HT10MCNNNN-XM 来实现 1 TB 大容量存储的扩展。

## 2.6 FPGA 部分硬件设计

FPGA 主要包含功能:隔离 RS422 串口扩展、外部控制信号输入输出、控制 CPU 的上电顺序、整机 5 V 输入电源的监测功能、EEPROM 的扩展、PROM 的扩展等。FPGA 和 2K1000 处理器之间通过 Local BUS 总线、多个 GPIO 和 UART 进行控制和通信。FPGA 设计框图如图 5 所示。

图 5 FPGA 部分硬件设计框图

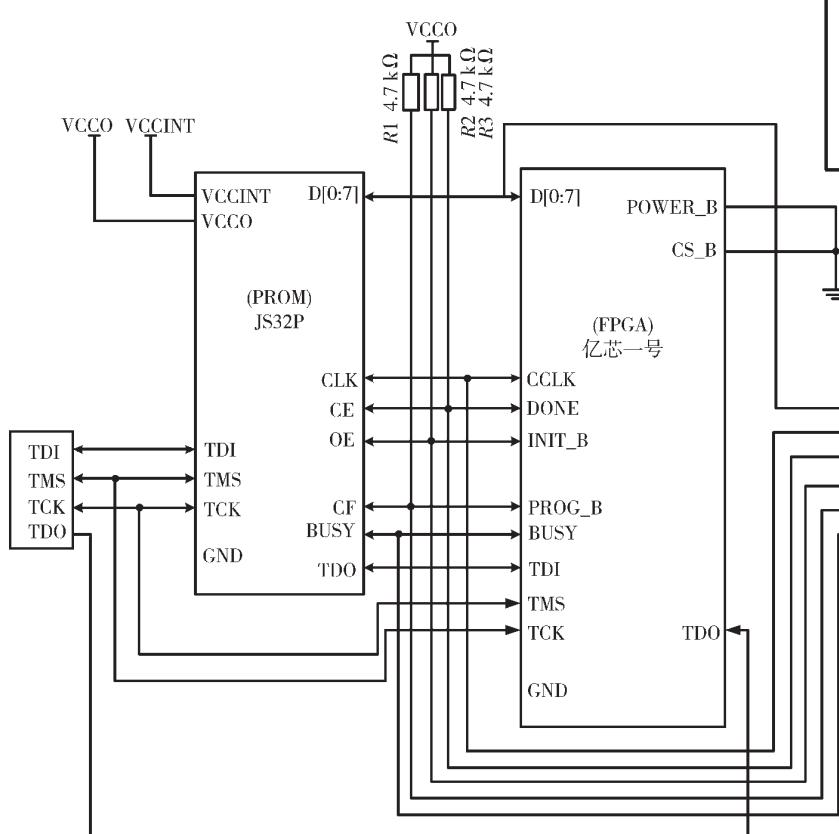

## 2.7 PROM 配置电路

FPGA 的配置设计选用 JTAG 和 Master Select MAP 两种方式。使用 Master Select MAP(Parallel) Mode 配置方式的优点是能够减少 FPGA 的启动配置时间,有效地提高系统的启动速度,增加 FPGA 配置方式的灵活性<sup>[7]</sup>。PROM 型号设计选用中国电子科技集团公司第 58 研究所的 JS32P 来存储 FPGA 的配置信息,该器件容量为 128 Mb,使用 3.3 V 和 1.8 V 同时供电,最大的工作频率可达 33 MHz,该产品和 XCF32P 功能兼容,但不支持压

缩的 MCS 文件。PROM 启动配置硬件设计框图如图 6 所示。

图 6 PROM 配置电路设计框图

## 2.8 EEPROM 接口电路

EEPROM 是带电可擦可编程只读存储器, 是一种掉电后数据不丢失的存储芯片, 因为掉电后不丢失, 所以能够有效地存放一些关键的监控信息和系统的温度数据等, EEPROM 设计选用中微爱芯电子有限公司的 AiP25-C256, 其容量为 256 Kb, 存储器的结构为  $32\text{768}\times 8\text{ bit}$ , 内部分为 512 页, 每页 64 B, 采用 I<sub>C</sub> 接口, 广泛应用于低功耗、低电压系统。

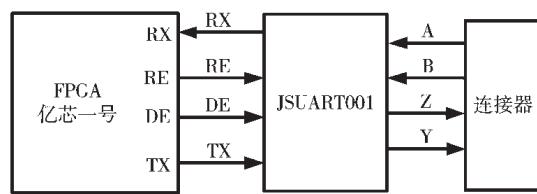

## 2.9 RS422 接口电路

RS422 接口芯片使用中国电子科技集团公司第 58 研究所的隔离式 RS422/485 收发器 JSUART001, JSUART001 将一个 3 通道的数字隔离器、一个三态差分线路驱动器、一个差分输入的接收器和一个的隔离 DC-DC 转换器集成于单片封装中, 从而实现完全集成的信号与电源隔离 RS-485 解决方案, 可配置为半双工或全双工模式, 实现最高 16 Mb/s 的传输速率, 供电 3.3 V 或 5 V 可选, 同时带  $\pm 15\text{ kV}$  的 ESD 保护功能, 该芯片可兼容 ADI 公司的 ADuM2682。当使用串口功能时 RE 和 DE 可由 FPGA 控制置高或置低使芯片处于异步半双工状态, 当使用数据传输功能时 RE 和 DE 可由 FPGA 控制置高或置低使芯片出去单向或双向数据发送状态。RS422 接口

的硬件设计框图如图 7 所示。

图 7 RS422 电路设计框图

## 2.10 磁隔离 IO 接口电路

磁隔离 IO 接口用于 FPGA 接收陀螺、加速度计及里程计数脉冲和向外发送控制信号。设计选用中国电子科技集团公司第 58 研究所的双通道隔离器 JS002, 以及中国电子科技集团公司第 58 研究所的四通道隔离器 JS004P 磁隔离 IO 接口。该芯片是一种基于电磁隔离的多通道数字隔离器, 可实现输入输出之间完全的电气隔离, 电路两端分别供电可实现 3 V/5 V 电平转换, 通过精确匹配传输线的特征阻抗<sup>[8]</sup>, 能够把输入数据通过高频编码之后接收端实现无失真恢复。该型号电路可与 ADI 公司的 ADuM14xx 系列功能兼容。

## 2.11 1553B 接口电路

1553B 接口电路用于完成 1553B 总线通信, 设计选用中国电子科技集团公司第 58 研究所的全功能模块 1553B 总线控制器, 型号为 JS1553B-003, JS1553B-003 是一款高性能的 MIL-STD-1553B 总线通信控制器, 该模块电路内部由一块协议处理芯片和一块收发器芯片(双路)组成, 包含了完整的主处理器与 1553B 总线的接口, 集成了双通道收发器、协议处理器、存储器管理、处理器接口逻辑和内置 4 KB 的 RAM, 实现了与 1553B 终端的全兼容, 具有总线控制器(BC)、远程终端(RT)和监视器(MT)三大功能<sup>[9]</sup>。该芯片与 DDC 公司的 BU-64843GC-140 电路功能兼容。

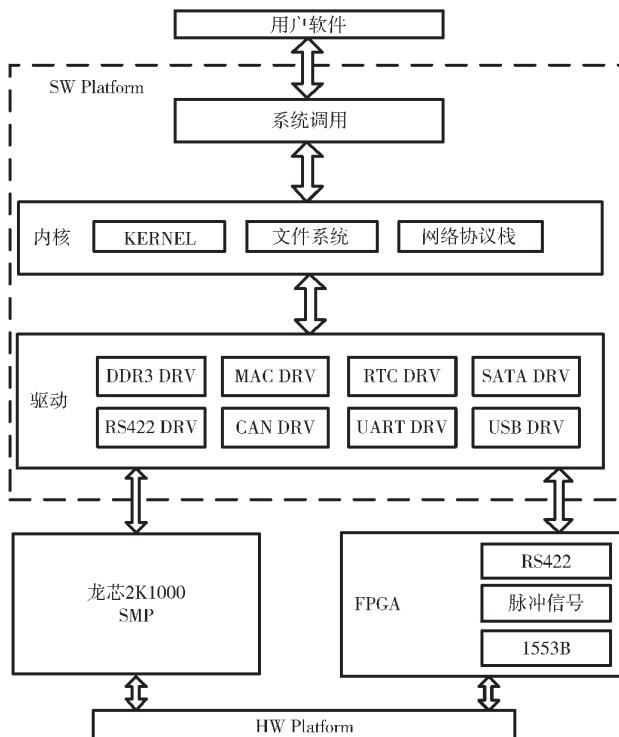

## 3 软件设计

捷联惯性导航系统信号处理平台软件由系统引导软件、操作系统软件和驱动接口软件组成, 各软件功能如下。

### 3.1 系统引导软件

系统引导软件是捷联惯性导航系统信号处理平台上电后首先加载的一段程序软件, 该软件负责对处理器, 即龙芯 2K100 处理器进行初始化, 包括初始化中断、内存、串口、GPIO、以太网以及启动 TFTP 服务、调试等功能。本项目的系统引导软件选用 PMON 软件, PMON 是一个兼有 BIOS 和 BOOTLOADER 部分功能的软件代码, 多用于嵌入式系统, 其支持 EXT2、FAT32、RAM 文件系

统,支持网络引导(TFTP)、磁盘引导、Flash 引导以及内建调试功能,并具有很好的通用性,能够支持 MIPS、ARM、PowerPC 等平台<sup>[10]</sup>。系统引导软件主要用于引导以及操作系统软件的升级,与其他软件相互独立和用户层的应用不对接,用户所需的功能均在操作系统软件和驱动接口软件代码中实现。

### 3.2 操作系统软件

操作系统软件是捷联惯性导航系统信号处理平台系统运行的基础,该软件提供应用所需的进程管理、内存管理、文件系统、网络通信、安全机制、驱动程序等基础功能,为实现系统控制、数据通信提供可能。

Linux 系统由于具有内核源码开发、免费使用、可移植性高、跨平台支持性好、易于裁剪等特点,被广泛应用于嵌入式领域。但是由于 Linux 系统自身架构的问题,无法满足实时操作系统需求,当前比较流行的实时 Linux 扩展莫过于 RTAI、Xenomai、XtratuM 和实时抢占补丁,经过改善单内核方案(Linux+RT 抢占式补丁)以及双内核方案(RTLinux)越来越多的实时化方案被设计出来,使 Linux 具有强大的硬软实时处理能力,比如单内核方案(Linux+RT 抢占式补丁)以及双内核方案(RTLinux)。

实时操作系统是指一个能够在事先指定或者确定的时间内完成系统功能和对外部或者内部,同步或者异步事件做出响应的系统<sup>[11]</sup>。实时性的核心在于确定性而不是单纯的系统响应所读,即在规定的时间内完成规定的事情。

本次软件设计采用 RTLinux 操作系统软件方案,其总体架构如图 8 所示,其中 SW-platform 部分为软件的总

图 8 捷联惯性导航系统信号处理平台 Linux 软件整体框图

体框架,它对上位用户的应用软件提供交互接口 API,对下位龙芯的硬件提供外设驱动,其中 RS422 和脉冲和脉冲计数器在 FPGA 上实现,龙芯处理器和 FPGA 之间通过 LocalBus 总线通信。

### 4 实时性测试

#### 4.1 测试原理说明

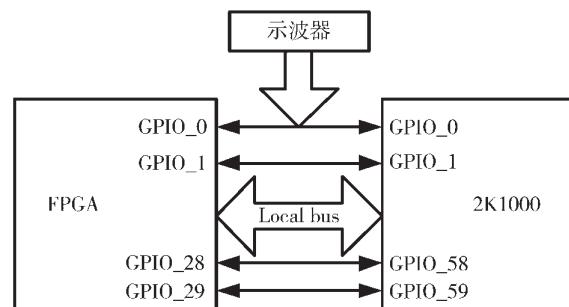

测试平台为龙芯 2K1000+FPGA, RTLinux 版本为 V3.10。测试原理框图如图 9 所示。

图 9 实时性测试原理框图

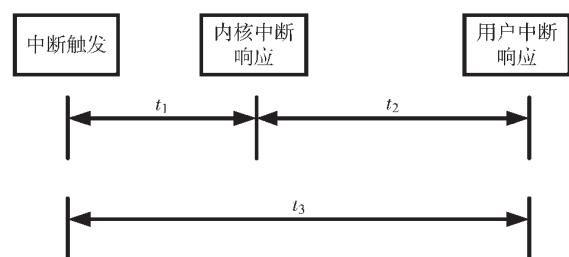

中断响应测试 RTLinux 下的响应时间使用 FPGA 通过 GPIO 向龙芯 2K1000 发中断,设置上升沿触发中断。中断响应时间测试计时如图 10 所示。

图 10 中断响应时间测试计时

#### 测试流程:

(1)龙芯 2K1000 通过写 FPGA 约定寄存器后,FPGA 返回 GPIO\_A 中断信号;

(2)同时 FPGA 通过拉高另外一个 GPIO\_B 表示开始计时,以标记示波器采集计时时间开始点;

(3)龙芯 2K1000 响应中断信号后,触发中断处理函数发信号给应用层进程,应用层通过系统调用,去读取 FPGA 最终的计时数据结果,同时 FPGA 通过拉低 GPIO\_B 表示计时停止,以标记示波器采集计时时间结束。

#### 4.2 测试结果说明

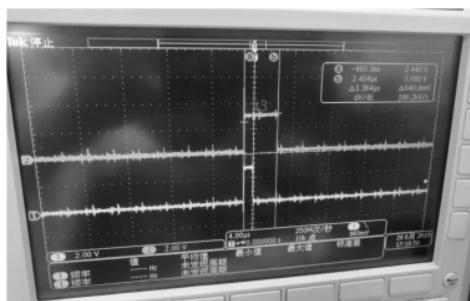

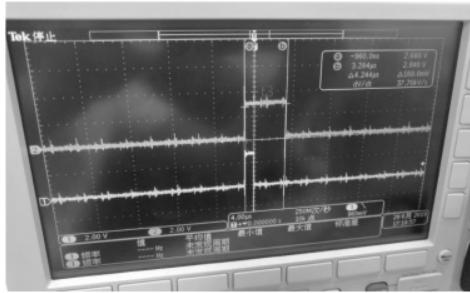

根据上述测试方法测试时,中断时间统计表如表 1

表 1 中断时间统计表

| 响应时间                  | RTlinux |            |

|-----------------------|---------|------------|

|                       | 空载      | 80% CPU 负荷 |

| 内核中断响应时间( $t_{min}$ ) | 3.3     | 3.6        |

| 内核中断响应时间( $t_{max}$ ) | 3.5     | 40(统计最大值)  |

所示, 测试波形如图 11、图 12 所示。RTLinux 中断响应时间平均不大于 40  $\mu$ s。VxWorks 不大于 10  $\mu$ s。

图 11 内核层中断响应时间波形图

图 12 内核层加 80%CPU 负载中断响应时间波形图

经测试结果表明系统完全可以达到实时性要求。

5 结论

针对目前捷联惯性导航系统信号处理平台国产化的迫切需求,本次设计开发使用国产CPU+FPGA架构搭建硬件平台,设计采用100%的国产化元器件实现了捷联惯性导航系统信号处理平台的设计和开发,经过适配软件和系统测试产品性能稳定,经测试结果表明系统完全可以达到实时性要求,具有全天候、自主、隐蔽等优点,短时定位定向精度高<sup>[12]</sup>,拓展了我国国产化综合处理平台的设计思路,具有较高的推广和应用价值。

(上接第 101 页)

参技术[J].南京航空航天大学学报,2017,49(2):239-244.

- [6] KALANTARI A , SPENKO M .Modeling and performance assessment of the HyTAQ, a hybrid terrestrial/aerial quadrotor[J].IEEE Transactions on Robotics , 2014 , 30(5) : 1278 – 1285.

- [7] LÖTTERS J C , SCHIPPER J , VELTINK P , et al .Procedure for in-use calibration of triaxial accelerometers in medical applications[J].Sensors and Actuators A : Physical , 1998 , 68 (1 – 3) : 221 – 228.

- [8] ISLAM S , LIU P X , EL SADDIK A .Robust control of four-rotor unmanned aerial vehicle with disturbance uncertainty[J].IEEE Transactions on Industrial Electronics , 2014 , 62(3) : 1563 – 1571.

- [9] DE MARINA H G , PEREDA F J , GIRON-SIERRA J M , et al .

参考文献

- [1] 李鑫,员智凯.浅议后现代战争理论与我国军事技术变革发展趋势[J].西北工业大学学报(社会科学版),2010,40(1):98-102.

- [2] 陶敏.地面车辆定位定向系统关键技术研究[D].长沙:国防科学技术大学,2007.

- [3] 魏敬和,林军.深度学习算法、硬件技术及其在未来军事上的应用[J].电子与封装,2019,19(12):1-6,22.

- [4] 张红良.陆用高精度激光陀螺捷联惯性导航系统误差参数估计方法研究[D].长沙:国防科学技术大学,2010.

- [5] 丁文娟.捷联惯性/里程计/伪卫星车载组合导航系统研究[D].西安:西北工业大学,2006.

- [6] 龙芯中科技术有限公司安全事业部.龙芯芯片技术白皮书[Z].2017.

- [7] 刘沛文,虞亚君.基于FPGA的16位宽加载电路的8位宽载方法[J].电子与封装,2020,20(10):44-48.

- [8] 曹正州,张艳飞,何小飞,等.用于FPGA的自动阻抗匹配电路设计[J].电子与封装,2020,20(5):46-50.

- [9] 朱正国.基于1553B通信协议的总线模块设计与实现[D].西安:西安电子科技大学,2013.

- [10] 韦东山.嵌入式Linux应用开发完全手册[M].北京:人民邮电出版社,2008.

- [11] 赵宇.基于实时扩展的射频仿真系统实时控制的实现[D].南京:南京航空航天大学,2006.

- [12] 陈哲.捷联惯导系统原理[M].北京:宇航出版社,1986.

(收稿日期:2020-10-10)

---

## 作者简介：

张禹(1993-),男,本科,工程师,主要研究方向:数字信号处理、DSP、FPGA应用等面向的硬件开发和研究。

钱宏文(1975-),男,本科,研究员级高级工程师,主要研究方向:集成电路应用和微系统领域设计。

扫码下载电子文档

UAV attitude estimation using unscented Kalman filter and TRIAD[J].IEEE Transactions on Industrial Electronics , 2011 , 59(11) : 4465-4474.

- [10] 秦永元.惯性导航[M].北京:科学出版社,2014.

- [11] 杨晓,王国柱.基于 PID 控制理论的改进粒子群优化算法[J].控制工程,2019,26(8):1497–1502.

- [12] 刘春,傅丽娟,谢皓,等.基于 PID+Kalman 的姿态角算法研究[J].仪表技术与传感器,2018(2):157–161.

(收稿日期: 2020-10-21)

#### 作者简介：

任剑秋(1995-),男,硕士研究生,主要研究方向:嵌入式系统。

钟小勇(1964-),通信作者,男,硕士,教授级高级工程师,主要研究方向:无损检测、嵌入式系统及应用等,E-mail:zhongxy52@163.com。

扫码下载电子文档

## 版权声明

经作者授权，本论文版权和信息网络传播权归属于《电子技术应用》杂志，凡未经本刊书面同意任何机构、组织和个人不得擅自复印、汇编、翻译和进行信息网络传播。未经本刊书面同意，禁止一切互联网论文资源平台非法上传、收录本论文。

截至目前，本论文已经授权被中国期刊全文数据库（CNKI）、万方数据知识服务平台、中文科技期刊数据库（维普网）、DOAJ、美国《乌利希期刊指南》、JST 日本科技技术振兴机构数据库等数据库全文收录。

对于违反上述禁止行为并违法使用本论文的机构、组织和个人，本刊将采取一切必要法律行动来维护正当权益。

特此声明！

《电子技术应用》编辑部

中国电子信息产业集团有限公司第六研究所