# 一种调节供电进行温度补偿的高精度时钟电路\*

刘铭扬<sup>1,2,3</sup>,王小松<sup>1,2,3</sup>,刘昱<sup>1,2,3</sup>

(1.中国科学院微电子研究所,北京100029;2.中国科学院大学,北京100049;

3.新一代通信射频芯片技术北京市重点实验室,北京100029)

**摘要:** 基于0.18 μm CMOS标准工艺,实现了一种调节供电电压对温度进行补偿的高精度时钟电路,且有效避免了温度变化及供电波动对振荡频率的影响。相较于同种类型电路,该结构无需带隙基准源及运算放大器,在优化性能的同时,极大程度地缩减了芯片面积及电路复杂度。经仿真验证,当温度变化为-40℃~85℃时,时钟偏差小于1%,可以稳定输出频率为2 MHz的时钟信号;当供电由1.6 V波动至2.0 V时,时钟振荡频率波动仅为28 Hz。

**关键词:** 环形振荡器;温度补偿;时钟自校准

中图分类号: TN432

文献标识码: A

DOI:10.16157/j.issn.0258-7998.201026

中文引用格式: 刘铭扬,王小松,刘昱. 一种调节供电进行温度补偿的高精度时钟电路[J]. 电子技术应用, 2021, 47(5): 117–121.

英文引用格式: Liu Mingyang, Wang Xiaosong, Liu Yu. A high-precision clock circuit with temperature compensation based on power supply regulation[J]. Application of Electronic Technique, 2021, 47(5): 117–121.

## A high-precision clock circuit with temperature compensation based on power supply regulation

Liu Mingyang<sup>1,2,3</sup>, Wang Xiaosong<sup>1,2,3</sup>, Liu Yu<sup>1,2,3</sup>

(1.Institute of Microelectronics of Chinese Academy of Sciences, Beijing 100029, China;

2.University of Chinese Academy of Sciences, Beijing 100049, China;

3.Beijing Key Laboratory of Radio Frequency IC Technology for Next Generation Communications, Beijing 100029, China)

**Abstract:** Based on 0.18 μm CMOS IC process, a high-precision clock circuit that controls power supply voltage to compensate temperature was presented, which effectively avoids the influence of temperature changes and power supply voltage fluctuations on the oscillation frequency. Compared with the other types of clock generating circuit, this structure does not require bandgap reference sources and operational amplifier. While optimizing performance, it greatly reduces the chip area and circuit complexity. Under the -40℃ to 85℃ temperature range, the output frequency is stable at 2 MHz and the clock deviation is less than 1%. When the power supply voltage fluctuates from 1.6 V to 2.0 V, the variation of clock oscillation frequency is 28 Hz at most.

**Key words:** ring oscillator; temperature compensation; clock self-correction

## 0 引言

参考时钟于任何模数混合电路而言,都是尤为重要的组成部分。通常用来产生时钟信号的方式有两种:其一是使用片外晶体振荡器、陶瓷振荡器等,虽说可以输出恒定的频率,却难以避免地增加了整个系统的面积和成本;其二是设计片内集成振荡器,按照结构类型的不同,又可以划分为迟滞振荡器、LC振荡器和环形振荡器<sup>[1]</sup>。

相较于其他几种片内集成振荡器,环形振荡器仅由奇数个反相器串联而成,其功耗较低,结构简单,且输出频率不受限,所以应用范围更广。但环形振荡器的输出频率更容易受到工艺参数、温度和供电波动带来的影响,

由此带来很大的时钟偏差<sup>[2]</sup>。如何对不可抗因素造成的偏差进行补偿,以提高环振电路输出频率的可靠性与稳定性,一直都是一项具有挑战性的工作。

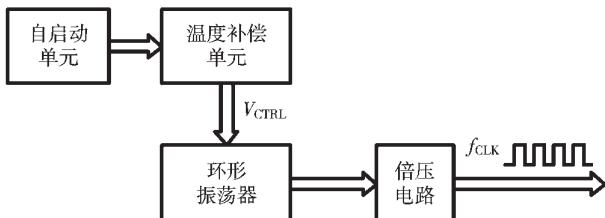

目前国内外关于温度补偿的片内时钟振荡器设计,如文献[3–6],大多使用包含运算放大器的带隙基准源、额外的片内电容、LDO稳压电路以及额外的补偿电压运算电路等进行补偿。而本文基于SMIC 0.18 μm CMOS标准工艺设计出的高精度时钟电路,无需繁冗的补偿单元,仅凭借基准电流源和超源跟随器级联的结构,便足以产生对温度自校准的补偿电压,来控制环形振荡器输出稳定的振荡频率,后又通过简单的倍压单元,最终可输出幅值为1.8 V、频率稳定在2 MHz、占空比为50%的

\* 基金项目:科技部重点研发计划(2019YFB2204500)

时钟信号,其结构框架如图 1 所示。当温度变化为 -40 ℃~85 ℃时,时钟偏差小于 1%。当供电电压由 1.6 V 波动至 2 V,在 -40 ℃~85 ℃的温度范围内,时钟输出频率的最大变化范围仅为 28 Hz。

图 1 带温度和工艺补偿的高精度时钟电路结构框图

## 1 环振及其温度补偿原理

### 1.1 环形振荡器原理

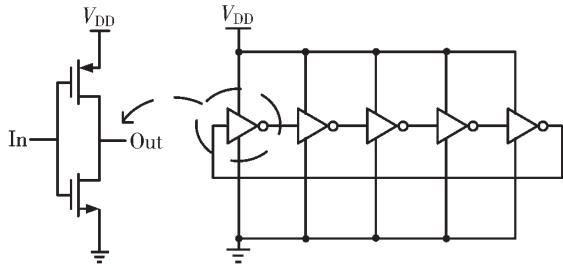

最简单的环形振荡器由奇数个反相器串联而成,在设计中选取反相器个数为 5 个,如图 2 所示。

图 2 五级反相器构成的环形振荡器

其振荡频率为:

$$f = \frac{1}{2Nt_d} = \frac{1}{10t_d} \quad (1)$$

$t_d$  为每一级反相器的传播延时,其定义如下:

$$t_d = \frac{T_{pHLL} + T_{pLH}}{2} = 0.69C_L \left( \frac{R_{eqn} + R_{exp}}{2} \right) \quad (2)$$

其中  $R_{eqn}$  和  $R_{exp}$  分别为 NMOS 和 PMOS 的导通电阻:

$$R_{eq} = \frac{1}{\mu_0 C_{ox} \frac{W}{L} (V_{GS} - V_{TH})} \quad (3)$$

为方便计算,假设 NMOS 管与 PMOS 管的寄生电容与导通电阻相同,则有:

$$f = \frac{1}{10t_d} = \frac{\mu_0 C_{ox} \frac{W}{L} (V_{GS} - V_{TH})}{0.69C_L} \quad (4)$$

### 1.2 温度对环形振荡器输出频率的影响

环形振荡器输出频率受温度的影响主要来源于载流子迁移率与阈值电压对温度的依赖关系。

从文献[7]中,可以得到载流子迁移率与过驱动电压随温度变化的关系如下:

$$\mu(T) = \mu(T_0) = \left( \frac{T}{T_0} \right)^{-1.5} \quad (5)$$

$$V_{TH}(T) = V_{TH}(T_0) [1 + TCV_{TH} \cdot (T - T_0)] \quad (6)$$

由此得出修正后的振荡频率公式如下:

$$f(T) = \frac{\mu_{T0} \cdot (T)^{-1.5} \cdot C_{ox} \frac{W}{L} (V_{GS} + V_{TH_{T0}} - \frac{TV_{TH_{T0}}}{T_0} \cdot T)}{0.69C_L} \quad (7)$$

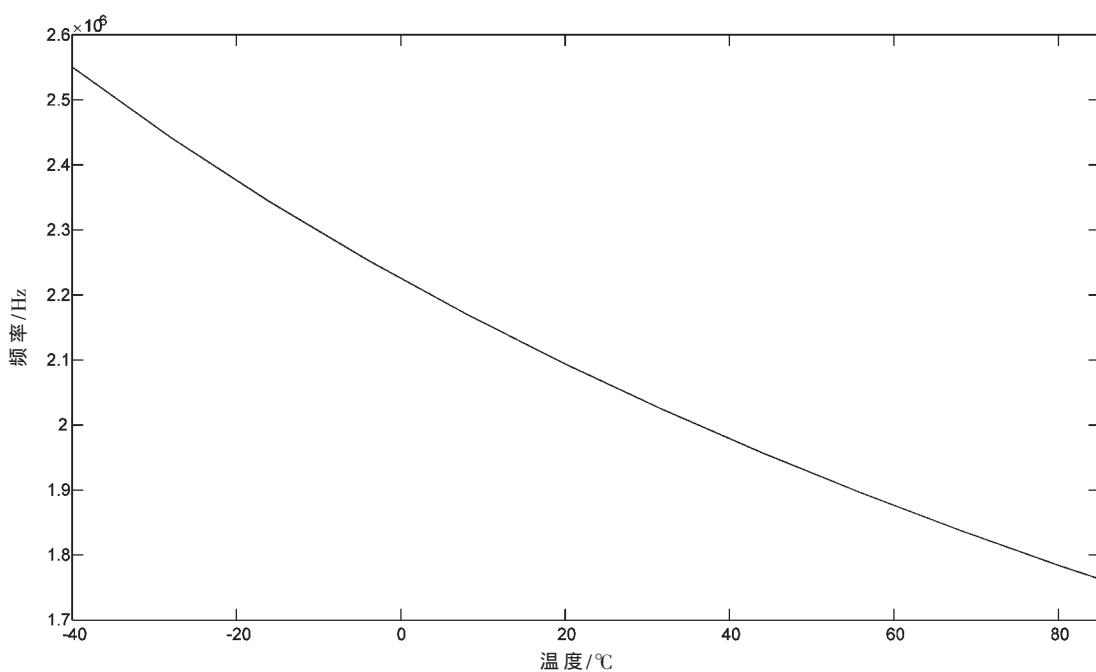

温度与环形振荡器输出频率呈负相关,温度越高,环形振荡器输出频率越低。仿真图 2 中环形振荡器输出频率随温度的变化,所得结果如图 3 所示。当温度由 -40 ℃变化到 85 ℃时,该环形振荡器输出频率的最大差值可达到 993 kHz,频率偏差最高达到 49.7%。

文献[8]以反相器输出电压的下降时间为切入点,推

图 3 五级环形振荡器频率随温度变化曲线

导出另外一种振荡频率的表达公式：

$$t_d = \mu_0 C_{ox} \frac{W}{L} \frac{V_{DD}}{(V_{DD} - V_{TH})^2} \quad (8)$$

$$f = \frac{1}{10t_d} = \frac{(V_{DD} - V_{TH})^2}{10\mu_0 C_{ox} \frac{W}{L} V_{DD}} \quad (9)$$

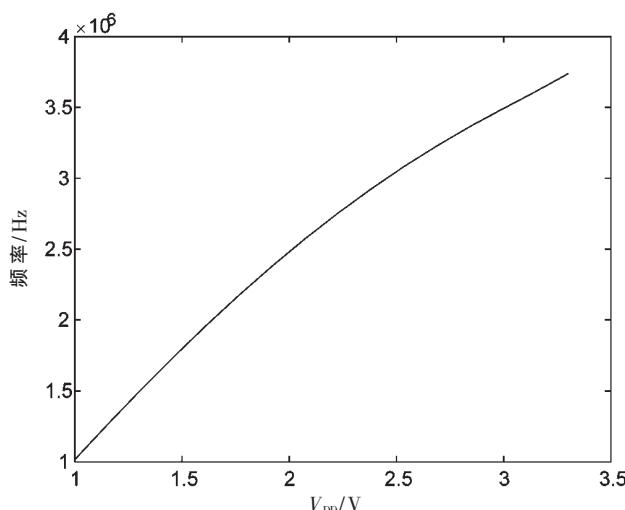

由式(9)可知,当 $V_{DD}$ 增加时,环形振荡器的输出频率也会随着增加,仿真图2中的环形振荡器,得到频率随供电波动的变化如图4所示。

图4 供电对环形振荡器输出频率的影响

供电与环形振荡器输出频率呈正相关,而温度与环形振荡器输出频率成负相关,这为我们提供温度补偿的思路,即将 $V_{DD}$ 更换为与温度呈正相关的 $V_{CTRL}$ ,随着温度增加, $V_{CTRL}$ 增加,控制环形振荡器输出频率增加,以补偿温度增加造成的环形振荡器输出频率衰减。

## 2 调节供电进行温度补偿的高精度时钟电路设计

### 2.1 温度补偿单元设计

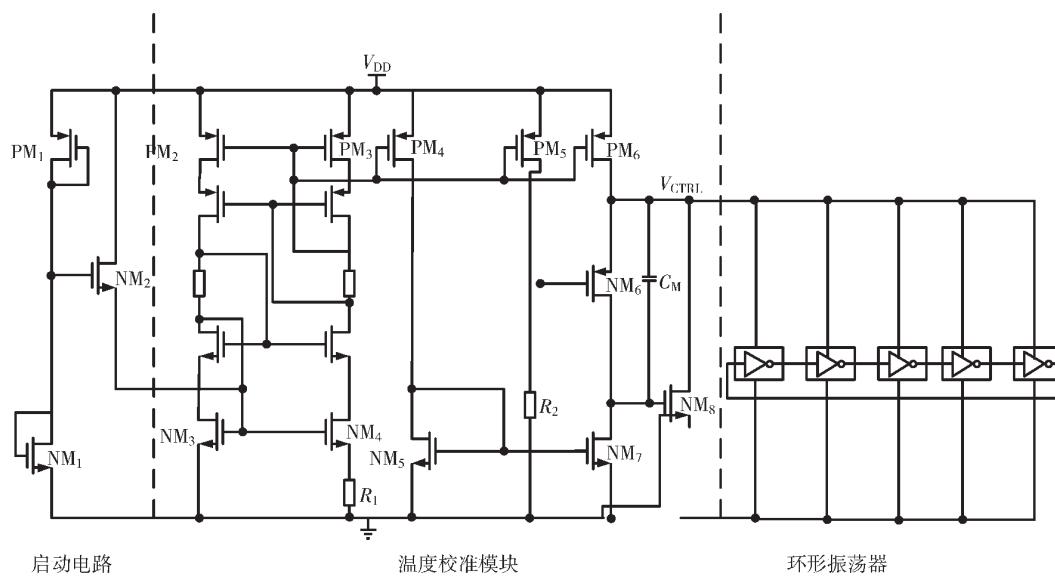

本设计中,补偿单元由自启动电路、基准电流源、超源跟随器三部分组成,其电路原理图如图5所示。

设置合适的宽长比,使 $NM_3$ 和 $NM_4$ 工作在亚阈值区,流经 $R_1$ 的电流 $I_{R_1}$ 可表示为<sup>[9]</sup>:

$$I_{R_1} = \frac{W}{L} I_0 e^{\frac{V_{GS}}{\zeta V_T}} \cdot (1 - e^{-\frac{V_{DS}}{V_T}}) \approx \frac{W}{L} I_0 e^{\frac{V_{GS}}{\zeta V_T}} \quad (10)$$

其中 $V_T = KT/q$ 。

取 $NM_4$ 的宽长比为 $NM_3$ 的N倍,则有:

$$\ln N = \frac{V_{GS3} - V_{GS4}}{\zeta V_T} = \frac{I_{R_1} R_1}{\zeta V_T} \quad (11)$$

从而得到:

$$I_{R_1} = \frac{\zeta V_T \ln N}{R_1} = \frac{\zeta K \ln N}{q R_1} T \quad (12)$$

可以发现, $I_{R_1}$ 是一个与温度正相关的 $I_{PART}$ 电流,该电流以1:1的关系镜像至 $R_2$ ,可以推导出:

$$V_{CTRL} = V_{R2} + V_{sep6} \quad (13)$$

展开 $V_{R2}$ 可得出:

$$V_{R2} = I_{R_1} \cdot R_2 = \frac{\zeta K}{q} \cdot \frac{R_1 \ln N}{R_1} \quad (14)$$

由式(14)可以得到 $V_{R2}$ 是一个正温度系数电压,且与温度呈线性关系,通过调节 $R_1$ 、 $R_2$ 、 $N$ ,即可以补偿温度变化为时钟电路带来的偏差。

流经 $PM_4$ 、 $NM_5$ 、 $NM_7$ 的电流为 $I_{R_1}$ 的等比复制,调整 $NM_8$ 的宽长比,使流经 $NM_8$ 的电流也等于 $I_{R_1}$ ,即有 $|V_{dsat6}| = V_{dsat8}$ ,展开 $V_{sep6}$ 可以得到:

$$V_{sep6} = |V_{dsat6}| + |V_{Thp}| \quad (15)$$

$$V_{sep6} = V_{gs8} - V_{Thp} + |V_{Thp}| \quad (16)$$

由式(16)可知,通过适当调节 $NM_8$ 管的尺寸,可以调

图5 温度及工艺补偿单元电路图

整  $V_{\text{sq}6}$ , 以调整  $V_{\text{CTRL}}$  的值, 既而消去温度及工艺偏差引发的阈值电压变化。

同时超源跟随器置于基准电流源与环形振荡器间, 可起到缓冲作用, 降低设计中对  $R_2$  的阻值要求, 但 NM<sub>6</sub>、NM<sub>8</sub> 构成了负反馈, 必要时可以增加米勒补偿电容  $C_M$  来提高环路的稳定性。

将式(9)中的  $V_{\text{DD}}$  替换为  $V_{\text{CTRL}}$  可得到本设计中的振荡频率公式。

$$f = \frac{V_{\text{CTRL}} - V_{\text{TH}}}{10\mu_0 C_{\text{OX}} \frac{W}{L} V_{\text{CTRL}}} \quad (17)$$

此外针对实际制造过程中的工艺偏差, 可通过修调基准电压源中  $R_1$  的电阻值以消去工艺偏差引发的环振频率变化<sup>[10]</sup>。

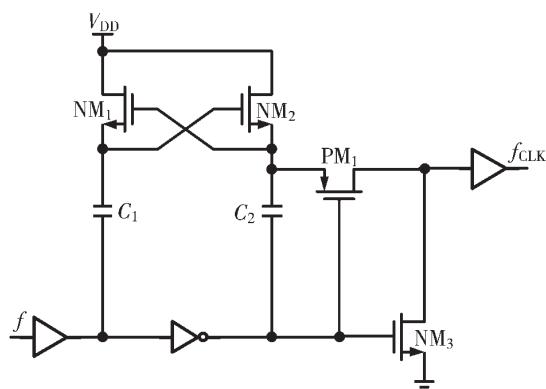

## 2.2 倍压单元的设计

环形振荡器输出信号的幅值与  $V_{\text{CTRL}}$  相等, 若想作为时钟信号后续用于数模混合电路中, 需对其进行一个抬升, 图 6 所示为一个简单的倍压电路原理图, 需注意将 PM<sub>1</sub> 的衬底连接至  $V_{\text{DD}}$  以避免寄生 PN 结的导通<sup>[10]</sup>。

图 6 倍压电路

## 3 电路仿真和测试结果

本文设计的带有温度和工艺补偿的高精度时钟电路基于 SMIC 0.18 μm CMOS 标准工艺进行仿真测试以验证正确性。

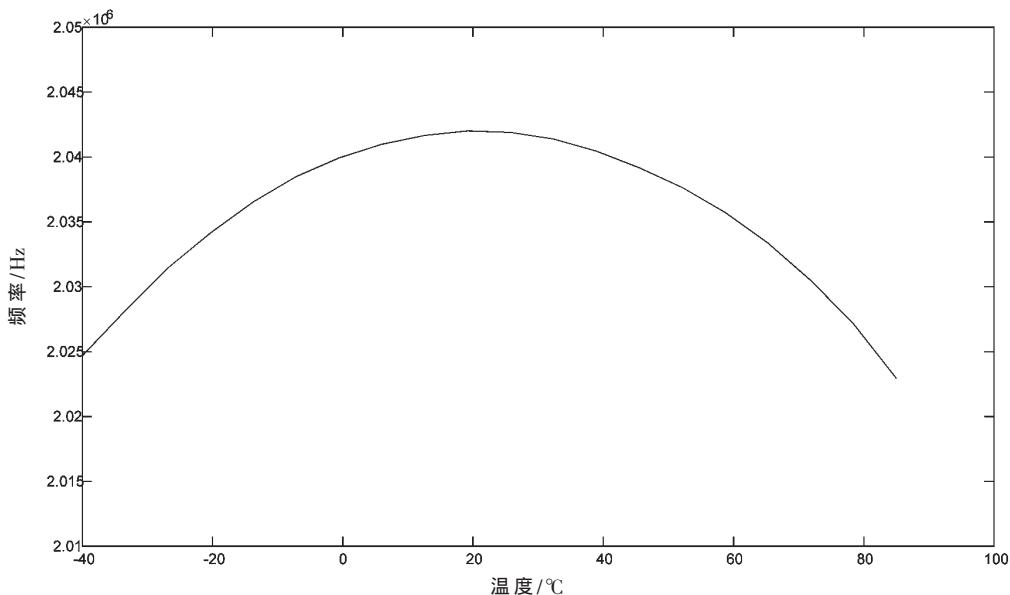

将温度扫描范围定义为 -40 ℃~85 ℃, 仿真时钟频率  $f_{\text{CLK}}$  随温度的变化曲线如图 7 所示, 时钟频率稳定在 2 MHz, 最大变化范围为 19 kHz, 时钟偏差小于 1%。

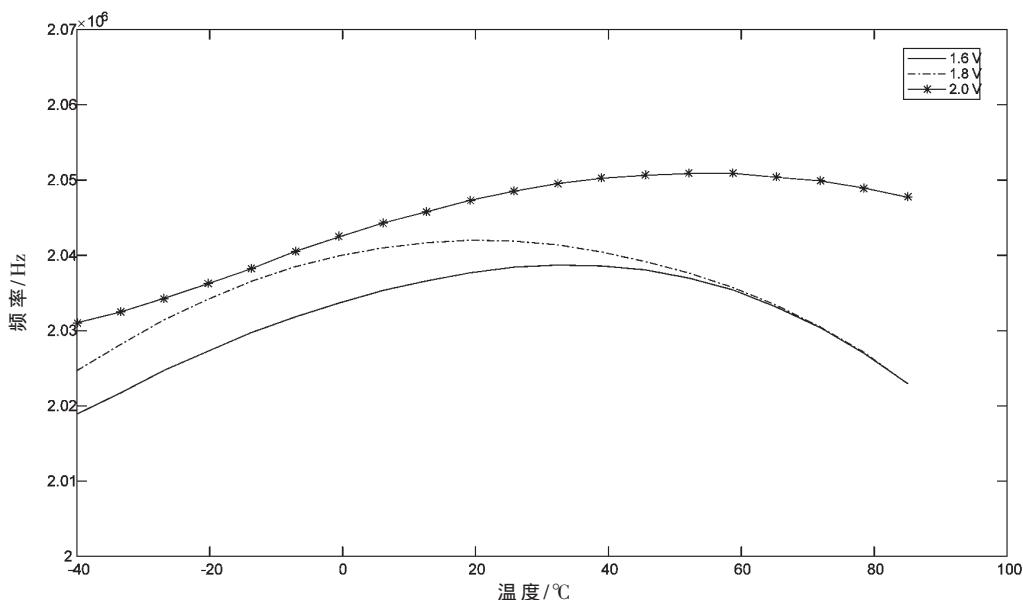

分别在 1.6 V、1.8 V、2.0 V 三种供电下进行 -40 ℃~85 ℃ 的温度扫描, 得到的仿真结果如图 8 所示。时钟频率稳定在 2 MHz, 时钟输出频率最大变化范围为 28 Hz。

本文同其他文献的测试结果对比如表 1 所示, 可以看出, 相较于其他文献, 本文的电路结构更为简单, 补偿效果也更优。

## 4 结论

本文设计了一种通过调节供电电压进行温度补偿的高精度时钟电路, 时钟的振荡频率不受温度及工艺波动的影响。仿真结果表明, 温度从 -40 ℃ 变化到 85 ℃ 时, 时钟频率最大变化仅为 19 kHz, 时钟偏差小于 1%; 当供电电压由 1.6 V 变化到 2.0 V 时, 在 -40 ℃~85 ℃ 的温度范围内, 频率变化最大值仅为 28 Hz, 且结构简单, 更易与其他模数混合电路集成。

## 参考文献

- [1] 胡磊. 基于温度和工艺补偿的高精度时钟电路技术研究[D]. 西安: 西安电子科技大学, 2017.

- [2] SUNDARESAN K, ALLEN P E, AYAZI F. Process and temperature compensation in a 7-MHz CMOS clock oscillator[J]. IEEE Journal of Solid State Circuits, 2006, 41(2): 433~442.

- [3] SUNDARESAN K, HO G K, POURKAMALI S, et al. Electronically temperature compensated silicon bulk acoustic

图 7 时钟频率随温度的变化曲线

图 8 不同供电下时钟频率随温度的变化曲线

表 1 本文与其他文献测试结果对比

| 参数    | 工艺               | 时钟偏差/%          | 振荡频率随供电的变化 | 补偿所用的方法                |

|-------|------------------|-----------------|------------|------------------------|

| 文献[1] | SMIC0.18 μm CMOS | 2.00@-40~80 °C  | -          | LDO, 带隙基准, 数字控制电路及算法校准 |

| 文献[2] | GFO.18 μm CMOS   | 2.97@-40~125 °C | -          | 带隙基准, LDO              |

| 文献[5] | HJTC0.18 μm CMOS | 2.00@-30~70 °C  | -          | 复杂的补偿电压产生及运算电路         |

| 本文    | SMIC0.18 μm CMOS | 0.95@-40~85 °C  | 28 Hz      | 基准电流源, 超源跟随器           |

resonator reference oscillators[J]. IEEE Journal of Solid-State Circuits, 2007, 42(6): 1425–1434.

- [4] 李景虎, 刘梦飞, 张兴宝. 一种工艺和温度自校正的环形振荡器[J]. 微电子学, 2017, 47(6): 64–67.

- [5] 虞晓凡, 林平分. 一种带温度和工艺补偿的片上时钟振荡器[J]. 微电子学与计算机, 2009(1): 22–26.

- [6] 李庆山, 胡锦, 李湘春. 带温度与工艺补偿的新型振荡器[J]. 固体电子学研究与进展, 2013(4): 340–345.

- [7] BAKER R J. CMOS: circuit design, layout, and simulation[M]. Wiley–IEEE Press, 2005.

- [8] BELLAOUAR A, ELMASRY M I. Low-power digital VLSI design—circuits and systems[M]. Kluwer Academic Publishers, 1995.

- [9] SANSEN W M C. Analog design essentials[J]. Springer, 2007.

- [10] RABAEEY J M, CHANDRAKASAN A P, BORIVOJE N.

(上接第 116 页)

- Module, Rev 2.5[Z]. 2018.

- [15] SFF Committee. SFF-8665, Specification for QSFP+28Gb/s 4X Pluggable Transceiver Solution(QSFP28), Rev 1.9[Z]. 2015.

- [16] SFF Committee. SFF-8679, QSFP+ 4X hardware and electrical specification, Rev1.8[Z]. 2018.

(收稿日期: 2020-09-24)

Digital integrated circuits: a design perspective[M]. Prentice Hall, 2003.

(收稿日期: 2020-10-21)

#### 作者简介:

刘铭扬(1996-), 女, 硕士研究生, 主要研究方向: 数模混合集成电路设计。

王小松(19-), 男, 博士, 副研究员, 主要研究方向: 模拟/射频/混合 CMOS 集成电路与模块、面向物联网应用的射频技术。

刘昱(1975-), 男, 博士, 研究员, 主要研究方向: 高性能模拟/射频 CMOS 集成电路、硅基毫米波集成电路、超低功耗短距离无线通信系统、高精度低功耗传感电路、物联网相关技术及医疗电子系统集成技术。

扫码下载电子文档

#### 作者简介:

解文军(1984-), 男, 硕士, 高级工程师, 主要研究方向: 芯片-封装-系统信号完整性及电源完整性仿真。

李仁刚(1980-), 男, 硕士, 芯片设计工程师, 主要研究方向: 集成电路设计技术和计算机体系结构。

韩大峰(1979-), 男, 硕士, 主任工程师, 主要研究方向: 大数据、FPGA 异构加速技术。

扫码下载电子文档

## 版权声明

经作者授权，本论文版权和信息网络传播权归属于《电子技术应用》杂志，凡未经本刊书面同意任何机构、组织和个人不得擅自复印、汇编、翻译和进行信息网络传播。未经本刊书面同意，禁止一切互联网论文资源平台非法上传、收录本论文。

截至目前，本论文已经授权被中国期刊全文数据库（CNKI）、万方数据知识服务平台、中文科技期刊数据库（维普网）、DOAJ、美国《乌利希期刊指南》、JST 日本科技技术振兴机构数据库等数据库全文收录。

对于违反上述禁止行为并违法使用本论文的机构、组织和个人，本刊将采取一切必要法律行动来维护正当权益。

特此声明！

《电子技术应用》编辑部

中国电子信息产业集团有限公司第六研究所