# 基于 FPGA 的 LVDS 无时钟数据传输方案设计与实现 \*

毕彦峰<sup>1</sup>, 李杰<sup>1</sup>, 胡陈君<sup>2</sup>

(1. 中北大学 电子测试技术重点实验室, 山西 太原 030051;

2. 苏州中盛纳米科技有限公司, 江苏 苏州 215123)

**摘要:** 针对离线式弹载数据采集存储设备小型化需求, 设计了一种基于 FPGA 的 LVDS(Low-Voltage Differential Signaling)无时钟高速数据传输系统。在不外挂接口芯片的情况下, 用板载时钟代替差分时钟, 仅使用一对差分管脚即可完成一路 LVDS 无时钟数据传输, 系统中数据接口较多时可以很大程度上减少板卡体积。通过提高 FPGA 内部 SERDES(Serializer-Deserializer)反串行化比例以及数据进行 8B/10B 编码解决鉴相器失效的问题, 并以此为板载时钟提供准确的相位信息来对齐串行数据和模拟时钟, 最后按照模拟时钟将串行 LVDS 数据反序列化, 从而达到板载时钟代替 LVDS 随路时钟的目的, 以此实现基于 FPGA 无随路时钟的 LVDS 高速传输。试验表明, 该系统能够可靠、有效工作, 具备一定工程实用价值。

**关键词:** FPGA; 无时钟传输; LVDS; SERDES

中图分类号: TN919; TP274

文献标识码: A

DOI: 10.16157/j.issn.0258-7998.201076

中文引用格式: 毕彦峰, 李杰, 胡陈君. 基于 FPGA 的 LVDS 无时钟数据传输方案设计与实现[J]. 电子技术应用, 2021, 47(6): 62-66.

英文引用格式: Bi Yanfeng, Li Jie, Hu Chenjun. Design and implementation of LVDS clockless data transmission scheme based on FPGA[J]. Application of Electronic Technique, 2021, 47(6): 62-66.

## Design and implementation of LVDS clockless data transmission scheme based on FPGA

Bi Yanfeng<sup>1</sup>, Li Jie<sup>1</sup>, Hu Chenjun<sup>2</sup>

(1. State Key Laboratory of Electronic Testing Technology, North University of China, Taiyuan 030051, China;

2. Suzhou Zhongsheng Nanotechnology Company, Suzhou 215123, China)

**Abstract:** Aiming at the miniaturization requirements of off-line bomb-borne data acquisition and storage equipment, an FPGA-based LVDS clockless high-speed data transmission system is designed. Without an external interface chip, the onboard clock is used to replace the differential clock, and only a pair of differential pins can complete a LVDS clockless data transmission. When there are many data interfaces in the system, the board volume can be greatly reduced. The problem of phase detector failure is solved by increasing the deserialization ratio of the FPGA internal SERDES and 8B/10B encoding of the data, so to provide accurate phase information for the onboard clock to align the serial data and the analog clock. Finally, following the analog clock, the serial LVDS data is deserialized, so as to achieve the purpose of replacing the LVDS accompanying clock with the onboard clock, so as to achieve high-speed LVDS transmission based on FPGA without accompanying clock. Tests show that the system can work reliably and effectively, and has certain engineering practical value.

**Key words:** FPGA; no clock transmission; LVDS; SERDES

## 0 引言

常规弹药制导化改造试验过程中, 事后回读弹载数据记录仪所记录的各种指令参数是测试反馈中重要的方式。在靶场测设发射导弹之前, 数据回读也是监测弹药状态的一种十分重要的方式。随着科技的进步, 数据存储设备愈发趋近小型化、高速化, 所能提供的数据回

读接口也越来越少, 导致对采集存储设备进行数据回读时无法同时满足速度快和接口少的条件<sup>[1-2]</sup>。

在采集侵彻或冲击信号时, 由于所需要的采样频率较高, 产生的数据量较大, 普通的低速并行接口无法进行高速数据传输, LVDS 接口采用高速串行差分协议, 抗干扰能力强, 可以满足高速传输的需求<sup>[3-4]</sup>。但是由于弹上测量设备空间有限, 而传统的 LVDS 接口包含一路差分数据和一路差分时钟, 系统中一般采用主控芯片外挂

\* 基金项目: 国家自然科学基金(61973280)

LVDS 传输芯片的模式<sup>[5-6]</sup>,当多路 LVDS 接口同时使用时会过多占用弹内有限的空间。因此,本文提出一种基于 FPGA 的无随路时钟的高速数据传输方案,仅使用一对差分引脚传输一路 LVDS 差分数据就可以实现 1 Gb/s 的板间数据通信,无需外挂 LVDS 芯片并将通信接口的数量减半,当系统中有多路 LVDS 接口时可以很大地减少接口数量。具体来说,该方案的主要内容体现在以下几个方面:(1)用板载时钟模拟传统差分时钟实现无时钟 LVDS 传输数据,以达到精简接口的目的;(2)利用 SERDES 内部鉴相器解决每次上电时板载时钟和差分数据初始相位处于随机状态所导致的误码问题;(3)提出利用 8B/10B 编码解决传输连续相同电平时鉴相器失效的问题;(4)扩展 SERDES 的反序列化比例至 10:1 来完成 8B/10B 编码后的数据反序列化。

## 1 系统总体设计

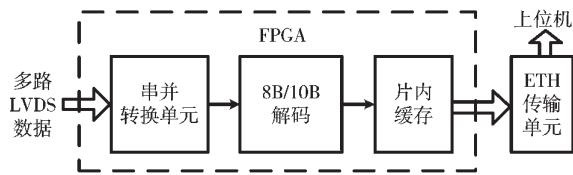

如图 1 所示,系统主要由串并转换单元、8B/10B 编码、片内缓存和以太网传输单元四部分组成。串并转换单元负责模拟 LVDS 随路时钟,参照鉴相器提供的相位关系对齐模拟时钟和 LVDS 数据,并将高速串行数据转换成为 10 bit 并行数据。8B/10B 解码模块主要负责将接收到的 10 bit 并行数据转换成为有效的 8 bit 数据。经过片内 RAM 缓存,通过以太网将数据传输到上位机。

图 1 系统总体设计

### 1.1 模拟随路时钟设计

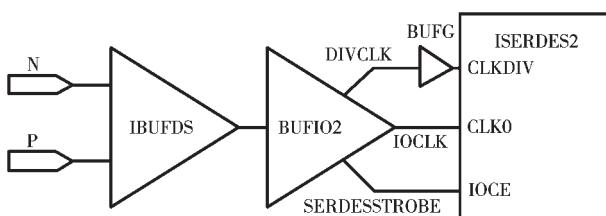

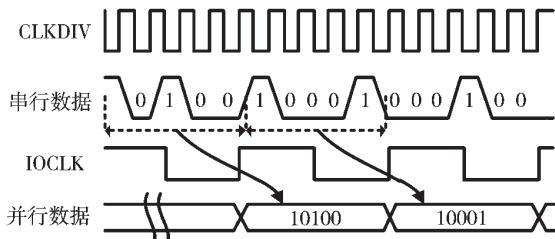

传统的 LVDS 数据传输总线包含一路 LVDS 差分数据和一路 LVDS 差分随路时钟。差分数据在传输时需同步于差分时钟,数据在进行反序列化时也需要参考随路时钟。但很多弹载数据存储设备由于接口数量有限,无法同时提供 LVDS 差分数据和随路时钟。考虑到在实际数据传输时,链路双方采用已知的固定时钟频率进行数据传输,即可以采用一种回读系统自己提供时钟的方式来模拟随路时钟,并将数据按照此时钟进行串并转换。这种时钟需要模拟真实的随路时钟,为串并转换模块提供参考时钟和选通脉冲 STROBE。传统的随路时钟处理方式如图 2 所示,差分随路时钟通过 IBUFDS 和 BUFI02

图 2 传统随路时钟处理方式

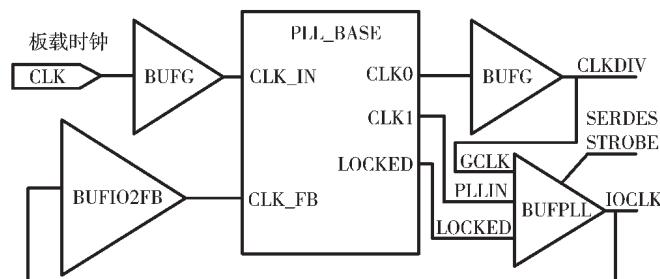

为 ISERDES 提供 CLKDIV、IOCLK 和 SERDESSTROBE 3 个信号<sup>[7-8]</sup>。在模拟随路时钟时同样需要产生这 3 个信号,如图 3 所示,利用板载时钟通过锁相环倍频产生 CLKDIV,并通过 BUFPPLL 可以产生 IOCLK 和 SERDESSTROBE 信号。

图 3 板载时钟模拟随路时钟

### 1.2 相位调整技术研究

利用 FPGA 内部提供的 ISERDES 对数据进行反序列化时需要参考 CLKDIV 时钟,但由于 CLKDIV 时钟是根据板载时钟通过 PLL 生成的,因此 CLKDIV 时钟的相位与板载时钟保持一致。而每次上电时,LVDS 差分数据与 CLKDIV 的初始相位关系处于一个随机的状态,在这个初始相位关系条件下依照 CLKDIV 对数据进行反序列化,若不满足触发器的静态时序要求,在高速传输时会产生极大的误码导致无法传输有效的数据。可以利用 FPGA 内部的 IODELAY 对数据通路添加延迟并且保持时钟的相位不变的方式来产生相位偏移,从而达到调节数据和时钟相位关系的目的。但是每当系统重新上电或复位时,这种数据和时钟的初始相位状态是随机的,调节相位关系无法通过添加固定时间的延迟来解决,所以在设计时只能采取在传输数据的过程中动态地调整相位关系。FPGA 内部的 SERDES 提供的鉴相器可以检测当前数据相对于参考时钟的上升沿相位超前或者滞后,可以根据鉴相器提供的相位关系动态地调节 IODELAY 的延迟值,这样系统复位、布线或者温度等因素导致的相位偏移都可以通过这种动态调节的方式调整到最佳的相位关系,从而有效地按照板载时钟将串行数据反序列化。

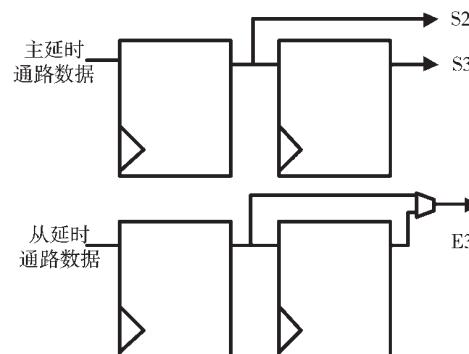

鉴相器的结构和原理如图 4 所示,S2 和 S3 相差一

图 4 鉴相器电路

一个时钟周期,通过判断 S2 和 S3 不相等来判定串行数据是否发生变化。通过比较 S3 和 E3 来指示相位关系是超前还是之后。即只有在  $S2 \neq S3$  的条件下,E3 和 S3 产生的相位检测结果才是有效的。当串行数据连续发送相同的数值时 S2 始终等同于 S3,即连续的 0 或者连续的 1,会使得相位检测模块失效,直到发生电平翻转才可以恢复相位检测。当进行连续相同电平的传输,会导致鉴相器长时间失效,这种相位的校准机制就会暂时停止,此时如果受到温度等影响产生相位的偏移,若不满足时序收敛的条件则会产生误码,这个问题可以通过对数据进行 8B/10B 编码解决。8B/10B 编码一般使用在交流耦合中来实现直流均衡,在本设计中数据发送前端对数据进行 8B/10B 编码,数据回读系统进行数据回读时,可以通过 8B/10B 解码将数据恢复成为有效信号。通过 8B/10B 编码进行扰码的数据会保证一段时间的直流平衡,即一段时间内的 0 和 1 数量相等<sup>[9]</sup>。将数据进行 8B/10B 编码传输时,连续的相同电平最高不会超过 5 bit,即最少每 5 bit 会进行一次相位检测,可以为数据的正确恢复提供足够的电平跳变,这样即使有连续相同电平的 8 bit 数据也会被编码为含有电平跳变的 10 bit 数据。典型数据的 8B/10B 编码如表 1 所示,在传输多个连续相同的电平时,都会被插入多个电平跳变,可以防止鉴相器的长时间失效。

### 1.3 比例扩充设计

利用 8B/10B 编码可以解决鉴相器失效的问题

题,但是这种编码传输的方式又会带来一个新的问题,FPGA 内部的 SERDES 最高支持 8:1 比例的数据反序列化,而对数据进行 8B/10B 编码后,数据位宽从 8 位扩展到了 10 位,从而无法实现对串行数据的反序列化。

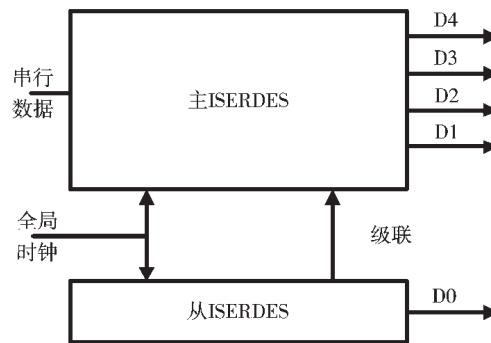

FPGA 内部单个 SERDES 支持 2:1~4:1 比例范围的数据反序列化,将两个相邻的 SERDES 级联可以完成 2:1~8:1 比例范围的数据反序列化。当需要对数据进行 10:1 比例反序列化时,可以采用一种巧妙的方式,通过对数据进行 2×5:1 比例反序列化来实现。

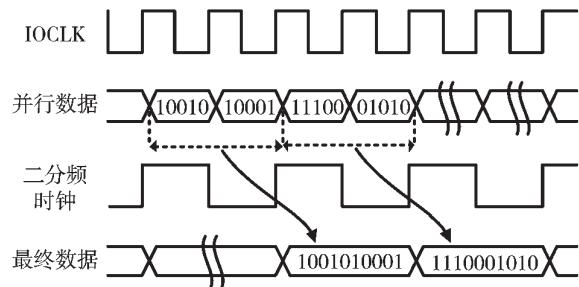

如图 5 和图 6 所示,当需要对串行数据 1010110001 进行 10:1 的数据反序列化,可以分别对前 5 位 10101

图 5 数据反序列化

图 6 比例转换

和后 5 位进行 5:1 比例的反序列化,最后将两次转化的数据进行拼接,即可完成 10:1 比例的数据反序列化。利用 SERDES 进行 5:1 反序列化的电路连接图如图 7 所示。

图 7 反序列化连接图

### 1.4 帧格式设计

当传输串行数据时,LVDS 总线前端将并行数据序列化进行传输,串并转换单元需要将串行数据转换成并行数据,此时需要对数据进行对齐,即确定哪一位才是这一帧的第一位。通过 LVDS 链路双方约定固定帧的方式来确定当前总线是否空闲和数据是否对齐完成。若当 LVDS 总线初始化或空闲时,总线上的数据不为约定好的固定帧,则需要使能 SERDES 的 BITSLIP 信号<sup>[10]</sup>,每使能一次,则相当于串行数据的起始位置向后顺延一位,直到并行数据与约定的固定帧一致时则表示数据对齐。固定帧首先考虑的 0x55(0b01010101) 和 0xAA(0b10101010),在经过 8B/10B 编码后变成 0b1010101010 和 0b0101010101,虽然完美地实现了直流均衡和电平跳变,但是进行数据对齐时无法确定哪一位才是数据的起始位。本系统采用不断发送 0xA9(0b1010100110),数据 0xA9 进行 8B/10B 编码后会变成 0b1010100110,能够满足 LVDS 传输时要求的直流均衡以及提供了足够的电平翻转。

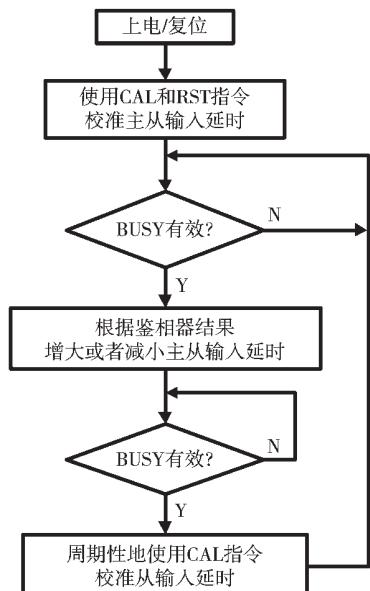

相位校准的基本流程如图 8 所示,校准相位需要周期性地使能 CAL,每使能一次,会经过 28 个周期的校准时间,即每次校准最少需要 28 个时钟周期。SPARTAN-6 系列 FPGA 内部 IODELAY2 最多支持 255 个 TAP 的校准,一般调整相位只需要调整 128 个 TAP,所以最多只

图 8 相位校准的基本流程

需要 3 584 个时钟周期即可完成校准。在校准完成之前, LVDS 总线前端需要持续发送空闲数据。由于 INCDEC 信号只能指示当前数据和时钟的上升沿相位超前或者滞后, 因此当校准成功后, INCDEC 会持续保持电平翻转的状态。所以当相位校准完成前, LVDS 总线需要一直发送空闲数据 0x2A6, 当完成校准后, 才可以发送有效数据。

### 1.5 以太网传输

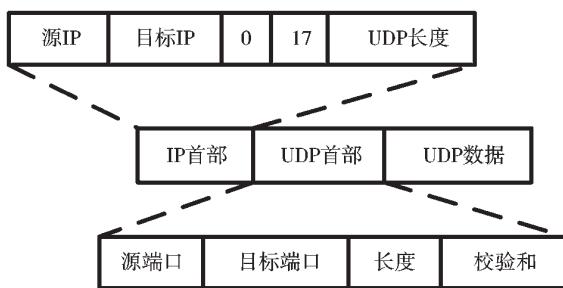

以太网传输采用 UDP(用户数据报协议)传输, UDP 是传输层的协议, 是一种无连接的传输, 在基本的 IP 数据报服务至上增加了差错检测。相比于 TCP 传输, UDP 传输不需要在端系统维护连接状态, 减少了不必要的开销, 增大了传输速度<sup>[11-13]</sup>。UDP 通信的帧格式如图 9 所示。

图 9 UDP 帧格式

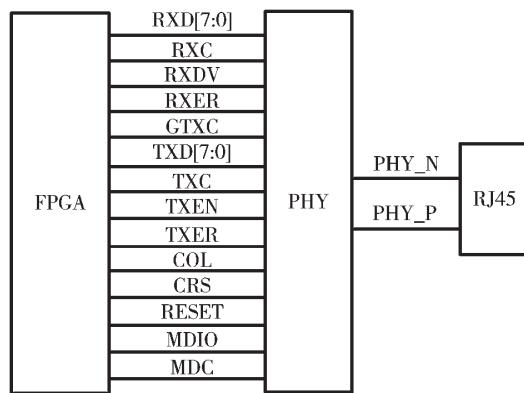

PHY 芯片采用 RTL8211EG, 可以实现 GMII 接口传输。FPGA 与 PHY 芯片的连接如图 10 所示, 使用 FPGA 充当 MAC 侧, 控制 PHY 芯片进行 UDP 协议传输。在实际传输时将控制好的 UDP 数据帧依次发送, FPGA 驱动 TXC、TXD 和 TXEN 向 PC 端发送数据, 数据格式必须满足 UDP 通信数据格式, 数据才能被 PC 接收到, 否则就

图 10 FPGA 与 PHY 连接图

会被网卡物理层丢弃<sup>[14-16]</sup>。

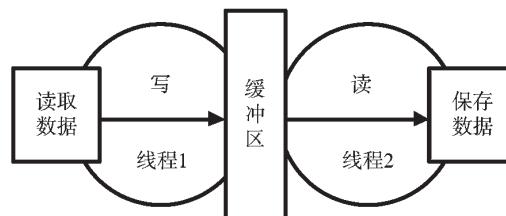

PC 接收端上位机采用 Qt 框架 C++ 语言编写, 缓冲区设计采用 4K 对齐, 有效地提高存储速度。为了提高以太网接口的传输速度, 上位机采用多个线程并设置了两个大容量缓冲区, 缓冲区的设计如图 11 所示, 其中一个线程读取以太网中的数据并将数据保存在其中一个缓冲区中, 当一个缓冲区存满之后, 继续将数据保存在另一个缓冲区, 另一个线程负责将存满数据的缓冲区写到文件中。两个线程同时工作, 读取以太网的数据与写文件同时进行, 有效地提高了传输速度。

图 11 缓冲区设计

### 2 硬件测试

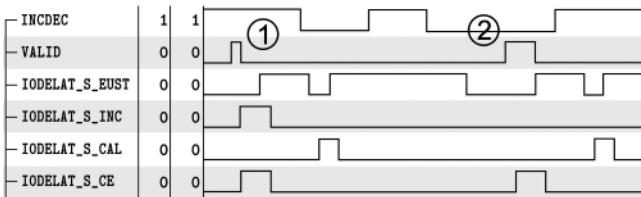

首先, 使用 Xilinx 公司提供的 ICON 和 ILA 两个 IP 核进行测试, 验证整个相位校准的流程。如图 12 所示抓取的真实波形, 根据图中标记①, 当鉴相器 VALID 信号拉高时, INCDEC 指示的相位状态有效。获取到当前数据和时钟的相位关系后, 开始进行相位校准, 使能 IODELAY 的 CE 信号, 并根据 INCDEC 指示的状态控制 IODELAY 的 INC 信号将信息传递给 IODELAY, IODELAY 接收到相位信息则会进入 BUSY 状态, 当 BUSY 拉低时, 即可使能 IODELAY 的 CAL 信号, 此时 IODELAY 再次进入 BUSY 状态开始调整延迟, 当 BUSY 再次拉低时表示延迟调整完成。紧接着进入标记②的状态, 延迟调整完成后鉴相器会再次指示调整之后的相位关系。从图中可以看到, 在 VALID 信号有效时, INCDEC 处于高低电平的跳变状态, 此时相位的校准已然完成, 实际的相位校准流程与图 8 相符。

接下来对系统进行硬件测试, 连接时线缆采用双绞

图 12 相位校准的实际过程

线。测试时 LVDS 前端发送真实数据,首先需要发送空闲数据 0xA9,当相位校准完成后再发送有效数据,保证 LVDS 数据回读设备完成相位校准后再进行数据接收。由于数据回读设备内部的状态机首先进行相位校准,因此最开始的空闲数据不会被传输,如图 13 所示,当有效数据传输开始时,LVDS 发送端数据的产生速度小于总线的传输速度,所以在传输的过程中会有等待填充数据产生。

图 13 实际工程数据

### 3 结论

本文分别从硬件总体设计、模拟随路时钟的实现过程、校准数据和时钟相位关系的原理和实现过程以及通过提高 SERDES 反串行化比例实现 8B/10B 编码解决鉴相器失效的问题 4 方面介绍了基于 LVDS 的无随路时钟高速数据回读系统的设计与实现。通过对 FPGA 内部信号的抓取可以直观地观察到校准模拟时钟和串行数据相位关系的过程,整个校准过程符合 IODELAY 调整延迟的固有流程。通过对整个数据回读系统进行整体测试,读取码率为 1 Gb/s 的 LVDS 总线数据,前端数据为真实的工程数据,结果与程序设计一致。经过验证,通过数据回读设备板载时钟模拟 LVDS 随路时钟、提高 SERDES 反串行化比例实现 8B/10B 编码和利用鉴相器将数据和时钟对齐的方式能有效地将无随路时钟的高速串行数据反序列化,去除掉 LVDS 随路时钟,减少 LVDS 总线的接口线缆数量,实现了一种接口数量少并且传输速度快的数据传输系统,为离线式数据存储系统的回读提供了一种传输速度快、灵活可靠和可移植性强的方案。

## 参考文献

- [1] 王瀚,李杰,雷文彬,等.智能弹药飞参数据高速回读系统关键技术研究[J].电子技术应用,2019,45(11):55-58.

- [2] 李化雷,段晓超.高速串行 LVDS 在雷达波控系统中的应用[J].信息技术与信息化,2019(7):112-114.

- [3] 程洪涛,赵冬青,储成群,等.基于 LVDS 的高速数据存储系统优化设计[J].实验室研究与探索,2018,37(5):74-77,99.

- [4] 郭佳欣.基于 LVDS 的图像采集存储装置的设计与实现[D].太原:中北大学,2017.

- [5] 张尊.基于 LVDS 的高速自同步串行传输系统的研究[J].科技经济市场,2019(5):6-8.

- [6] 周弟伟.基于 LVDS 的长距离高速串行数据传输系统设计[J].信息通信,2019(6):55-56.

- [7] 雷武伟,文丰,刘东海,等.基于 LVDS 的高可靠性远距离数据传输设计[J].电子技术应用,2019,45(6):130-134.

- [8] 陈英骥.基于 FPGA 高速 SerDes 串行接口模块发送端设计[D].西安:西安电子科技大学,2018.

- [9] 王俊杰,万书芹,叶明远,等.一种低延时的多通道 8B/10B 编码器设计[J].光通信技术,2020,44(2):33-36.

- [10] 罗远彦,曹伟.利用 SERDES 和 FPGA 完成的低成本高清图像数据发送设计[J].数字技术与应用,2015(5):139.

- [11] 陈军旗,赵凤怡.基于 FPGA 的千兆以太网图像采集系统设计[J].通讯世界,2019,26(5):18-19.

- [12] 吴长瑞,徐建清,蒋景红.基于 FPGA 的千兆以太网接口应用研究与实现[J].现代电子技术,2018,41(9):1-5.

- [13] 包海燕,孟欢.千兆以太网 MAC 的 FPGA 实现与设计[J].电子产品世界,2018,25(6):67-70.

- [14] 王媛丽.基于 FPGA 千兆以太网数据传输系统设计[J].数字技术与应用,2015(12):160-161.

- [15] 温杰,李锦明,闫晓俊.基于千兆以太网的高速图像传输设计[J].计算机测量与控制,2015,23(11):3707-3708,3712.

- [16] 李洋,禹卫东,胡晓,等.基于 FPGA 的千兆以太网数传系统设计[J].电子测量技术,2015,38(10):72-77.

(收稿日期:2020-11-05)

### 作者简介：

毕彦峰(1995-),男,硕士研究生,主要研究方向:高速数据传输和存储、惯性导航。

李杰(1976-),男,博士,教授,主要研究方向:微系统集成理论与技术、惯性感知与控制技术、组合导航理论、计算几何及智能信息处理等。

扫码下载电子文档

## 版权声明

经作者授权，本论文版权和信息网络传播权归属于《电子技术应用》杂志，凡未经本刊书面同意任何机构、组织和个人不得擅自复印、汇编、翻译和进行信息网络传播。未经本刊书面同意，禁止一切互联网论文资源平台非法上传、收录本论文。

截至目前，本论文已经授权被中国期刊全文数据库（CNKI）、万方数据知识服务平台、中文科技期刊数据库（维普网）、DOAJ、美国《乌利希期刊指南》、JST 日本科技技术振兴机构数据库等数据库全文收录。

对于违反上述禁止行为并违法使用本论文的机构、组织和个人，本刊将采取一切必要法律行动来维护正当权益。

特此声明！

《电子技术应用》编辑部

中国电子信息产业集团有限公司第六研究所