# 高速电力线载波信道分析模块的设计与实现

郝伟琦,王贤辉,李 锋,肖德勇,陈奎熹

(北京智芯微电子科技有限公司,北京 102200)

**摘要:** 高速电力线载波信道噪声环境复杂,而现有设备难以对载波信道噪声采集和测量分析。为此,提出了一种高速电力线载波信道分析模块,可实现现场噪声高精度样本采集、信道衰减特性测试等功能,并且可在实验室测试环境中进行噪声回放,实现现场环境的真实模拟。首先介绍了分析模块的硬件架构组成,描述了FPGA逻辑电路的状态机设计及嵌入式软件设计方案,最后对研制的样机进行了测试,结果表明信道分析模块能够满足设计要求的所有功能,解决了高速电力线载波通信芯片对抗噪声技术研究和现场运维测试的难题。

**关键词:** 高速电力线载波通信;信道噪声;高速信号采集;FPGA

中图分类号: TN919.5

文献标识码: A

DOI:10.16157/j.issn.0258-7998.201119

中文引用格式: 郝伟琦,王贤辉,李铮,等. 高速电力线载波信道分析模块的设计与实现[J]. 电子技术应用, 2021, 47(6): 100–104, 109.

英文引用格式: Hao Weiqi, Wang Xianhui, Li Zheng, et al. Design and implementation of a HPLC channel analysis module[J]. Application of Electronic Technique, 2021, 47(6): 100–104, 109.

## Design and implementation of a HPLC channel analysis module

Hao Weiqi, Wang Xianhui, Li Zheng, Xiao Deyong, Chen Kuixi

(Beijing Smart Chip Microelectronic Co., Ltd., Beijing 102200, China)

**Abstract:** The noise environment of HPLC channel is complex, but the existing equipment is difficult to collect and analyze the channel noise. Therefore, this paper proposes a HPLC channel analysis module, which can realize the functions of high-precision sample collection, channel attenuation characteristic test, etc., and can play back the noise in the laboratory test environment to realize the real simulation of the field environment. Firstly, the hardware architecture of the analysis module is introduced, the state machine design of FPGA logic circuit and embedded software design are described. Finally, the prototype is tested. The results show that the channel analysis module can meet all the functions of the design requirements, and solve the problems of HPLC communication chip anti noise research and field maintenance test.

**Key words:** HPLC; channel noise; high speed signal acquisition; FPGA

## 0 引言

电力线载波通信(Power Line Communication, PLC)是一种使用电力线作为物理通信介质的通信方式。利用电力线等媒体传输数据信息,可以降低运营成本、减少构建新的通信网络的支出<sup>[1]</sup>。而相比窄带载波,高速载波具有速率高、抗干扰能力强等优点,可以应用于用电信息采集、智慧能源等多场景,作为解决“最后一公里”问题的有效传输模式,是组成电网信息物理系统的基础底层网络构件<sup>[2]</sup>。但与传统通信介质相比,电力线上各类电力负载的接入及其接入的变化就造成了复杂多变的电力线信道特性<sup>[3-4]</sup>,影响电力线信道通信质量的特性有线路阻抗、噪声等<sup>[5]</sup>,其中噪声是影响低压电力线载波通信质量的重要因素<sup>[6]</sup>。

当前载波通信领域正在研究各种抗噪声方法以提高抗噪声干扰能力<sup>[7]</sup>。传统抗噪声研究的一般流程为现

场采集,实验室仿真,最后进行现场测试。该方式在实验室难以还原现场复杂的噪声环境,而在现场验证费时费力,覆盖噪声场景有限,难以应对大规模高速电力线载波现场调试运维需求。

为此,本文提出了一种高速电力线载波信道分析模块,可实现噪声采集、噪声分析、数据存储、信道测试等功能,并且可在实验室模拟真实现场环境。本信道分析模块基于现场可编程门阵列(Field Programmable Gate Array, FPGA)和模拟前端(Analog Front End, AFE)芯片实现,成本相对较低,便于携带,解决了高速电力线载波通信中噪声研究和现场运维测试的难题。

### 1 噪声分析模块架构设计

#### 1.1 功能指标定义

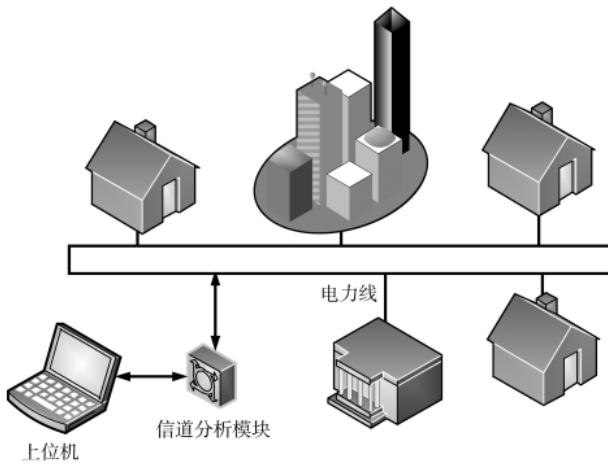

信道分析模块的连接示意图如图1所示。图中所示为一个典型的电力线环境,信道分析模块通过电力线耦

图 1 信道分析模块连接示意图

合接口连接至电力线,可以从电力线采集或向电力线注入噪声。数字通信接口连接至上位机,可由上位机控制模块的工作状态。

为满足高速电力线载波通信中噪声研究和现场运维测试的需求,噪声分析模块需具备以下主要功能:

**噪声采集功能:**采集带宽 0.2~25 MHz,单次采集时长大于 20 ms;支持单次采集、多次采集、随机延时盲采等多种方式。

**噪声分析功能:**现场噪声频谱的 FFT 实时分析,找出干扰频点分布。

**噪声录波回放功能:**支持回放噪声信号的装载、循环回放,多种噪声切换等。

**噪声信号发生功能:**白噪声、脉冲噪声、窄带噪声、扫频噪声等。

**信道测量功能:**支持单频、扫频等测量信号发生,测量信号的接收和分析,进行信道衰减测试。

## 1.2 模块架构设计

信道分析模块架构分为模拟信号处理、数字信号处理和主控制器三部分;模拟信号处理电路基于 AFE 芯片 AD9866 搭建,采样率为 50 MS/s,采样位宽为 12 bit,可采集并重建覆盖高速载波通信频段的噪声信号。数字信号处理和主控制器基于 FPGA 及 MCU 设计,两者采用 SPI 总线互联,实现模拟信号的高速采样、FFT 分析与回放功能。FPGA 与 MCU 协同工作,由 FPGA 硬件逻辑处理高速数据的采集及缓冲,MCU 负责对 FPGA 的控制及文件系统处理。

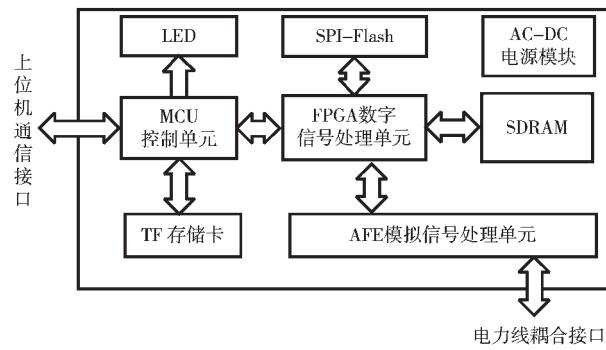

信道分析模块原理结构框图如图 2 所示。模拟信号处理电路将来自电力线的模拟信号放大后转换为数字信号,经由 FPGA 进行处理,并且可将 FPGA 输出的数字信号转换为模拟信号,注入电力线进行发送。FPGA 主要进行高速数字信号的处理工作,SDRAM 存储器实现采样数据缓存,MCU 控制器实现了文件及控制接口,SPI-Flash 用于保存 FPGA 的配置文件,AC-DC 电源模块用于为系统供电。

图 2 信道分析模块原理结构框图

## 2 主要功能模块实现

### 2.1 FPGA 逻辑模块划分

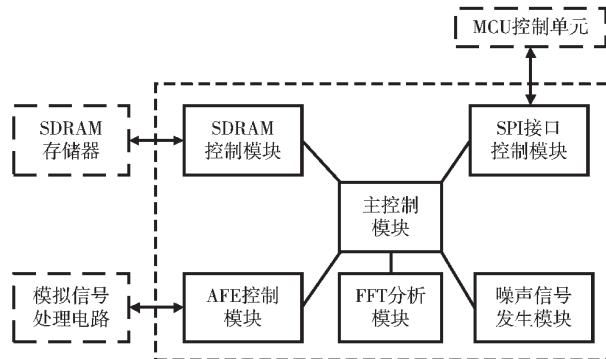

依据系统功能及架构,模拟信号的采样率选择为 50 MHz,在 12 bit 位宽下数据吞吐率为 600 Mb/s,需要使用 SDRAM 进行数据缓冲。根据系统功能需求,FPGA 内部逻辑模块的划分如图 3 所示。

图 3 FPGA 内部逻辑模块

**主控模块:**运行主状态机,协调 FPGA 内部各个模块工作,解析 MCU 通过 SPI 下发的指令码。

**SDRAM 控制模块:**控制外部 SDRAM 存储器,实现数据存储、读取及刷新逻辑。

**AFE 控制模块:**控制 AD9866 芯片实现模数及数模转换,实现模拟信号的接收及发送。

**信号发生模块:**控制可编程噪声信号数字激励的生成,用于波形发生功能。

**FFT 分析模块:**用于实时分析采集到的信号频谱信息,用于噪声实时分析及信道衰减测试。

**SPI 接口控制模块:**作为控制命令及数据交互通道,对外接口符合 SPI 接口标准<sup>[8]</sup>。

### 2.2 主控模块

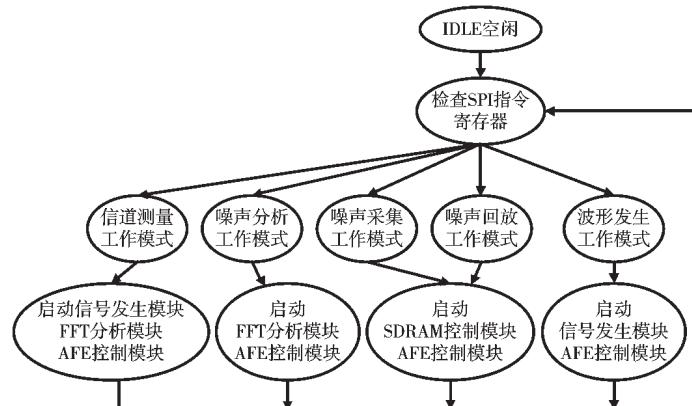

主控模块主要功能为协调各个逻辑模块正常工作,根据不同的工作状态控制数据的接收及发送模块。主控模块的逻辑状态机如图 4 所示。

### 2.3 SDRAM 控制模块

SDRAM 控制模块使用状态机实现 SDRAM 芯片的读写逻辑接口<sup>[9]</sup>,其状态机包括初始化、数据读写、数据刷

图 4 主控模块逻辑状态机

新等操作<sup>[10-11]</sup>。模块启动稳定后开始对 SDRAM 芯片进行初始化操作,配置工作模式。读写时,首先进行激活,读写数据操作后自动进行预充电,并对行地址进行复位的操作。

由于在电力线噪声采集及噪声回放过程中数据流是连续的,但 SDRAM 芯片需要定期执行数据刷新,不能持续读写,故需要使用 FIFO 对数据进行缓冲<sup>[12-13]</sup>。

AFE 控制模块采集的数据首先写入 FIFO 中,读写逻辑电路从 FIFO 中读取数据写入 SDRAM。写完一页数据后执行数据刷新动作,然后等待再次触发 SDRAM 写入动作。如此往复,完成对采样数据的连续写入。在噪声回放模式时,数据流向相反,实现采样数据流的连续输出及噪声重建。

## 2.4 信号发生模块

信号发生模块可以发生周期性的噪声信号,基于 XILINX 公司的 DDS IP 核以及数字逻辑实现<sup>[14]</sup>。信号发生模块能够发送白噪声、脉冲噪声、窄带噪声、扫频噪声信号,可用于电力线载波设备的定量抗噪声测试。

## 2.5 FFT 分析模块设计

FFT 分析模块基于 XILINX 公司的 FFT IP 核实现,可对采样数据流进行快速傅里叶变换<sup>[15]</sup>,获取信号的频谱特性。

输入离散信号数据流通过 FFT 模块计算,可得出傅里叶变换实部及虚部,并储存在 FPGA 内部寄存器组,供 MCU 进行读取,获取实时的频谱分析数据。

## 3 MCU 控制程序设计

MCU 的主要功能为控制 FPGA 工作模式、接收上位机指令、执行文件管理相关功能。

### 3.1 主程序流程

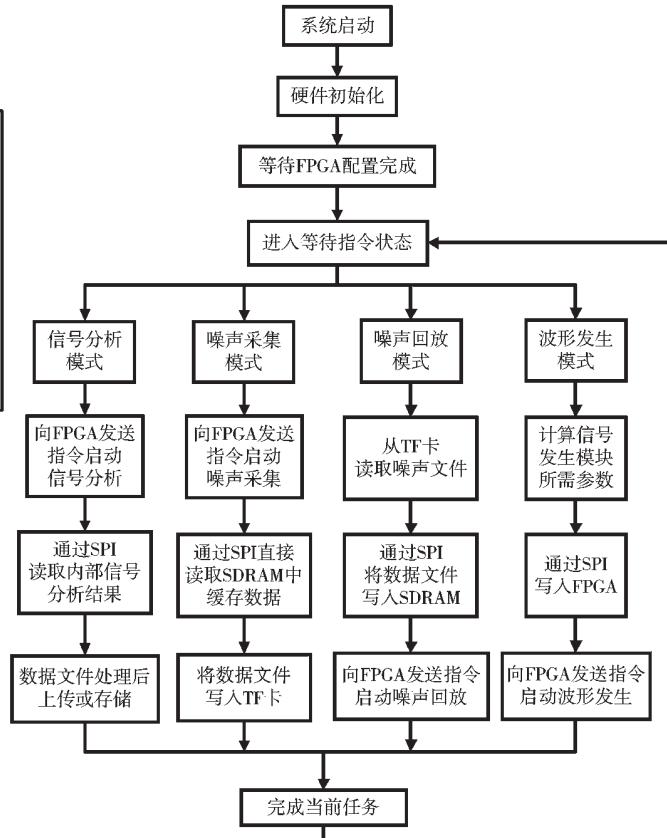

MCU 与 FPGA 协同工作可以发挥各自优势<sup>[16]</sup>,MCU 嵌入式软件主要程序执行流程如图 5 所示,系统启动后执行硬件初始化,等待 FPGA 完成配置,由上位机发送指令进入不同的工作模式分支。

### 3.2 噪声采集模式工作流程

MCU 向 FPGA 写入指令码启动噪声采集,支持单次

图 5 MCU 主程序流程

采集、多次采集、随机延时盲采等多种定制采集方案。

### 3.3 噪声回放模式工作流程

MCU 读取 TF 卡中的数据文件,将数据写入 SDRAM 中,然后向 FPGA 写入指令码启动信号回放。FPGA 模块循环回放 SDRAM 中缓存的数据文件,输出录制的噪声信号。

### 3.4 信号发生模式工作流程

MCU 将扫频频率、步进时间、步进频率等控制参数写入 FPGA 内部的信号发生模块,为电力线信道测试提供激励源<sup>[17]</sup>。

### 3.5 噪声分析功能工作流程

噪声分析功能用于实时分析现场噪声干扰频域特性,FPGA 循环采样噪声数据并进行 FFT 计算,从而分析当前信道噪声的频域特性。

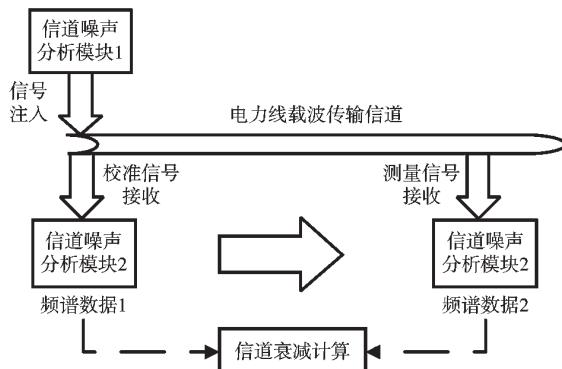

### 3.6 信道测量功能工作流程

信道测量功能依托于信号发生功能与信号分析功能实现,测量时,需要使用两个信道分析模块协同工作,其中模块 1 工作于信号发生模式作为激励源,模块 2 工作于信号分析模式测量信道。

信道测量方法如图 6 所示。模块 1 在载波信道发送端接入电力线,循环发送覆盖电力线通信频段的扫频噪声信号;模块 2 在信道发送端使用最大保持模式接收信号、测量信号频谱特征并记录为发送端频谱数据 1。然

图 6 信道测量功能示意图

后模块 2 在信道接收端使用最大保持模式测量信号频谱特征并记录为接收端频谱数据 2。将频谱数据 1 与频谱数据 2 在上位机进行矫正计算, 即可得出该通信频段载波信道的衰减特性。

#### 4 实现及测试结果分析

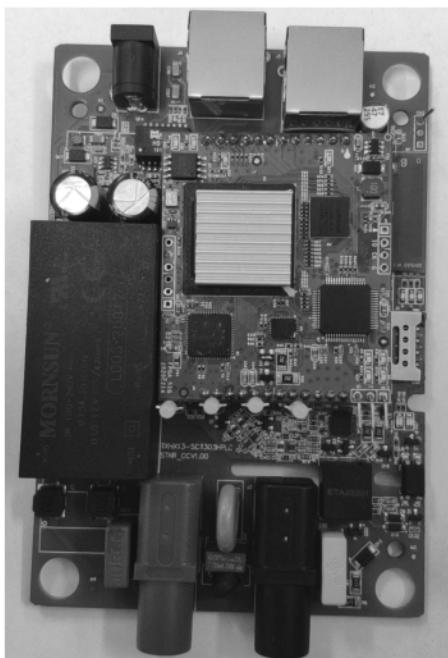

按照前述章节设计实现的信道分析模块样机实物如图 7 所示, 模块整体外形尺寸为  $12\text{ cm} \times 8.2\text{ cm}$ , 可使用电力线或外接直流电源供电。

图 7 信道分析模块样机

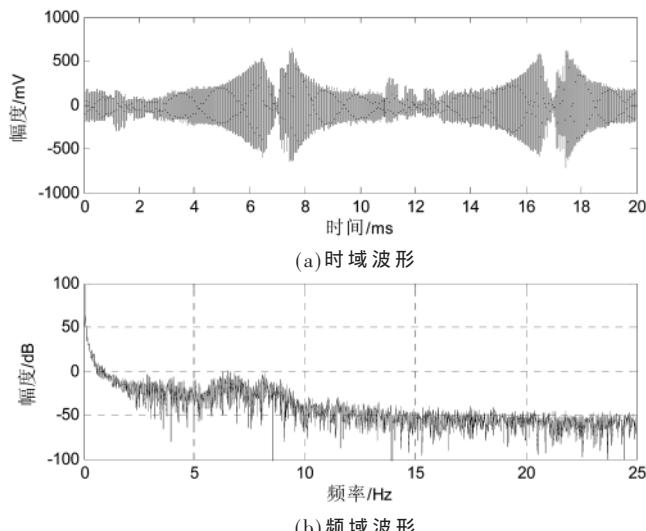

##### 4.1 噪声信号采集功能测试

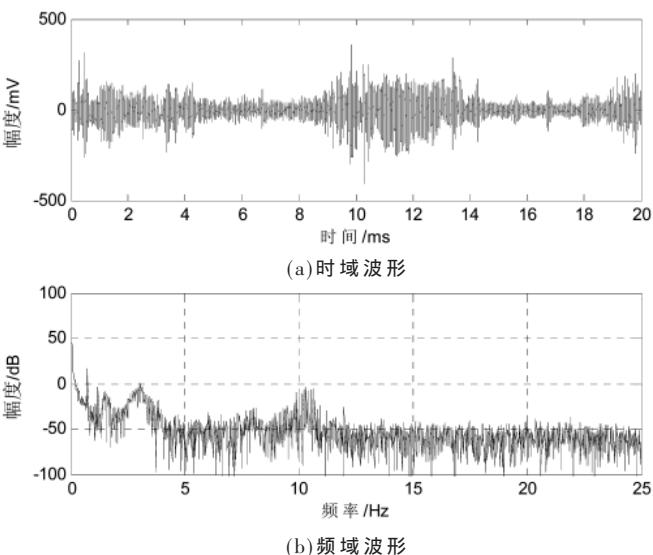

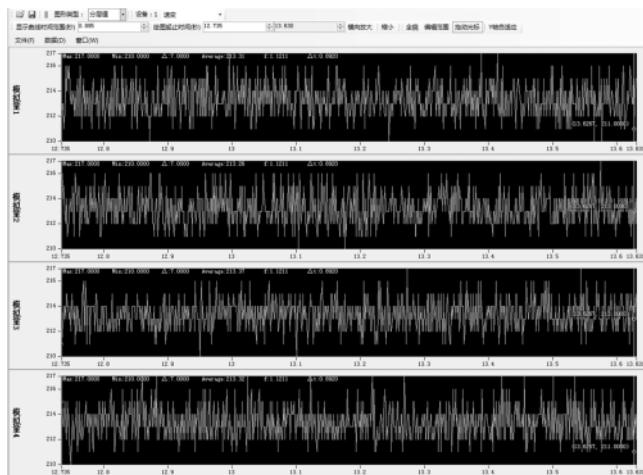

将信道分析模块接入实验室环境, 电力线采集到的噪声数据经软件可视化处理后的时域图形及频域图形如图 8 所示, 采样长度为 20 ms。

将噪声分析模块接入某现场台区配电室, 采集到的噪声数据经软件可视化处理后的时域图形及频域图形如图 9 所示, 采样长度为 20 ms。此环境为居民用电小区, 用电负载较为复杂, 包括一些大功率居民用

图 8 实验室环境电力线噪声时域及频域波形

图 9 现场环境电力线噪声时域及频域波形

电设备。

##### 4.2 噪声信号回放功能测试

使用信号回放功能回放采集的数据文件, 将信道测量模块输出接至示波器, 输出录制的噪声波形信号, 可观察到输出的噪声信号与采集信号的波形一致。

将不同环境下噪声注入电力线载波通信测试平台, 使用不同厂家标准 HPLC 载波模块在此环境下进行载波回传测试, 测试模块的抗噪声能力, 测试条件为  $TMI=4$ ,  $PB=1$ , 测试结果如表 1 所示。

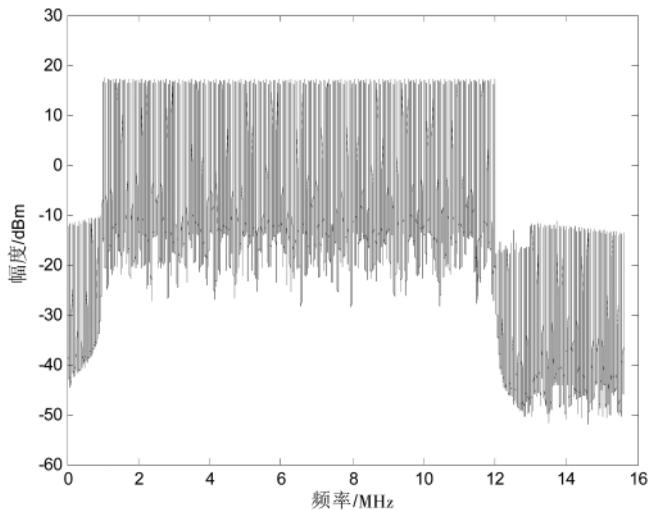

##### 4.3 噪声信号发生功能测试

对扫频噪声波形发生功能进行测试, 扫频参数为起始频率 1 MHz, 结束频率 12 MHz, 此参数配置下 Pico 示波器采集到的频谱尖峰保持数据经过可视化处理后的频域图形如图 10 所示。可观察到波形扫频起始频率、截止频率与设定相同, 表明波形发生功能正常。

表 1 不同厂家模块在典型噪声环境下抗衰减能力

| 高速载波模块 | 无干扰下     | 实验室环境       | 现场环境        |

|--------|----------|-------------|-------------|

|        | 抗衰减能力/dB | 噪声下抗衰减能力/dB | 噪声下抗衰减能力/dB |

| 厂家 1   | 频段 1     | 94          | 53          |

|        | 频段 2     | 95          | 47          |

| 厂家 2   | 频段 1     | 91          | 无法通信        |

|        | 频段 2     | 92          | 49          |

| 厂家 3   | 频段 1     | 84          | 53          |

|        | 频段 2     | 83          | 46          |

| 厂家 4   | 频段 1     | 93          | 49          |

|        | 频段 2     | 91          | 22          |

图 10 信道分析模块扫频模式输出

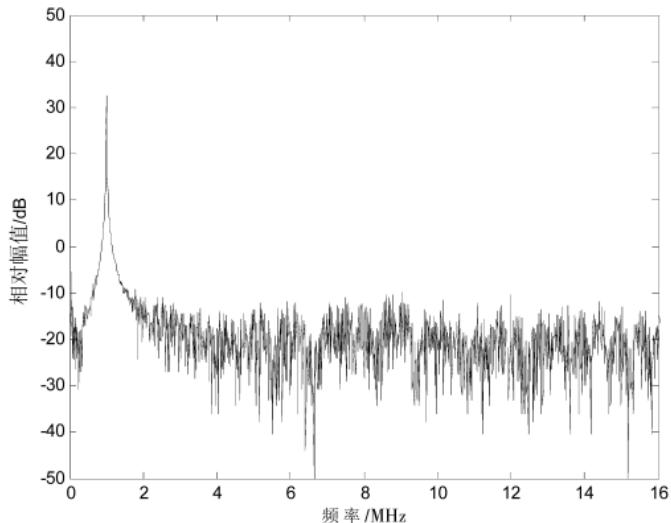

#### 4.4 噪声分析功能测试

使用信号源向信道分析模块注入 1 MHz 频率的单频噪声信号, 使用信号分析模式输出采集的频谱数据, 经过可视化处理后可观察到接收信号的频谱信息, 如图 11 所示, 可观察到 1 MHz 的单频噪声信号频谱, 表明模块噪声信号分析功能工作正常。

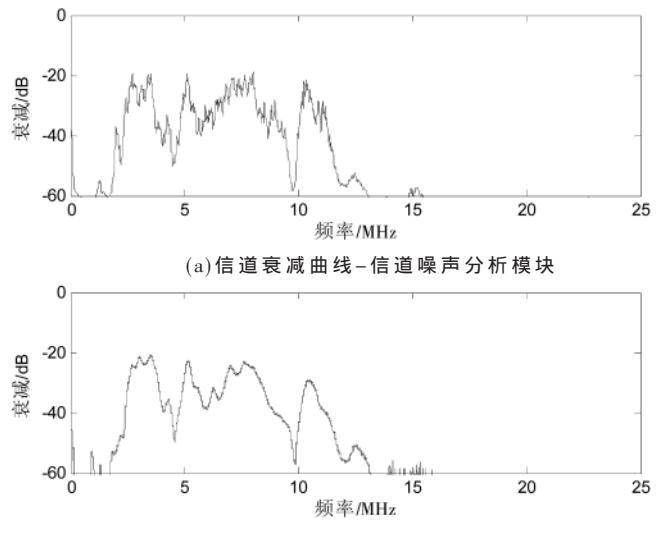

#### 4.5 信道测量功能测试

将一个模块配置为扫频信号发生模式, 将信号注入电力线, 使用另一个信道分析模块在另一位置采集此信号并输出频谱最大保持数据, 经过软件可视化处理后可生成信道衰减曲线, 如图 12(a)所示。图 12(b)为 Pico 示波器在同一接收位置采集的频谱最大保持数据经过标定后输出的信道衰减曲线。从图中可观察到, 电力线信道上衰减导致接收端信号频谱不完全平坦, 存在某些衰减较大的频点。通过对载波信道的衰减特性分析, 有助于选择合理的载波通信频率, 并为中继器的安装位置选取提供理论依据。

#### 5 结论

通过上述测试, 表明本文设计的高速电力线载波信道分析模块各功能工作正常, 噪声采集及回放功能达到了预期指标, 可应用于现场噪声样本的采集及分析, 并

图 11 信号分析功能输出信号频谱

图 12 电力线信道接收端信道衰减曲线

且能够在实验室电力线测试信道注入现场环境噪声, 模拟现场工作环境, 解决了高速电力线载波通信中噪声研究和现场运维测试的难题, 对高速电力线载波技术的应用推广具有重要意义。

#### 参考文献

- [1] 中国电子技术标准化研究院.宽带电力线通信标准化白皮书[R].2014.

- [2] 胡江溢, 祝恩国, 杜新纲, 等.用电信号采集系统应用现状及发展趋势[J].电力系统自动化, 2014, 38(2): 131–135.

- [3] 仲元昌, 杨洁, 曾孝平.低压电力线的信道特性[J].重庆大学学报(自然科学版), 2002(9): 29–31.

- [4] 赖征田.电力线载波信道特性研究及仿真[J].电力系统通信, 2010, 31(216): 39–42.

- [5] 孙秀娟, 罗运虎, 刘志海, 等.低压电力线载波通信的信道特性分析与抗干扰措施[J].电力自动化设备, 2007(2):

(下转第 109 页)

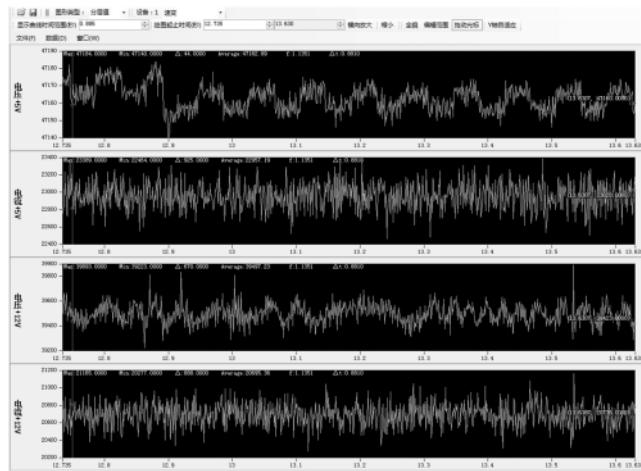

图 11 传感器通道数据绘图

图 12 电压电流通道数据绘图

0.067 14%。经过大量的实验数据分析，采集精度均能满足要求。

4 结论

为了实现对信号的高精度采集,本文通过对多通道SAR型模数转换硬件电路的分析,设计了一种高精度、多通道的数字变换器,经过大量实验验证其具备很高的可靠性,能够满足任务要求。

参考文献

- [1] 师明,王保丰,曹玉娟,等.面向航天器飞控任务的数据处理系统的设计与验证[J].航天器工程,2018,27(6):69-76.

- [2] 储成君.基于FPGA的多通道模数混合采集装置的设计及实现[D].太原:中北大学,2014.

接第 10

- 43–46.

- [6] 房曙光.低压电力线通信信道特性[J].继电器, 2007, 35(22): 53–56.

- [7] 杨挺, 刘佳林, 张亚健, 等.电力线载波通信时频混合降噪方法[J].电网技术, 2018, 42(10): 3153–3160.

- [8] 王永利.基于 FPGA 的带寄存器寻址 SPI 接口设计[J].物联网技术, 2013(3): 45–47.

- [9] 陆鹏.一种从机 SPI 通信接口的 FPGA 设计与实现[J].信息通信, 2020(3): 142–143.

- [10] 侯宏录, 张文芳.基于 FPGA 的 SDRAM 控制器设计方案[J].兵工自动化, 2012, 31(2): 57–60.

- [11] 杨腾.基于 FPGA 的应用于 STM32 的 SDRAM 控制器设计方案[J].智库时代, 2019(7): 254–257.

- [12] 贺婷.基于乒乓数据存储机制的 FPGA 视频监控系统设计[J].电脑知识与技术, 2015, 11(31): 189–190.

- [13] 吴明阳.基于 FPGA 的高速数据采集系统的设计分析[J].数码世界, 2019(1): 6–7.

- [14] 周欢, 陈剑云, 钟汉华.基于 Xilinx IP 核的任意信号发生

- [3] 李海兰,李刚.精密低噪声 CMOS 轨-轨运算放大器 AD8605/AD8606/AD8608[J].电子元器件应用,2006(1): 106-107, 116.

- [4] 高旭彬.通用型运放输出摆动范围的实验与分析[J].电子技术,2013,42(8):61-62,54.

- [5] 瞿林.基于 CAN 总线的分布式温度采集系统的设计与实现[D].太原:中北大学,2015.

- [6] 马青.高速数据采集信号调理电路的研究[D].哈尔滨:哈尔滨理工大学,2009.

- [7] 史帅.宽带高精度功率分析仪通道设计与实现[D].成都:电子科技大学,2019.

- [8] 董耀文.电动汽车用霍尔电流传感器的设计[D].南京:南

(下转第 114 页)

器的设计[J].华东交通大学学报,2018,35(4):112-116.

- [15] 沈龙龙, 李军旗, 于水游. 基于 FPGA 的 1024 点 FFT 在信号实时解码处理中的实现[J]. 光电技术应用, 2020, 35(3): 67–72, 77.

[16] 张月, 陶林伟. 基于 FPGA 与 STM32 的多通道数据采集系统[J]. 西北工业大学学报, 2020, 38(2): 351–358.

[17] 杨爱冰, 董天强, 陈波, 等. 低压电力线信道传输特性测量与研究[J]. 实验室研究与探索, 2017, 36(1): 136–139, 143.

(收稿日期:2020-11-16)

---

## 作者简介：

郝伟琦(1989-),通信作者,男,硕士,高级工程师,主要研究方向:电力通信与计算机网络技术,E-mail:haoweiqi@sgitg.sgcc.com.cn。

王贤辉(1983-),男,硕士,高级工程师,主要研究方向:电力通信与计算机网络技术。

李铮(1979-),男,学士,工程师,主要研究方向:电力通信与计算机网络技术。

扫码下载电子文档

## 版权声明

经作者授权，本论文版权和信息网络传播权归属于《电子技术应用》杂志，凡未经本刊书面同意任何机构、组织和个人不得擅自复印、汇编、翻译和进行信息网络传播。未经本刊书面同意，禁止一切互联网论文资源平台非法上传、收录本论文。

截至目前，本论文已经授权被中国期刊全文数据库（CNKI）、万方数据知识服务平台、中文科技期刊数据库（维普网）、DOAJ、美国《乌利希期刊指南》、JST 日本科技技术振兴机构数据库等数据库全文收录。

对于违反上述禁止行为并违法使用本论文的机构、组织和个人，本刊将采取一切必要法律行动来维护正当权益。

特此声明！

《电子技术应用》编辑部

中国电子信息产业集团有限公司第六研究所