# 亚皮秒级激光回波半实物仿真系统关键技术研究

朱敏<sup>1</sup>, 吴楠<sup>1</sup>, 杨春玲<sup>1</sup>, 陈海燕<sup>2</sup>, 李睿<sup>2</sup>

(1. 哈尔滨工业大学 电气工程及自动化学院, 黑龙江 哈尔滨 150001; 2. 中国空空导弹研究院, 河南 洛阳 471009)

**摘要:** 激光回波仿真系统能够根据所模拟的目标生成高频高精度模拟回波信号。提出一种激光回波仿真系统设计方案, 系统中采用 FPGA 生成延时信号, 可以对回波信号实现亚皮秒级的延时精度; 对光纤通信协议进行了优化, 用 FPGA 实现基于该协议的回波信号传输系统, 摆脱了现有方案中对反射内存卡的依赖性, 提升了数据的刷新频率。仿真结果表明, 所设计的仿真系统数据传输速度达到 1.6 Gb/s, 回波精度达到 125 ps, 距离分辨率达到 0.05 m。为基于激光阵列的高精度激光制导半实物仿真系统的研制奠定了基础。

**关键词:** 回波仿真; 激光成像制导; FPGA; 光纤传输; 高精度延时; 锁相环

中图分类号: TN95

文献标识码: A

DOI: 10.16157/j.issn.0258-7998.201212

中文引用格式: 朱敏, 吴楠, 杨春玲, 等. 亚皮秒级激光回波半实物仿真系统关键技术研究[J]. 电子技术应用, 2021, 47(6): 119–125, 130.

英文引用格式: Zhu Min, Wu Nan, Yang Chunling, et al. Research on key technologies of sub-picosecond laser echo semi-physical simulation system[J]. Application of Electronic Technique, 2021, 47(6): 119–125, 130.

## Research on key technologies of sub-picosecond laser echo semi-physical simulation system

Zhu Min<sup>1</sup>, Wu Nan<sup>1</sup>, Yang Chunling<sup>1</sup>, Chen Haiyan<sup>2</sup>, Li Rui<sup>2</sup>

(1. School of Electrical Engineering and Automation, Harbin Institute of Technology, Harbin 150001, China;

2. China Air-borne Missile Academy, Luoyang 471009, China)

**Abstract:** The laser echo simulation system can generate high-frequency and high-precision analog echo signals according to the simulated target. This paper presents a design scheme of a laser echo simulation system. The system uses FPGA to generate a delay signal, which can achieve a sub-picosecond delay accuracy for the echo signal. This paper optimizes the optical fiber communication protocol and uses FPGA to implement the echo signal transmission system, which has got rid of the dependence on the reflective memory card in the existing scheme, and has increased the data refresh frequency. The simulation results show that the data transmission speed of the simulation system designed in this paper reaches 1.6 Gb/s, the echo accuracy reaches 125 ps, and the distance resolution reaches 0.05 m. It laid the foundation for the development of high-precision laser guidance semi-physical simulation system based on laser array.

**Key words:** echo simulation; laser imaging guidance; FPGA; optical fiber communication; high accuracy delay; PLL

## 0 引言

近年来, 激光雷达由于在分辨率、抗干扰能力、隐蔽性及远距离探测能力等方面的优良性能, 逐渐在各国军事界引起关注<sup>[1]</sup>, 应用范围也得到了很大的扩展<sup>[2-5]</sup>。

在激光雷达成像制导的过程中, 半实物仿真技术是快速获取高精度目标表面数据的重要途径。半实物仿真是指将真实物体通过激光雷达生成的真实图像与诱饵弹等模拟物体通过仿真系统生成的模拟图像经过分光镜形成一个完整的激光图像, 为后续的制导过程提供基础。半实物仿真方式可以降低人力物力的消耗, 提高效率, 加快成像制导系统的开发进程, 做到快速完整地测试其性能。而生成模拟图像的部分即为本文重点研究

的激光回波仿真系统。

美国 AMCOM 和 AMRDEC 是最早对激光回波仿真系统开发与设计相关技术进行研究的机构<sup>[6-8]</sup>。2002 年, CORNELL M C 等人在 AMCOM 的帮助下, 搭建了用于测试直接探测型雷达的回波模拟系统<sup>[9]</sup>。该系统可以模拟复杂目标及背景, 且阵列中的每一路回波都具有较为真实的光学模型及参数, 并以亚纳秒的精度传输。2004 年, AMRDEC 完善了以上系统结构, 开发出了激光回波仿真系统的模拟硬件装置<sup>[10]</sup>, 实现了对由回波构成的三维图像成像精度达到 0.075 m 的模拟, 其最大测试距离远超 5 000 m。北京理工大学的徐锐等人在 2016 年参照国外相关系统, 搭建了一套激光回波仿真系统<sup>[11-12]</sup>, 该

系统成像分辨率达到 1.04 m, 即时间精度为 6.94 ns, 成像帧频为 300 Hz, 成像阵列规模小, 传输速率及精度低。本文针对现有方案存在的不足, 设计了一种能提高系统传输速率和精度的方法。

## 1 回波仿真系统原理及总体设计方案

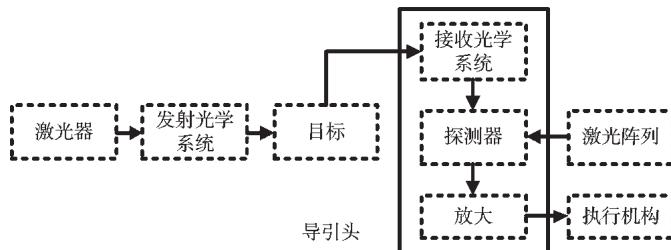

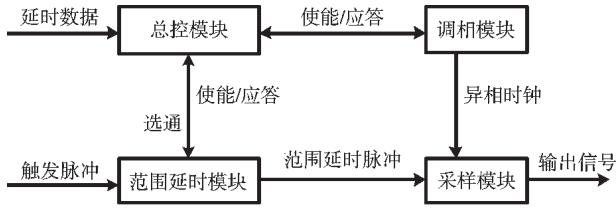

相对于传统的激光制导系统, 激光回波仿真系统省去了激光发射部分, 其结构如图 1 所示。

图 1 激光回波仿真系统原理框图

通过在上位机对目标三维物体的建模分析, 获得包含物体表面形状信息的目标数据, 由表面相对距离与光速相除得到不同的延时, 生成驱动信号进而直接驱动激光阵列, 产生模拟实际激光雷达的回波组脉冲<sup>[13]</sup>, 脉冲信号耦到激光二极管的面阵上, 点亮的激光阵列相当于一个包含距离信息的三维动态图像。图像经导引头内的探测器接收后进行放大, 由执行机构进行后续制导操作。

采集物体表面形状信息建立数据库还可以解决一些物体实测难度大的问题, 有较高的实用价值。

生成模拟回波组的帧频和精度是衡量回波仿真系统性能的关键。模拟回波组要在单位时间内模拟较多不同的目标情况以满足仿真系统实时性要求。同时, 由于目标形状与回波返回探测器的时间差成正比, 为了清晰获取模拟目标的形状, 就需要提高时间差的精度。

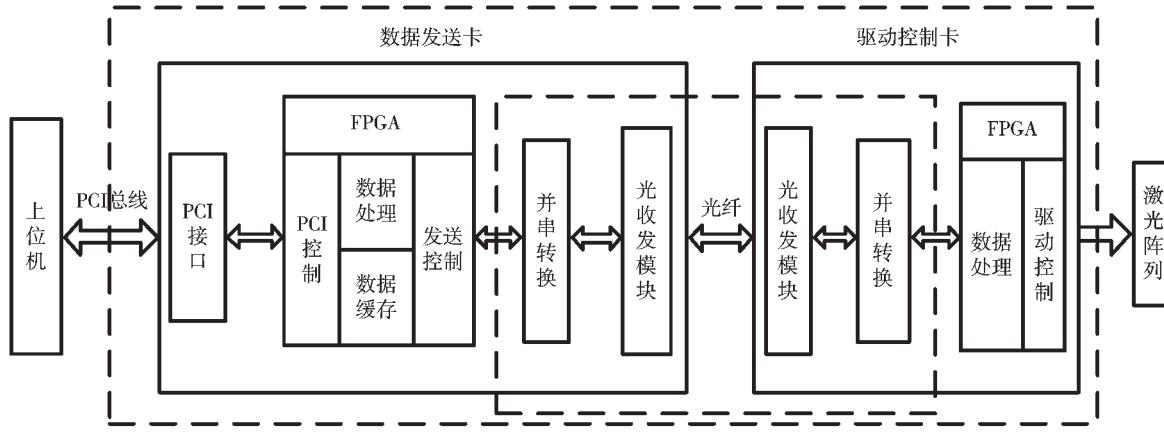

本文采用自主设计的传输板卡与光纤通信协议栈配合 PCI 总线实现生成回波的高频, 采用锁相环构建时钟相位延迟线实现生成回波的高精度<sup>[14-15]</sup>。系统总体方案设计架构如图 2 所示。

系统以 FPGA 为核心, 主要包含上位机、数据接收卡、驱动控制卡以及激光阵列四部分。其工作流程如下:

(1) 上位机针对所需要模拟的实际物体或典型图形进行三维建模, 生成目标物体表面相关数据, 包括二维通断信息及三维延时信息。

(2) 数据通过总线传递至数据接收卡, 在此完成对这些数据的编码、分组、存储等操作, 然后按照一定顺序, 将处理后的数据通过光纤传递给驱动控制卡。

(3) 驱动控制卡上的 FPGA 依照数据生成相应的驱动信号, 通过 I/O 接口输出至激光阵列。可以扩展数据发送卡的光纤接口数量, 使用多块驱动控制卡来扩大阵列驱动规模。

(4) 激光阵列由驱动信号驱动控制, 生成反映三维信息的图像。其中驱动控制方式根据阵列规模, 可以采用扫描式、拍照式或部分扫描式, 本文不做重点描述。

## 2 回波仿真系统数据传输协议优化

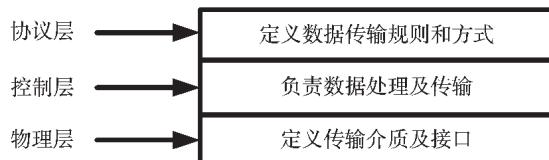

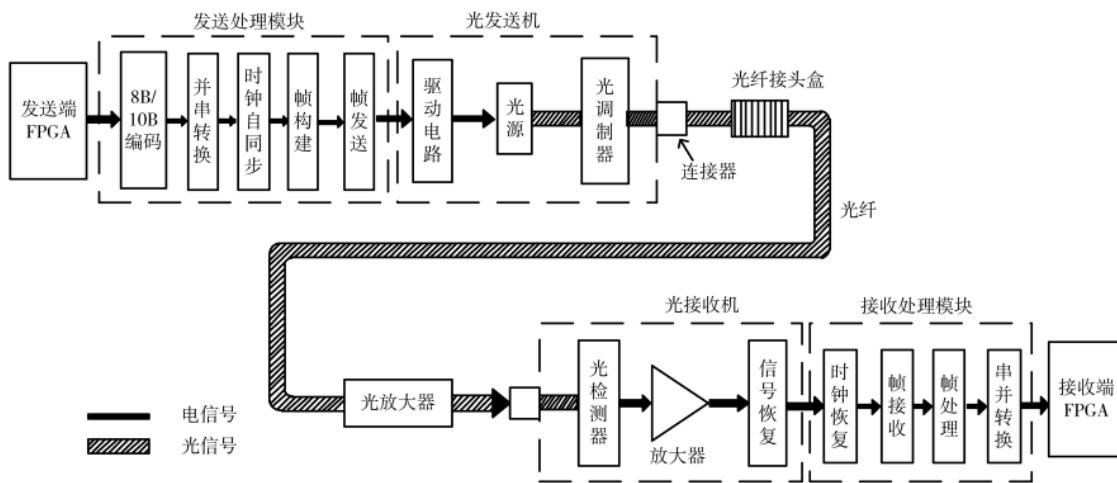

本文方法在现有的 OSI 模型和 FCP 协议栈结构基础上进行了优化, 去掉了与其他网络协议及应用的接口, 舍去了与数字通信需求不相符合, 且较为繁琐的公共服务与映射协议两层, 降低了传输延时, 更适用于大量数据高速传输情况。简化后的光纤通信协议架构图如图 3 所示, 本文采用的光纤传输系统结构如图 4 所示。

图 3 光纤通信协议栈结构

首先定义物理层相关内容。定义传输的物理媒介及物理接口等。方法采用单模光纤配合单模 SC 插头的方式。数据从发送端 FPGA 发出后, 进入发送处理模块。控制层定义了在进行光纤通道线缆传输之前对数据的编码方式。方法采用 8B/10B 编码, 保证数据流能够产生足够多的跳变, 从而保证接收方时钟的同步, 时钟恢复较

图 2 系统总体方案设计框图

图 4 光纤系统结构框图

容易,同时传输效率高,误码纠错能力强。之后将数据由低速并行数据转换为高速串行数据。为了进一步解决时钟信号与数据信号的同步问题,采用自同步模型进行时钟处理。将时钟信息嵌入到待发送的数据中,在接收端对接收数据流进行时钟解算以恢复时钟信息。避免了信号间的延迟、偏斜问题,同时有利于实现高速串行数据传输。将数据由低速并行数据转换为高速串行数据。为了进一步解决时钟信号与数据信号的同步问题,采用自同步模型进行时钟处理。将时钟信息嵌入到待发送的数据中,在接收端对接收数据流进行时钟解算以恢复时钟信息。这样避免了信号间的延迟、偏斜问题,同时有利于实现高速串行数据传输。

协议层定义了数据传输机制,执行基本的信令和帧相关功能,在发送部分需要进行帧构建及帧发送。采用包含 CRC 校验位的通用 FC-2 帧格式进行数据传输。同时进行流控制保证发送方发送数据速度可以被接收方接受。采用基于 credit 的流量控制法,避免由于接收缓冲区溢出导致的帧丢失现象。接收端不发生数据溢出的最大缓存容量可表示为:

$$BO_{\max}(t) = RTT \times Rpk \quad (1)$$

RTT 为发送接收端间的链路往返时延, Rpk 为链路带宽峰值。取信号时延  $5 \mu s/km$ , L 表示链路长度, FS 表示 FC 帧大小并考虑到 8B/10B 编码方式的影响, 接收方为发送方分配的最大缓冲区数量为:

$$C_{\max} = \frac{2 \times 5 \times 10^{-6} \times L \times Rpk}{1.25FS} \quad (2)$$

之后经过光发送机进行电光转换,采用光耦合技术将光信号尽可能注入光纤通道传输至光接收机,进行光电转换后恢复出原始电信号向后传输。光发送机和光接收机作为一对光调制解调器,将带有信息的信号在电信号和光信号间相互转换。在接收部分对经过光纤传输产生一定衰减和畸变的微弱光信号进行放大和整形,从而保证了数据传输的质量。

在接收处理模块先通过时钟数据恢复技术为接收数据提供稳定的同步于串行数据流的高速时钟信号,与发送端自同步功能相对应,可以抑制时钟抖动。然后进行数据接收及 CRC 校验等处理,最后经过串并转换后传递至接收端 FPGA 进行后续操作。

其中串并转换芯片选择 TLK2501, 光电转换模块采用 AFBR5921 光纤收发器。串并转换模块串行传输速率在 1.5 Gb/s 到 2.5 Gb/s 之间, 光电转换模块传输速率在 1.0625 Gb/s 到 2.125 Gb/s 之间, 可以配合使用。由于 TLK2501 与 AFBR5921 的接口电路电平形式不同, 采用交流耦合的方式进行连接。设计硬件电路完成对目标数据的高速传输。

### 3 基于 FPGA 的回波仿真系统延时电路的设计与实现

激光回波仿真系统的实时性要求其生成的回波有较高的更新频率,也就是要保证数据在上位机和驱动控制卡间有较高的传输速度。国内外回波仿真系统中常采用反射内存卡作为光纤传输的接口,但反射内存卡与没有 PCI 接口的激光阵列无法直接相连,需要加入中间环节,增加了传输延时,实时性不高,传输协议不透明,可扩展性差。本方案自行设计了数据接收卡与驱动控制卡分别代替发射及接收端的反射内存卡,摆脱了系统对反射内存卡的依赖,提高了系统的传输速率和可移植性。

#### 3.1 模块 IP 总体架构设计

仿真系统中的信号生成模块是本次的设计重点。将各路距离差值通过延时附加在该路激光二极管驱动脉冲上,即可使点亮的激光阵列包含目标的三维信息。采用时间内插法构建延迟线,常见的方法如表 1 所示。

采用时钟相位延迟线方法,通过调用 FPGA 内部锁相环动态配置端口,产生对应于每一路数据的同频异相时钟,实现延时的高精度。同时,采用计数器方法实现延时的大动态可调节范围,最终设计的高精度大范围回波

表 1 延迟线构建方法优缺点

| 指标方法 | 时钟相位延迟线            | IODELAY 延迟线              | 模拟电路延迟线                       | 专用进位链延迟线               |

|------|--------------------|--------------------------|-------------------------------|------------------------|

| 理论精度 | 100 ps             | 100 ps                   | 10 ps                         | 100 ps                 |

| 集成度  | 高                  | 较高                       | 低                             | 高                      |

| 方法优点 | 精度较高,集成度高;<br>设计简单 | 精度较高;利用现成延迟线,<br>设计复杂度较低 | 精度很高                          | 精度较高,集成度高              |

| 方法缺点 | 相位差控制难度高           | 依赖于指定芯片的模块单元,<br>不具备通用性  | 延时范围小;集成度低;<br>PCB 电路复杂且稳定性较低 | 难以保证每一路延时相同,<br>设计复杂度高 |

生成 IP 核如图 5 所示。

图 5 高精度大范围回波生成 IP 核结构框图

### 3.2 锁相环精度延时模块设计

锁相环用于实现目标信号的高精度延时,通过对系统时钟的移相及采样,生成延时值等于同频异相时钟与系统时钟相位差的目标延时信号。

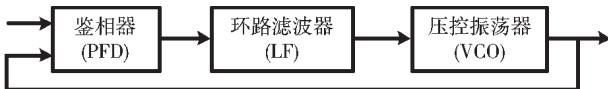

锁相环是一个通过负反馈跟踪频率值并锁定相位差值,最终生成同频异相时钟的闭环控制系统,由鉴相器、环路滤波器和压控振荡器三部分组成。其相位数学模型如图 6 所示。

图 6 锁相环相位模型

设输入信号为  $u_i(t)=U_{im}\sin(\omega_it+\varphi_i(t))$ , 输出信号  $u_o(t)=U_{om}\cos(\omega_ot+\varphi_o(t))$ 。由于负反馈回路对相位差的锁定作用,锁定后瞬时相位差为:

$$\varphi_e(t)=\omega_it-\omega_ot+\varphi_i(t)-\varphi_o(t) \quad (3)$$

鉴相器(PD)用于从参考信号和反馈信号中产生相位误差信号,其组成为乘法器和低通滤波器两部分,其中乘法器实现参考输入信号与反馈输出信号相乘的功能,乘法器输出的电压信号为:

$$u_d(t)=Ku_i(t)u_o(t)=\frac{1}{2}KU_{im}U_{om}\sin(2\omega_ot+\varphi_i(t)+\varphi_o(t)) + \frac{1}{2}KU_{im}U_{om}\sin(\varphi_i(t)-\varphi_o(t)) \quad (4)$$

鉴相器的低通滤波器部分用于消除高频的和频分量,只保留差频分量通过,此时输出的电压信号为:

$$u_d(t)=U_d\sin\varphi_e(t) \quad (5)$$

环路滤波器(LF)主要用于建立环路的动态特性,调节锁相环的外在表现,同时滤除鉴相器输出电压中的高频噪声。在时域角度对滤波过程进行分析,以时域传

递函数  $F(p)$  将输入变量与输出变量的相位相关联,此时有:

$$u_c(t)=F(p)u_d(t) \quad (6)$$

压控振荡器(VCO)对于输出相位与输入控制电压相当于理想积分器,其振荡频率为:

$$\omega_v(t)=\omega_0+K_0u_c(t) \quad (7)$$

压控振荡器输出信号通过信号负反馈回路反馈到鉴相器,鉴相器影响  $u_c(t)$  的相位而不影响频率。对式(7)两端取积分,有:

$$\varphi_o(t)=K_0 \int_0^t u_c(\tau) d\tau \quad (8)$$

采用微分算子表示输出相位,则有:

$$\varphi_o(t)=\frac{u_o(t)K_0}{p} \quad (9)$$

由相位数学模型分析锁相环路频率及相位关系,得到动态方程:

$$p\varphi_e(t)=p\varphi_o(t)-KF(p)\sin\varphi_e(t) \quad (10)$$

其中环路增益  $K=K_0U_d$ ,由式(10)得出环路瞬时频差等于固有频差与控制频差的差值。当环路状态达到锁定时,固有频差即为控制频差,可表示为:

$$\Delta\omega_o=KF(j\Omega)\sin\varphi_e(\infty) \quad (11)$$

由此推出稳态相差表达式:

$$\varphi_e(\infty)=\arcsin \frac{\Delta\omega_o}{KF(j0)} \quad (12)$$

移相过程是改变稳态相差的过程,由表达式可知,此过程可以通过联合控制固有频差  $\Delta\omega_o$  和环路增益  $K$  来实现。

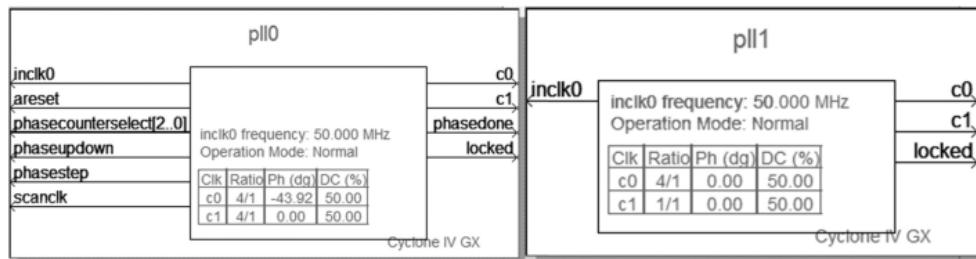

本系统设计过程中 FPGA 主控芯片采用 Altera 公司生产的 Cyclone IV 系列 EP4CE6F17C8 芯片,芯片内置锁相环的调相过程利用生产商提供的动态配置端口实现。通过配置端口参数对输出时钟相位按要求进行实时更新。系统调相过程中需要配置两个锁相环,其中 pll1 输入时钟为开发板配置的 50 MHz 外部晶振时钟,经过锁相环的四倍频输出一个 200 MHz 时钟,作为同步时钟应用于延时生成系统;同时输出一个 50 MHz 时钟用于 pll0 的重配置。pll0 通过配置输入端口参数完成对输入时钟的移相过程。两个锁相环端口的动态配置图如图 7 所示。

相位动态调整精度为压控振荡器周期的 1/8,如式(13)所示。

图 7 锁相环动态配置端口图

$$\phi_{\min} = \frac{T_{\text{vco}}}{8} = \frac{1}{8F_{\text{vco}}} \quad (13)$$

查找数据手册得到本系统所用 FPGA 的压控振荡器频率范围为 600~1 300 MHz, 对应相位调整精度范围为 96~208 ps。在综合考虑了系统的稳定性和精度之后, 将相位调整的最小步长设置为 125 ps。

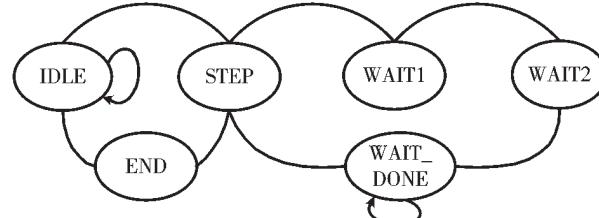

之后根据锁相环动态调整的步骤，编写状态机，控制生成的锁相环，并得到目标的同频异相时钟。该状态机的状态转移图如图 8 所示。

在 Modelsim 中对该模块进行仿真，将移相次数设置为 15，移相得到的同频异相时钟与参考时钟间的相位差为 1.875 ns，该值是移相次数与最小步长的乘积，该模块功能实现。

#### 4 测试结果及分析

为验证设计的正确性,搭建测试平台,对各模块进

图 8 锁相环重配置状态转移图

行验证。

首先运用 Labwindows 完成上位机部分对图像的处理、显示及数据的转化。离散化图像每一点的像素深度信息与  $64 \times 64$  规模激光阵列的驱动数据一一对应。上位机界面及输出后的数据结果如图 9、图 10 所示。

搭建板卡硬件电路对数据传输模块进行实测。对光纤进行环路测试、板卡间数据传输以及误码率测试。搭建

图 9 图像生成及显示界面

图 10 像素深度信息输出结果

建系统实物测试电路如图 11 所示。

图 11 光纤传输系统实物测试图

通过上位机软件向 FPGA 发送连续数的方式，检验数据的一致性及传输速度，测试结果如图 12 所示。

图 12 光纤传输系统测试结果

由图可见数据在收发端保持一致，且经过长时间测试，没有出现误码情况，传输准确性较高，模块功能可以正常实现。且由于系统的时钟为 100 MHz，数据为 16 位二进制数，因此其传输速度约为 1.6 Gb/s。

由于每个激光二极管需要两个字节的范围延时数据和一个字节的精度延时数据进行驱动，激光阵列中 4 096 个像素点共需要的数据量为  $1.2 \times 10^4$  个字节，要达到 1 kHz 的刷新频率，每秒要传输的数字量为  $1.2 \times 10^7$  字节，传输速率最小约 100 Mb/s。考虑到数据的存储处理等时间，传输速率要提升几倍。本文方法传输速度可以保证 1 kHz 刷新频率。

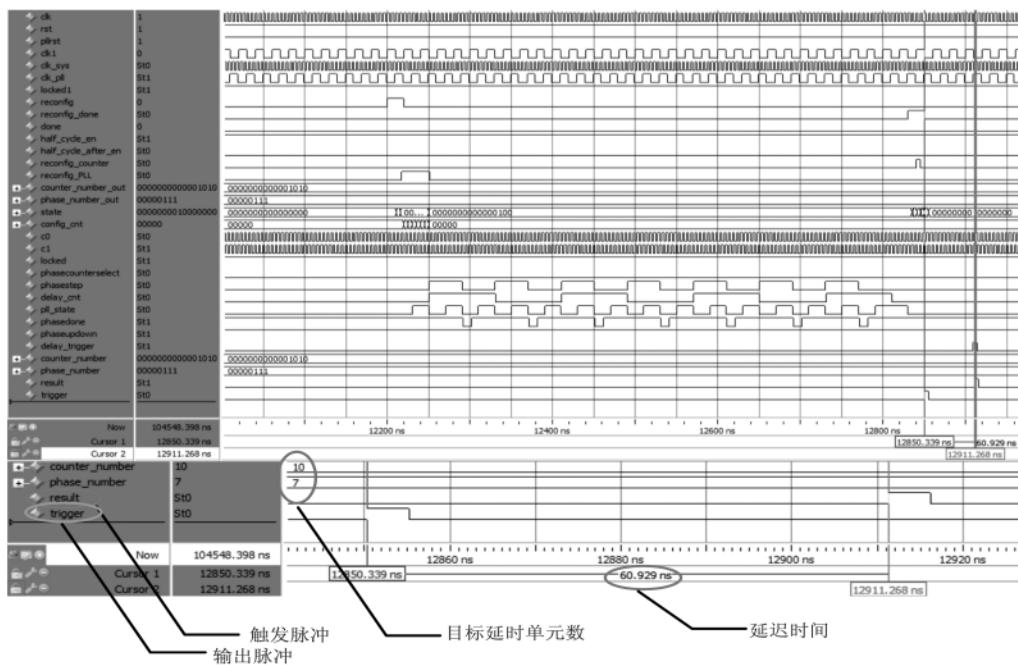

最后对高精度延时生成系统进行测试，方式为在 Modelsim 中进行门级仿真。以范围延时 10 个时钟周期，精度延时 6 个基本单元为例，此时测得的实际目标延时值为 60.804 ns，得到仿真结果如图 13 所示。

再将精度延时值改为 7 个单元进行仿真，仿真结构如图 14 所示。可以看出，两者之间的延时差为 125 ps，与锁相环中设定的最小延时步长相同，分辨率达到预定要求。

记录多次改变精度延时值时仿真得到的实际延时值，将数据汇成表格，结果如表 2 所示。

由表 2 中的数据可以看出，对于不同的目标延时值，实际生成的延时值总存在一定的误差，这是由于范围延时模块的采样问题、芯片内部的走线延时等多种因素造成。但此误差并不会随着延时值的不同而发生变化，而是始终固定在 10.054 ns，因此可以通过前端或后端的误差补偿来消除这一误差，使系统的精度达到分辨率的要求。

## 5 结论

本文在现有的激光回波仿真系统架构的基础上提出了传输速度更快、精度更高的设计方案。提出一种新

图 13 三维图像生成模块门级仿真结果 1

124—www.ChinaAET.com

《电子技术应用》<http://www.chinaaet.com>

图 14 三维图像生成模块门级仿真结果 2

表 2 时序仿真延时量实测数据

| 理论延时值  | 实际延时值  | (ns)   |

|--------|--------|--------|

| 50.75  | 60.804 | 10.054 |

| 51.875 | 61.929 | 10.054 |

| 52     | 62.054 | 10.054 |

| 52.5   | 62.554 | 10.054 |

| 53.125 | 63.179 | 10.054 |

| 53.5   | 63.554 | 10.054 |

| 54     | 64.054 | 10.054 |

| 54.875 | 64.929 | 10.054 |

的基于 FPGA 的光纤通信的方案,解决了现有反射内存卡传输速度慢的问题。光纤传输模块的数据传输速度达到 1.6 Gb/s,回波刷新频率超过了 1 kHz。开发了高精度延时电路,通过对锁相环的动态配置,达到每路 125 ps 的多路延时生成。仿真结果证明,本文方法可以满足激光回波仿真系统高传输速率、高精度的实际需求。

#### 参考文献

- [1] 陈运涛,黄寒砚,陈玉兰.雷达技术基础[M].北京:国防工业出版社,2014.

- [2] 刘尚富,胡辉.国外激光雷达的发展趋势[J].舰船电子工程,2017,37(6):1-4.

- [3] STEINVALL O,CARLSSON T,LARSSON C G H,et al. Laser based 3-D imaging new capabilities for optical sensing [R].FOI,Sweden:FOI-R--0856-SE,2003:1650-1942.

- [4] 杨兴雨,苏金善,王元庆.国内外激光成像雷达系统发展的研究[J].激光杂志,2016,37(1):1-4.

- [5] 黄鹏宇,杨麒麟.军用激光雷达技术的发展趋势分析[J].军民两用技术与产品,2017(4):92.

- [6] BUFORD J A.HWIL weapon system simulations in the U.S. army aviation and missile command(USA AMCOM)[J].Proceedings of SPIE-The International Society for Optical Engineering,2001,4366:82-89.

- [7] KIM H J,MOBLEY S B,BUFORD J A.AMCOM radar HWIL simulation system development[C].International Society for Optics and Photonics,2003.

- [8] KIM H J,CORNELL M C.Hardware-in-the-loop projector system for light detection and ranging sensor testing[J].Optical Engineering,2012,51(8):3609.

- [9] CORNELL M C,SNYDER D R.LADAR scene projector for hardware-in-the-loop testing[J].Proceedings of SPIE-The International Society for Optical Engineering,2002,4717:77-85.

- [10] KIM H J,CORNELL M C.AMRDEC's HWIL synthetic environment development efforts for LADAR sensors[J].Proceedings of SPIE-The International Society for Optical Engineering,2004,5408:203-214.

- [11] XU R,WANG X,TIAN Y,et al.Ladar scene projector for a hardware-in-the-loop simulation system[J].Applied Optics,2016,55(21):5745.

- [12] XU R,SHI R,YE J,et al.Research on key technologies of LADAR echo signal simulator[C].Applied Optics and Photonics China,2015.

- [13] 戴永江.激光雷达技术[M].北京:电子工业出版社,2010.

- [14] 陈学锋.光纤通信技术的应用及发展趋势探讨[J].通讯世界,2016(2):9-10.

(下转第 130 页)

- ence on Digital System Design: Architectures, Methods and Tools.IEEE , 2009 : 441–448.

- [3] 张颖.卫星数传 VCM/ACM 链路的关键技术研究[D].北京:中国科学院大学(中国科学院国家空间科学中心),2019.

- [4] 夏宇闻.VerilogHDL 数字系统设计教程[M].北京:北京航空航天大学出版社,2015.

- [5] MUELLER K H, MULLER M.Timing recovery in digital synchronous data receivers[J].IEEE Transactions on Communications , 1976 , 24(5) : 516–531.

- [6] Gardner F M.A BPSK/QPSK timing-error detector for sampled receivers[J].IEEE Transactions on Communications , 1986 .

- [7] BARLETTA L, MAGARINI M, SCARDONI F, et al.Impact of loop delay on the performance of Gardner timing recovery[J].IEEE Photonics Technology Letters , 2013 , 25(18) : 1797–1800.

- [8] Huang Zhen , Yang Pan , Zhang Weihan.Improved gardner suppression timing jitter synchronization algorithm[J].Journal of Electrical and Electronic Engineering , 2020 , 8(1) : 21–26.

- [9] 韩孟来,倪永婧.一种 16 倍采样的 Gardner 定时同步方法[J].电讯技术 , 2019 , 59(2) : 223–228.

- [10] 杜勇.数字通信同步技术的 MATLAB 与 FPGA 实现[M].北京:电子工业出版社,2015.

- [11] 吴大维.一种 QPSK 解调器(松尾环)的研制[J].电讯技术 , 1990(4) : 22–26.

- [12] SANGRIOTIS M, XEZONAKIS I.Digital costas loop-like PLL for the carrier recovery of a QPSK signal[J].Electronics Letters , 1993 , 29(10) : 897–899.

- [13] LINN Y.Robust M-PSK phase detectors for carrier synchronization PLLs in coherent receivers : theory and simulations[J].IEEE Transactions on Communications , 2009 , 57(6) : 1794–1805.

- [14] 何宗苗,姚远程,秦明伟.基于 System Generator 的盲均衡器设计与实现[J].电子技术应用 , 2014(7) : 33–36.

- [15] 刘俊杰.全数字锁相环电路的设计与实现[D].成都:电子科技大学 , 2011.

- [16] 杜瑜.三阶数字锁相环环路参数的设计方法[J].电讯技术 , 2007(5) : 156–158.

(收稿日期:2020-12-21)

扫码下载电子文档

(上接第 118 页)

- (5) : 1619–1622.

- [13] 赵洪锟.基于嵌入式 Linux 的 IEEE1588 协议的分析与实现[D].济南:山东大学 , 2012.

- [14] 王晋祺,陈鸿.基于 ARM 的 IEEE1588 精密时钟同步协议实现[J].电子器件 , 2019(6) : 1527–1531.

- [15] 陈炯聪.IEEE 1588 同步技术在电力系统中的应用[M].北京:中国电力出版社 , 2012.

- [16] 王延年,宋小伟.高精度时钟同步系统的研究与实现策

略[J].国外电子测量技术 , 2018(3) : 30–33.

(收稿日期:2020-12-02)

作者简介:

宋艳(1975–),女,高级工程师,主要研究方向:信息、通信技术及调度自动化技术。

应斌杰(1991–),男,硕士,工程师,主要研究方向:通信工程。

毛立振(1993–),通信作者,男,学士,工程师,主要研究方向:电力系统及自动化,E-mail:137356994@qq.com。

扫码下载电子文档

(上接第 125 页)

- [15] BOIYO D K, CHABATA T V, KIPNOO E K R, et al. Reconfigurable high-speed optical fiber networks : optical wavelength conversion and switching using VCSELs to eliminate channel collisions[J].Optical Fiber Technology , 2017 , 33 : 30–35.

(收稿日期:2020-12-17)

作者简介:

朱敏(1981–),男,博士,副教授,主要研究方向:电子系统自动化测试。

吴楠(1997–),男,硕士研究生,主要研究方向:FPGA 应用及数字图像处理。

杨春玲(1965–),通信作者,女,博士,教授,主要研究方向:电子系统设计,E-mail:yangcl1@hit.edu.cn。

扫码下载电子文档

## 版权声明

经作者授权，本论文版权和信息网络传播权归属于《电子技术应用》杂志，凡未经本刊书面同意任何机构、组织和个人不得擅自复印、汇编、翻译和进行信息网络传播。未经本刊书面同意，禁止一切互联网论文资源平台非法上传、收录本论文。

截至目前，本论文已经授权被中国期刊全文数据库（CNKI）、万方数据知识服务平台、中文科技期刊数据库（维普网）、DOAJ、美国《乌利希期刊指南》、JST 日本科技技术振兴机构数据库等数据库全文收录。

对于违反上述禁止行为并违法使用本论文的机构、组织和个人，本刊将采取一切必要法律行动来维护正当权益。

特此声明！

《电子技术应用》编辑部

中国电子信息产业集团有限公司第六研究所