**导读:**射频与微波技术包括电磁波的产生、放大、发射、传播及其与物质的相互作用、接收等,是雷达、通信等电子信息科学重要的公用技术。为了加强国内同行在射频微波领域的学术交流,促进微波技术应用水平的提高,《电子技术应用》杂志2021年第7期、第8期推出“射频与微波”主题专栏,论文内容涵盖

硅基射频场效应管的研制、Ka波段频率源的分析和设计、双模式高增益射频接收芯片的设计、反激变换器板级辐射的仿真、电磁波在等离子体中的传播分析等。本专栏论文都具有鲜明的工程应用背景,接触前沿技术应用,期待与读者互相切磋借鉴,共同提高我国的微波应用水平。本期刊出上半部分。

**特约主编:**谢拥军,北京航空航天大学电子信息工程学院教授,博士生导师。主要研究方向为天线与微波技术、计算电磁学及其应用、电磁兼容等。目前主持多项国家级纵向和企业横向科研项目。发表学术论文200余篇(其中SCI论文70余篇),主编(或参编)《HFSS原理与工程应用》、《简明微波》等专著8本。

## 采用平面分栅结构的高增益宽带射频VDMOS研制

于森<sup>1,2,3</sup>,宋李梅<sup>1,2,3</sup>,李科<sup>2,3</sup>,丛密芳<sup>2,3</sup>,李永强<sup>2,3</sup>,任建伟<sup>2,3</sup>

(1.中国科学院大学,北京100049;2.中国科学院微电子研究所,北京100029;

3.中国科学院硅器件技术重点实验室,北京100029)

**摘要:**硅基射频场效应晶体管具有线性度好、驱动电路简单、开关速度快、热稳定性好、没有二次击穿等优点,在HF、VHF和UHF波段具有广阔的应用前景。针对射频场效应晶体管宽带、高增益和高效率的应用需求,基于标准平面MOS工艺,采用平面分栅(split gate)结构,通过优化结构和工艺参数研制出一款工作电压为28V的硅基射频垂直双扩散金属氧化物半导体场效应晶体管(VDMOS)。该器件在30~90MHz频段范围内,小信号增益大于19dB,在60MHz频点下连续波输出功率可以达到87W,功率附加效率达72.4%,具有优异的射频性能。

**关键词:**射频;场效应晶体管;分栅;高增益;宽带;高效率

中图分类号:TN386.1

文献标识码:A

DOI:10.16157/j.issn.0258-7998.201192

中文引用格式:于森,宋李梅,李科,等.采用平面分栅结构的高增益宽带射频VDMOS研制[J].电子技术应用,2021,47(7):1~4,11.

英文引用格式:Yu Miao,Song Limei,Li Ke,et al. Development of high-gain broadband RF VDMOS using planar split gate structure[J]. Application of Electronic Technique,2021,47(7):1~4,11.

### Development of high-gain broadband RF VDMOS using planar split gate structure

Yu Miao<sup>1,2,3</sup>, Song Limei<sup>1,2,3</sup>, Li Ke<sup>2,3</sup>, Cong Mifang<sup>2,3</sup>, Li Yongqiang<sup>2,3</sup>, Ren Jianwei<sup>2,3</sup>

(1. University of Chinese Academy of Sciences, Beijing 100049, China;

2. Institute of Microelectronics of Chinese Academy of Sciences, Beijing 100029, China;

3. Key Laboratory of Science and Technology on Silicon Devices, Chinese Academy of Sciences, Beijing 100029, China)

**Abstract:** Silicon-based radio frequency field effect transistors have the advantages of excellent linearity, simple drive circuit, fast switching speed, excellent thermal stability, no secondary breakdown, etc., and have broad application prospects in HF, VHF and UHF bands. In view of the application requirements of the RF field effect transistors with broadband, high gain and high efficiency, based on the standard planar MOS process, the split gate structure was adopted and a silicon-based RF vertical double-diffused metal oxide semiconductor field effect transistor with working voltage of 28 V was developed by optimizing the structure and process parameters. In the frequency range from 30 MHz to 90 MHz, the device can achieve small signal gain greater than 19 dB, the continuous wave output power can reach 87 W at the frequency of 60 MHz, the power added efficiency up to 72.4%, has excellent radio frequency performance.

**Key words:** radio frequency; field effect transistor; split gate; high gain; broadband; high efficiency

## 0 引言

硅基射频场效应晶体管作为固态功率器件,与双极型晶体管相比,具有线性度好、驱动电路简单、开关速度快、热稳定性好、没有二次击穿和可以多胞并联输出大功率等一系列优点<sup>[1-2]</sup>,在高频(HF)、甚高频(VHF)和特高频(UHF)波段(如移动通信、广播、超视距雷达、磁共振成像、射频加热和无线电接收器等领域)得到广泛应用<sup>[3-4]</sup>。近几年来,虽然氮化镓(GaN)器件市场发展迅速,但是由于GaN材料加工工艺复杂,成本较高,主要适用于3.5 GHz或更高频段的高频大功率应用场合,而在较低频段,硅基射频垂直双扩散金属氧化物半导体场效应晶体管(Vertical Double-diffused Metal Oxide Semiconductor field effect transistor, VDMOS)由于成熟度和性价比更高而更具优势,因此,硅基射频VDMOS主要应用在低频宽带大功率和对可靠性要求较高的领域<sup>[5-7]</sup>。

目前,国外的硅基VDMOS技术比较成熟,主要公司有MA-COM、Polyfet、ST等。Polyfet公司有最高频率达1.5 GHz、输出功率范围为4~400 W的硅基射频VDMOS产品;ST公司的硅基VDMOS产品频率范围为1~250 MHz,最高峰值功率达到1 200 W;MA-COM公司的硅基VDMOS产品频率范围为DC~1 GHz,输出功率最高达600 W。国内的硅基VDMOS技术相对比较落后,但也有一定进展,如国内文献报导过的1 GHz、10 W、8 dB的硅基VDMOS器件<sup>[8]</sup>,以及530~650 MHz、连续波输出功率20 W、增益7.5 dB、效率49%的硅基VDMOS<sup>[9]</sup>等。

随着通信技术不断朝着超宽带、小型化、低功耗的趋势发展<sup>[9]</sup>,在包括电台应用在内的许多应用领域都需要器件能在较低工作电压下(28 V、12 V甚至更小)实现宽带、大功率、高增益、高效率的射频输出。本文基于电台应用对宽带、高增益、高效率射频场效应晶体管的应用需求,对标MA-COM公司某款同指标产品,设计一款工作频率在30~90 MHz范围内、输出功率大于80 W、功率增益大于13 dB、效率大于60%的高性能宽带射频场效应晶体管。

## 1 器件设计

## 1.1 基本原理

功率增益 $G_p$ 和截止频率 $f_T$ 是描述器件频率特性的两个关键参数<sup>[9]</sup>:

$$G_p = k \cdot f_T / (f_0^2 \cdot 8\pi R_G C_{gd}) \quad (1)$$

$$f_T = g_m / 2\pi (C_{gs} + C_{gd}) \quad (2)$$

其中, $g_m = \mu_n C_{ox} Z (V_{GS} - V_T) / L$ ;  $k$ 为与寄生参量有关的比例系数; $f_0$ 为工作频率; $R_G$ 为栅电阻; $C_{gd}$ 为栅漏电容; $C_{gs}$ 为栅源电容; $Z$ 为总栅宽; $L$ 为沟道长度。根据以上公式可知,可以通过优化结构和工艺参数提高器件的频率特性,如降低栅电容、缩短沟道长度和减小栅极电阻。

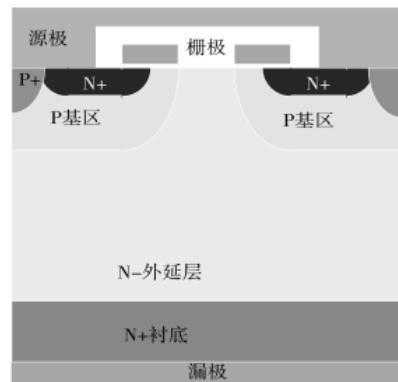

栅电容大小与器件结构密切相关,分栅(split gate)结构可以通过最小化栅漏重叠区域面积有效降低栅氧化

层电容 $C_{ox}$ 来减小 $C_{gd}$ <sup>[10-11]</sup>。图1所示为分栅VDMOS剖面结构图,与常规的低频VDMOS结构相比,分栅结构仅保留了两沟道上方的栅电极,大大减小了栅电极面积,从而得到较小的栅电容。因此,本文采用平面分栅结构降低栅电容,提高器件频率特性。

图1 分栅VDMOS

在缩短沟道长度方面,本文通过采用硼、砷离子注入双扩散自对准技术配合适当的沟道注入剂量和退火时间,可以实现对沟道长度的精确控制;为了减小栅极电阻,通过提高多晶硅栅电极的掺杂浓度和杂质激活率以及采用电阻率较低的栅极材料可以得到较低的栅电阻<sup>[12]</sup>。

器件的射频输出功率 $P_{out}$ 可表示如下<sup>[13]</sup>:

$$P_{out} = \eta \cdot (V_{DS} - V_{DSat}) \cdot I_D \quad (3)$$

其中, $I_D \propto \mu_n \cdot Z / L$ ;  $\eta$ 为效率,主要与导通电阻 $R_{on}$ 有关。根据式(3)可知,在效率一定的前提下,提高工作电压 $V_{DS}$ 和工作电流 $I_D$ 可以增大器件的输出功率。具体地,可以通过适当增大总栅宽来提高工作电流,增大射频输出功率。

## 1.2 器件仿真

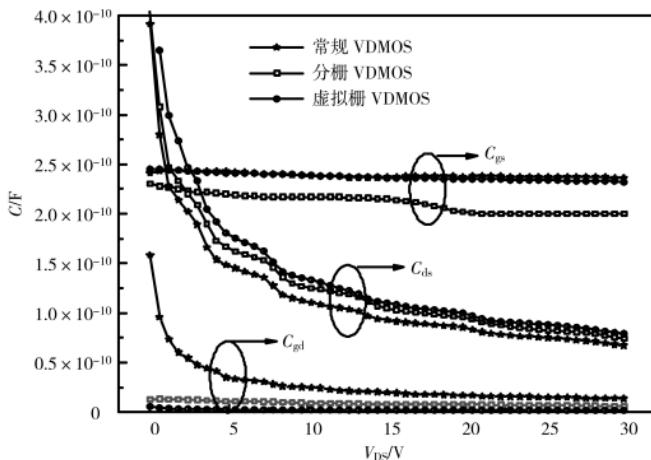

除分栅结构之外,虚拟栅(dummy gate)<sup>[14-15]</sup>结构也可以有效降低栅电容,但与分栅结构不同的是,虚拟栅结构在两个栅极之间引入和源极短接的虚拟栅电极,在正向漏偏压时,虚拟栅电极会辅助耗尽半导体中的载流子,使得 $C_{gd}$ 进一步减小。图2所示为常规VDMOS、分栅VDMOS和虚拟栅VDMOS的电容随漏压变化仿真曲线,表1为3种不同结构VDMOS的仿真参数及仿真值,表中 $C_{gs}$ 、 $C_{gd}$ 、 $C_{ds}$ 分别为栅源电容、栅漏电容和漏源电容。

通过仿真结果可以看出,虽然虚拟栅结构的 $C_{gd}$ 最小,在28 V工作电压下仅为1.6 pF,但是这种结构的 $C_{gs}$ 和 $C_{ds}$ 均大于分栅结构,在 $V_{DS}=28$  V时,虚拟栅VDMOS中的 $C_{gs}$ 为233.7 pF, $C_{ds}$ 为83.5 pF, $f_T$ 为4.4 GHz,而分栅VDMOS中的 $C_{gs}$ 为199 pF, $C_{ds}$ 为79.2 pF, $f_T$ 为4.8 GHz,这是因为虚拟栅电极的存在会不可避免地引入额外寄生电容 $C_{gs}$ 和 $C_{ds}$ ,导致 $f_T$ 降低。此外,与常规低频结构相比,由于半

图 2 3 种不同结构电容随漏压变化仿真曲线

表 1 不同结构 VDMOS 仿真参数

| 结构        | $R_{on}/\Omega$ | $C_{gs}/\text{pF}$ | $C_{gd}/\text{pF}$ | $C_{ds}/\text{pF}$ | $f_T/\text{GHz}$ |

|-----------|-----------------|--------------------|--------------------|--------------------|------------------|

| 常规 VDMOS  | 0.098           | 236.6              | 13.9               | 71.2               | 3.4              |

| 分栅 VDMOS  | 0.119           | 199.8              | 6.4                | 79.2               | 4.8              |

| 虚拟栅 VDMOS | 0.156           | 233.7              | 1.6                | 83.5               | 4.4              |

导体表面两沟道间积累层的缺失,导致这两种结构的 $R_{on}$ 略微增大,常规 VDMOS、分栅 VDMOS 和虚拟栅 VDMOS 中 $R_{on}$ 分别为 $0.098\Omega$ 、 $0.119\Omega$ 和 $0.156\Omega$ ,与常规结构相比,虚拟栅结构的导通电阻增大 59%,而分栅结构导通电阻仅增大 21%。

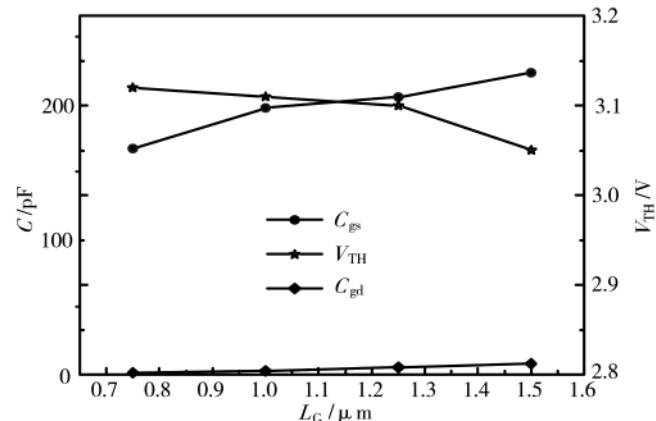

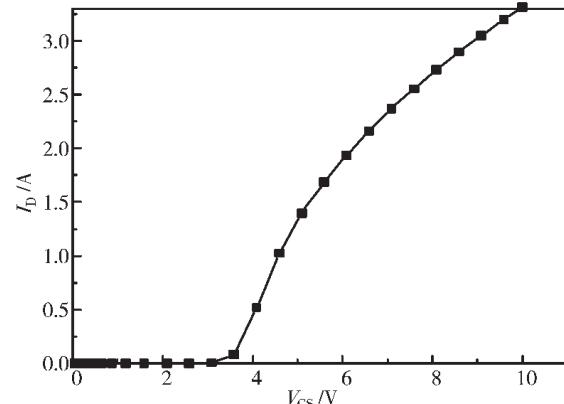

缩短栅电极长度  $L_G$  可以减小栅电容,从图 3 中可以直观地看出:减小  $L_G$  可以有效降低电容  $C_{gs}$  和  $C_{gd}$ ,但需要注意的是,栅极长度太短会造成部分导电沟道表面没有栅极覆盖,无法形成反型层,导致晶体管阈值电压  $V_{TH}$  迅速增大。因此,需要综合考虑栅电容与阈值电压之间的矛盾关系,折中优化,最终选定  $L_G$  为  $1.25\mu\text{m}$ ,仿真得到器件的转移特性曲线如图 4 所示,  $V_{TH}$  在  $3.09\text{V}$  左右。

分栅 VDMOS 的击穿电压  $BV$  不仅受到外延层浓度和厚度的影响,还受到两个栅极间距离的影响,结合 Sentaurus TCAD 仿真优化,选择合适的外延层参数和栅极间

图 3 栅电容和阈值电压与栅极长度关系仿真曲线

图 4 转移特性仿真曲线

距,仿真得到该器件的  $BV$  为  $96.8\text{V}$ ,可以满足  $28\text{V}$  工作电压的要求,图 5 为该器件的击穿特性仿真曲线。

图 5 击穿特性仿真曲线

## 2 射频性能评估

### 2.1 电性能测试

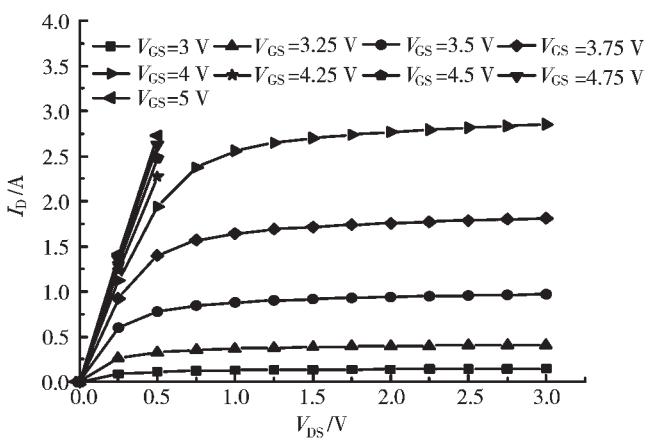

表 2 给出了器件电性能测试结果。测试结果显示,该器件实测击穿电压  $BV$  达到  $95.5\text{V}$ ,阈值电压  $V_{TH}$  为  $3.2\text{V}$ ,导通电阻  $R_{on}$  为  $0.16\Omega$ ,最大跨导  $g_m$  为  $8.9\text{S}$ ,输入电容  $C_{iss}$ 、输出电容  $C_{oss}$ 、反馈电容  $C_{rss}$  分别为  $191\text{pF}$ 、 $128\text{pF}$ 、 $10.5\text{pF}$ ,其中  $C_{iss} = C_{gs} + C_{gd}$ ,  $C_{oss} = C_{ds} + C_{gd}$ ,  $C_{rss} = C_{gs}$ , 各电性能参数均满足设计要求。

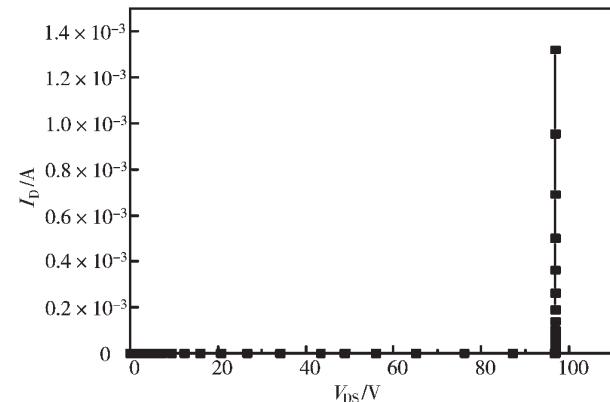

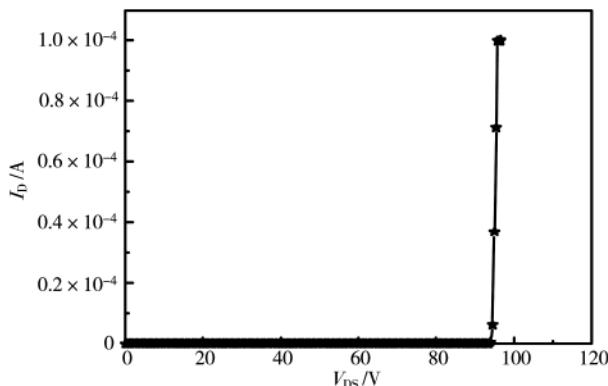

图 6 为该器件的实测击穿特性曲线,图 7 是实测的输出特性曲线。从实测的击穿曲线可以看出,击穿电压的实测值与仿真值拟合良好,说明本文对该器件的电性能分析和设计比较合理,实际的工艺过程控制良好。

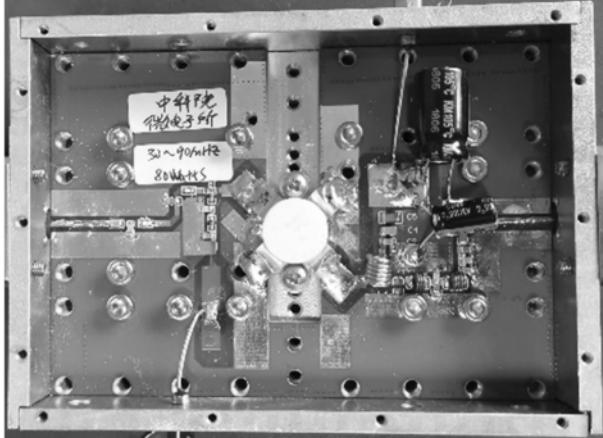

### 2.2 射频小信号测试

通过小信号模拟可以对器件的射频性能进行初步估计,图 8 是该器件及其匹配电路的 PCB 测试板。图 9 为

表 2 电性能测试结果

| 参数                  | 测量值  |

|---------------------|------|

| $BV/\text{V}$       | 95.5 |

| $V_{TH}/\text{V}$   | 3.20 |

| $R_{on}/\Omega$     | 0.16 |

| $g_m/\text{s}$      | 8.90 |

| $C_{iss}/\text{pF}$ | 191  |

| $C_{oss}/\text{pF}$ | 128  |

| $C_{rss}/\text{pF}$ | 10.5 |

图 6 击穿特性曲线

图 7 输出特性曲线

图 8 PCB 测试板

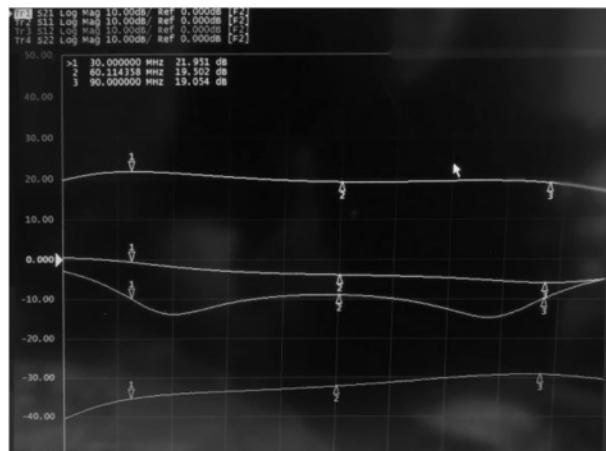

矢量网络分析仪上各频点的  $S$  参数测量曲线, 其中, 从上至下依次为  $S_{21}$ 、 $S_{11}$ 、 $S_{22}$  和  $S_{12}$  参数曲线。测试结果显示, 该器件在  $V_{DS}=28$  V、 $I_{DQ}=0.2$  A 的测试条件下, 在 30~90 MHz 频段范围内, 小信号增益  $S_{21}$  大于 19 dB, 增益平坦度为  $\pm 0.5$  dB, 小信号增益满足设计要求, 平坦度较好。

### 2.3 窄带射频性能测试

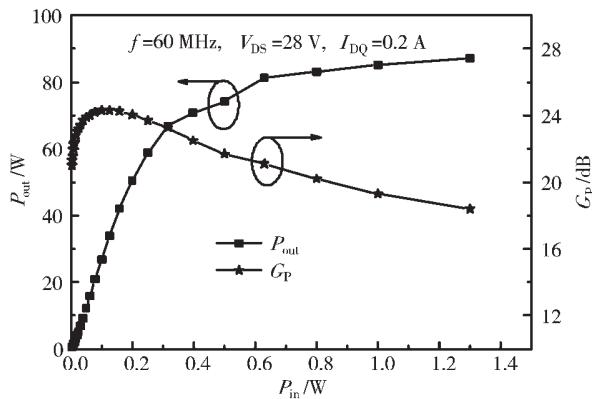

图 10 给出了该器件在  $f=60$  MHz、 $V_{DS}=28$  V、 $I_{DQ}=0.2$  A 的测试条件下, 其输出功率  $P_{out}$  和功率增益  $G_p$  与输入功

图 9 S 参数测量曲线

图 10 输出功率和增益与输入功率关系曲线

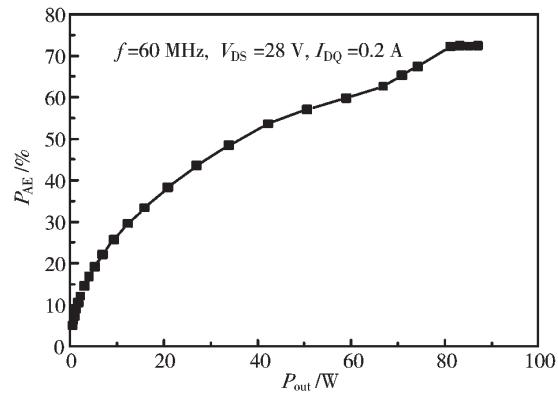

率  $P_{in}$  的关系曲线, 图 11 为该器件功率附加效率  $P_{AE}$  与输出功率  $P_{out}$  的关系曲线。测试结果显示, 该器件在 60 MHz 的频点下可以实现  $P_{out}=87$  W、 $G_p=18.4$  dB、 $P_{AE}=72.4\%$  的优异射频性能。

图 11 功率附加效率与输出功率关系曲线

### 2.4 宽带射频性能测试

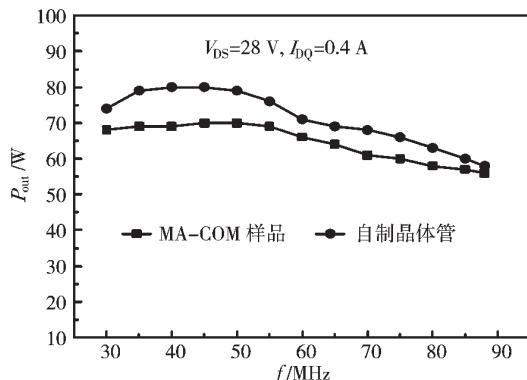

宽带射频性能是在  $V_{DS}=28$  V、 $I_{DQ}=0.4$  A 的测试条件下, 由两路器件经过功分器合成测得的。图 12 为在  $P_{in}=1$  W 时, 测试得到的 MA-COM 样品晶体管和本文自行研制

(下转第 11 页)

MOSFET using coupled electrical-thermal-mechanical analysis[C].Proceedings of the IEEE 2012 Prognostics and System Health Management Conference(PHM-2012 Beijing), 2012.

- [14] 高璐,徐策,董光冬,等.基于电磁仿真软件的平面变压器共模电磁干扰建模方法及其应用[J].电工技术学报,2020,35(24):5057–5063.

- [15] 刁家骐.基于混沌扩频技术的 AC/DC 开关变换器的传导 EMI 研究[D].广州:广州大学,2020.

(收稿日期:2021-03-08)

## 作者简介：

吴键澄(1995-),男,硕士研究生,主要研究方向:反激变换器、电磁兼容等。

杨汝(1971-),通信作者,女,博士,教授,硕士生导师,主要研究方向:电力电子装置与系统,E-mail:yangru@gzhu.edu.cn。

余连德(1951-),男,硕士,教授,主要研究方向:电力传动与变频器开发。

扫码下载电子文档

(上接第4页)

图 12 输出功率与频率关系曲线

晶体管的输出功率与频率关系曲线。经过对比可以看出，在30~90 MHz频段范围内，本文自制晶体管的射频输出功率均大于该样品晶体管，实测输出功率大于60 W。

### 3 结论

本文基于标准平面 MOS 工艺,采用平面分栅结构,通过优化结构和工艺参数研制出一款工作电压为 28 V 的宽带、高增益、高效率硅基射频场效应晶体管。该器件的直流参数符合设计要求,射频性能方面,该器件在 60 MHz 频点下连续波输出功率可以达到 87 W,增益达 18.4 dB,功率附加效率达 72.4%;在 30~90 MHz 频段范围内,小信号增益均大于 19 dB,实测输出功率均大于样品晶体管,具有优异的射频性能。

## 参考文献

- [1] 刘英坤,王占利,何玉樟,等.400MHz,CW 300W VDMOS 功率场效应晶体管[J].半导体技术,2000(2): 26-28.

- [2] 杨法明,杨发顺,张锗源,等.功率 VDMOS 器件的研究与发展[J].微纳电子技术,2011,48(10): 623-629, 673.

- [3] RAAB F H, CAVERLY R, CAMPBELL R, et al. HF, VHF, and UHF systems and technology[J]. IEEE Transactions on Microwave Theory and Techniques, 2002, 50(3): 888-899.

- [4] FARHADI R, FARHADI B. Optimization of vertical double-diffused metal-oxide semiconductor(VDMOS) power transistor structure for use in high frequencies and medical devices[J].

Electronic Physician, 2014, 6(2):816-819.

- [5] RAMARAO B V, MISHRA J K, PANDE M, et al. Comparison study of LDMOS and VDMOS technologies for RF power amplifiers [C]. 57th DAE Solid State Physics Symposium. Indian Inst Technol, Bombay, INDIA, 2012: 492–493.

- [6] 李飞. 硅射频 DMOSFET 发展现状 [J]. 科技创新与品牌, 2020(7): 52–55.

- [7] 林良. 高性能射频半导体功率器件设计及其可靠性研究 [D]. 上海: 上海交通大学, 2016.

- [8] 祁斌, 刘英坤, 王长河. 1GHz 微波功率 MOSFET 的研究 [J]. 半导体技术, 2000(1): 23–25.

- [9] 刘洪军, 傅义珠, 李相光. 530~650MHz 20W CW Si-VDMOS 场效应晶体管 [J]. 固体电子学研究与进展, 2009, 29(2): 192–194, 286.

- [10] REN M, CHEN Z, NIU B, et al. A low miller capacitance VDMOS with shield gate and oxide trench [C]. 2016 IEEE International Nanoelectronics Conference (INEC). Chengdu, 2016: 1–2.

- [11] CHEN Q, FENG Q. Impact of the parasitic capacitances with the change of distance between gates of the split-gate VDMOS [C]. World Automation Congress 2012, Puerto Vallarta, Mexico, 2012: 1–4.

- [12] 苏延芬, 刘英坤, 邓建国, 等. 射频功率 Trench MOSFET 研制 [J]. 微纳电子技术, 2008(7): 380–382, 386.

- [13] 格列别尼科夫. 射频与微波功率放大器设计 [M]. 张玉兴, 赵宏飞, 译. 北京: 电子工业出版社, 2006.

- [14] XU S M, REN C H, FOO P D, et al. Dummy gated radio frequency VDMOSFET with high breakdown voltage and low feedback capacitance [C]. 12th International Symposium on Power Semiconductor Devices & ICs. Proceedings. Toulouse, France, 2000: 385–388.

- [15] 张方媛. 功率 VDMOS 器件结构设计 [D]. 西安: 西安电子科技大学, 2009.

(收稿日期: 2020-12-10)

---

## 作者简介：

于淼(1994-),女,硕士研究生,主要研究方向:射频场效应晶体管。

扫码下载电子文档

## 版权声明

经作者授权，本论文版权和信息网络传播权归属于《电子技术应用》杂志，凡未经本刊书面同意任何机构、组织和个人不得擅自复印、汇编、翻译和进行信息网络传播。未经本刊书面同意，禁止一切互联网论文资源平台非法上传、收录本论文。

截至目前，本论文已经授权被中国期刊全文数据库（CNKI）、万方数据知识服务平台、中文科技期刊数据库（维普网）、DOAJ、美国《乌利希期刊指南》、JST 日本科技技术振兴机构数据库等数据库全文收录。

对于违反上述禁止行为并违法使用本论文的机构、组织和个人，本刊将采取一切必要法律行动来维护正当权益。

特此声明！

《电子技术应用》编辑部

中国电子信息产业集团有限公司第六研究所