# 2.3~2.7 GHz 双模式低噪声射频接收前端全集成芯片的设计 \*

饶忠君<sup>1</sup>, 张志浩<sup>1,2</sup>, 章国豪<sup>1,2</sup>

(1. 广东工业大学 信息工程学院, 广东 广州 510006; 2. 河源广工大协同创新研究院, 广东 河源 517000)

**摘要:** 基于 GaAs pHEMT 工艺设计了一款 2.3~2.7 GHz 双模式低噪声射频接收前端全集成芯片。该接收前端芯片包含一个单刀双掷(SPDT)收发开关及一个带旁路功能的低噪声放大器。一方面,采用带源级电感负反馈的共源共栅结构实现了放大器模式,将 SPDT 开关作为放大器输入匹配网络的一部分,一体化优化设计获得最少元件及较高 Q 值的输入匹配网络,进而实现低噪声、高增益和良好的输入回波损耗匹配;另一方面,采用多组开关联合实现了旁路功能用于衰减高输入功率的射频信号。测试结果表明,在 2.3~2.7 GHz 的宽频带范围内,实现的接收前端芯片在 LNA 模式下的噪声系数可达到 1.53~1.64 dB 的较低水平,且增益在 18.1~19.2 dB 之间,在 2.5 GHz 时输入 1 dB 压缩点为 -1.5 dBm;在旁路模式下,插入损耗在工作频段内维持在约 6~7 dB 的水平。

**关键词:** GaAs pHEMT; 低噪声放大器; 低噪声; 双模式

中图分类号: TN722.3

文献标识码: A

DOI: 10.16157/j.issn.0258-7998.211497

中文引用格式: 饶忠君, 张志浩, 章国豪. 2.3~2.7 GHz 双模式低噪声射频接收前端全集成芯片的设计[J]. 电子技术应用, 2021, 47(7): 17~20, 47.

英文引用格式: Rao Zhongjun, Zhang Zhihao, Zhang Guohao. Design of a 2.3~2.7 GHz dual-mode low-noise RF receiver front end[J]. Application of Electronic Technique, 2021, 47(7): 17~20, 47.

## Design of a 2.3~2.7 GHz dual-mode low-noise RF receiver front end

Rao Zhongjun<sup>1</sup>, Zhang Zhihao<sup>1,2</sup>, Zhang Guohao<sup>1,2</sup>

(1. School of Information, Guangdong University of Technology, Guangzhou 510006, China;

2. Synergy Innovation Institute of GDUT, Heyuan, Heyuan 517000, China)

**Abstract:** A fully-integrated dual-mode low-noise RF receiver front-end for the 2.3 GHz~2.7 GHz band was presented based on a GaAs pHEMT technology. The receiver front-end consists of a single-pole double-throw(SPDT) transmit-receive switch and a low-noise amplifier(LNA)with bypass mode. The cascode common-source structure with inductive degeneration topology is adopted to achieve the LNA. The SPDT switch is embedded into the input matching network as a concurrent design to realize high Q matching network with minimum components for low noise, high gain and superior input return loss matching. Concurrent design of multiple switches for Bypass function is utilized to attenuate the high input power transmissions. The measurement results show that the presented FEM exhibits low noise figure of 1.53~1.64 dB and gain of 18.1~19.2 dB for 2.3~2.7 GHz frequency range in the high-gain LNA mode. At 2.5 GHz, the tested input 1 dB compression point at 2.5 GHz is -1.5 dBm. The insertion loss in Bypass mode typically varies from 6 to 7 dB in the operation frequency bands.

**Key words:** GaAs pHEMT; low noise amplifier; low noise; dual mode

## 0 引言

近年来,通信技术以惊人的速度发展,新一代移动通信芯片将被要求支持更多的频段和敦促显著的频率灵活性。低噪声放大器在蜂窝通信、WLAN、无线传感网络和 WiMax 等领域得到了广泛运用<sup>[1]</sup>。在 2019 年 RDCAPE 会议,BANSAL M 和 JYOTI 提出了一款基于 CMOS 工艺的 2.4 GHz 蓝牙通信的低噪声放大器,它的噪声系数为 3.695 dB,最大增益为 21.154 dB<sup>[2]</sup>。同年的

IEMCON 会议,KHOSAVI H 等人发表了一个应用于 WLAN 2.4 GHz 的低噪声放大器,该低噪声放大器的增益为 15.1 dB,噪声系数为 2.7 dB<sup>[3]</sup>。近年来,对于宽频带低噪放的研究也受到了广泛的关注。例如 2020 年 PATHAKR D 等人设计了一个工作在 2.2~2.55 GHz 的无线传感器网络低噪声放大器,在工作频段内的噪声系数和增益分别为 3.6 dB 和 24 dB<sup>[4]</sup>。但是,这些研究在实现高增益宽频带情况下获得的噪声系数普遍比较大。为

\* 基金项目:广东省重点领域研发计划项目(2018B010115001);国家自然科学基金项目(61974035);广东省“珠江人才计划”本土创新科研团队项目(2017BT01X168)

此,本文基于 GaAs pHEMT 工艺,设计并实现了一款宽频带、可满足多种无线通信服务需求的带旁路功能的射频接收前端全集成芯片。在 LNA 模式下,该芯片在 2.3~2.7 GHz 的宽频带范围内可实现 1.53~1.64 dB 较低的噪声系数和 18.1~19.2 dB 较高的增益性能。

## 1 电路设计

### 1.1 接收前端芯片整体框图

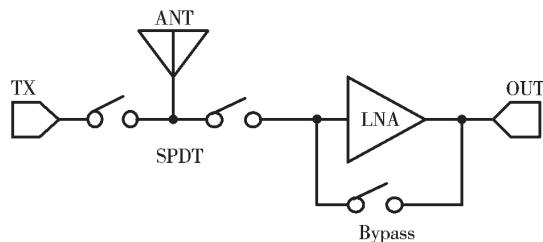

图 1 显示了所设计的射频接收前端全集成芯片整体框图,主要由单刀双掷(SPDT)收发开关和低噪声放大器两部分构成。其中,设计的低噪声放大器包含两种工作模式,LNA 使能模式和旁路(Bypass)模式<sup>[5]</sup>。ANT 端口为射频信号的输入端,OUT 端口为射频信号输出端。从天线端接收到的信号先经过 SPDT 开关的 RX 通道到达低噪声放大器的输入端。在 LNA 模式下,低噪声放大器将接收到的微小信号进行放大以供给后级电路。在 Bypass 模式下,输入的高功率信号将被旁路,使得输出信号能够在可控范围内,供后级电路处理,同时提高接收系统的动态范围<sup>[6]</sup>。

图 1 射频接收前端芯片框架图

### 1.2 射频开关设计

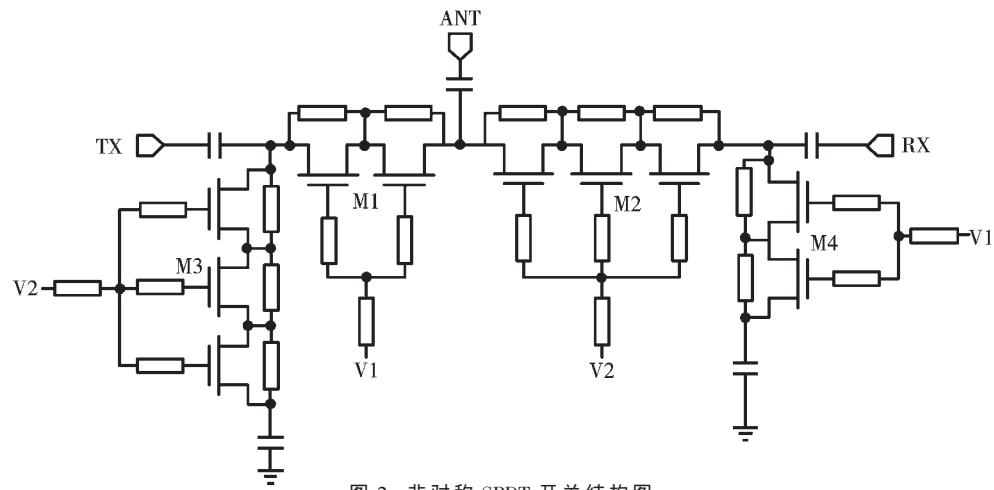

如图 2 所示,本设计的 SPDT 开关采用非对称结构<sup>[7]</sup>。根据发射及接收输入信号不同的功率容量要求,在发射链路的串联支路上堆叠了 2 个开关管(等效为 M1),并联支路上堆叠了 3 个开关管(等效为 M3);而在接收链路的串联支路上堆叠了 3 个开关管(等效为 M2),并联的支路上堆叠了 2 个开关管(等效为 M4)。在 TX、ANT、RX

图 2 非对称 SPDT 开关结构图

射频端口和与之间加入隔直电容以实现直流电压的悬浮<sup>[8]</sup>。当 V1 为高电平,V2 为低电平时,M1、M4 导通,M2、M3 关断,此时工作于发射模式,来自 PA 的大功率信号从 TX 端口输入,从 ANT 端口输出。当 V1 为低电平,V2 为高电平时,M2、M3 导通,M1、M4 关断,从天线接收到的信号从 ANT 端口输入,从 RX 端口输出。

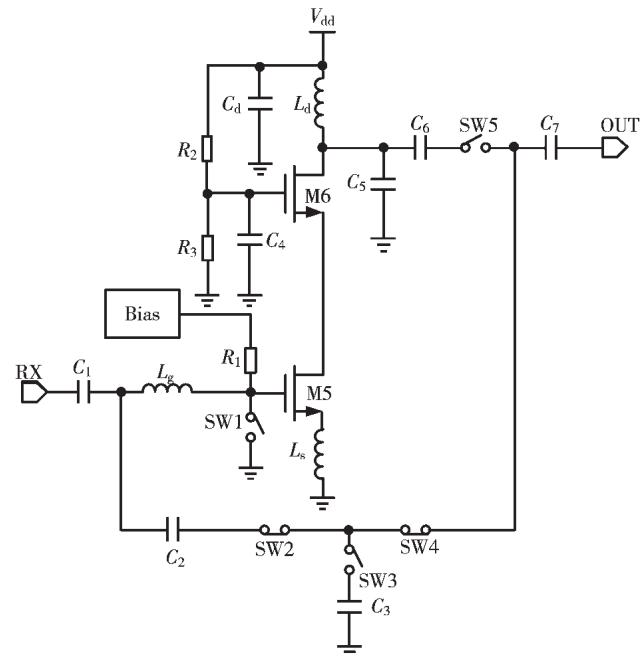

### 1.3 LNA 模式电路设计

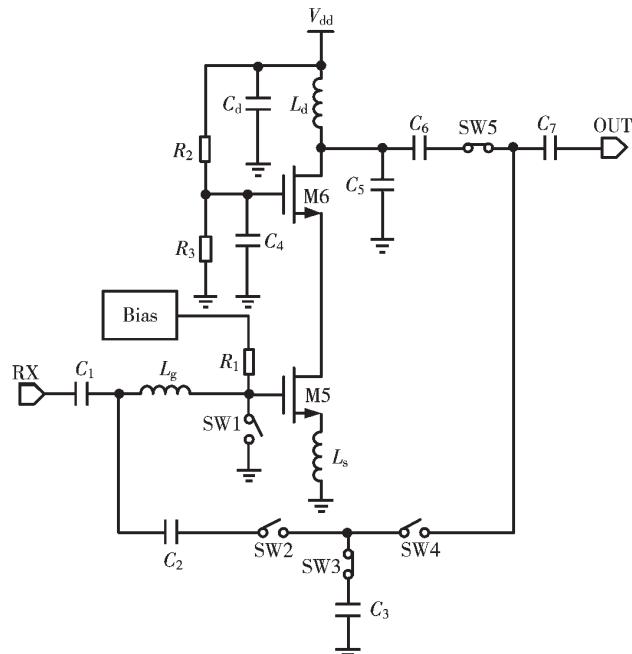

低噪声放大器的设计目标是在尽量低噪声系数的情况下提高增益<sup>[9]</sup>。如图 3 所示,为了同时获得较低的噪声系数和较高的增益,主放大电路采用带源极电感负反馈的共源共栅结构<sup>[10]</sup>。在不增加噪声的情况下,输入端采用源极电感  $L_s$  负反馈结构实现输入匹配,尽可能实现最小的噪声和最大的增益。LNA 模式的输入阻抗  $Z_{in}$ 、输入网络等效 Q 值、增益  $A_v$  如下:

图 3 LNA 模式原理图

$$Z_{in} = R_{on} + R_g + \frac{1}{j\omega(C_1 + C_{gs})} + j\omega(L_g + L_s) + \frac{g_{m5}L_s}{C_{gs}} \quad (1)$$

$$Q = w(L_g + L_s)/(R_{on} + R_g) \quad (2)$$

$$A_v = (g_{m6} + g_{mb6})r_{05}g_{m5}r_{05} \quad (3)$$

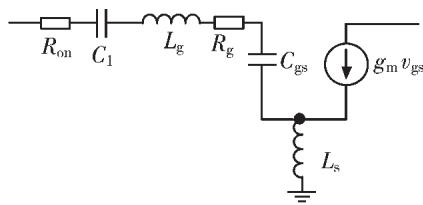

其中,  $C_1$  为隔直电容,  $C_{gs}$  为 M5 管的栅源电容,  $g_{m5}$  为 M5 管的跨导,  $g_{m6}$ 、 $g_{mb6}$  分别为 M6 管的跨导和体跨导,  $r_{05}$  与  $r_{06}$  分别为 M5 管、M6 管的输出电阻,  $R_{on}$  为 RX 射频开关导通电阻<sup>[11]</sup>,  $R_g$  为栅极输入匹配电感等效寄生电阻。由式(1)可知, 输入匹配电路主要由 RX 开关导通电阻  $R_{on}$ 、隔直电容  $C_1$ 、输入电感  $L_g$ 、源极电感  $L_s$ 、M5 的栅源电容  $C_{gs}$  等构成。可以通过调节输入电感  $L_g$  与源极电感  $L_s$  的值使得输入等效电感值与隔直电容  $C_1$ , 放大管 M1 的寄生电容  $C_{gs}$  输入等效电容值在低噪声放大器所处的频带内谐振, 使得输入阻抗的虚部近似等于零。同时在这一过程中还需要折中调节源极电感  $L_s$  的值, 使得输入阻抗的实部为  $50 \Omega$ , 实现整体阻抗的匹配<sup>[12]</sup>。作为全集成接收前端芯片, 射频开关与低噪声放大器是联合设计的, 因此射频开关也参与了低噪声放大器的输入匹配, 进而实现整个工作频带的输入匹配。如图 4 所示, 输入等效电路为串联 RLC 电路, 由式(2)可知输入网络等效  $Q$  值与  $R_{on}$  和  $R_g$  成反比。因此, 在设计过程中, 应尽量提高输入匹配网络的  $Q$  值并降低开关的插入损耗, 有助于提升增益并降低噪声系数。由式(3)可知, 共源共栅放大器的增益是共源极放大器增益的平方, 具有高增益特性, 可以实现更高的增益<sup>[13]</sup>。此外共源共栅结构的等效漏源电容  $C_{sl}$  可以等效为共源管的栅漏电容和共栅管的栅漏电容的串联, Miller 电容效应较小, 进而使得输出端对输入端产生的影响较小<sup>[14]</sup>。

图 4 输入网络等效电路

#### 1.4 Bypass 模式电路设计

考虑到接收机在靠近信号源时会获得很高的功率, 同时为了提高接收机的动态范围<sup>[15]</sup>, 本设计增加了 Bypass 电路功能。如图 5 所示, Bypass 功能主要由开关 SW1、SW2、SW3、SW4 和 SW5 构成, 这些开关根据工作模式自动切换。在 LNA 模式下, 开关 SW1、SW2、SW4 处于关断状态, 开关 SW3 和 SW5 处于闭合状态。开关 SW3 被设计在 LNA 模式下增加 Bypass 通路的隔离度。在 Bypass 模式下, 开关 SW1、SW2、SW4 处于导通闭合状态, 开关 SW3 和 SW5 处于关断状态。开关 SW2 和 SW4 为 Bypass 主要通路, Bypass 模式下的插入损耗主要由这两个开关管决定。开关 SW1 主要用于在 Bypass 模式下切

图 5 Bypass 模式原理图

断低噪声放大器的栅极偏置, 并防止高输入功率信号对放大管 M5 的栅源极造成损坏。

#### 2 测试结果分析

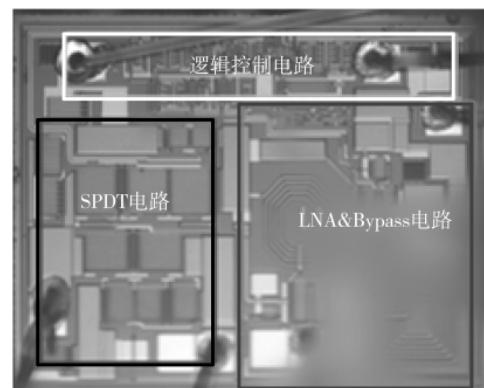

图 6 给出了射频接收前端全集成芯片的显微镜照片, 其中黑色方框为 SPDT 开关, 灰色方框代表 LNA 和 Bypass 电路, 白色方框代表逻辑控制电路。

图 6 全集成接收前端芯片照

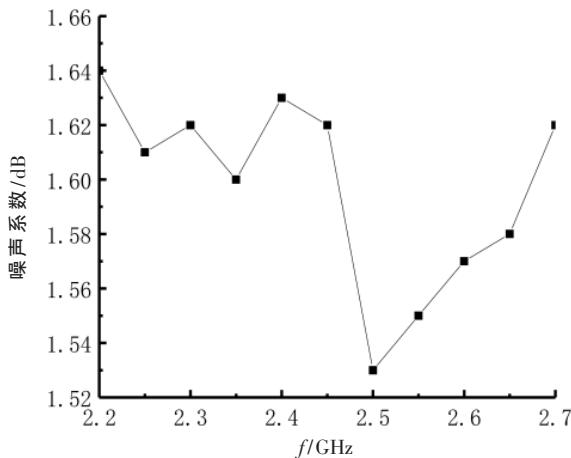

图 7 描述了 LNA 模式下接收前端芯片的噪声系数测试, 包括 SPDT TX/RX 开关以及 LNA 噪声系数, 在 2.3~2.7 GHz 频率范围内, 噪声系数为 1.53~1.64 dB。

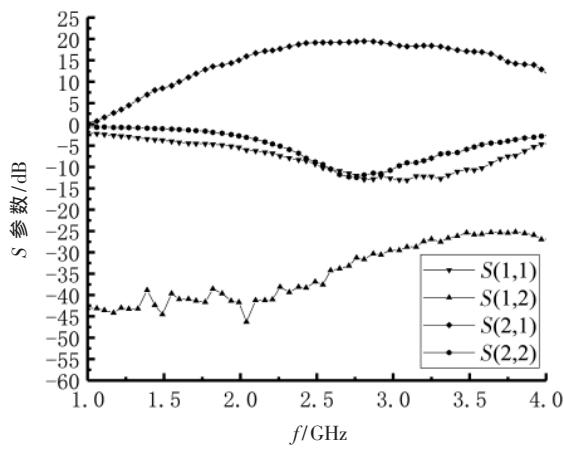

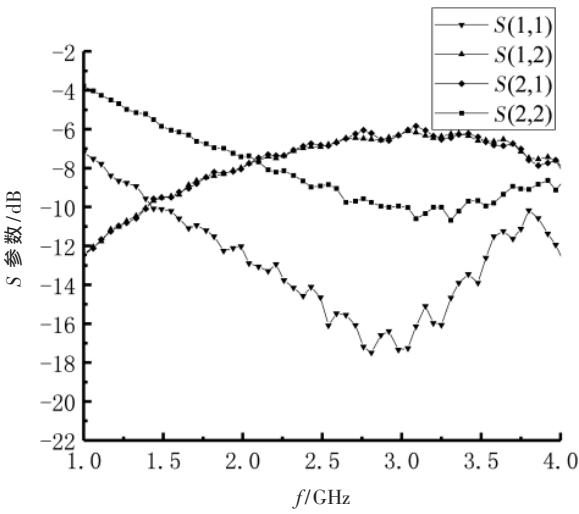

图 8 呈现了 LNA 模式的小信号 S 参数测试结果。在 2.3~2.7 GHz 频率范围内, LNA 模式下小信号增益  $S_{21}$  在 18.1~19.2 dB 之间, 反向隔离度大于 -30 dB。

图 9 给出了 Bypass 模式下 S 参数测试图。在 2.3~2.7 GHz, 旁路整体损耗约为 6~7 dB, 能有效衰减输入的高功率信号。

图 7 LNA 模式噪声系数测试图

图 8 LNA 模式 S 参数测试图

图 9 Bypass 模式 S 参数测试图

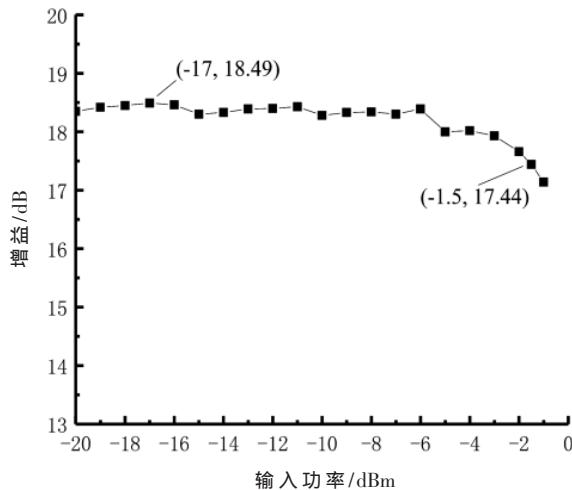

如图 10 所示, LNA 模式下, 在 2.5 GHz 时测试输入 P1dB 为 -1.5 dBm。这表明低噪声放大器的线性度良好。

本文结果与近年来发表的文献对比如表 1 所示, 可以看出, 本设计实现的芯片的噪声系数水平明显低于其他设计。

图 10 LNA 模式输入 P1dB@2.5 GHz 测试图

表 1 LNA 测试结果与近年来发表文献对比

| 频率 / GHz | 增益 / dB  | 噪声系数 / dB |

|----------|----------|-----------|

| 文献[2]    | 2.4      | 21.154    |

| 文献[3]    | 2.4      | 15.1      |

| 文献[4]    | 2.2~2.55 | 24        |

| 本文       | 2.3~2.7  | 18.1~19.2 |

|          |          | 1.53~1.64 |

### 3 结论

本文基于一种 GaAs pHEMT 工艺, 设计并实现了一款宽频带的射频接收前端全集成芯片, 具有 LNA 高增益和 Bypass 双模式。整体电路由非对称收发开关及带源级电感负反馈的共源共栅结构构成, 在宽频带内保证较低的噪声系数的同时也提升了增益和线性度。实现的接收前端全集成芯片在 LNA 模式下, 于 2.3~2.7 GHz 频率范围内测试的噪声系数可达到 1.53~1.64 dB 的较低水平, 且增益在 18.1~19.2 dB 之间。在 2.5 GHz 时, 输入 1 dB 压缩点为 -1.5 dBm。

### 参考文献

- [1] BANSAL M, JYOTI. A review of various applications of low noise amplifier[C]. 2017 International Conference on Innovations in Control, Communication and Information Systems, 2017: 1~4.

- [2] BANSAL M, JYOTI. Low power and high linearity cascode CMOS LNA for BLE applications in 45 nm technology[C]. 2019 3rd International Conference on Recent Developments in Control, Automation and Power Engineering, 2019: 76~81.

- [3] KHOSRAVI H, BIJARI A, KANDALAFTE N, et al. A low power concurrent dual-band low noise amplifier for WLAN applications[C]. 2019 IEEE 10th Annual Information Technology, Electronics and Mobile Communication Conference, Canada: IEEE, 2019: 1118~1123.

- [4] PATHAK D, VARDHAN D, KUMAR A, et al. An ultra low power 2.4GHz sub-threshold LNA with tunable input

(下转第 47 页)

- and Systems , 2013.

- [2] 李毅.高速数据采集、存储及处理系统设计[D].西安:西安电子科技大学,2009.

- [3] SEKIMOTO R, SHIKATA A, YOSHIOKA K, et al. A 0.5-V 5.2-fJ/conversion-step full asynchronous SAR ADC with leakage power reduction down to 650 pW by boosted self-power gating in 40-nm CMOS[J]. IEEE Journal of Solid-State Circuits, 2013, 48(11): 2628–2636.

- [4] LIOU C Y, HSIEH C C. A 2.4-to 5.2fJ/conversion-step 10b 0.5-to-4MS/s SAR ADC with charge-average switching DAC in 90nm CMOS[C]. 2013 IEEE International Solid-State Circuits Conference Digest of Technical Papers, 2013.

- [5] CHEN Y J, HSIEH C C. A 0.4V 2.02fJ/conversion-step 10-bit hybrid SAR ADC with time-domain quantizer in 90nm CMOS[C]. 2014 Symposium on VLSI Circuits digest of Technical Paper, 2014.

- [6] STEPANOVIC D V. Calibration techniques for time-interleaved SAR A/D converters[D]. Berkeley: University of California at Berkeley, 2012.

- [7] KEANE J P, GUILAR N J, STEPANOVIC D, et al. An 8GS/s time-interleaved SAR ADC with unresolved decision detection achieving -58dBFS noise and 4GHz band width in 28nm CMOS[C]. 2017 IEEE International Solid-State Circuits Conference, 2017.

- [8] Guo Mingqiang, Mao Jiaji, Sin Sai-Weng, et al. A 29mW 5GS/s time-interleaved SAR ADC achieving 48.5dB SNDR with fully-digital timing-skew calibration based on digital-

- mixing[C]. IEEE Symposium on VLSI Circuits, 2019.

- [9] 王娜.电荷再分配 SAR ADC 设计中高精度的实现[D]. 成都: 四川大学, 2006.

- [10] 闫传平. 逐次逼近型模数转换器数字校准技术研究与实现[D]. 成都: 电子科技大学, 2010.

- [11] 杜翎. 基于非二进制量化算法的逐次逼近模数转换器的设计[D]. 成都: 电子科技大学, 2016.

- [12] 陈海波. 0.35um CMOS 工艺下 12 位 30MS/s SAR ADC 的设计[D]. 南京: 东南大学, 2016.

- [13] Lee Chun C, Lu Cho-Yung, NARAYANASWAMY R, et al. A 12b 70MS/s SAR ADC with digital startup calibration in 14nm CMOS[C]. Symposium on VLSI Circuits Digest of Technical Papers, 2015.

- [14] Ye Fan, Li Shuai, Zhu Min, et al. A 13-bit 180-MS/s SAR ADC with efficient capacitor-mismatch estimation and dither enhancement[C]. 2019 IEEE International Symposium on VLSI Circuits and Systems, 2019.

- [15] Shen Junhua, SHIKATA A, FERNANDO L D, et al. A 16-bit 16-MS/s SAR ADC with on-chip calibration in 55-nm CMOS[J]. IEEE Journal of Solid State Circuits, 2018, 53(4): 1149–1160.

(收稿日期: 2020-12-06)

**作者简介:**

杨荣彬(1982-),男,硕士研究生,工程师,主要研究方向:模拟集成电路设计。

徐振涛(1987-),男,博士研究生,工程师,主要研究方向:模拟集成电路设计。

扫码下载电子文档

(上接第 20 页)

- matching for wireless sensor network applications[C]. 2020 IEEE International Conference on Semiconductor Electronics. Malaysia: IEEE, 2020: 73–76.

- [5] 魏启迪,林俊明,章国豪,等.应用于 802.11ac 的 SiGe BiCMOS 低噪声放大器[J].电子技术应用, 2018, 44(7): 42–45.

- [6] ZHONG L, ZHANG Z, LI J, et al. A dual mode integrated LNA and switch for WLAN receiver[C]. 2019 IEEE Asia-Pacific Microwave Conference. Singapore: IEEE, 2019: 1354–1356.

- [7] 耿红亮.高线性宽带非对称 SPDT 射频开关设计[D].杭州:浙江大学, 2017.

- [8] 张志浩.射频开关的研究及其在新一代智能手机前端的应用[D].广州: 广东工业大学, 2017.

- [9] 张玲玲.基于 GaAs 工艺的低噪声放大器及 ESD 保护电路设计[D].南京: 东南大学, 2015.

- [10] 徐邵然.应用于 WSN 的 2.4GHz 低功耗低噪声放大器设计[D].南京: 东南大学, 2015.

- [11] 张昊.宽带接收机前端关键模组中关键电路的研究与

设计[D].合肥:中国科学技术大学, 2018.

- [12] 屠志晨.pHEMT 通用导航低噪声放大器设计[D].杭州:浙江大学, 2016.

- [13] 汪宁欢.应用于 5G 基站的低噪声放大器和射频接收前端设计[D].南京: 中国电子科技集团公司电子科学研究院, 2019.

- [14] 张宁.GaAs\_pHEMT 噪声模型及低噪声放大器的研究设计[D].西安: 西安电子科技大学, 2019.

- [15] 倪冬欣,彭龙新,李建平,等.5\_6GHz 限幅低噪声放大器的研制[J].固态电子学研究与进展, 2020, 40(1): 18–22.

(收稿日期: 2021-03-12)

**作者简介:**

饶忠君(1996-),男,硕士研究生,主要研究方向:射频集成电路设计。

张志浩(1989-),通信作者,男,博士,讲师,主要研究方向:射频集成电路设计、射频电路特性建模及电磁仿真,E-mail: zhihaozhang@gdut.edu.cn。

章国豪(1964-),男,博士,教授,主要研究方向:模拟、射频、微波及毫米波单片集成电路设计及新技术研发。

扫码下载电子文档

## 版权声明

经作者授权，本论文版权和信息网络传播权归属于《电子技术应用》杂志，凡未经本刊书面同意任何机构、组织和个人不得擅自复印、汇编、翻译和进行信息网络传播。未经本刊书面同意，禁止一切互联网论文资源平台非法上传、收录本论文。

截至目前，本论文已经授权被中国期刊全文数据库（CNKI）、万方数据知识服务平台、中文科技期刊数据库（维普网）、DOAJ、美国《乌利希期刊指南》、JST 日本科技技术振兴机构数据库等数据库全文收录。

对于违反上述禁止行为并违法使用本论文的机构、组织和个人，本刊将采取一切必要法律行动来维护正当权益。

特此声明！

《电子技术应用》编辑部

中国电子信息产业集团有限公司第六研究所