# 一种应用于 CAN 收发器的宽输入范围的迟滞比较器设计 \*

冯世勤, 冯全源

(西南交通大学 微电子研究所, 四川 成都 611756)

**摘要:** 为了将 CAN(Controller Area Network)总线上的-12~12 V 的信号转化为 0~5 V 的串行数字信号, 设计了一种应用于 CAN 收发器的宽输入范围的迟滞比较器。实现的方案是先使用电阻将电源和总线上的信号线性叠加得到 5 V 电压内的信号, 再使用全差分放大器进行钳位, 使用共模反馈稳定共模工作点, 最后使用对尾电流进行温度补偿的内部正反馈的迟滞比较器比较得到数字信号。基于 VIS 0.4  $\mu\text{m}$  BCD 工艺, 使用 Hspice 进行了仿真验证。仿真结果表明: 电路能够将-12~12 V 的电压比较得到正确的数字信号。在常温即 25 °C, TT 工艺角下, 迟滞门限为 108.9 mV。在温度从 -40 °C~125 °C 变化时, 迟滞门限电压变化小于 9.16 mV, 温度系数为 0.055 5 mV/°C。

**关键词:** 迟滞比较器; 宽输入范围; 迟滞门限电压; 温度补偿; 全差分运算放大器; 共模反馈

中图分类号: TN402

文献标识码: A

DOI: 10.16157/j.issn.0258-7998.201253

中文引用格式: 冯世勤, 冯全源. 一种应用于 CAN 收发器的宽输入范围的迟滞比较器设计[J]. 电子技术应用, 2021, 47(7): 52~56.

英文引用格式: Feng Shiqin, Feng Quanyuan. Design of a hysteresis comparator with wide input range for CAN transceiver[J]. Application of Electronic Technique, 2021, 47(7): 52~56.

## Design of a hysteresis comparator with wide input range for CAN transceiver

Feng Shiqin, Feng Quanyuan

(Institute of Microelectronics, Southwest Jiaotong University, Chengdu 611756, China)

**Abstract:** A hysteresis comparator with wide input range for Controller Area Network(CAN) transceiver is designed to convert the -12~12 V signals on CAN bus into 0~5 V serial digital signals. The solution is to use resistance to linearly superimpose the signals on the power supply and bus to get the signals in the 5 V voltage, then use full differential amplifier to clamp, use common mode feedback to stabilize the common mode working point, and finally use the internal positive feedback hysteresis comparator that can compensate the temperature of the tail current to get the digital signal. Based on VIS 0.4  $\mu\text{m}$  BCD process, Hspice is used for simulation and verification. The simulation results show that the circuit can get the correct digital signal by comparing the voltage of -12~12 V. The hysteresis threshold was 108.9 mV at room temperature(25 °C) and TT process corner. When the temperature changes from -40 °C to 125 °C, the change of hysteresis threshold voltage is smaller than 9.16 mV, the temperature coefficient is 0.055 5 mV/°C.

**Key words:** hysteresis comparator; wide input range; hysteresis threshold voltage; temperature compensation; fully differential operational amplifier; common mode feedback

## 0 引言

CAN 总线作为一种现场总线, 因为其可靠安全、实时通信和灵活控制的特点, 在工程实践中广受工程师的欢迎<sup>[1]</sup>。CAN 总线整体由物理总线、收发器和控制单元三部分构成。CAN 收发器是负责 MCU 或 DSP 等 CAN 控制单元和物理总线之间信号传递的结构<sup>[2]</sup>。CAN 总线上的信号 CANH 和 CANL 是摆幅为-12~12 V 的差分电压信号, 而 CAN 控制单元仅识别数字信号, 所以 CAN 收发器中的比较器需要将共模范围为-12~12 V 的模拟信号转化为 0~5 V 的串行数字信号。CAN 收发器中比较

器的性能对整个网络系统的安全性、可靠性和电磁兼容性起到了关键作用<sup>[3]</sup>。本文设计的比较器目的就是将总线信号 CANH 和 CANL 得到的差分信号 VID 转化为数字信号, 比较器输出的迟滞范围约为 108.9 mV。

### 1 传统的迟滞比较器

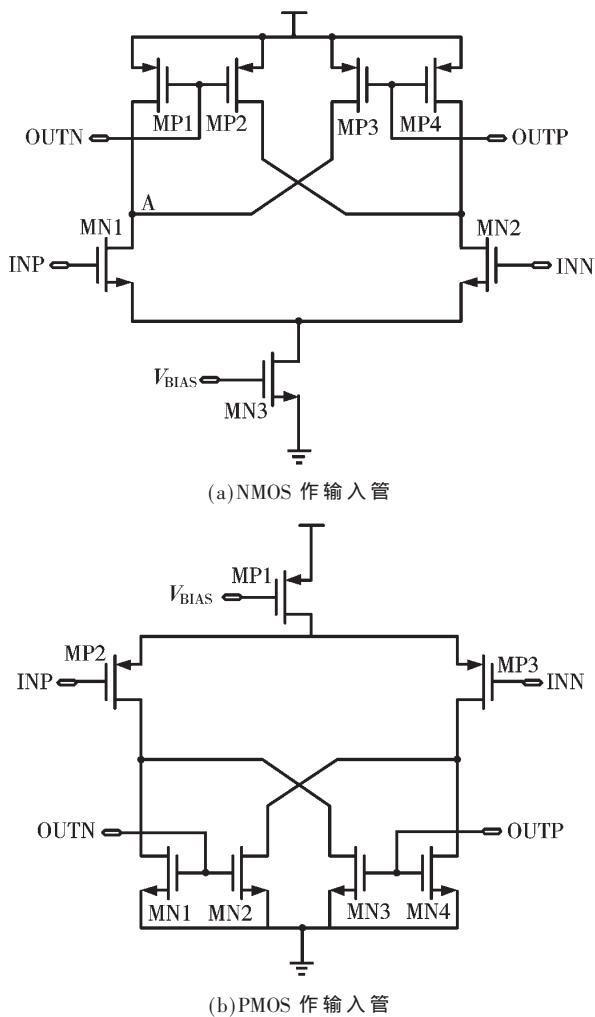

模拟电路常见的结构中, 迟滞比较器可以实现模拟信号到数字信号的转换, 还可以降低电源噪声和外界干扰等因素对输出的影响, 使得电路可以在复杂的环境中使用<sup>[4]</sup>。传统内部正反馈迟滞比较器如图 1 所示。

以图 1(a)为例, 内部正反馈迟滞比较器基本的工作

\* 基金项目: 国家自然科学基金重大项目(62090012); 国家自然科学基金重点项目(62031016, 61831017);

四川省重点项目(2019YFG0498, 2020YFG0282, 2020YFG0452, 2020YFG0028)

图 1 传统内部正反馈迟滞比较器

原理为: 电路中有两条反馈通路, 第一条通路是 A 点信号由共源极接法的 MP1 反向放大回到 A 点, 属于串联电流负反馈; 第二条通路是 A 点信号由 MP2、MP3 两级放大回到 A 点, 属于并联电压正反馈。设计时要保证正反馈系数大于负反馈系数, 电路整体保持正反馈, 这样电压传输曲线就会呈现出迟滞的特性<sup>[5]</sup>。

如图 1(a)所示的使用 NMOS 作为输入管的迟滞比较器, 使 MN1 处在饱和区有:

$$V_{GS\_MN1} = V_{IN, CM} - V_{OV\_MN3} \geq V_{THN} \quad (1)$$

$$V_{DS\_MN1} \geq V_{GS\_MN1} - V_{THN} \quad (2)$$

得到输入共模范围为:

$$V_{THN} + V_{OV\_MN3} \leq V_{IN} \leq V_{DD} - V_{OV\_MP3} + V_{THN} \quad (3)$$

由式(3)可知, 输入电压最低为一个 NMOS 过驱动电压和一个阈值电压, 约为 0.9 V。宽长比设置合理的话, 输入共模范围最高可高于  $V_{DD}$ 。

但是即使使用 PMOS 作为输入管, 如图 1(b)所示, 输入共模范围为:

$$V_{OV\_MN3} - |V_{THP}| \leq V_{IN} \leq V_{DD} - V_{OV\_MP3} - |V_{THP}| \quad (4)$$

由式(4)可知, 输入电平最低可以是负电压。

文献[6, 7]同时使用 NMOS 和 PMOS 作为输入管, 当 NMOS 输入管截止的时候, PMOS 输入管还可以工作, 同理 PMOS 输入管截止的时候, NMOS 输入管还可以工作。这样可以使比较器获得轨到轨的输入共模范围。

但是以上结构仍然不能处理超过电源范围的电压, 因此本文采取的方法是将 -12~12 V 先转化为 0~5 V 的电压, 再进行比较。

## 2 本文提出的比较器结构

### 2.1 比较器整体架构

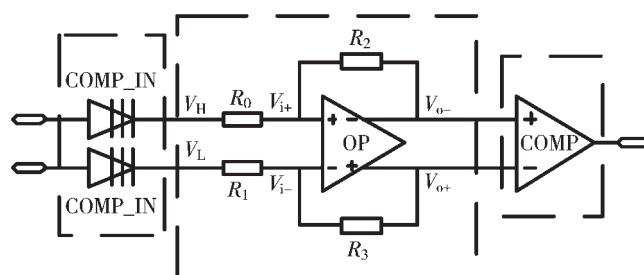

本文提出的比较器结构共分为三部分, 如图 2 所示。先是利用电阻将输入的差分电压和电源电压线性叠加, 得到 -0.4~4.4 V 的电压; 第二级利用全差分运放钳位, 稳定电压, 这样就实现差模输入到共模输出的线性转换; 有  $R_0=R_1=R_2=R_3$ , 理想运放虚断, 应用基尔霍夫电流定律可以得到:

$$\frac{V_{i1} - V_{i+}}{R} = \frac{V_{i+} - V_{o-}}{R} \quad (5)$$

$$\frac{V_L - V_{i-}}{R} = \frac{V_{i-} - V_{o+}}{R} \quad (6)$$

因而稳定后的输出电压为:

$$V_{o+} = 2V_{i+} - V_L \quad (7)$$

$$V_{o-} = 2V_{i-} - V_H \quad (8)$$

又根据运放虚短的特性,  $V_{i+} = V_{i-}$ , 因此:

$$V_{ID} = V_{o+} - V_{o-} = V_H - V_L \quad (9)$$

从上式可知: 差分信号  $V_{ID}$  并没有变化, 只是承载的电平变大, 可以增强差分信号对外界干扰的抵抗能力, 变得更加稳定<sup>[8]</sup>。

最后一级是对尾电流进行温度补偿的迟滞比较器, 比较得出数字信号。

图 2 本文提出的比较器的整体架构图

### 2.2 电平线性转化

第一个模块实现的功能是将总线上的差分信号从 -12~12 V 的电平转化到 0~5 V 这一后级电路可以处理的电平范围内。

如图 3 所示, 采用电阻分压的方法将电源电压和输入信号进行线性叠加得到 -0.4~4.4 V 的电压。在图 1 中, 将其他部分电路视为一个负载, 加上后级负载, 这个电压可能会有微小的变化, 但是负载变化对  $V_H$  和  $V_L$  影响一样, 差分信号  $V_H - V_L$  基本消除了负载的影响。

图 3  $V_{IN}$  线性转化

设计有  $R_0=R_2$ ,  $R_1=2R_0$ , 利用叠加定理计算, 可以得到如下结果。

令  $V_{IN}=0$ , 有:

$$V_{OUT1} = \frac{R_0}{R_1||R_2} V_{DD} = \frac{2}{5} V_{DD} = 2 \text{ V} \quad (10)$$

令  $V_{DD}=0$ , 有:

$$V_{OUT2} = \frac{1}{5} V_{IN} = -2.4 \sim 2.4 \text{ V} \quad (11)$$

所以得出:

$$V_{OUT} = V_{OUT1} + V_{OUT2} = -0.4 \sim 4.4 \text{ V} \quad (12)$$

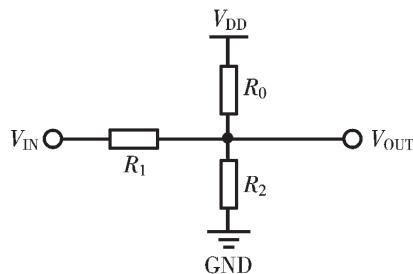

### 2.3 运放以及偏置电路

全差分运放相比单端输出的运放, 具有输出摆幅大、共模抑制比好、能够有效抑制偶次谐波的优点<sup>[9]</sup>; 再加上运放需要高增益以保证高精度, 因此本文设计的运放为采用密勒补偿的全差分两级运放。第一级为电流源做负载的差分输入级, 采用 PMOS 作为输入管。而使用电流源做负载可以提高电路的 PSRR, 同时可以提高增益<sup>[10]</sup>。只考虑沟道长度调制效应, 且为简便计算, 将 NMOS 和 PMOS 输出阻抗简化为  $r_{ON}$  和  $r_{OP}$ , 输入级增益为:

$$A_{V1} = g_{mp}(r_{ON}||r_{OP}) \quad (13)$$

第二级为电流源做负载的共源极, 进一步增大了增益, 第二级增益为:

$$A_{V2} = g_{mn}(r_{ON}||r_{OP}) \quad (14)$$

运放总的直流增益为:

$$A_{V\_ALL} = g_{mp}g_{mn}(r_{ON}||r_{OP})^2 \quad (15)$$

为解决两级运放的稳定性问题, 引入密勒补偿。密勒补偿不仅降低了所需的电容值, 还带来了“极点分裂”效应, 就是使两级间的极点向原点移动, 使输出极点向远离原点的方向移动, 提高了运放的相位裕度<sup>[11]</sup>。

全差分运放的共模输出电压不能通过差分信号的负反馈来控制, 因此需要设计共模反馈电路保证共模点钳位在电源电压的一半即 2.5 V。因为在高增益运算放大器中, 顶部和底部电流源存在的随机失配会导致共模电平显著的变化, 这种现象可能会导致运放的失效, 因而需要采用共模反馈技术稳定运放的共模点<sup>[12]</sup>。先采用电阻分压的方法得到电源电压的一半即 2.5 V 的参考电压, 再用电阻分压的方法得到运放输出共模电压和参考电压进行比较, 输出共模点大于 2.5 V, MP16 所在支路电流减小, 将二极管接法的 MN8 视为恒定负载, 负载上的压降减小, A 点电压减小, 所以电流源 MN4、MN5 栅压下降, 各自电流减小, 等效阻抗  $r_{ON}$  增大, B 点电压增加, 因为共源极增益为负, OUTP 和 OUTN 电压减小。输出共模点小于 2.5 V 的情况类似。这样就实现了通过共模反馈调节输出的共模电平, 保证运放工作在线性区域<sup>[13]</sup>。

$K$  为 MN2 与 MN1 宽长之比,  $(W/L)_N$  是 MN1 的宽长比, 与电源无关的偏置电流为:

$$I_{REF} = \frac{2}{\mu_n C_{OX} (W/L)_N} \frac{1}{R_0^2} \left(1 - \frac{1}{\sqrt{K}}\right)^2 \quad (16)$$

启动电路可以使偏置电路摆脱零偏置点, 进入正常工作状态<sup>[14]</sup>。本文的启动电路的工作原理是: 电路未上电时, MP3 未开启, X 点为 0, MP4 开启, 慢慢拉高 Y 点电位, MN1、MN2 开启, 拉高了 Z 点电位, 从而开启了 MP1、MP2, 进一步开启了 MP3, MP5~MP8 为二级管接法, 因此

图 4 本文采用运放的结构

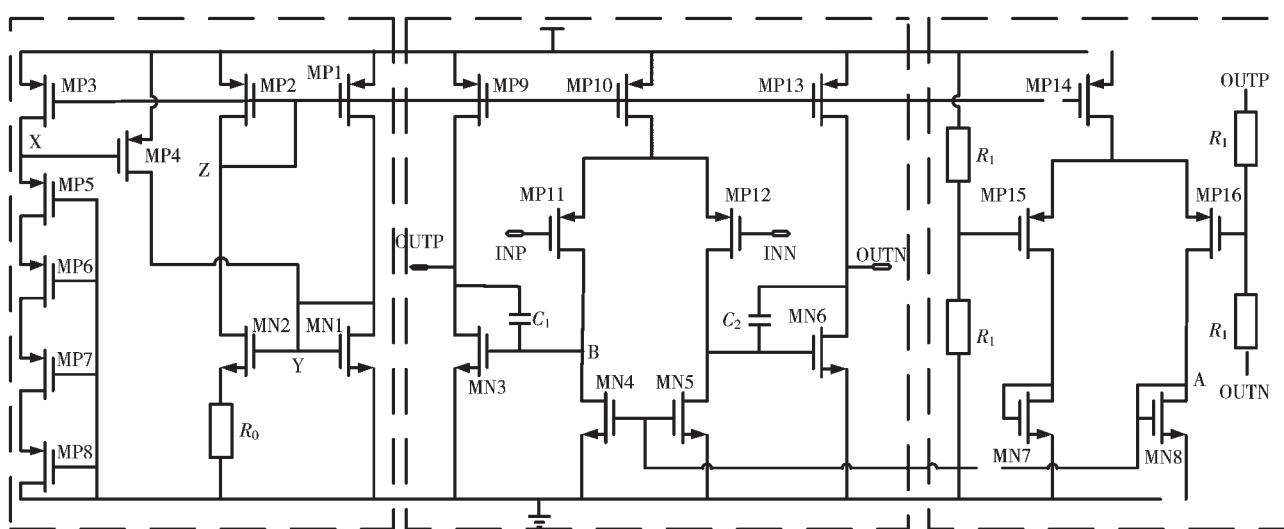

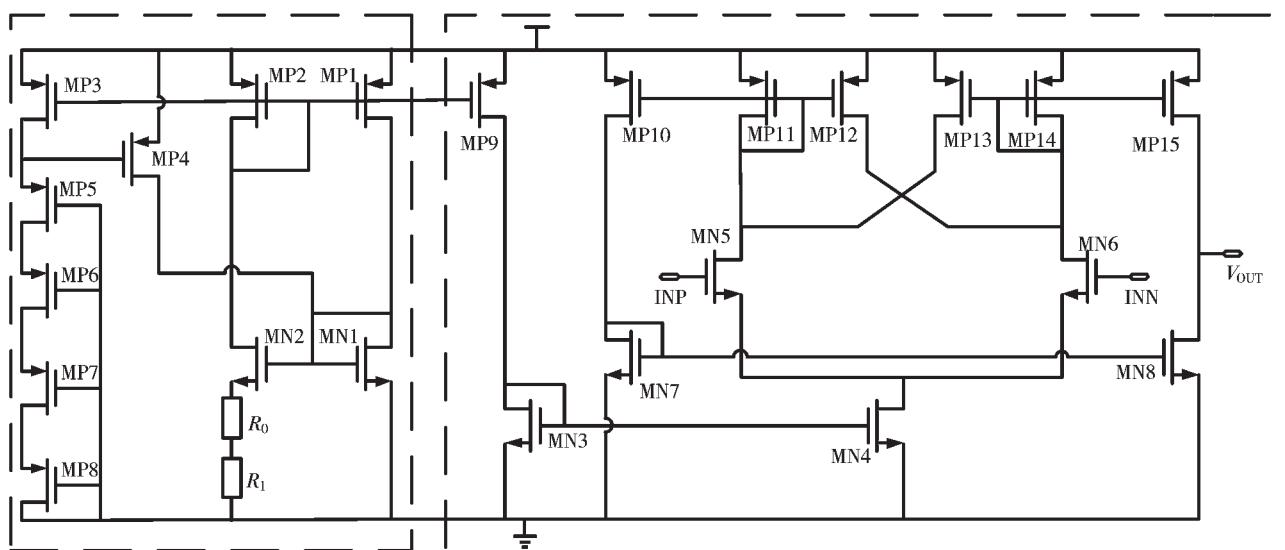

图 5 本文采用迟滞比较器的结构

X 点电位慢慢地拉高, 将 MP4 关断, 实现了降低功耗的目的。

#### 2.4 简单温度补偿的迟滞比较器

如图 5 所示, 本文采用的迟滞比较器为两级, 第一级和图 1(a)所示输入级一样, 使得电路整体呈现正反馈, 第二级为电流源做负载的共源极放大电路的输出级, 提供合理的输出摆幅和输出阻抗。偏置电路和运放中的类似, 区别在于做了简单的温度补偿, 采用  $R_0$ 、 $R_1$  两个温度系数相反的电阻, 减小了温度对偏置电流的影响, 使得迟滞比较器中 MN4 提供的尾电流受温度变化影响较小, 从而补偿了比较器的迟滞范围。

### 3 仿真结果及分析

基于 VIS 0.4  $\mu\text{m}$  BCD 工艺, 使用 Hspice 对电路性能进行了仿真验证。

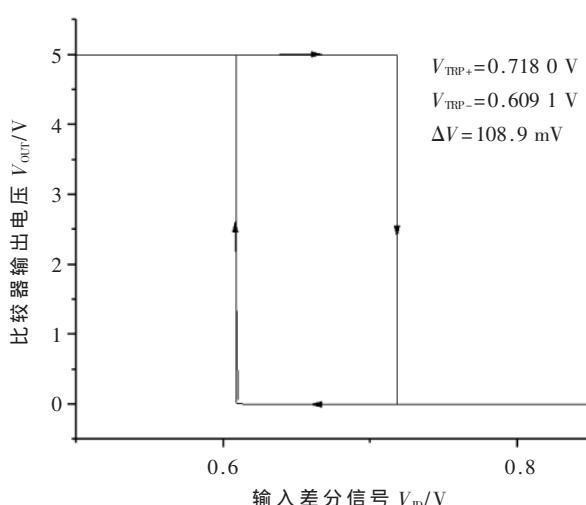

为了检验电路迟滞特性, 首先通过直流仿真查看常温(即 25  $^{\circ}\text{C}$ ), TT 工艺角下的迟滞曲线, 如图 6 所示, 测

量翻转阈值电压, 可计算得到迟滞门限电压为 108.9 mV。

在电源电压 5 V, 温度为 25  $^{\circ}\text{C}$  下, 进行瞬态仿真, 表 1 展示了输入输出电压, 说明本文所设计的比较器正确地将差分信号转化为数字信号。

表 1 比较器逻辑功能仿真结果

| 同相输入<br>$V_{\text{CANH}}/\text{V}$ | 反相输入<br>$V_{\text{CANL}}/\text{V}$ | 输入差分信号<br>$V_{\text{ID}}/\text{V}$ | 输出逻辑 R |

|------------------------------------|------------------------------------|------------------------------------|--------|

| -11.1                              | -12                                | 0.9                                | 0      |

| 12                                 | 11.1                               | 0.9                                | 0      |

| 6                                  | -12                                | 6                                  | 0      |

| 12                                 | 6                                  | 6                                  | 0      |

| -11.5                              | -12                                | 0.5                                | 1      |

| 12                                 | 11.5                               | 0.5                                | 1      |

| -12                                | -6                                 | -6                                 | 1      |

| 6                                  | 12                                 | -6                                 | 1      |

图 6 本文设计的比较器的迟滞特性曲线

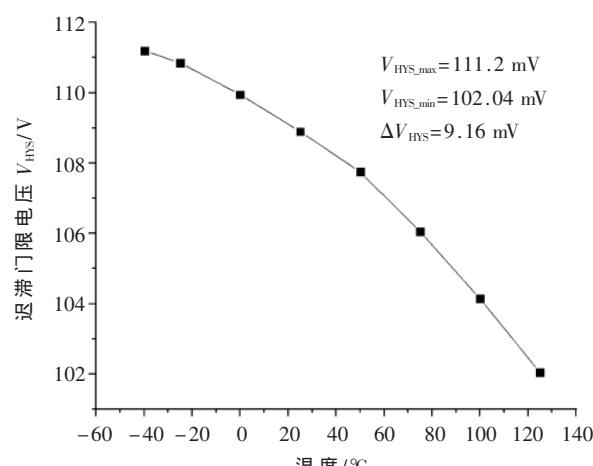

TT 工艺角下, 直流仿真  $-40\text{ }^{\circ}\text{C}$ ~ $125\text{ }^{\circ}\text{C}$  内多个温度节点下的迟滞电压, 拟合得到如图 7 所示的曲线。

图 7 迟滞门限电压随温度的变化

文献[15]设计的迟滞比较器的迟滞电压在0~85℃范围内温度系数为0.11 mV/℃。本文设计的迟滞比较器的迟滞门限电压在-40℃~125℃范围内的变化最大为9.16 mV,温度系数为0.055 5 mV/℃。说明本文对迟滞比较器尾电流的温度补偿有效。

#### 4 结论

本文提出了一款宽输入范围的全差分迟滞比较器。通过仿真验证,电路能够将-12~12 V范围内的差分输入信号准确地转化为数字信号。迟滞门限电压温度系数为0.055 5 mV/℃,满足工业级应用。下一步将研究减小器件失配对迟滞门限电压的影响。

#### 参考文献

- [1] 徐深,牛洪海,陈俊,等.CAN总线数据发送优化方法研究及应用[J].自动化仪表,2020,41(11):101~104,110.

- [2] 杨力宏,张乐玉,姚和平,等.一款基于BCD工艺的低EMI、高可靠CAN总线收发器的设计[J].空间电子技术,2019,16(1):70~74.

- [3] THUN M V, DAVID B, DAVID W, et al. SEL and TID test results of a hardened CAN transceiver[C]. Radiation Effects Data Workshop, 2017.

- [4] 张书磊,莫太山,叶甜春.跨阻放大器自动静噪电路的设计与实现[J].电子技术应用,2013,39(6):46~48,52.

- [5] 郭晓锋,成俊,江喜平,等.一种新颖的低阈值迟滞比较器的设计及应用[J].中国集成电路,2017,26(6):16~19,53.

- [6] CHU W S, CURRENT K W. A CMOS voltage comparator with rail-to-rail input-range[J]. Analog Integrated Circuits and Signal Processing, 1999, 19(2): 145~149.

- [7] 贺莎,邹望辉.一种集成轨到轨比较器电路设计[J].电子测试,2020(7):35~36,106.

- [8] 李帅三.CMOS全差分放大器的研究与设计[D].哈尔滨:黑龙江大学,2015.

- [9] 张镇,王雪原,冯奕.一种高速高精度AB类全差分运算放大器的设计[J].电子与封装,2019,19(4):19~23.

- [10] SANSEN M C. 模拟集成电路设计精粹[M].北京:清华大学出版社,2008.

- [11] 拉扎维.模拟CMOS集成电路设计[M].西安:西安交通大学出版社,2002.

- [12] 郑凯伦,郭桂良.一种高跨导增益高线性度的共模反馈电路[J].微电子学与计算机,2020,37(7):31~35.

- [13] 蔡坤明,何杞鑫,陶吉利,等.一种增益增强型套筒式运算放大器的设计[J].电子技术应用,2010,36(5):66~69.

- [14] 张龙,冯全源,王丹.一种带曲率补偿的低功耗带隙基准源设计[J].电子元件与材料,2014,33(9):58~61.

- [15] 薛鹏飞,朱江,乔明.一种滞回比较器设计[J].电子与封装,2015,15(3):26~28,43.

(收稿日期:2020-12-27)

#### 作者简介:

冯世勤(1998-),男,硕士研究生,主要研究方向:模拟集成电路设计。

冯全源(1963-),通信作者,男,博士,教授,主要研究方向:集成电路、RFID技术等,E-mail:fengquanyuan@163.com。

扫码下载电子文档

(上接第51页)

- 滤波器[J].上海大学学报(自然科学版),2014,20(4):466~471.

- 关雪芹,刘太君,赵辉,等.宽阻带SIW滤波器设计[J].无线通信技术,2020,29(1):21~25,31.

- 杨雪霞.微波技术基础[M].北京:清华大学出版社,2015.

- 汪洋,郭瑜,余超,等.毫米波双通带基片集成波导滤波器设计[J].微波学报,2020,36(2):23~27.

- 滕鑫,陈继新.加载缺陷地结构的SIW宽阻带带通滤波器设计[C].中国电子学会.2019年全国微波毫米波会议论文集(下册),2019.

- 黄强,童元伟.基于SCMRC结构的慢波半模基片集成波导带通滤波器[J].电子元件与材料,2020,39(9):72~77.

- 张国鹏,黄玉兰.基于CSRR-QMSIW谐振器的双通带滤波器的设计[J].压电与声光,2019,41(4):469~472.

- 翟琼华.硅基MEMS微波带通滤波器的设计及制备[D].太原:中北大学,2016.

- CHEN X P, WU K, LI Z L. Dual-band and triple-band substrate integrated waveguide filters with chebyshev and quasi-elliptic responses[J]. IEEE Transactions on Micro-

wave Theory & Techniques, 2007, 55(12): 2569~2578.

- CHEN B J, SHEN T M, WU R B. Dual-band vertically stacked laminated waveguide filter design in LTCC technology[J]. IEEE Transactions on Microwave Theory & Techniques, 2009, 57(6): 1554~1562.

- REZAEE M, ATTARI A R. A novel dual mode dual band SIW filter[C]. Microwave Conference. IEEE, 2014.

- AZAD A R, MOHAN A. Substrate integrated waveguide dual-band and wide-stopband bandpass filters[J]. Microwave & Wireless Components Letters IEEE, 2018, 28(8): 660~662.

(收稿日期:2021-01-29)

#### 作者简介:

濮泽宇(1995-),男,硕士研究生,主要研究方向:毫米波滤波器。

万晶(1986-),女,硕士,助理研究员,主要研究方向:微波毫米波集成电路。

梁晓新(1979-),通信作者,女,博士,研究员,主要研究方向:微波毫米波集成电路,E-mail:liangxiaoxin@ime.ac.cn。

扫码下载电子文档

## 版权声明

经作者授权，本论文版权和信息网络传播权归属于《电子技术应用》杂志，凡未经本刊书面同意任何机构、组织和个人不得擅自复印、汇编、翻译和进行信息网络传播。未经本刊书面同意，禁止一切互联网论文资源平台非法上传、收录本论文。

截至目前，本论文已经授权被中国期刊全文数据库（CNKI）、万方数据知识服务平台、中文科技期刊数据库（维普网）、DOAJ、美国《乌利希期刊指南》、JST 日本科技技术振兴机构数据库等数据库全文收录。

对于违反上述禁止行为并违法使用本论文的机构、组织和个人，本刊将采取一切必要法律行动来维护正当权益。

特此声明！

《电子技术应用》编辑部

中国电子信息产业集团有限公司第六研究所