# 基于信号与电源完整性的有效分析优化 2.5D–3D 的设计

何永松<sup>1</sup>, 秦祖立<sup>2</sup>, 林 麟<sup>1</sup>, 吴 凯<sup>1</sup>

(1. 上海燧原科技有限公司, 上海 200000; 2. 上海铿腾电子科技有限公司, 上海 200000)

**摘要:** HBM(高带宽内存)存储系统与传统的 DRAM 接口相比, 具有高速率和低功耗特性。在 2.5D/3D 的设计中, 随着 HBM 速率的提高, 对信号与电源完整性的设计的考量越来越重要, 如何通过有效的仿真指导产品的设计是一个挑战。首先从信号完整性的角度讨论了设计的考量点, 其次从电源完整性的角度讨论电源噪声在高速传输信号中的影响, 并提出了如何仿真与预测大量同步开关噪声等电源噪声对眼图的影响, 最后基于芯片的测试结果对比仿真, 给出结论。

**关键词:** 2.5D/3D 设计; 信号完整性; 电源完整性; 同步开关噪声; 电源噪声预测

中图分类号: TN402

文献标识码: A

DOI: 10.16157/j.issn.0258-7998.219806

中文引用格式: 何永松, 秦祖立, 林麟, 等. 基于信号与电源完整性的有效分析优化 2.5D–3D 的设计[J]. 电子技术应用, 2021, 47(8): 64–67, 71.

英文引用格式: He Yongsong, Qin Zuli, Lin Lin, et al. Optimizing 2.5D/3D IC design with efficient power and signal integrity analysis[J]. Application of Electronic Technique, 2021, 47(8): 64–67, 71.

## Optimizing 2.5D/3D IC design with efficient power and signal integrity analysis

He Yongsong<sup>1</sup>, Qin Zuli<sup>2</sup>, Lin Lin<sup>1</sup>, Wu Kai<sup>1</sup>

(1. Shanghai Enflame Technology, Shanghai 200000, China; 2. Cadence Shanghai, Shanghai 200000, China)

**Abstract:** Compared with the traditional DRAM interface, the HBM(High Bandwidth Memory) storage system has the characteristics of high speed and low power consumption. In the design of 2.5D/3D, as the rate of HBM increases, the design considerations of signal and power integrity are becoming more and more important. How to guide the design of products through effective simulation is a challenge. The article firstly discusses design considerations from the perspective of signal integrity, then discusses the impact of power supply noise on high-speed transmission signals from the perspective of power integrity and proposes how to simulate and predict the effects of Simultaneous Switch noises. Finally based on the silicon chip, simulations have well correlated and verified by test results.

**Key words:** 2.5D/3D design; signal integrity; power integrity; SSN; voltage noise prediction

## 0 引言

高带宽内存(High Bandwidth Memory, HBM)存储系统已成为某些超级计算机中用于高性能图形加速、网络设备以及高性能数据中心的最广泛使用的存储器件。与传统的存储器接口相比, HBM 可实现更高的带宽, 同时消耗更少的功耗。HBM 广泛应用于高级封装中, 结合中介层基板芯片(Interposer), 实现存储器的数据读写。而 Interposer 的设计随着 HBM 的速率上升, 信号完整性(SI)和电源完整性(PI)带来的挑战越来越大。Interposer 的设计人员在初始设计时, 为了克服 SI 和 PI 的挑战, 需要有效的仿真方法学指导设计。本文从 SI 和 PI 角度讨论如何设计仿真, 并通过实测芯片验证仿真方法学的可靠性。

### 1 高速 HBM 系统信道设计的挑战

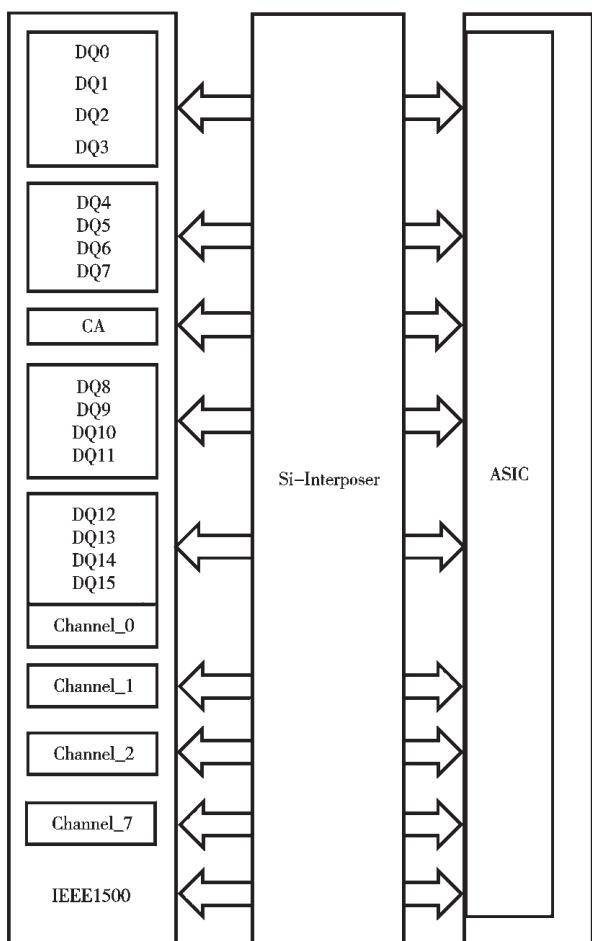

图 1 所示为典型的 2.5D 通信系统, HBM 和专用集

成电路(ASIC)通过中介层芯片进行数据通信, HBM 单个模块包含了 8 个独立的数字通道, 每一个通道包含了 32 根关键数据信号线, 全部通道共包含 1 024 根数据信号线, 同时包含了地址、时钟等信号, 总信号超过 1 700 根。目前 HBM 的信号传输速率由 HBM2 的 2.0 GHz~2.4 GHz 上升到 HBM3 的 7.2 GHz。信号经过 Interposer 通道, 将会遇到以下干扰因素: 信号串扰、码间干扰、信号插损、信号回损、电源噪声等等。

设计人员在设计之初需要充分考虑并利用仿真指导优化, 以达到上述信号干扰因素的排除或降低影响。

### 2 基于信号完整性的优化与仿真

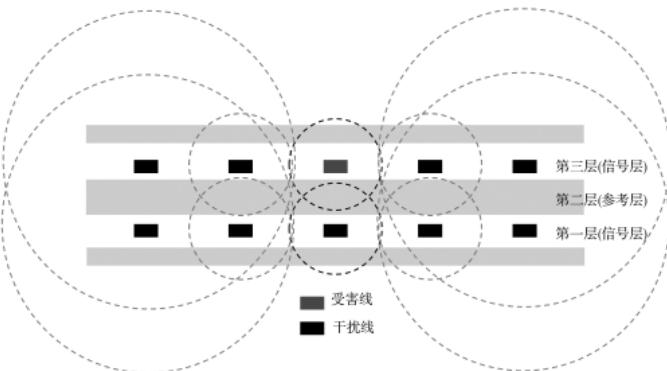

信号通道模型如图 2 所示。

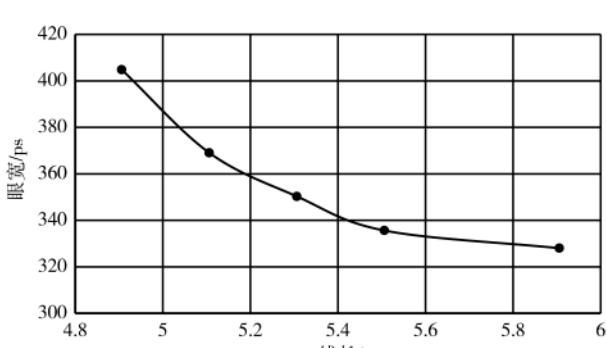

信号层置于第一层与第三层, 而第二层是屏蔽地层。基于此模型, 首先仿真了线长 S 对于信号眼宽的影响, 如图 3 所示。

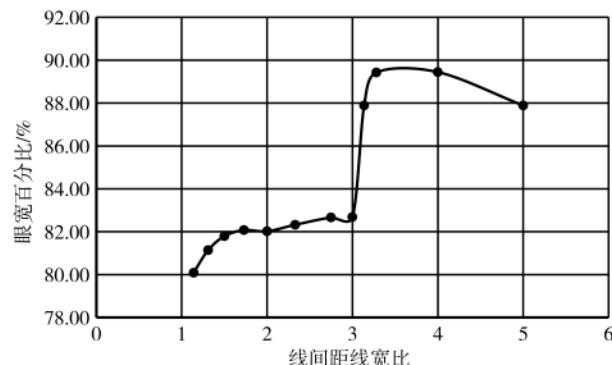

图 3 表明，当信号线物理线长增加，插入损耗(insertion loss)值变大时，在布局 HBM 与 ASIC 在 Interposer 上的位置关系时，需要尽可能降低两者的位置，以确保信号的插损合理可控。除了线长的考虑，还需要考虑线宽与间距的影响。根据实际的 HBM 凸点焊球(Bump)的分布得知，预留给 HBM 单独通道的物理高度是一定的，这时候需要通过仿真确定线间距与线宽比。

从图 4 得知，当线间距与线宽的比值达到 3 时，眼宽将会有大的提升，大概有 8% 的眼宽改善，在影响眼宽的因素中，串扰在 3 倍间距后影响会大幅减弱，因此对于速率越来越高的 HBM 系统，需要充分考虑线间距串扰的影响。除上述因素之外，对设计布局布线的重要 SI 考量因素还包括电源和地网络的完备以及硅工艺的特性：包括金属层和过孔层的厚度、介电层的厚度与介电参数等。

### 3 基于电源完整性的设计优化与仿真

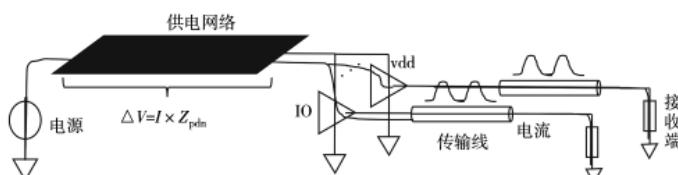

电源网络的供电可靠性对于 HBM 系统通信是十分重要的考量。当信号从一端经中介层信道发送到接收端时，电源网络会有自身的噪声，对信号传输会有干扰，设计人员在针对自己的产品进行设计，需要充分验证传输通道中的电源噪声的影响，除了电源网络的阻抗指标，对信道的同步开关噪声(SSN)等进行充分验证是十分重要的一步。电源网络供电示意图如图 5 所示。

和传统的存储器件相比，超过 1 024 根关键信号线会同时翻转，当信号线上的翻转电流经过供电网络时，经由网络的阻抗会产生波动电压，即为同步开关翻转噪声，对于这种噪声的仿真，目前仿真工具能力的极限无法应对大量传输线的场景。需要新的仿真方法来替

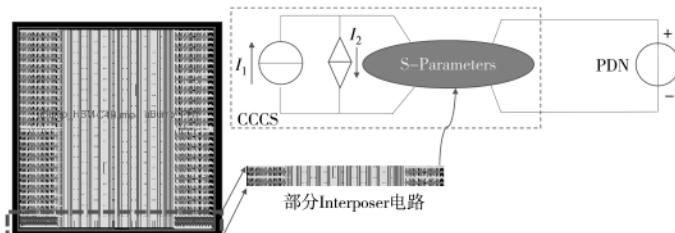

代和覆盖。在此提出倍流流控恒流源方法学(Multiple Current With Current Controlled Current Source,CCCS Method)。图 6 展示了 CCCS 方案的示意结构图。

图 6 CCCS 方法主要方案示意图

首先,将整个 HBM 通信模块进行局部的 S 参数提取,这部分的电路包含了完整的信号与电源地的组成,其余部分可以视为这部分的复制。其次在使用软件仿真设置时,将这部分的 Spice 电路引入流控电流源模块,将电流节点放大到目标倍数。这样就可以用局部准确、全局倍流的方式对电源供电网络(PDN)和全局信号网络进行电源噪声包括同步翻转噪声的预测。

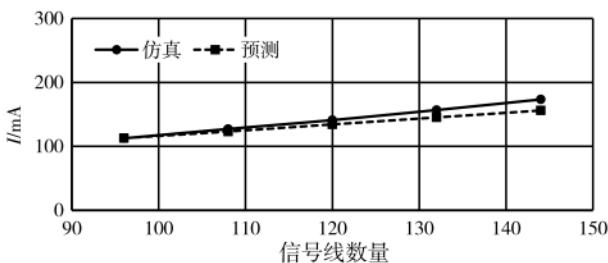

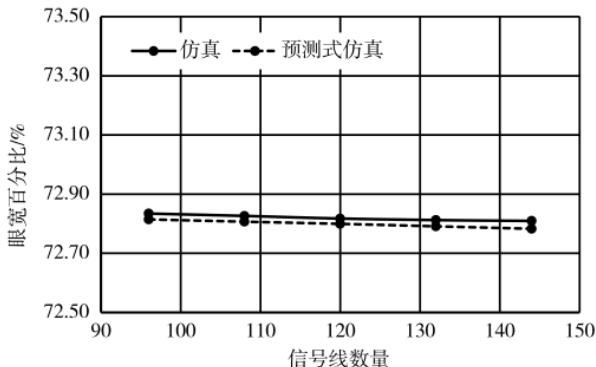

为了验证上述方案的准确性与可靠性,在工具可仿真的范围内做了全仿真与预测式仿真的对比。对比内容包括了电流与眼宽。这里仿真线的数目分别是 96、108、120、132、144。而基于 12 根线的基础,应用了 CCCS 预测式仿真方法,预测了同样数目信号线对应的五组实验。分别得到电流与眼图的对比结果如图 7、图 8 所示。

图 7 CCCS 方案仿真电流与预测电流的比较

图 8 CCCS 方案仿真眼宽与预测眼宽的比较

图 7 和图 8 的仿真结果表明在应用了 CCCS 预测式仿真方法可靠地将电流倍数到目标数量,并且与全仿真

的结果接近,线性度好。同时也观察到一个现象,当预测式仿真的信号线数量越大,与全仿真的结果误差越小。实验中,预测式仿真基数为 12 根线,仿真条件为常温下 PRBS 码,提取参数的工具用到了 Cadence 的 XcitePI 和 Clarity(3D),电流及眼图仿真工具为 Cadence 的 SystemSI。至此验证了 CCCS 预测式仿真的准确性与可靠性。

#### 4 基于 CCCS 的仿真与实验室实测数据的对比

前述已经阐明了 CCCS 仿真方法,可以有效地将局部电源噪声预测到全局的电源噪声,包含 SSN 的影响。这里,基于工具的仿真能力将基于 144 根线的全仿真去预测全局超过 1700 根线的噪声。表 1 为选取的 144 根线预测式仿真的电流与眼宽的数据趋势。

表 1 基于 144 根信号线的 CCCS 预测式仿真

| 信号数量   | 预测电流 / mA | 眼宽百分比 / % |

|--------|-----------|-----------|

| 144    | 173.307   | 72.81     |

| 400    | 646.423   | 72.71     |

| 800    | 1085.9    | 72.06     |

| 1 200  | 1 490.57  | 71.43     |

| 1 700+ | 1 982.52  | 70.56     |

在相同的仿真环境下,基于 144 根线的全仿真进行了预测式的 4 组实验,使用的码型为 PRBS,可见的是电流的线性增加及眼宽占比的线性下降。预测式的仿真结果表明,基于现有的设计,当同时翻转超过 1700 根信号线时,常温下将会有大约 2.2% 的眼宽的损失。基于相同的仿真环境,选取和搭建了测试平台,见图 9,在此平台上做了信号通道眼宽的扫描。

图 9 实验室测试平台

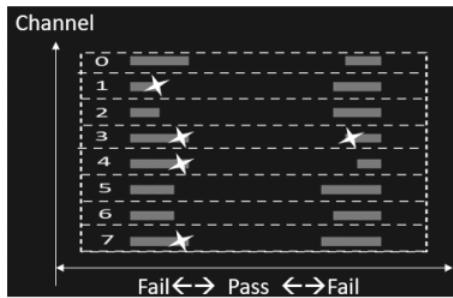

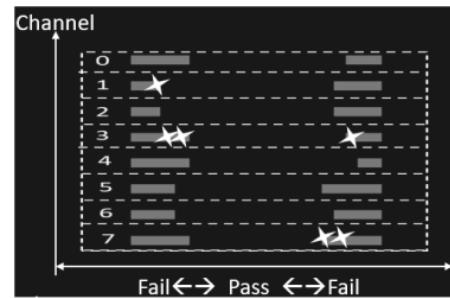

在芯片的通道扫描中设置了两组码型 PRBS 和 1010,在这两种码型下,分别单独启动 HBM 模块的 1 到 8 个通道(Channel)进行眼宽扫描,得到了图 10 和图 11 的扫描结果。

扫描过程中,除去时钟命令和地址信号,同时翻转的关键信号为 DQ/DQS/DQSN/DBI/DM/PAR 等,全通道

图 10 HBM 模块 8 通道启动眼宽损失分布(PRBS 码)

大约 1 280 根,从图 10 和图 11 的扫描结果,可以看到单个通道随着全通道的启动,受到了不同的影响。其中 PRBS 码测试下,通道 3 受到了 2 个眼宽单位的损失,这里,每个单位实验室设定为 0.78% 眼宽。可以看出,PRBS 下通道 3 最大损失了 1.56% 眼宽,1010 码型下通道 3 损失了 2.34% 眼宽。

5 结论

本文讨论了在 2.5D 和 3D 封装形式下, 基于信号完整性与电源完整性的考量, 介绍了如何仿真优化 HBM 系统高速信号通道的设计, 特别提出了 CCCS 预测式电源噪声的仿真方法, 进行了全仿与预测仿的对比, 并与实验室芯片实测数据进行对比, 验证了仿真数据的合理性和一致性。

参考文献

- [1] Shi Wenjun, Zhou Yaping, SUDHAKARAN S.Power delivery

(上接第 63 页)

表 5 数据传递评估结果

| N5<br>project<br>评估类型 | 传统<br>Sub-flow                        | virtuoso<br>所需<br>时间 | flow                                               | Rapid<br>Sub-flow  | MSOA<br>所需<br>时间 | flow | 效率<br>提升 | 应用场景                  |

|-----------------------|---------------------------------------|----------------------|----------------------------------------------------|--------------------|------------------|------|----------|-----------------------|

| 模拟-><br>数字            | Virtuoso<br>LEF/DEF<br>文件输出           | 2 天                  | Innovus<br>restore &<br>Innovus<br>LEF/DEF<br>文件输出 | Innovus OA<br>1 小时 | >90 %            |      |          |                       |

| 数字-><br>模拟            | Virtuoso<br>GDS<br>stream<br>in & out | 2~4<br>小时            | Innovus<br>OA save<br>& Virtuoso<br>open           | <8 分钟              | >93 %            |      |          | 大<br>部<br>分<br>场<br>景 |

#### 5.4 power mesh 和 routing

对于 power mesh 和重复性的 routing 脚本, MSOA 使用有着一定的局限性, 在前几个评估的 case 中可见, 对于大尺寸、绕线要求低、但绕线多的情况下, MSOA 对 design 速率有很大提升, 但如果设计定制化要求高, Virtuoso 和 Innovus 所需要的时间会比较接近, MSOA flow 对于这种情况下只是向 designer 多提供了一种选择方式, 具体如

图 11 HBM 模块 8 通道启动眼宽损失分布(1010 码)

network design and modeling for high bandwidth memory (HBM)[C]//2016 IEEE 25th Conference on Electrical Performance of Electronic Packaging and Systems(EPEPS),2016: 3–6.

- [2] CHO J, KIM H, FAN J, et al. Investigation of statistical eye-diagram estimation method for HBM including ISI, X-talk, and power noise[C]//2017 IEEE International Symposium on Electromagnetic Compatibility & Signal/Power Integrity(EMCSI), 2017: 411–415.

- [3] THOMAS H, NA N, WONG A, et al. Top-Down jitter specification approach for HBM system optimization[C]//Design Con 2019, 2019.

- [4] 李玉山.信号完整性与电源完整性分析(第二版)[M].北京:电子工业出版社, 2015.

(下转第 71 页)

何使用由 designer 决定, Power mesh 也是同理。power mesh 和 routing 评估结果如表 6 所示。

表 6 power mesh 和 routing 评估结果

| N5                                                    | 传统 virtuoso flow                               | Rapid MSOA flow |                                              |            |

|-------------------------------------------------------|------------------------------------------------|-----------------|----------------------------------------------|------------|

| project<br>评估类型                                       | Sub-flow                                       | 所需<br>时间/h      | Sub-flow                                     | 所需<br>时间/h |

| Power mesh<br>or highly<br>repetitive<br>routing unit | Virtuoso Power<br>Planning/Group/<br>Skill/WSP | 2               | TCL script for<br>special nets<br>in Innovus | 2          |

参考文献

- [1] Cadence Design Systems , Inc.Mixed Signal(MS) interoperability guide[Z].2021.

- [2] Cadence Design Systems , Inc.Mixed Signal design challenges and cadence MSOA rapid flow overview[Z].2021.

作者简介

贺恺华(1989-),女,硕士,工程师,主要研究方向:数字后端、模拟后端

丁学伟(1982-),男,硕士,工程师,主要研究方向:模拟IP

扫码下载电子文档

## 版权声明

经作者授权，本论文版权和信息网络传播权归属于《电子技术应用》杂志，凡未经本刊书面同意任何机构、组织和个人不得擅自复印、汇编、翻译和进行信息网络传播。未经本刊书面同意，禁止一切互联网论文资源平台非法上传、收录本论文。

截至目前，本论文已经授权被中国期刊全文数据库（CNKI）、万方数据知识服务平台、中文科技期刊数据库（维普网）、DOAJ、美国《乌利希期刊指南》、JST 日本科技技术振兴机构数据库等数据库全文收录。

对于违反上述禁止行为并违法使用本论文的机构、组织和个人，本刊将采取一切必要法律行动来维护正当权益。

特此声明！

《电子技术应用》编辑部

中国电子信息产业集团有限公司第六研究所