# 一种带有 DAC 失配整形的高精度 Sigma-Delta 调制器 \*

刘铭扬<sup>1,2,3</sup>, 王小松<sup>1,2,3</sup>, 刘 昱<sup>1,2,3</sup>

(1.中国科学院微电子研究所,北京 100029; 2.中国科学院大学,北京 100049;

3.新一代通信射频芯片技术北京市重点实验室,北京 100029)

**摘要:**为减小生理信号采集应用中仪表放大器的设计难度,需在低功耗、小信号带宽的前提下大幅度提高模数转换单元的精度和动态范围以作补偿。为此,面向生理信号采集应用,实现了一种带前馈结构的高精度三阶五比特 Sigma-Delta 调制器,其不需要复杂的 OTA 结构和过高的过采样率,且功耗较低,并将二阶噪声整形动态元件匹配方案应用于 DAC 中,以避免多比特量化造成的非线性谐波失真。该 Sigma-Delta 调制器采用 SMIC 0.18 μm CMOS 标准工艺,在 1 MHz 的采样率,1 kHz 的信号带宽内,峰值 SNDR 达到 111 dB,动态范围达到 120 dB,有效位数达到 18 bit,工作电源电压为 1.8 V,整体功耗为 0.87 mW。

**关键词:**Sigma-Delta 调制器;多比特量化器;二阶动态元件匹配;逐次逼近;前馈结构

中图分类号: TN432

文献标识码: A

DOI:10.16157/j.issn.0258-7998.211398

中文引用格式: 刘铭扬,王小松,刘昱. 一种带有 DAC 失配整形的高精度 Sigma-Delta 调制器[J]. 电子技术应用, 2021, 47(9): 25–29, 38.

英文引用格式: Liu Mingyang, Wang Xiaosong, Liu Yu. A high precision multi-bit sigma-delta modulator with mismatch-shaping DACs[J]. Application of Electronic Technique, 2021, 47(9): 25–29, 38.

## A high precision multi-bit sigma-delta modulator with mismatch-shaping DACs

Liu Mingyang<sup>1,2,3</sup>, Wang Xiaosong<sup>1,2,3</sup>, Liu Yu<sup>1,2,3</sup>

(1. Institute of Microelectronics of Chinese Academy of Sciences, Beijing 100029, China;

2. University of Chinese Academy of Sciences, Beijing 100049, China;

3. Beijing Key Laboratory of Radio Frequency IC Technology for Next Generation Communications, Beijing 100029, China)

**Abstract:** In order to reduce the difficulty of designing the amplifier of the instrument in the application of physiological signal acquisition, a higher-precision analog-to-digital conversion unit is required. This paper implements a high-precision sigma-delta modulator with feedforward structure, which does not require complex OTA structure and high oversampling rate, and has low power consumption, and a second-order noise shaping dynamic component matching scheme used in DAC to avoid nonlinear harmonic distortion caused by multi-bit quantization. The sigma-delta modulator adopts SMIC 0.18 μm CMOS standard technology. At a sampling frequency of 1 MHz and a signal bandwidth of 1 kHz, the peak SNDR can reach 111 dB, the operating power supply voltage is 1.8 V, and the overall power consumption is 0.87 mW.

**Key words:** sigma-delta modulator; multi-bit quantizer; 2nd-order dynamic element matching; successive approximation; feed-forward

## 0 引言

由仪表放大器、抗混叠滤波器和模数转换器组成的模拟前端(Analog Front End, AFE)是可穿戴医疗设备中信息采集系统的重要组成部分<sup>[1]</sup>。实际信息采集过程中,外界环境中的非理想因素及皮肤与电极接触带来的可变动阻抗使仪表放大器得到的信号幅度变动极大,且存在很大的基线漂移<sup>[2]</sup>。面对这样一个频带窄、动态范围大的待处理信号,ADC 模块必须满足高动态范围、低失真的特性,以降低仪表放大器和后端数字处理单元的

设计难度,保证信号的采集质量。

相较于流水线型(Pipelined)、逐次逼近型(SAR)、全并行型(Flash)等奈奎斯特采样率型 ADC<sup>[3-4]</sup>,采用过采样技术和噪声整形技术的 Sigma-Delta 型 ADC 更容易满足上述低失真、低功耗、高精度的需求<sup>[3]</sup>。Silva 等人提出一种全前馈结构,前馈支路直接连接到量化器的输入端<sup>[4]</sup>,可以有效缩减积分器的输出摆幅,降低 OTA 的设计难度。

本文面向生理信号采集应用,对文献[4]中的全前馈结构进行了优化,设计了一种带前馈支路的三阶五比特高精度 Sigma-Delta 调制器,并引入二阶动态元件匹配

\* 基金项目: 科技部重点研发计划(2019YFB2204500)

算法,以解决多比特量化引入的电容阵列非线性问题。

## 1 Sigma-Delta 调制器的结构选择

对于一个  $n$  阶的 Sigma-Delta 调制器,若采用  $B$  位量化,其理想峰值信噪比可表示为:

$$\text{SNR}_{p,\text{ideal}} = \frac{(A_{\max}/\sqrt{2})^2}{P_e} = \frac{3\pi}{2} (2^B - 1)^2 (2n+1) \left(\frac{\text{OSR}}{\pi}\right)^{2n+1} \quad (1)$$

其中,过采样率  $\text{OSR} = f_s/2f_b$ 。根据式(1),提高量化器位数  $B$ 、环路阶数  $n$  和过采样率  $\text{OSR}$  皆可提高调制器的信噪比。但过度提高环路阶数  $n$ ,会造成环路不稳定,且会增加了 OTA 的设计难度。提高量化器位数,会引入多比特的 DAC 电容阵列,造成电路的非线性失真。过度提高 OSR,会大大增加调制器的功耗<sup>[5]</sup>。

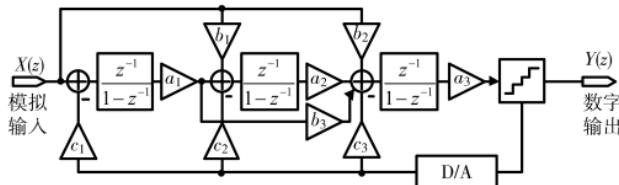

经折衷考量,本文的调制器采用图 1 所示的三阶五比特全前馈等效结构,  $\text{OSR}=64$ ,采样时钟为 1 MHz。

图 1 全前馈的 Sigma-delta 调制器的等效结构

令调制器的噪声传递函数达到理想的高通形式  $(1-z^{-1})^3$ ,推导调制器系数间的关系得:

$$\begin{cases} b_1 = \frac{a_1(3a_2 - b_3)}{a_2} \\ b_2 = 3a_1a_2 \end{cases} \quad (2)$$

$$\begin{cases} c_1 = \frac{1}{a_1 a_2 a_3} \\ c_2 = \frac{3a_2 - b_3}{a_2 a_3} \\ c_3 = \frac{3}{a_3} \end{cases} \quad (3)$$

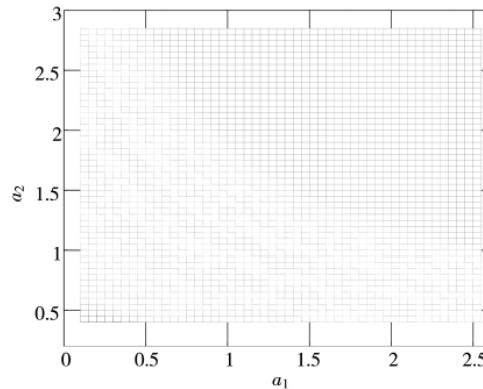

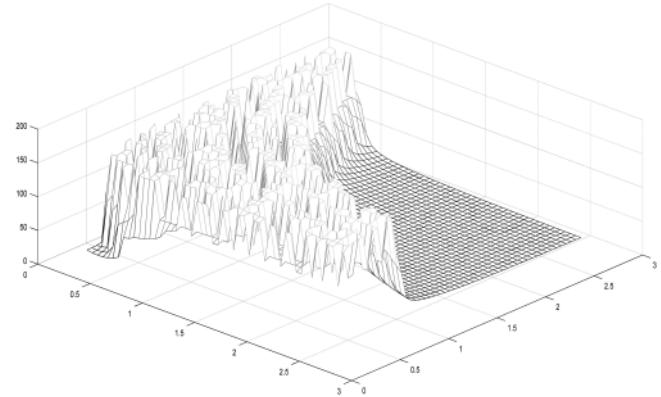

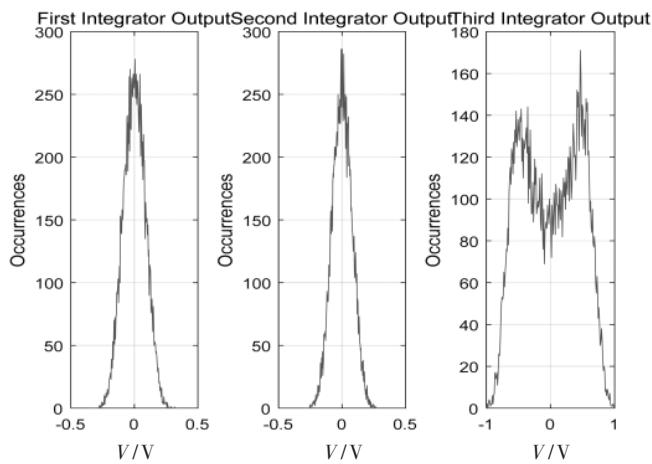

选取  $a_3=0.6$ 、 $b_3=1$ ,在  $[0.1, 2.55]$ 、 $[0.4, 2.85]$  的区间内扫描调制器系数  $a_1a_2$  与调制器信噪比间的关系,可绘制结果如图 2 所示。在期望指标的范围内选择调制器系数  $a_1=1.3$ ,  $a_2=1$ ,  $a_3=0.6$ ,并在综合考虑开关非线性、热噪声、积分器增益、摆幅、压摆率、带宽等非理想因素后,使用 MATLAB 对调制器进行行为级建模,仿真结果如图 3 所示。三级积分器输出摆幅如图 4 所示,调制器的最大 SNDR 为 108 dB,有效位数接近 18 bit。

由图 4 可知,前馈结构将第一二级积分器的输出摆幅控制在一个极小的范围内,大大降低了 OTA 直流增益对调制器性能的影响。

## 2 Sigma-Delta 调制器的电路实现

### 2.1 总体结构实现

由式(2)、式(3)计算得出调制器的系数实现方案如表 1 所示。

(a) 系数与调制器信噪比关系的平面图

(b) 系数与调制器信噪比关系的三维图

图 2 调制器系数与调制器信噪比间的关系

图 3 行为级仿真结果

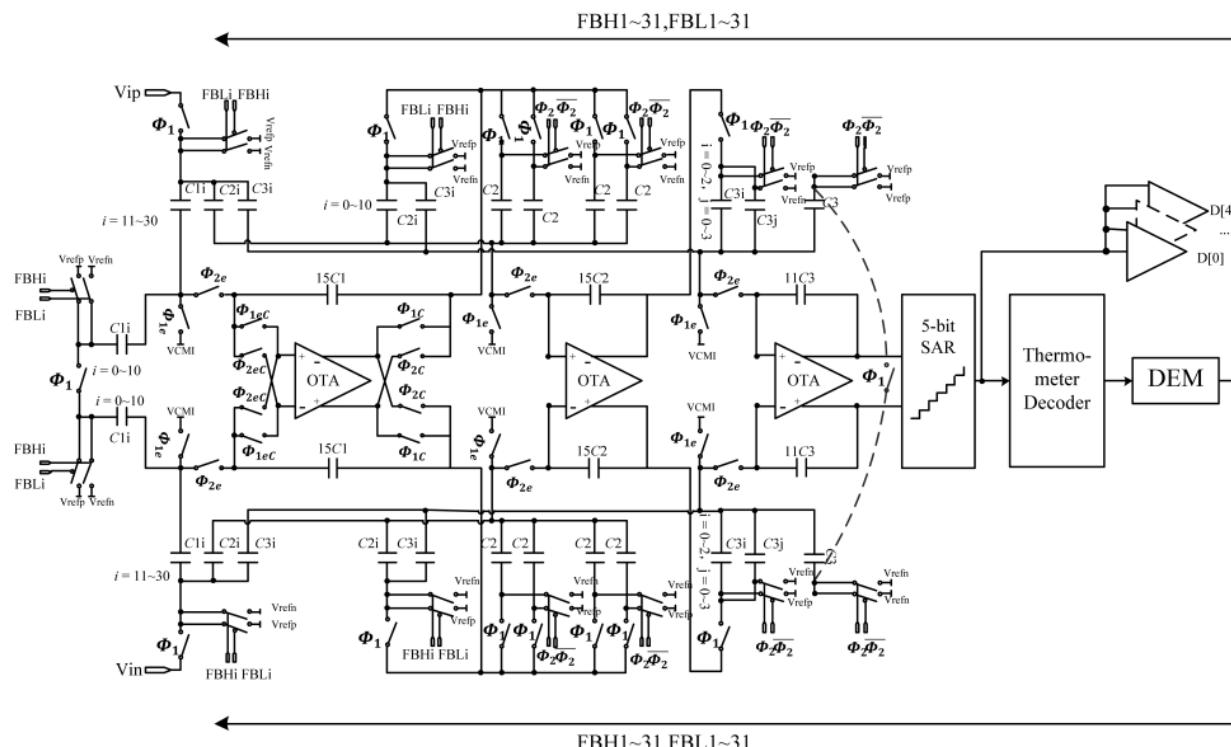

选取第一级单位电容  $c_1$  为 200 fF, 第二、三级单位电容  $c_2, c_3$  为 50 fF, 其总体电路结构如图 5 所示。由于第一、二级积分器输出摆幅很低,对 OTA 的带宽和增益需求也得到降低,固选用简单的 A 类运放进行设计;反馈 DAC 的参考电压设置为 1.8 V 和 0 V,以避免对额外电压产生电路的设计需求;5 bit 量化器采用异步逻辑的逐次逼近型量化器,以降低静态功耗、减小硬件开销。

图 4 三级积分器输出摆幅

表 1 调制器系数实现

| 系数    | 电容            | 系数        | 电容            | 系数        | 电容            |

|-------|---------------|-----------|---------------|-----------|---------------|

| $a_1$ | $20C_1/15C_1$ | $a_{1c1}$ | $31C_1/15C_1$ | $a_{2b1}$ | $20C_2/15C_2$ |

| $a_2$ | $15C_2/15C_2$ | $a_{2c2}$ | $31C_2/15C_2$ | $a_{3b2}$ | $20C_3/11C_3$ |

| $a_3$ | $7C_3/11C_3$  | $a_{3c3}$ | $31C_3/11C_3$ | $a_{3b3}$ | $11C_3/11C_3$ |

和整体面积;第一级采样开关使用 $0.33\mu\text{m}$ 沟道长度的 MOS 管搭建 CMOS 开关,加大 MOS 管尺寸为 $64/0.33\mu\text{m}$ ,以减小管子的导通阻抗,同时避免开关导通电阻阻抗随输入信号幅度变化而引发的非线性失真;所有开关皆由两相不交叠时钟控制, $\Phi_1$  相为采样相, $\Phi_2$  相为积分相,以避免沟道电荷注入引发误差。

## 2.2 跨导放大器的设计

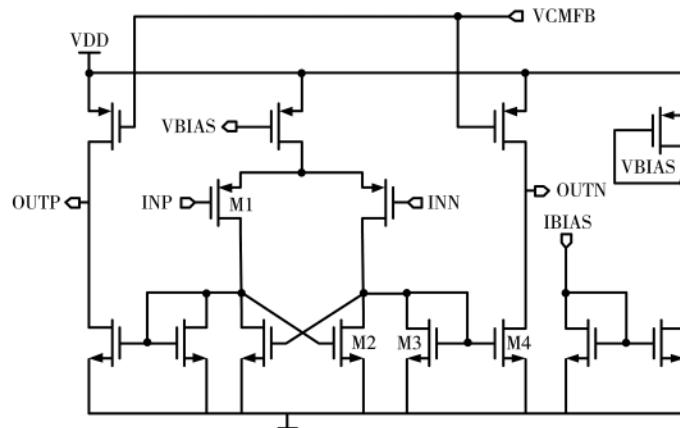

在设计中选用单极电流镜型结构的 OTA 进行积分器的搭建,其结构如图 6 所示,该结构引入一对交叉耦合的 MOS 管构成正反馈,以提高增益和 GBW。

图 6 前两级 OTA 结构

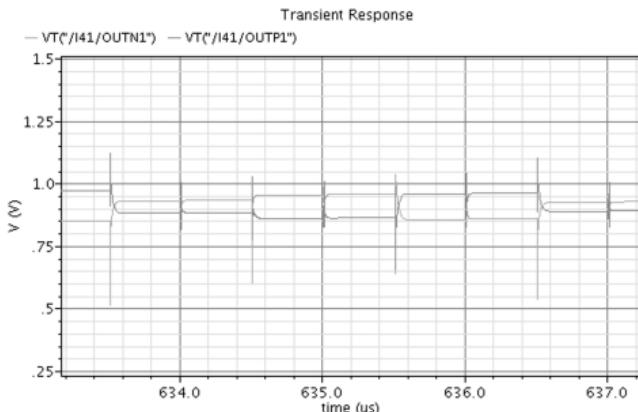

瞬态仿真下,积分器的输出波形如图 7 所示,积分器的输出摆幅很小,稳定在共模电压附近,且在 $\Phi_1$  相和 $\Phi_2$  相皆可建立完全。

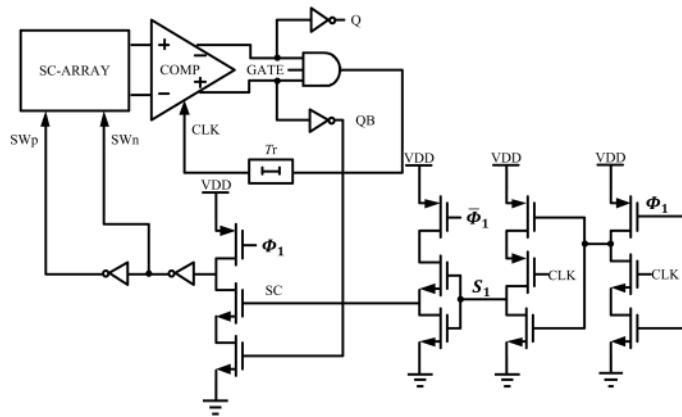

## 2.3 5 bit 量化器的设计

采用动态逻辑可尽量减少高频翻转节点,以实现低功耗设计,固选择带异步复位的高速 TSPC 触发器构成的寄存器链来产生异步 SAR 逻辑。在 $\Phi_2$  相 DAC 对第三级积分器的输出进行采样,而在 $\Phi_1$  相比较器的时钟控

图 5 调制器的整体电路实现

图 7 第一级积分器的建立

制信号 CLK 由 GATE 信号控制环振电路产生, 同时, CLK 控制比较器产生比较结果 Q 和 QB, 也控制 TSPC 触发器产生顺序控制信号 S, 继而使顺序选通信号 SC 在时钟信号到来前翻转为高电平, 以将锁存住的比较结果更快地反馈给 DAC, 其整体结构如图 8 所示。在设计中需保证时钟信号产生环路的延时  $T_r$  大于比较器的复位时间。

图 8 采用 TSPC 逻辑构成的异步 SAR 量化器

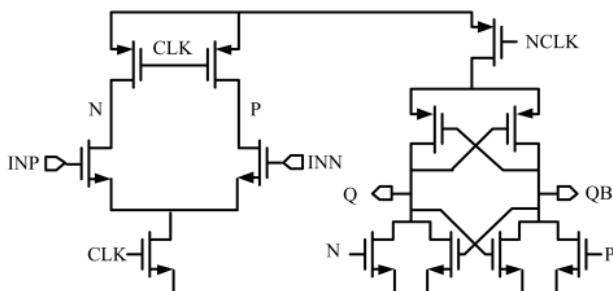

比较器采用低功耗动态比较器, 其结构如图 9 所示。CLK 为低电平时, 比较器处于复位态, P、N 被充电至 VDD; CLK 为高电平时, INP 与 INN 间的压差传导至锁存器, 输出比较结果 Q 与 QB。

图 9 低功耗动态比较器

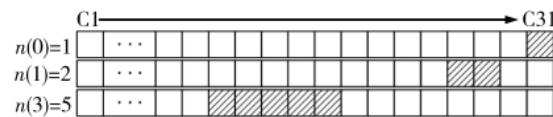

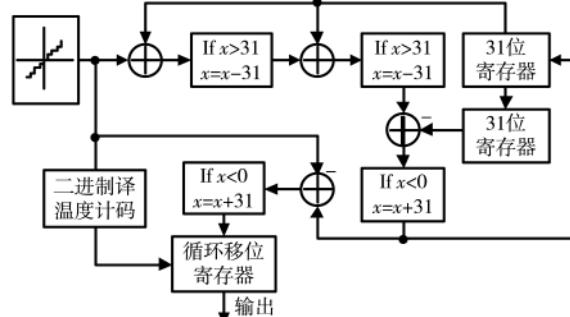

#### 2.4 两阶动态元件匹配算法

量化器输出的 5 bit 二进制码流转换为 31 bit 温度

计码。设反馈电容阵列的理想单位值是  $C_{\text{average}}$ , 出现失配的实际值为  $c_i$ , 电容阵列的失配误差传递函数为  $\text{NTF}(z)$ 。定义指针  $p(z)$ , 在循环移位中, 指针永远指向最后一个选通电容的下一位, 而当前时间选通的电容个数为  $n(z)$ , 则 DAC 的输出可以表示为<sup>[6]</sup>:

$$Y(z)=n(z) \cdot C_{\text{average}} + \text{NTF}(z) \cdot \sum_{i=0}^{p(z)-1} (C_i - C_{\text{average}}) \quad (4)$$

$$\text{NTF}(z)=\sum_{j=0}^k \beta_j \cdot z^{-j} \quad (5)$$

构建 DAC 失配误差整形函数  $\text{NTF}(z)$ , 使  $\text{NTF}(z)$  有二阶高通形式  $(1-z^{-1})^2$ , 展开可得  $\beta_0, \beta_1, \beta_2$  分别为 1, -2, 1。由此推导出指针  $p(k)$  的时域表达式为:

$$p(k)=n(k)+2p(k-1)-p(k-2)+31S_{\text{off}}(k) \quad (6)$$

其中  $p(k), p(k-1), p(k-2)$  分别表示  $k+1, k, k-1$  时刻的电容阵列的起始位置, 当指针溢出 31 位, 令  $S_{\text{off}}(k)=0$ 。

二阶动态元件匹配的移位示意图如图 10 所示, 算法逻辑框图如图 11 所示。

图 10 二阶 DWA 移位示意图

图 11 二阶 DWA 算法逻辑框图

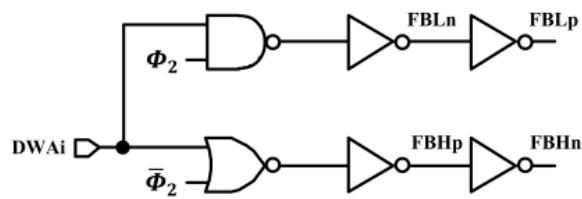

经由 DWA 输出的加权平均码在  $\Phi_2$  相通过图 12 的控制逻辑产生反馈 DAC 的开关控制信号。

图 12 反馈开关控制信号

#### 3 仿真结果

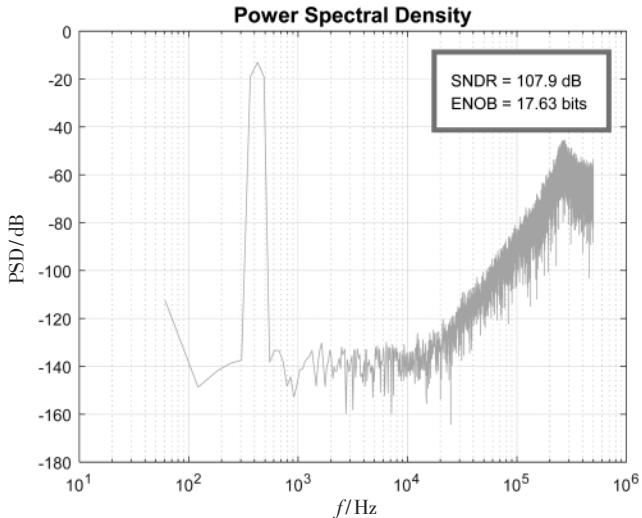

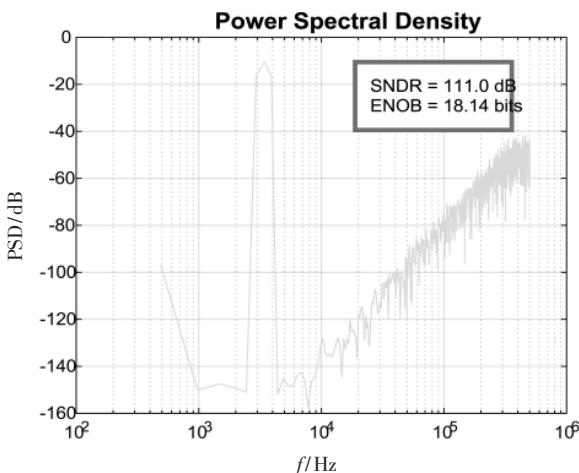

本文设计的带前馈结构的高精度多比特 Sigma-Delta 调制器使用 SMIC0.18 μm 的 CMOS 标准工艺, 电源电压为 1.8 V, 在 1 MHz 采样率下, 为加快仿真速度, 保证 OSR 不变, 调整相干采样点数, 略微增大信号带宽, 输入幅度

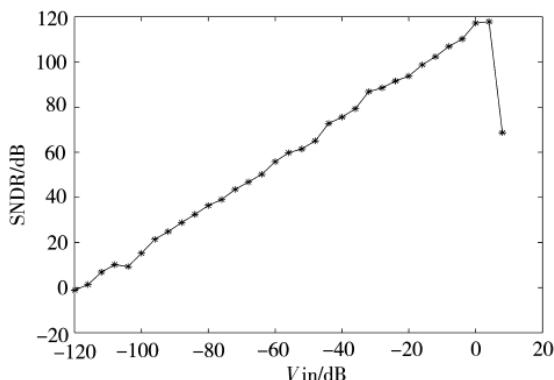

为 $-10.4$  dBFS@ $3.41$  kHz 的信号, 最终仿真得到信号噪声失真比(SNDR)为 $110$  dB, 有效位数(ENOB)为 $18$  bit, 输出频谱图如图 13 所示。由于谐波失真很小, SNR 曲线与 SNDR 曲线近似重合, 可用 SNDR 曲线计算调制器动态范围, 动态范围测量曲线如图 14 所示, 动态范围(DR)约为 $120$  dB。其功耗约为 $0.87$  mW。

图 13 调制器输出功率谱密度

图 14 调制器动态范围曲线

FOM 值(Figure-of-Merit)综合考虑了 ADC 的精度、功耗和速度, 是更为全面的性能指标, 采用式(7)可计算出本结构的 FOM 值为 $3.01$  pJ/step, 与其他已发表的同类 Sigma-Delta 调制器性能对比如表 2 所示。由表 2 可知, 本文中的调制器综合性能更优。

$$FOM = \frac{\text{Power}}{2^{\text{ENOB}} \times F_s} \quad (7)$$

表 2 本文与其他已发表论文的性能比较

| 来源    | 工艺/<br>nm | 电压/<br>V | 带宽/<br>kHz | SNDR/<br>dB | DR/dB | 功耗/<br>μW | FOM/<br>(pJ/step) |

|-------|-----------|----------|------------|-------------|-------|-----------|-------------------|

| 文献[7] | 350       | 5        | 2          | 100.2       | 107.6 | 3 200     | 9.5               |

| 文献[8] | 180       | 1.8      | 0.5        | 77.85       | -     | 204       | 49.8              |

| 文献[9] | 180       | 0.6      | 0.25       | 45          | -     | 0.54      | 7.43              |

| 本文    | 180       | 1.8      | 1          | 111         | 120   | 870       | 3.01              |

#### 4 结论

本文设计的面向生理信号采集应用的 Sigma-Delta

调制器采用全前馈等效结构, 减小调制器的输入输出信号幅度, 大大降低了对 OTA 的直流增益和摆幅要求; 在不过度增加 OSR 的前提条件下, 增加量化器量化位数来提高调制器精度, 并采用基于异步逻辑的逐次逼近型 ADC 来实现五比特量化; 最终采用二阶动态元件匹配算法来解决多比特量化引入的 DAC 非线性失真问题。仿真结果表明, Sigma-Delta 调制器信噪失真比(SNDR)为 $111$  dB, 动态范围(DR)为 $120$  dB, 有效位数为 $18$  bit, 整体功耗为 $0.87$  mW, 满足了生理信号采集应用中对 ADC 高精度、高动态范围的设计需要。

#### 参考文献

- [1] TAKHTI M, TENG Y, ODAME K.A high frequency read-out channel for bio-impedance measurement[C]//2016 IEEE International Symposium on Circuits and Systems(ISCAS), Montreal, QC, 2016: 1514–1517, DOI: 10.1109/ISCAS.2016.7527546.

- [2] TENG Y, ODAME K.A 10 MHz 85 dB dynamic range instrumentation amplifier for electrical impedance tomography[C]//IEEE Biomedical Circuits and Systems Conference(BioCAS), 2014: 632–635.

- [3] XU H, LIU X, YIN L.A closed-loop interface for a high-Q micromechanical capacitive accelerometer with 200 ngrt/Hz input noise density[J].IEEE Journal of Solid-State Circuits, 2015, 50(9): 2101–2112.

- [4] ZAKHEM S, LIU J.An approach for evaluating the performance of a multiband wideband receiver with one sigma-delta ADC and one AGC[C]//MILCOM 2009–2009 IEEE Military Communications Conference, Boston, MA, 2009: 1–6, DOI: 10.1109/MILCOM.2009.5380102.

- [5] MALKI B, YAMAMOTO T, VERBRUGGEN B, et al.A 70 dB DR 10b 0-to-80MS/s current-integrating SAR ADC with adaptive dynamic range[C]//2012 IEEE International Solid-State Circuits Conference, San Francisco, CA, 2012: 470–472, DOI: 10.1109/ISSCC.2012.6177095.

- [6] DES MARAIS D J, STRAUSS H, SUMMONS R E, et al. Carbon isotope, evidence for the stepwise oxidation of the Proterozoic environment[J].Nature, 1992,, 359: 605–609.

- [7] SCHREIER R.Understanding delta-sigma data converters[M]. New York : IEEE Press , 2004.

- [8] LI D, YANG Y T, SHI Z C, et al.A low-distortion multi-bit sigma-delta ADC with mismatch-shaping DACs for WLAN applications[J].Microelectronics Journal, 2015, 46(1): 52–58.

- [9] LV R, CHEN W, LIU X.A high-dynamic-range switched-capacitor sigma-delta ADC for digital micromechanical vibration gyroscopes[J].Micromachines, 2018, 9(8): 372.

- [10] SOHEL A, KHADIR A A, MAAZ M, et al.A 1.8V 204.8-μW 12-bit fourth order active passive ΣΔ modulator for

(下转第 38 页)

Medical Engineering , 2014 , 61(5) : 1436–1447.

- [4] 张丹, 李佳蔚. 探索思维的力量探索思维的力量: 脑机接口研究现状与展望[J]. 科技导报, 2017, 35(9): 62–67.

- [5] WOLPAW J R, MCFARLAND D J, NEAT G W, et al. An EEG-based brain-computer interface for cursor control[J]. Electroencephalography and Clinical Neurophysiology , 1991 , 78(3): 252–259.

- [6] MCFARLAND D J, SARNACKI W A, WOLPAW J R. Electroencephalographic(EEG) control of three-dimensional movement(Article)[J]. Journal of Neural Engineering , 2010 , 7 (3): 036007.

- [7] PFURTSCHELLER G, BRUNNER C, SCHLÖGL A, et al. Mu rhythm(de)synchronization and EEG single-trial classification of different motor imagery tasks[J]. NeuroImage , 2006 , 31 : 153–159.

- [8] 张莉. 表面肌电信号模式识别及其运动分析[D]. 长春: 吉林大学, 2013.

- [9] 黄思娟, 吴效明. 基于 Mu/Beta 节律想象运动脑电信号特征的提取[J]. 中国组织工程研究与临床康复 , 2010(43): 8061–8064.

- [10] 林文通. 基于运动想象 EEG 信号的特征提取研究[D]. 南京: 南京邮电大学, 2017.

- [11] 明东, 王坤, 何峰, 等. 想象动作诱发生理信息检测及其应用研究: 回顾与展望[J]. 仪器仪表学报 , 2014(9):

1921–1931.

- [12] 王晓旭. 多任务运动想象脑电信号分类算法研究[D]. 长春: 吉林大学, 2019.

- [13] PFURTSCHELLER G, ARANIBAR A. Event-related cortical desynchronization detected by power measurements of scalp EEG[J]. Electroencephalography and Clinical Neurophysiology , 1977 , 42(6): 817–826.

- [14] 周仲兴, 明东, 朱誉环, 等. 基于扩展 Informax ICA 的站起想象动作脑电特征提取[J]. 仪器仪表学报 , 2009(3): 459–464.

- [15] 李立亭. 基于共空间模式的四类运动想象脑电信号分类方法[J]. 仪器仪表用户 , 2016 , 23(5): 12–14.

- [16] 李明爱, 王蕊, 郝冬梅. 想象左右手运动的脑电特征提取及分类研究[J]. 中国生物医学工程学报 , 2009(2): 166–170, 176.

(收稿日期: 2020-12-22)

#### 作者简介:

张莉(1987-), 女, 硕士, 工程师, 主要研究方向: 本科实验实践教学、信号处理与模式识别。

王凯瑞(1999-), 男, 本科, 主要研究方向: 电气工程及其自动化。

李杨(1997-), 男, 本科, 主要研究方向: 电气工程及其自动化。

扫码下载电子文档

(上接第 24 页)

- [14] VOJIR T, NOSKOVAL J, MATAS J. Robust scale adaptive mean-shift for tracking[J]. Pattern Recognition Letters , 2014 , 49(3): 250–258.

- [15] WU Y, LIM J, YANG M H, et al. Object tracking benchmark[J]. IEEE Transactions on Pattern Analysis and Machine Intelligence , 2015 , 37(9): 1834–1848.

(收稿日期: 2020-12-29)

#### 作者简介:

孟令军(1969-), 男, 博士, 副教授, 主要研究方向: 目标跟踪、数字图像处理、嵌入式系统设计。

尚桠朝(1995-), 男, 硕士研究生, 主要研究方向: 目标跟踪、图像处理。

扫码下载电子文档

(上接第 29 页)

- biomedical applications[C]//2019 Devices for Intergrated Circuit , DOI: 10.1109/DEVIL.2019.8783626.

- [11] YOON Y, ROH H, LEE H, et al. A 0.6-V 540-nW delta-sigma modulator for biomedical sensors[J]. Analog Integrated Circuits and Signal Processing , 2013 , 75(2): 323–327.

(收稿日期: 2021-02-14)

#### 作者简介:

刘铭扬(1996-), 女, 硕士研究生, 主要研究方向: 数模

混合集成电路设计。

王小松(1981-), 男, 博士, 副研究员, 主要研究方向: 模拟/射频/混合 CMOS 集成电路与模块、面向物联网应用的射频技术。

刘昱(1975-), 男, 博士, 研究员, 主要研究方向为: 高性能模拟/射频 CMOS 集成电路、硅基毫米波集成电路、超低功耗短距离无线通信系统、高精度低功耗传感电路、物联网相关技术及医疗电子系统集成技术。

扫码下载电子文档

## 版权声明

经作者授权，本论文版权和信息网络传播权归属于《电子技术应用》杂志，凡未经本刊书面同意任何机构、组织和个人不得擅自复印、汇编、翻译和进行信息网络传播。未经本刊书面同意，禁止一切互联网论文资源平台非法上传、收录本论文。

截至目前，本论文已经授权被中国期刊全文数据库（CNKI）、万方数据知识服务平台、中文科技期刊数据库（维普网）、DOAJ、美国《乌利希期刊指南》、JST 日本科技技术振兴机构数据库等数据库全文收录。

对于违反上述禁止行为并违法使用本论文的机构、组织和个人，本刊将采取一切必要法律行动来维护正当权益。

特此声明！

《电子技术应用》编辑部

中国电子信息产业集团有限公司第六研究所