# 面向 SoC 的 SRAM 读出电路加固设计

沈 婧,薛海卫,陈玉蓉,张猛华,王 蕾

(中国电子科技集团公司第 58 研究所,江苏 无锡 214035)

**摘要:** SRAM 存储器在 SoC 芯片中的应用已经越来越普遍,存储单元的加固设计已成为抗辐射 SoC 芯片设计首要考虑的问题之一。提出了两种 SRAM 读出电路的加固结构,分别从读出电路结构、数据读出速度和抗单粒子翻转能力等方面进行了对比。两种读出结构的 SRAM 均有较好的抗单粒子能力,但相比较单模双互锁结构的 SRAM,双模双互锁读出结构的 SRAM 读出时间更短。

**关键词:** SoC; 单粒子翻转; SRAM 读出电路; 数据读出速度

中图分类号: TN702

文献标识码: A

DOI:10.16157/j.issn.0258-7998.211423

中文引用格式: 沈婧,薛海卫,陈玉蓉,等. 面向 SoC 的 SRAM 读出电路加固设计[J]. 电子技术应用, 2021, 47(10): 38–41, 47.

英文引用格式: Shen Jing , Xue Haiwei , Chen Yurong , et al. Design of a radiation hardened read circuit of SRAM in SoC[J]. Application of Electronic Technique , 2021 , 47(10) : 38–41 , 47.

## Design of a radiation hardened read circuit of SRAM in SoC

Shen Jing , Xue Haiwei , Chen Yurong , Zhang Menghua , Wang Lei

(CETC 58 , Wuxi 214035 , China)

**Abstract:** The application of SRAM memory in SoC is more and more common, and the design of radiation hardened memory has become one of the most important issues in the design of radiation resistant SoC. In this paper, two kinds of SRAM read circuits are proposed and compared in terms of readout circuit structure, data readout speed and single event upset resistance. The SRAM of the two readout structures have good single event resistance, but SRAM with dual-input DICE structure has shorter readout time compared with SRAM with single-input DICE structure.

**Key words:** system on chip ; single event upset ; SRAM readout circuit ; data readout speed

## 0 引言

高能带电粒子在器件的灵敏区内产生大量带电粒子的现象,它属于电离效应。当能量足够大的粒子射入集成电路时,由于电离效应(包括次级粒子的),产生数量级多的电离电子-空穴对,引起半导体器件的软件错误,使逻辑器件和存储器产生单粒子翻转,CMOS 器件产生单粒子闭锁,甚至出现单粒子永久损伤的现象,辐射主要包括质子、中子、重离子和  $\alpha$  粒子<sup>[1-3]</sup>。集成度的提高、特征尺寸的降低、临界电荷和有效 LET 阈值下降等会使抗单粒子扰动能力降低。器件的抗单粒子翻转能力明显与电路设计、版图设计、工艺条件等因素有关<sup>[4]</sup>。

锁存器经常被用于现在的超大规模集成电路中,特别是 SoC 和 CPU 的流水线结构中<sup>[5-6]</sup>。数据读出电路的数据锁存也是必不可少的,因此提高锁存器的抗单粒子能力意义重大。本文基于双互锁(DICE)结构<sup>[7-8]</sup>和 Muller\_C 单元<sup>[9-10]</sup>,对 SoC 片上 SRAM 的数据读出电路进行了抗辐射加固设计,并先后提出了两种不同结构的读出电路。

## 1 基于双互锁结构(DICE)读出电路加固设计

在读出电路设计的过程中,需要考虑以下几个问题:

- (1)保留数据锁存能力;

- (2)尽量提高抗单粒子和抗闩锁能力;

- (3)不能影响数据读出的速度;

- (4)翻转后恢复时间要尽量短。

本文提出了 SoC 片上 RAM 的两种读出电路结构,第一种电路结构是基于 DICE 单元和 Muller\_C 延时结构的单模读出通路设计,灵敏放大器的输出通过基于 Muller\_C 单元的延时结构<sup>[11]</sup>分别为 DICE 单元提供两组输入信号,该设计不仅可以保证信号的抗 SEU 能力,也能有效地降低单粒子的瞬态扰动,缺点是延时单元会增加数据读出的时间;第二种电路结构是基于 DICE 结构的双模读出电路,在 DICE 单元的基础上,对灵敏放大器采用双模设计,该设计抗单粒子能力略高于第一种读出电路设计,同时灵敏放大器的输出在作为 DICE 单元输入的同时又与最后一级 Muller\_C 单元直接相连,从而减少了数据读出时间。

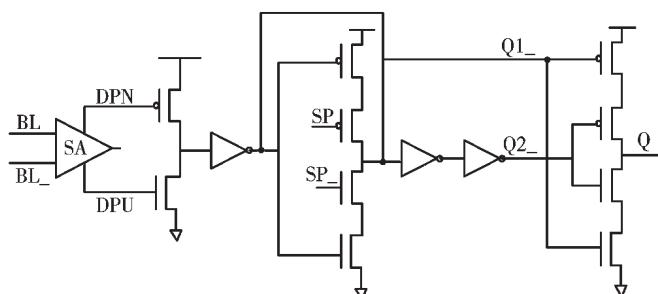

### 1.1 常见读出电路

图 1 是常见的数据读出电路,位线的 0/1 通过 SA 运放之后经过一级 Muller\_C 单元读出,Muller\_C 结构前是一个钟控的锁存器。灵敏放大器使能信号控制灵敏放大器工作,将这一电压差放大为满摆幅的 DPU 和 DPN 信号,将存储的数据读出。当读出结束后灵敏放大器停止工作,并且将其差分输入端口充电至“1”,这时 DPN 为“1”,DPU 为“0”,使数据无法写入锁存器中从而保证读出数据的正确性。灵敏放大器结构如图 1 所示。在读出存储节点信号时,SP 为“1”,这时锁存器的反馈链被打断,从而提高了数据读出的速度,当读出结束后,SP 跳变为“0”,从而所存读出的数据。它们在 SP 信号的控制下被锁存,并在 Q 端输出。

图 1 一般读出电路

### 1.2 基于 DICE 结构读出电路设计

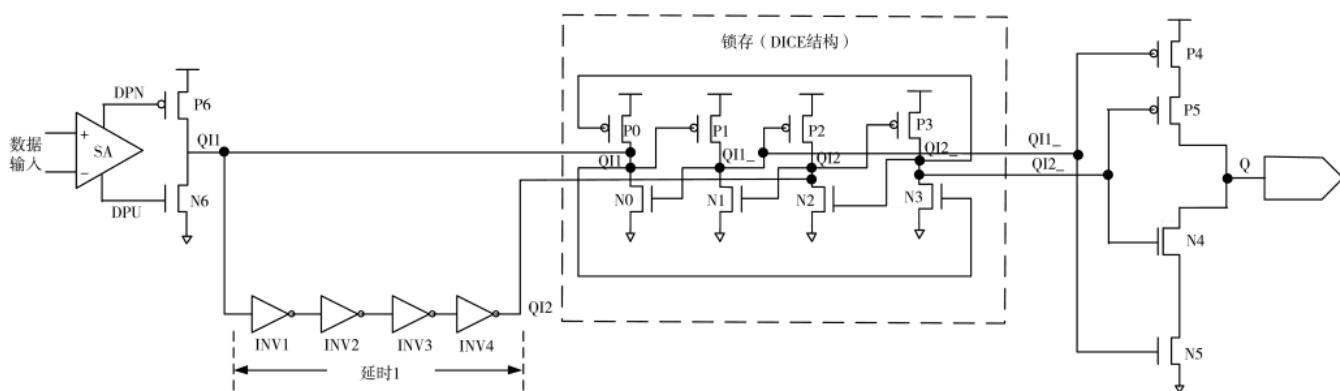

#### 1.2.1 单模双互锁结构读出电路

该读出电路结构主要由灵敏放大器、Muller\_C 单元和延时电路组成,基于 DICE 单元,数据经过灵敏放大器为 DICE 输入信号 QI1,通过延时结构为 DICE 单元提供另一路信号 QI2,电路结构图如图 2 所示。

该结构中延时电路由多级反相器组成,使得 DICE 单元的两组输入信号形成一定的延时错位,该延时必须要大于单粒子瞬态扰动的脉宽<sup>[12-13]</sup>。结合工艺与器件仿真,该部分电路的延时时间在 200 ps~300 ps。

加固后读出电路的抗 SEU 工作原理为:在读出过程中,如果 QI1、QI2 中的一个节点被打翻,这时 Q 输出高

阻,数据不能写入 DICE 锁存单元,当轰击脉冲过去后,QI1、QI2 节点恢复到正确值,这时 Q 输出读出的数据,同时数据被保存到 DICE 单元中。在读出数据后,节点 QI1、QI2 与灵敏放大器的通路断开,这时输出 Q 只与 DICE 锁存器中存储的数据有关,由 DICE 锁存器的抗 SEU 特性可知,这时的输出具有抗 SEU 的能力。

但该结构有一个缺点,就是 QI2 通路的延时 1 会增加数据输入到 Q 的时间,而对于 SoC 芯片来说,该部分的延迟是希望被省下的,为了改进 SoC 时序的问题,对 SRAM 读出电路部分进行了优化改进,这就形成了第二种双模双互锁结构电路。

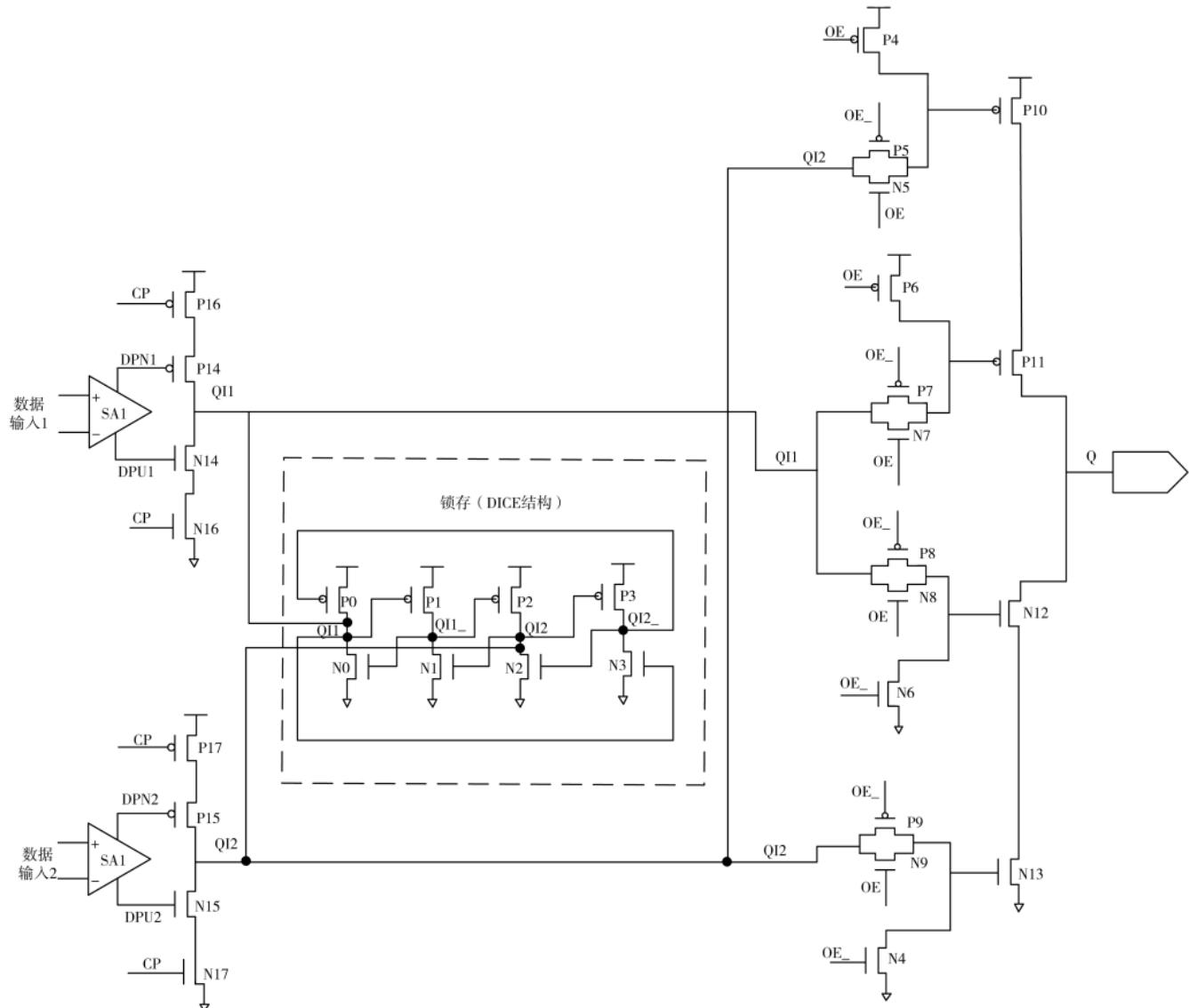

#### 1.2.2 双模双互锁结构读出电路

本结构在单模读出电路基础上做了改进优化,将延时电路产生的 QI2 信号用双模灵敏放大器来替代,并将 QI1、QI2 直接与后两级读出单元相连,保证 DICE 锁存特性的同时进一步缩短数据的读出时间,电路结构如图 3 所示。

双模双互锁的结构基础上增加了一个两级 OE 控制的读出单元,锁存单元的输出 QI1、QI2 经过第一级 OE 控制的传输门作为第二级读出单元的输入,OE 使能关断的情况下,第一级传输门关闭,锁存单元的数据不会传输到第二级读出单元;第二级读出单元因 OE 的关断而被上拉到固定高电平,第二级读出单元也将关断,没有新的数据传输到 Q。只有 OE 使能,Q 的数据才会更新。

两级带 OE 开关的读出结构对数据读出做了更好的隔离,只要 OE 使能不打开,端口的数据就不会发生变化,数据的扰动也将会在经过两级 OE 开关的读出电路后降低,再加上 Muller\_C 单元的本身特性,该 SRAM 读出电路读出单元有很好的抗单粒子扰动的性能,传输门的延时很小,也不会增加数据读出的时间。

本结构的抗 SEU 工作原理与第一种电路结构一样,双模电路结构对数据输入的加固起到了更好的效果,两级的 Muller\_C 单元起到了更好的抗扰动作用。而数据读书时间方面,通过仿真实验对比,双模双互锁结构的读出电路数据读出时间比第一种结构缩短了约 350 ps。

图 2 基于 DICE 结构单模读出电路

图 3 双模双互锁结构读出电路

### 1.3 读出时间 $T_a$ 对比

基于 sign off 工艺角和电压，采用 SPICE 仿真工具，分别对两种结构的 SRAM 进行了详尽的仿真验证，4 kB 容量的 SRAM 读出时间对比如表 1 所示。

表 1 两种 SRAM 结构读出时间对比

| 单模双互锁结构         |       | 双模双互锁结构         |      |

|-----------------|-------|-----------------|------|

| SRAM 读出时间 $T_a$ | (ns)  | SRAM 读出时间 $T_a$ | (ns) |

| 1.98 V, -55 °C  | 2.019 | 1.886           |      |

| 1.8 V, 25 °C    | 2.993 | 2.674           |      |

| 1.62 V, 125 °C  | 4.846 | 4.309           |      |

由表 1 的仿真数据可以得出，在相同容量的条件下，采用双模双互锁读出结构的 SRAM 读出时间缩短 10% 左右。

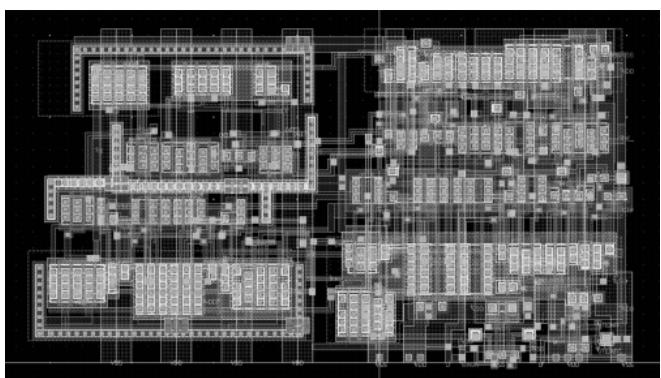

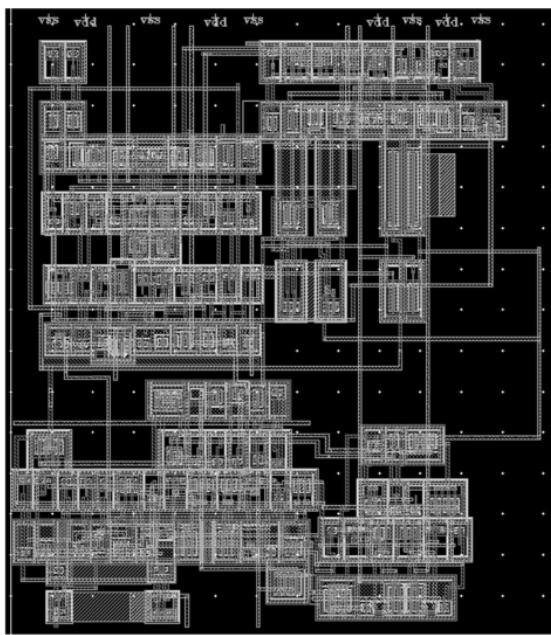

### 2 版图设计

为了防止数据输入通路的两个节点同时翻转，在版

图设计过程中充分考虑两组信号输入通路之间的间距。

图 4 为单模双互锁结构的 SRAM 读出电路，敏感节点设计为间距 5.4  $\mu\text{m}$ ；图 5 为双模双互锁结构的 SRAM 读出电路，敏感节点设计为间距 4  $\mu\text{m}$ 。

图 4 单模输入双互锁读出电路版图

图 5 双模输入双互锁读出电路版图

### 3 单粒子翻转实验数据对比

本设计的两种不同结构的 SRAM 分别应用于同一种 SoC 芯片的两个版本, 片内 SRAM 容量为 32 kB, 流片工艺为 0.18 μm CMOS 工艺, 单粒子仿真采用结合 TCAD 及 SPICE 软件相结合的方法<sup>[14-15]</sup>。

单粒子翻转试验采用中国原子能科学研究院的 HI-13 重离子加速器, 分别在 F、CL、Ti、Ge 和 I 五种离子下对电路进行了辐射实验, 两种结构的实验测得结果如表 2 所示。

在 F 离子和 CL 离子下, 片内 SRAM 均未发生单粒子翻转现象, 在 Ti 离子、Ge 离子、I 离子下片内 SRAM 均发生了不同位数的翻转, 实验结果表明在受到较高能量辐射时, 芯片的单粒子翻转效应更容易产生。

通过 SEU 数目和单粒子翻转截面的数据对比, 相同试验条件下双模 DICE 结构的 SRAM 的单粒子翻转数略少于单模 DICE 结构的 SRAM, 计算得出的单粒子翻转

截面结果数量级一致, 实验结果表明两种结构的 SRAM 具有相当的抗单粒子翻转能力。

### 4 结论

本文提出的两种基于 DICE 结构和 Muller\_C 单元的读出电路结构均能有效地提高 SoC 片内 SRAM 的抗单粒子能力和抗扰动能力。采用两种结构 SRAM 的 SoC 电路于 0.18 μm CMOS 工艺线流片验证。双模 DICE 读出结构的 SRAM 电路读出时间比单模 DICE 读出结构的 SRAM 电路读出时间缩短 10%, 在实际设计 SoC 片上 RAM 时, 可综合考虑面积、速度、抗 SEU 能力来选择读出电路的设计结构。

### 参考文献

- [1] BENEDETTO J, ETON P, AVERY K, et al. Heavy ion-induced digital single-event transients in deep submicron processes[J]. IEEE Transactions on Nuclear Science, 2004, 51: 3480-3485.

- [2] TANAY K, SENIOR M. Characterization of soft errors caused by single event upsets in CMOS processes[J]. Dependable and Secure Computing, 2004, 1(2): 128-143.

- [3] BAZE M P, WERT J, CLEMENT J W, et al. Propagating SET characterization technique for digital CMOS libraries[J]. IEEE Transactions on Nuclear Science, 2006, 53(6): 3472-3478.

- [4] 丁义刚. 空间辐射环境单粒子效应研究[J]. 航天器环境工程, 2007, 24(5): 283-291.

- [5] BHUVA B L, BLACK J D, MASSENGILL L W, et al. RHBD techniques for mitigating effects of single-event hits using guard-gates[J]. IEEE Transactions Nuclear Science, 2005, 52(6): 2531-2535.

- [6] 贺兴华, 肖山竹, 张路, 等. 空间 DSP 信息处理系统存储器 SEU 加固技术研究[J]. 宇航学报, 2010, 31(2): 472-477.

- [7] CALIN T, NICOLAIDIS M, VELAZCO R, et al. Upset hardened memory design for submicron CMOS technology[J]. Nuclear Science, 1996, 43(6): 2876-2878.

- [8] LI H, LI W, TAN J P, et al. Design of a low power radiation hardened 256K SRAM[C]//2006 8th International Conference

表 2 SoC 片内 SRAM 5 种离子辐射实验结果对比

| SRAM 类型         | 离子种类                               | 能量/MeV | 总注量/(ions/cm <sup>2</sup> ) | 辐射时间/min | SEU 数目/bit | 单粒子翻转截面/(cm <sup>2</sup> /bit) |

|-----------------|------------------------------------|--------|-----------------------------|----------|------------|--------------------------------|

| 单模 DICE 结构 SRAM |                                    |        |                             |          | 0          | 0                              |

| 双模 DICE 结构 SRAM | <sup>19</sup> F <sup>9+</sup>      | 115    | 1.00×10 <sup>7</sup>        | 12.13    | 0          | 0                              |

| 单模 DICE 结构 SRAM |                                    |        |                             |          | 0          | 0                              |

| 双模 DICE 结构 SRAM | <sup>35</sup> CL                   | 175    | 9.64×10 <sup>6</sup>        | 11.28    | 0          | 0                              |

| 单模 DICE 结构 SRAM |                                    |        |                             |          | 6          | 6.17×10 <sup>-7</sup>          |

| 双模 DICE 结构 SRAM | <sup>48</sup> Ti                   | 195    | 9.73×10 <sup>6</sup>        | 18.02    | 2          | 2.06×10 <sup>-7</sup>          |

| 单模 DICE 结构 SRAM |                                    |        |                             |          | 9          | 7.89×10 <sup>-7</sup>          |

| 双模 DICE 结构 SRAM | <sup>74</sup> Ge <sup>11,20+</sup> | 212    | 1.14×10 <sup>7</sup>        | 19.07    | 3          | 2.63×10 <sup>-7</sup>          |

| 单模 DICE 结构 SRAM |                                    |        |                             |          | 54         | 7.93×10 <sup>-6</sup>          |

| 双模 DICE 结构 SRAM | <sup>127</sup> I <sup>15,25+</sup> | 283    | 6.81×10 <sup>6</sup>        | 11.35    | 48         | 7.05×10 <sup>-6</sup>          |

(下转第 47 页)

满足 DDR3 规范要求。

#### 4 结论

本文介绍了 DDR3 的时序计算与仿真,结合一例实际 SiP 项目中的高密度互连 DDR3 系统封装和基板设计方案,进行 DQ 与 DQS、地址与时钟之间的时序仿真与优化。通过仿真发现,在信号波形满足 DDR3 的 AC 和 DC 判决标准后,其建立时间与保持时间仍可能不满足 DDR3 的时序要求,验证了 DDR3 时序仿真的重要性。本文在项目后仿阶段,针对 DQ 与 DQS、地址与时钟之间的不合格时序信号,进行具体分析,讨论时序与波形之间的关系,结合版图分析,提出优化方案并通过仿真迭代进行验证。鉴于后仿真阶段对设计修改的局限性,最终得到切合实际的优化方案,使所有信号均满足 JEDEC 协议规范。通过仿真来指导设计,为 SiP 的 DDR3 系统的设计与优化给出方向和建议。

#### 参考文献

- [1] 李扬.SiP 系统级封装设计仿真技术[J].电子技术应用,2017,43(7):47–50.

- [2] 曾燕萍,张景辉,王梦雅,等.DDR3 堆叠键合组件的信号完整性分析与优化[J].电子与封装,2020,20(12):120201.

- [3] 王福鑫,国凤娟,牛玉成,等.基于 SiP 技术的微系统设计与实现[J].电子技术应用,2018,44(12):17–19.

- [4] LEE Y C,PARK C S.LTCC-based monolithic system-in-package(SiP) module for millimeter-wave applications[J]. International Journal of RF and Microwave Computer-Aided Engineering, 2016, 26(9): 803–811.

- [5] 孙静,黄文清.基于 DDR3 高速电路拓扑结构的优化与仿真[J].计算机应用与软件,2017,34(2):147–151.

- [6] 孔维刚,陈长胜,张旭.Virtex-7 FPGA DDR3 电路的设计与仿真研究[J].航空计算技术,2018,48(4):93–96.

- [7] BOGATIN E.信号完整性与电源完整性分析[M].李玉山,

(上接第 41 页)

- on Solid-State and Integrated Circuit Technology Proceedings, 2006.

- [9] MULLER D,BARTKY W.A theory of asynchronous circuits[C]// Proceedings of International Symposium on the Theory of Switching, 1959: 204–243.

- [10] DEVARAPALLI S V,ZARKESH-HA P,SUDDARTH S C. SEU-hardened dual data rate flip-flop using Celements[C]// Int Symp Defect Fault Tolerance VLSI Syst.Albuquerque, NM, USA.2010: 167–171.

- [11] MONGKOLKACHIT P,BHUVA B,BOULGHASSOUL Y,et al. Mitigation of single-event transients in CMOS digital circuits[C]//Proceedings of Radiation and its Effects on Components and Systems, Nashville, Vanderbilt University, 2003: 335–340.

- [12] 张筱颖.基于异步保存及互锁存储单元的抗 SEE 触发器

刘洋,初秀琴,等,译.北京:电子工业出版社,2019.

- [8] 倪芸,姚晓东.高速并行总线信号完整性分析设计[J].电子测量技术,2013,36(4):106–110.

- [9] SHARMA H,MERVIN J,SELVAKUMAR D.DDR3 interconnect optimization—signal integrity and timing analysis perspective[C]//2015 International Conference on Control. IEEE, 2015.

- [10] 韩玉涛.高速总线的时序分析方法及 DDR 计算实例[J].常州工学院学报,2018,31(2):42–47.

- [11] 金帅,韩连刚,谢锡海.DDR3 与 FPGA 接口的高速电路板信号完整性分析[J].现代电子技术,2017,40(22):10–13.

- [12] 牛宾,史黎黎.基于 DDR3 的 PCB 设计及仿真[J].计算机与网络,2017,43(12):64–66.

- [13] 李晋文,胡军,曹跃胜,等.DDR3 时序分析与设计[J].计算机科学,2012,39(4):293–295.

- [14] JEDEC.DDR3 SDRAM specification :JESD 79-3F[S]. Arlington :JEDEC ,2012.

- [15] 陈兰兵,钟章民,肖定如,等.Cadence 高速电路设计[M].北京:电子工业出版社,2014.

- [16] 唐万明,范朝元.基于 Cadence 的 DDR 源同步时序仿真研究[J].现代电子技术,2014,37(8):75–78.

(收稿日期:2021-02-03)

#### 作者简介:

王梦雅(1992-),女,硕士研究生,工程师,主要研究方向:SiP 系统级设计、仿真技术。

曾燕萍(1987-),女,博士研究生,高级工程师,主要研究方向:三维集成系统设计、仿真技术。

张景辉(1994-),男,硕士研究生,工程师,主要研究方向:信号完整性与电源完整性仿真。

扫码下载电子文档

设计[J].固体电子学研究与进展,2013,33(5):497–500.

- [13] 周昕杰.单粒子瞬态扰动加固锁存电路:107124176[P]. 2017-09-01.

- [14] DODD P E,MASSENGILL L W.Basic mechanisms and modeling of single-event upset in digital microelectronics[J]. IEEE Trans.Nucl.Sci., 2003, 50: 583–602.

- [15] 周昕杰.TCAD 结合 SPICE 的单粒子效应仿真方法[J]. 电子与封装,2019,19(4):32–35,48.

(收稿日期:2021-02-23)

#### 作者简介:

沈婧(1988-),女,硕士,工程师,主要研究方向:存储器设计、低功耗信号处理器设计。

薛海卫(1978-),男,硕士,研究员级高级工程师,主要研究方向:抗辐照信号处理器设计、高性能信号处理器设计。

陈玉蓉(1982-),女,本科,工程师,主要研究方向:后端版图设计。

扫码下载电子文档

## 版权声明

经作者授权，本论文版权和信息网络传播权归属于《电子技术应用》杂志，凡未经本刊书面同意任何机构、组织和个人不得擅自复印、汇编、翻译和进行信息网络传播。未经本刊书面同意，禁止一切互联网论文资源平台非法上传、收录本论文。

截至目前，本论文已经授权被中国期刊全文数据库（CNKI）、万方数据知识服务平台、中文科技期刊数据库（维普网）、DOAJ、美国《乌利希期刊指南》、JST 日本科技技术振兴机构数据库等数据库全文收录。

对于违反上述禁止行为并违法使用本论文的机构、组织和个人，本刊将采取一切必要法律行动来维护正当权益。

特此声明！

《电子技术应用》编辑部

中国电子信息产业集团有限公司第六研究所