# 基于 LabVIEW 和 FPGA 的半实物仿真平台的设计与实现 \*

疏成成<sup>1,2</sup>, 苏建徽<sup>1,2</sup>, 施永<sup>1,2</sup>, 解宝<sup>1,2</sup>, 赖纪东<sup>1,2</sup>

(1. 光伏系统教育部工程中心, 安徽 合肥 230009;

2. 合肥工业大学 电气与自动化工程学院, 安徽 合肥 230009)

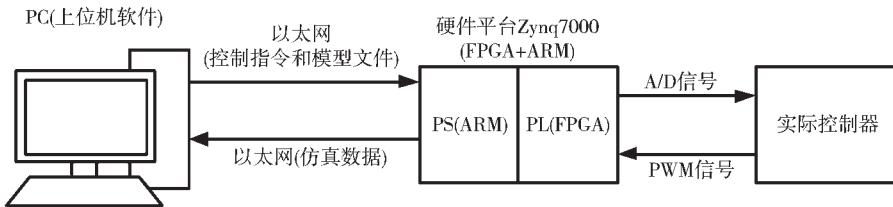

**摘要:** 针对电力电子本科或研究生教学实验, 基于 LabVIEW 和简易 FPGA 板卡, 设计了一种高性价比的电力电子半实物实时仿真教学实验平台。仿真平台系统由上位机和模型运算单元 FPGA 板卡组成, 人机界面及实验波形数据显示基于 LabVIEW 软件平台编制, 通过以太网实现与 FPGA 板卡数据交换, 平台系统可以进行多种电路拓扑模型的下载安装和 HIL 实时仿真实验。

**关键词:** 半实物仿真平台; LabVIEW; FPGA; 以太网控制

中图分类号: TN919.5; TP391.9; TP274

文献标识码: A

DOI: 10.16157/j.issn.0258-7998.211283

中文引用格式: 疏成成, 苏建徽, 施永, 等. 基于 LabVIEW 和 FPGA 的半实物仿真平台的设计与实现 [J]. 电子技术应用, 2021, 47(10): 57-62.

英文引用格式: Shu Chengcheng, Su Jianhui, Shi Yong, et al. Design and implementation of a hardware-in-the-loop simulation platform based on LabVIEW and FPGA[J]. Application of Electronic Technique, 2021, 47(10): 57-62.

## Design and implementation of a hardware-in-the-loop simulation platform based on LabVIEW and FPGA

Shu Chengcheng<sup>1,2</sup>, Su Jianhui<sup>1,2</sup>, Shi Yong<sup>1,2</sup>, Xie Bao<sup>1,2</sup>, Lai Jidong<sup>1,2</sup>

(1. Photovoltaic System Ministry of Education Engineering Center, Hefei 230009, China;

2. School of Electrical and Automation Engineering, Hefei University of Technology, Hefei 230009, China)

**Abstract:** Aiming at the teaching experiment of undergraduate or graduate students in power electronics, based on LabVIEW and simple FPGA board, a high cost-effective hardware in the loop real-time simulation teaching experiment platform for power electronics is designed. The simulation platform system is composed of upper computer and FPGA board. The man-machine interface and experimental waveform data display are based on LabVIEW software platform. Data exchange with FPGA board is realized through Ethernet. The platform system can download and install various circuit topology models and HIL real-time simulation experiments.

**Key words:** hardware-in-the-loop simulation platform; LabVIEW; FPGA; Ethernet control

## 0 引言

半实物实时仿真的技术有两种方式: 一种是快速控制原型(Rapid Control Prototyping, RCP)采用“虚拟控制器+实际对象”方式; 另一种是硬件在回路(Hardware in Loop, HIL)采用“实际控制器+虚拟对象”方式, 主要应用于电力电子系统控制器软件的开发。半实物实时仿真的应用领域非常广泛, 涉及轨道交通、风电、光伏发电、新能源汽车、电力系统、工业传动等<sup>[1-5]</sup>。半实物仿真的硬件在回路(HIL)仿真方式是将数学化的实体模型和实际控制器联系在一起运行的仿真系统<sup>[6-7]</sup>。相对于纯计算机软件仿真, 半实物仿真具有有效性、可重复性、经济

性、安全性等诸多优点, 是一种更接近实际情形的仿真技术<sup>[8-11]</sup>。

平台采用“FPGA+ARM”作为下位机, 用以太网方式和 LabVIEW 上位机通信, 实现在同一网络下下载模型, 很大程度降低了用户使用的难度, 让学生用模型做实验更加便捷。

### 1 半实物实时仿真平台的结构

半实物实时仿真平台是基于 HIL 仿真方式设计而成的, 主要由三部分组成: 硬件系统、实物软件模型和上位机系统。硬件系统主要用于采集和处理各种信号, 通过 FPGA 和 ARM 构建一个基本的通信平台, 保证通信的可靠性和稳定性, 并拥有丰富的 I/O 接口提升其扩展性。硬件系统通过以太网的方式与上位机系统建立通

\* 基金项目: 国家自然科学基金资助项目(51907045); 中央科研基本业务费支持项目(PA2020GDGP0053)

信,进行数据传输。在硬件系统的基础上,上位机软件主要完成硬件系统的相关配置、模型的参数设置、提供测试过程中的控制指令、创建可视化的人机交互界面等工作。上位机软件的存在大大提高了整个半实物实时仿真平台的易用性。实物软件模型是根据需要测试的实物设计出不同的实物模型,来配合硬件系统完成半实物实时仿真。该半实物实时仿真平台的原理示意图如图1所示。本文的平台可以在上位机软件中选择实物模型,将其下载到FPGA中,通过上位机进行参数的设置和仿真的启停等控制指令。仿真开始后,FPGA可以得到实物模型实时运行的数据。数据会在ARM程序中进行打包处理,然后通过以太网,将打包后的数据发给上位机软件。上位机对仿真的数据进行解析、转换格式等处理后,就会在虚拟示波器上显示相应曲线波形。

图1 HIL系统仿真平台原理图

## 2 硬件系统设计与实物模型搭建

本文的半实物仿真平台使用的是Xilinx公司Zynq7000系列的XC7Z020-2CLG400I的(FPGA+ARM)芯片。Zynq7000芯片可分为Processor System(PS)处理系统部分和Programmable Logic(PL)可编辑逻辑部分。PL部分加载了FPGA的程序,可以实时运行实物模型,得到相应的测试点数据。测试点的数据会保存在特定的地址区。PS部分加载了ARM的程序,是上位机程序和FPGA之间沟通的桥梁,主要有两个功能:(1)解析上位机软件下发的控制指令和参数,并通过一定的逻辑关系进行对FPGA控制;(2)在数据内存满时触发中断程序,对数据进行打包,发送给上位机。

搭建实物模型的步骤如下所示:

(1)根据该实物模型相关的数学公式和要求,选择自己的建模方法。

(2)根据数学公式,使用System Generator软件进行实物模型的搭建,生成Verilog工程文件。

(3)根据实物模型生成的Verilog工程文件,通过软件创建新项目,在新项目里为模型建立IP核和相应接口配置,和通信模块一起生成Bit文件。将Bit文件、相关参数配置文件和实物模型拓扑图按一定要求存放在上位机软件指定目录下。

## 3 上位机系统设计

LabVIEW是图形化的G语言的编写程序,利用框图式的程序来代替冗长的语言代码,能够快速地创建算法来解决各种工程问题,而且人机交互界面操作简易,可

以帮助用户快速上手操作。本文的半实物实时仿真平台的上位机软件是基于LabVIEW进行编写的<sup>[12-14]</sup>。上位机软件所采用的框架是“生产者+消费者”。生产者-事件结构根据用户的按键等动作进行触发中断,队列负责将相应中断和中断包含的数据传至条件结构,消费者-条件结构通过中断类型进行判断,进入不同的算法模块和功能模块。

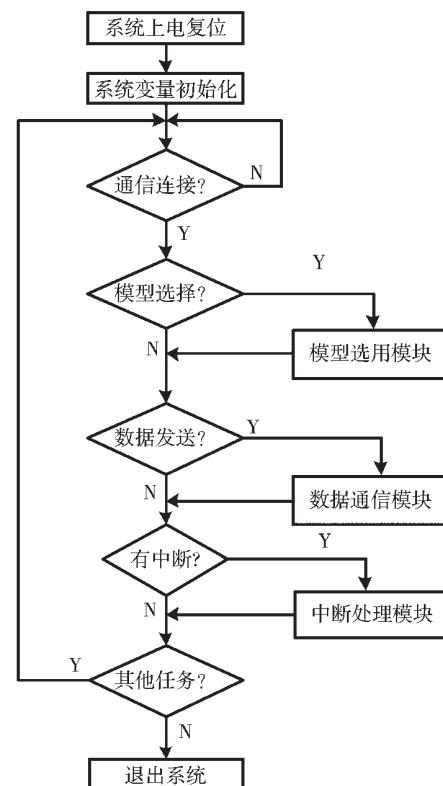

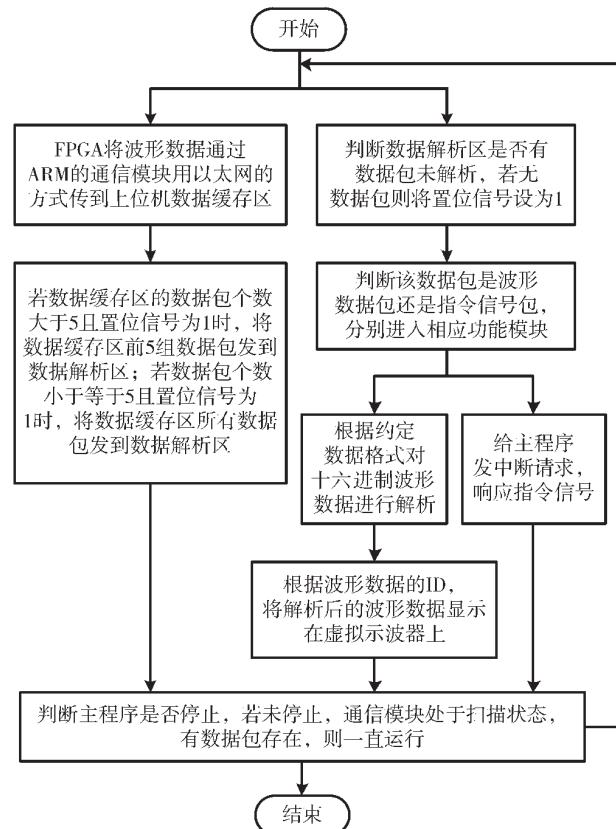

其软件的功能设计主要包括三大模块,分别为模型选用和参数设置模块、虚拟示波器模块和以太网通信及数据处理模块,可实现仿真启停控制、模型拓扑图显示、数据存储及追溯等常用功能。上位机软件主程序流程图如图2所示,中断处理模块包含了虚拟示波器模块。

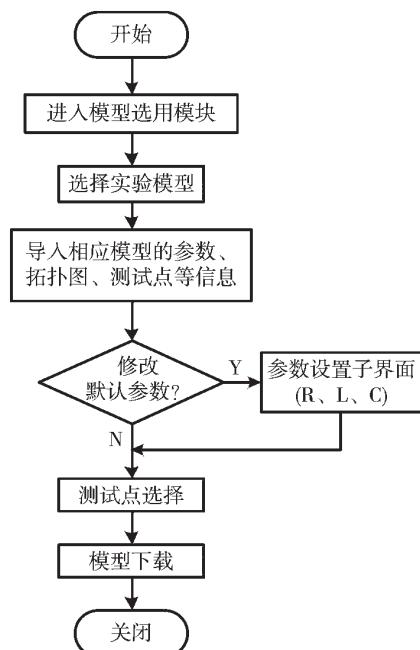

### 3.1 模型选用和参数设置模块设计

模型选用和参数设置模块负责实验所用的模型及其参数的管理,采用配置文件的方式保存各种实验模型的文件和参数信息。当导入一个模型时,通过NI的“递归文件列表”索引出该模型文件夹下所有文件名和路径,再通过“文本读取文件”和“读取JPEG文件”的控件将模型参数和拓扑图读取并显示在前面板。而且用户可以在该模块上对实验模型的参数和测试点的信息进行设置,然后将所有参数信息按变量名区分后打包传输给ARM,ARM通过协议解析变量,将其参数赋值到FPGA指定变量地址区中。FPGA中的

图2 主程序流程图

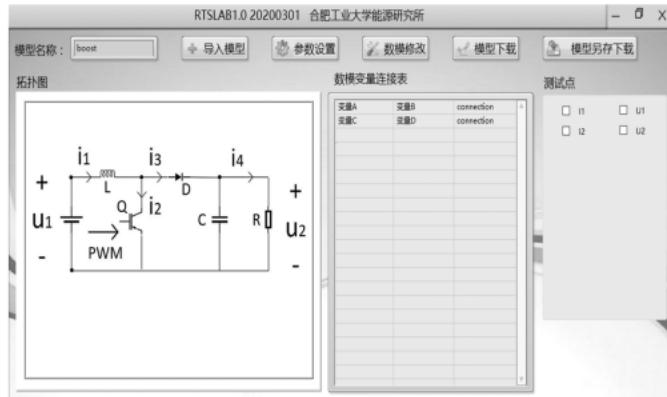

模型参数是通过读取指定变量区的值进行确定的。模型选择模块流程图如图 3 所示。上位机的 Boost 模型选用模块界面如图 4 所示。

图 3 模型选择模块流程图

图 4 Boost 模型选用模块界面

### 3.2 虚拟示波器模块设计

虚拟仪器技术是通过利用高性能的硬件和高效灵活的软件进行各种测试、自动化的应用。虚拟示波器根据这原理设计制作而成, 利用软件创建完全自定义的用户界面, 模块化硬件能方便地提供全方位的系统集成, 标准化的软硬件平台可以满足同步和定时应用的需求。本文的虚拟示波器是基于传统示波器的功能结合半实物仿真平台所需功能上进行设计的, 融合了虚拟仪器的特点, 在计算机上实现波形的显示并进行波形处理。其主要有以下功能:

#### (1) 多通道实现

根据半实物仿真平台的特点, 本文的软件设计了多通道的示波器, 可以最多同时解析 20 组数据包及其他变量

状态。选用 NI 示波器组件中的“XY 图”, 根据该示波器的特性, 开辟 20 个浮点型的二维数组, 每个二维数组对应保存着每条曲线数据和步长数据, 前 10 组保存电流曲线, 后 10 组保存电压曲线。通过图 4 的测试点的选择, 得到所需要显示曲线的变量名, 再与 ARM 传输过来的数据包对比, 得到相应测试点的曲线数据。将每条曲线数据与步长数据结合成二维数组元素, 然后将所有元素按顺序组成的新二维数组, 并赋值给示波器组件的局部变量, 进行曲线显示。

#### (2) 步长设置

步长是虚拟示波器水平方向(X 轴)上所代表的时间间隔, 也是实物模型在 FPGA 的运行步长。示波器的默认步长为该模型配置文件中的最小步长, 最小步长由事先的实验得出。也可以通过界面上的“步长设置”初步设置其步长, 当将步长信息传输到 ARM 中时, 由 ARM 对 FPGA 中的模型进行步长设置, 若设置成功, ARM 会给出上位机发送相应的置 1 信号, 若没有设置成功, 则会发 0 信号。上位机通过接收信号判断步长是否设置成功, 若成功则该设置的步长为最终步长, 而且 X 轴的相应步长变换为该值, 若失败则保持 X 轴的步长不变且弹出提示框告知需要重新设置步长。

#### (3) 波形显示、存储、清空

由于是虚拟示波器界面, 波形的显示与传统示波器有差异, 在波形显示的过程中, 通过“XY 图”示波器的“图例”和“图形控制选板”控件, 对显示的波形进行放大、缩小、局部放缩。在主程序中编写示波器的开始赋值、停止赋值、清空数据和保存数据的中断程序, 实现前面板示波器的开始和停止操作。实验完成后对实验数据进行存储和清空操作。

### 3.3 以太网通信及数据处理模块设计

#### 3.3.1 模型的下载方式

模型下载比较简单的方式是通过 JTAG 口进行烧写, 将模型固化在 FPGA 中, 即将固定的几种模型文件保存在 FPGA 的存储单元。这种方式存在着一些缺陷, 由于存储空间的限制, 模型数量有限且模型变化和扩展困难。本文的方式是模型以规定的文件数据格式存储在上位机硬盘或其他移动存储单元中, 通过以太网更新 Flash 的方式, 将模型的文件从上位机下载到 FPGA 中。

上位机会通过 LabVIEW 中的“读取文本文件”的函数来读取所选模型的 Bit 文件内容, 并通过以太网通信将模型 Bit 文件内容和 update 指令传输给 ARM。ARM 通过上位机下发的 update 的指令, 触发 ARM 的 Flash 写的函数, 将 Bit 文件内容烧到 Flash 中。

ARM 程序中需要一个单独程序负责 Flash 写的使能及关闭、Flash 擦除、Flash 读、Flash 写、读 Flash ID 等操作。当更新 Flash 结束后再反馈上位机一个下载模型是否成功的信号。

## 3.3.2 以太网通信及数据处理模块设计

核心控制板上利用 Realtek RTL8211E-VL 的以太网 PHY 芯片进行网络通信。PS 端 BANK501 的 GPIO 接口上连接着 PHY 芯片。RTL8211E-VL 芯片支持 10/100/1 000 Mb/s 传输速度的以太网, 它通过 RGMII 接口与 PS 部分的 MAC 层进行通信。RTL8211E-VL 芯片支持传输速度自适应、Master/Slave 自适应、MDI/MDX 自适应, 并且允许 MDIO 总线对 PHY 的寄存器进行管理。RTL8211E-VL 上电后会进行部分特定 IO 的电平的状态检测, 从而确定其工作模式。表 1 为 PHY 芯片上电后的默认设定信息。

上位机软件与 ARM 通信的过程中, 上位机作服务器, ARM 作客户端, 上位机设置端口号进行监听, ARM 通过 IP 地址和端口号连接上服务器。通信的数据分为控制指令、参数数据、模型文件内容和波形数据, 上位机与 ARM 通信的数据格式都是字符串, 为了保证消息传输过程不会失真, 两边的程序都针对传输数据进行头尾固定字符串校验和整个数据长度进行校验, 如果校验不通过, 则放弃这个包的数据。以太网通信模块数据处理程序流程图如图 5 所示。

为了避免通信过程中存在数据解析速率问题导致的丢包问题, 上位机采用并行数据处理方法。设立了数据缓存区和数据解析区, 数据解析区无数据包解析时给置位信号, 数据缓存区不断地接收下位机传送的数据包, 当出现置位信号时, 将前 5 组数据包发给数据解析区。FPGA 读取的 1 个波形数据由 4 个 16 进制的数据组成, 出于提高下位机工作效率的考虑, ARM 程序并未对数据进行解析处理, 直接将数据打包传给上位机。因此, 上位机软件对波形数据进行单独的算法解析。

表 1 PHY 芯片默认配置值

| 配置 Pin 值   | 说明                       | 配置值                     |

|------------|--------------------------|-------------------------|

| PHYAD(2:0) | MDIO/MDC 模式的 PHY 地址      | PHY Address 为 001       |

| SELRGV     | RGMII 1.8 V 或 1.5 V 电平选择 | 1.8 V                   |

| AN(1:0)    | 自协商配置                    | (10/100/1 000 Mb/s) 自适应 |

| RX Delay   | RX 时钟 2 ms 延时            | 延时                      |

| TX Delay   | TX 时钟 2 ms 延时            | 延时                      |

## 4 Buck 电路模型实验

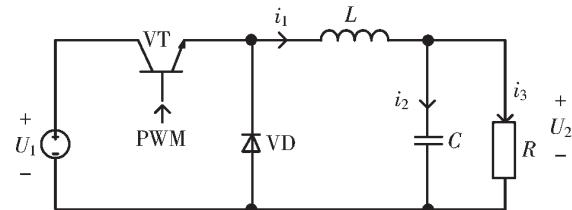

Buck 电路是一种常用的 DC/DC 变换的基本电路。下面是以 Buck 电路模型为例进行的实验验证, Buck 电路拓扑图如图 6 所示。PWM 驱动信号由外置信号发生器提供<sup>[15]</sup>。

将 PWM 信号频率设为 100 kHz, 占空比为 0.4。将下位机与上位机连接在同一网络下, 运行上位机时, 点击“模型选择”按钮, 进入图 4 界面, 点击“导入模型”并选用 Buck 模型。在上位机将参数分别设置为:  $U_1=12$  V,  $R=5 \Omega$ ,  $L=200 \mu\text{H}$ ,  $C=50 \mu\text{F}$ , 步长设置为 0.25  $\mu\text{s}$ 。然后

图 5 以太网通信模块数据处理程序流程图

图 6 Buck 电路拓扑图

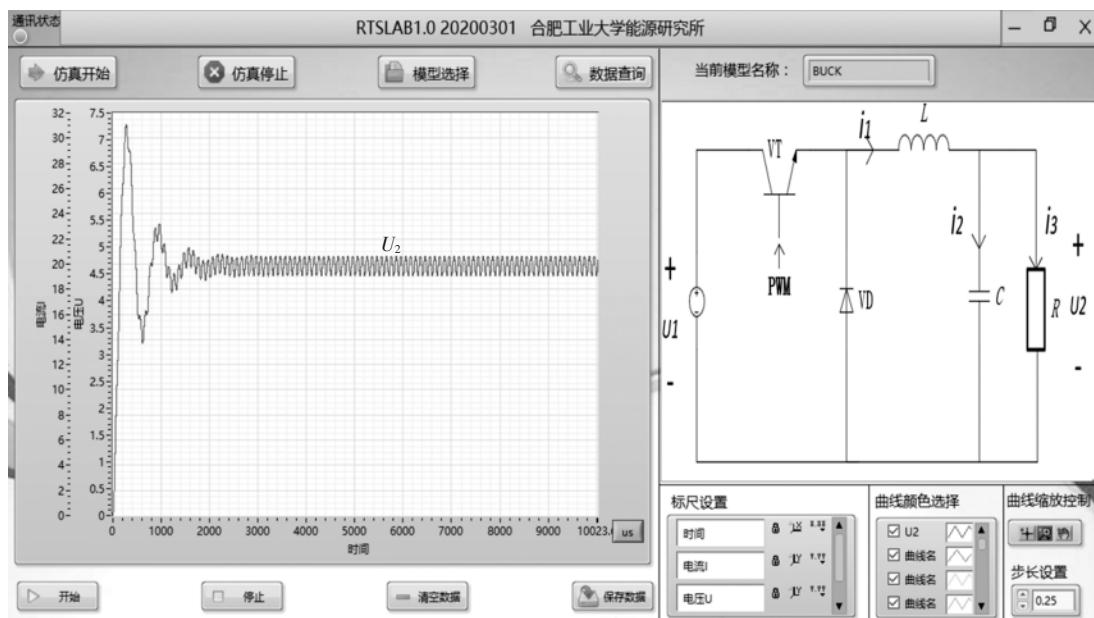

选择  $U_2$  为测试点, 点击“下载模型”, 在图 7 所示的前面板中先点击“仿真开始”按钮然后点击左下角的“开始”按钮, 仿真开始运行, 并有  $U_2$  的曲线输出显示。

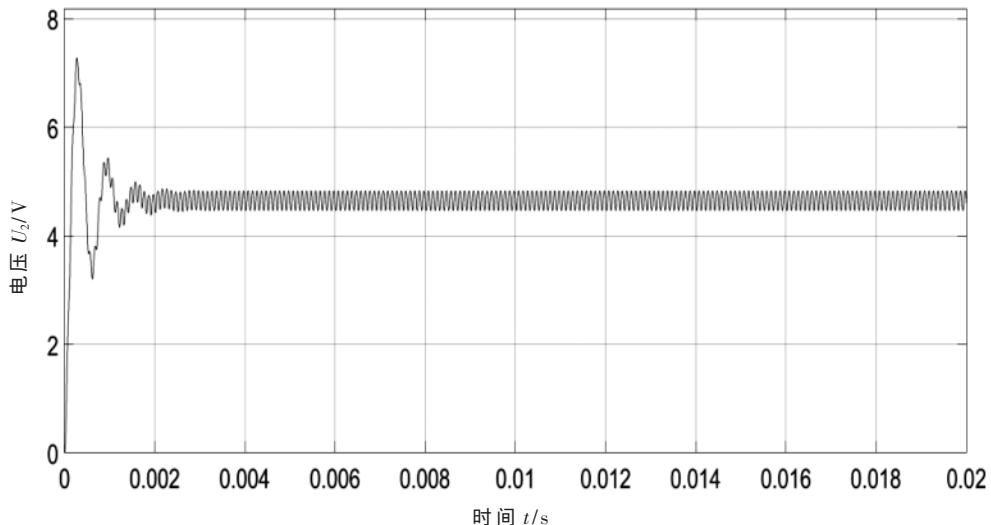

为验证实时仿真波形的正确性, 在 MATLAB 环境下进行了同样参数的仿真, 并与半实物实时仿真平台上的同一测试点波形进行了对比, 图 8 为 MATLAB 离线仿真波形。图 7 为上位机实时仿真波形, 表 2 为实验波形分析表, 对比实验表明, 该实时仿真结果是正确的, 说明实验仿真平台达到设计要求。

## 5 结论

基于 LabVIEW 上位机软件和 FPGA 设计的电力电子半实物实时仿真教学实验平台, 其操作灵活性和性能指标满足教学与科研需求。利用 LabVIEW 实现模型下载、参数设置以及仿真启停等控制指令的下发, 并接收 ARM 程序通过以太网上传的数据, 在虚拟示波器上显

图 7 上位机电压  $U_2$  实时仿真波形图 8 MATLAB 电压  $U_2$  仿真波形

表 2 实验波形分析表

| 实验类型   | 峰值电压/V | 稳定电压/V | 峰值电压时刻/μs | 稳定电压时刻/μs |

|--------|--------|--------|-----------|-----------|

| MATLAB | 7.28   | 4.65   | 275       | 2 742     |

| 实时仿真   | 7.28   | 4.65   | 275       | 2 742     |

示相应曲线波形,具有模型扩展方便、功能扩展容易等特点。利用 FPGA 的高速运算能力对模型进行迭代计算,并将得到的数据进行打包处理,通过以太网上传给上位机软件,实现了实时仿真的快速性和各点波形上传。上位机系统的设计主要包括了三大功能模块:模型选用和参数设置模块、虚拟示波器模块和以太网通信及数据处理模块。相比于将模型固化于 FPGA 中的设计方法,提出的通过以太网更新 Flash 的方式将模型文件从上

位机下载到 FPGA 中,解决了模型数量有限且模型变化和扩展困难问题。系统通过典型 Buck 电路模型 HIL 实时仿真实验,步长为 250 ns,验证了实验平台的准确性。

#### 参考文献

- [1] 王坚.电力电子系统硬件在回路仿真技术的探讨[J].大功率变流技术,2011(2):1-5,21.

- [2] 黄雨可,徐军,虞江航.基于 RCP 的嵌入式快速开发及半实物仿真技术[J].电子技术应用,2019(6):120-124,129.

- [3] 何海兴,王坚.基于 dSPACE 半实物仿真平台的永磁同步电动机数学模型的实现[J].变流技术与电力牵引,2006(5):40-45.

- [4] 王晓东,董新民,姚崇.基于 xPC 的飞行控制系统半实物仿真设计[J].传感器与微系统,2011,30(2):122-124.

- [5] 许为,应婷,李卫红.电力电子半实物仿真技术及其发

- 展[J].大功率变流技术,2014(6):1-5.

- [6] 张栋宇.基于FPGA的半实物仿真平台设计与应用[D].南京:南京大学,2016.

- [7] 刘延斌,金光.半实物仿真技术的发展现状[J].光机电信息,2003(1):27-32.

- [8] 黄建强,鞠建波.半实物仿真技术研究现状及发展趋势[J].舰船电子工程,2011(7):5-7,25.

- [9] 郑国,杨锁昌,张宽桥.半实物仿真技术的研究现状及发展趋势[J].舰船电子工程,2016,36(11):8-11.

- [10] 周瑜,张文能.电气控制与PLC技术半实物仿真实训装置构建[J].实验室研究与探索,2017,36(7):230-234.

- [11] 仇佳捷,包涌金,张峰,等.基于半实物仿真技术的复杂电系统设备检测平台的硬件设计[J].电测与仪表,2012,49(4):92-96.

- [12] 赵硕峰,张娟.基于LabVIEW平台的嵌入式光谱强度检测系统设计[J].电子技术应用,2017,43(6):90-93.

- [13] 孙玉环,李永红,岳凤英,等.基于LabVIEW的弹载计算

机测试系统[J].电子技术应用,2015,41(6):55-58.

- [14] 徐创,王建成,卫东.基于LabVIEW与CAN总线通讯的燃料电池监控系统设计[J].电源技术,2018,42(7):1015-1017.

- [15] 杨亚泽,余明杨.BUCK变换器的建模和仿真研究[J].大众科技,2010(6):37-38.

(收稿日期:2021-01-08)

#### 作者简介:

疏成成(1994-),通信作者,男,硕士研究生,主要研究方向:燃料电池技术和半实物仿真技术,E-mail:779325981@qq.com。

苏建徽(1964-),男,博士,教授,主要研究方向:光伏发电技术、分布式发电技术等。

施永(1985-),男,博士,主要研究方向:分布式发电与电力电子技术。

扫码下载电子文档

(上接第56页)

- [7] CHEN C, YI H, WAYNE L, et al. A high voltage analog multiplexer with digital calibration for battery management systems[C]//Proceedings of the 2012 IEEE International Conference on IC Design & Technology, 2012.

- [8] CHEN C L, WANG D S, LI J J, et al. A voltage monitoring IC with HV multiplexer and HV transceiver for battery management systems[J]. IEEE Trans. Very Large Scale Integr. (VLSI) Syst., 2015, 23(2): 244-253.

- [9] LEE T. HV switch using differential voltage shaping driver for 13 series li-ion battery cells BMS[C]//Proceedings of the 2016 International SoC Design Conference(ISOCC), 2016.

- [10] KWOK P N, LEE M C, WAN T C, et al. Universal high voltage multiplexer for CMOS OTP memory applications[C]//Proceedings of the 2008 IEEE International Conference on Electron Devices and Solid-State Circuits, Hong Kong, China, 2008.

- [11] ADAMS D A, BARNES H A, FITZPATRICK M D, et al. A radiation hardened high voltage 16:1 analog multiplexer for space applications(NGCP3580)[C]//Proceedings of the 2008 IEEE Radiation Effects Data Workshop, 2008.

- [12] HARA K, SAKANO J, MORI M, et al. A new 80 V 32×32ch low loss multiplexer LSI for a 3D ultrasound imaging system[C]//Proceedings of the Proceedings ISPSD'05 The

17th International Symposium on Power Semiconductor Devices and ICs, 2005.

- [13] BORG J, JOHANSSON J. An ultrasonic transducer interface IC with integrated push-pull 40 Vpp, 400 mA current output, 8-bit DAC and integrated HV multiplexer[J]. IEEE Journal of Solid-State Circuits, 2011, 46(2): 475-484.

- [14] GUANZIROLI F, PASSI S, TERENZI M, et al. New generation of high voltage integrated devices for ultrasound: 16 Channels pulser 5 levels with integrated transmit beamformer and 64 independent HV switches[C]//Proceedings of the 2017 IEEE International Ultrasonics Symposium(IUS), 2017.

- [15] RICOTTI G, BOTTAREL V. HV floating switch matrix with parachute safety driving for 3D echography systems[C]//Proceedings of the ESSCIRC 2018-IEEE 44th European Solid State Circuits Conference(ESSCIRC), 2018.

- [16] 张建人.超大规模集成电路设计基础[J].电子技术应用,1991(5):41.

(收稿日期:2021-03-08)

#### 作者简介:

李明明(1996-),男,硕士研究生,主要研究方向:模拟集成电路设计。

潘文光(1983-),通信作者,男,博士,副研究员,主要研究方向:模拟集成电路设计,E-mail:panwenguang@csmic.ac.cn。

扫码下载电子文档

## 版权声明

经作者授权，本论文版权和信息网络传播权归属于《电子技术应用》杂志，凡未经本刊书面同意任何机构、组织和个人不得擅自复印、汇编、翻译和进行信息网络传播。未经本刊书面同意，禁止一切互联网论文资源平台非法上传、收录本论文。

截至目前，本论文已经授权被中国期刊全文数据库（CNKI）、万方数据知识服务平台、中文科技期刊数据库（维普网）、DOAJ、美国《乌利希期刊指南》、JST 日本科技技术振兴机构数据库等数据库全文收录。

对于违反上述禁止行为并违法使用本论文的机构、组织和个人，本刊将采取一切必要法律行动来维护正当权益。

特此声明！

《电子技术应用》编辑部

中国电子信息产业集团有限公司第六研究所