# Buck 芯片缓冲电路设计的仿真分析与应用 \*

叶丰华, 刘昊, 康磊, 蔡文波

(浪潮电子信息产业股份有限公司 浪潮高效能服务器和存储技术国家重点实验室, 北京 100086)

**摘要:** Buck 型变换器的开关点是外部调优的主要对象, 随着开关频率的提高和负载电流的增大, 芯片内的寄生电感对开关电压波形的影响越来越大, 外部缓冲电路作为调整开关波形的工具起到关键的作用, 仅仅依靠经验来设计外部缓冲电路已经无法满足设计要求。通过对缓冲电路的工作原理进行分析, 结合仿真结果和工程实践, 分析缓冲电路的稳压性能和效率损失, 可以为外围缓冲电路的设计提供一种量化分析方法。

**关键词:** Buck 型变换器; 仿真; 缓冲电路; 效率

中图分类号: TN492

文献标识码: A

DOI: 10.16157/j.issn.0258-7998.211421

中文引用格式: 叶丰华, 刘昊, 康磊, 等. Buck 芯片缓冲电路设计的仿真分析与应用[J]. 电子技术应用, 2021, 47(10): 113–117, 123.

英文引用格式: Ye Fenghua, Liu Hao, Kang Lei, et al. Simulation analysis and application of buck chip buffer circuit design[J]. Application of Electronic Technique, 2021, 47(10): 113–117, 123.

## Simulation analysis and application of buck chip buffer circuit design

Ye Fenghua, Liu Hao, Kang Lei, Cai Wenbo

(State Key Laboratory of Inspur High Efficiency Server and Storage Technology, Inspur Electronic Information Industry Co., Ltd., Beijing 100086, China)

**Abstract:** The switching point of the buck converter is the main object of external tuning. With the increase of the switching frequency and the increase of the load current, the parasitic inductance in the chip has an increasing influence on the switching voltage waveform, and the external buffer circuit is used as the adjustment switch. The waveform tool plays a key role, and only relying on experience to design the external buffer circuit can no longer meet the design requirements. By analyzing the working principle of the buffer circuit, combined with simulation results and engineering practice, this paper analyzes the voltage regulation performance and efficiency loss of the buffer circuit, and provides a quantitative analysis method for the design of the peripheral buffer circuit.

**Key words:** buck converter; simulation; snubber; efficiency

## 0 引言

Buck 芯片工作的基本原理是将高输入电压斩波成具有一定占空比的周期脉冲, 之后再通过 LC 滤波器将周期脉冲整合成稳定的低压直流电<sup>[1-3]</sup>。

传导高压脉冲信号的位置称为 Phase 点, 常用 Buck 电源的典型参数为开关频率 500 kHz, 输入电压 12 V。Phase 点在 500 kHz, 0 V~12 V 脉冲的作用下, 成为了一个不可忽略的噪声源。

为了降低开关损耗, 当前开关电源的 MOSFET 开关速度非常快, 即 Phase 点波形的上升沿和下降沿的斜率很高。芯片内的寄生电感(ESL)在这样的激励下能够在 Phase 点产生很大的过冲(Overshoot)<sup>[4-5]</sup>, Phase 点过高的 Overshoot 会超过下管 MOSFET 的耐压值, 造成 MOSFET 过压损坏<sup>[6-8]</sup>, 使用缓冲电路可以削弱过冲对电路器件

的负面影响。

本文通过对缓冲电路的缓冲效果进行比较分析, 结合 Buck 芯片中不同的缓冲方法下测得的电源效率, 在仿真结果的辅助下评价两种缓冲方式的性能, 探究缓冲电路的设计技巧, 作为指导 Buck 芯片缓冲电路设计的方法。

### 1 Buck 开关电源中缓冲电路的设计

为 Phase 点到 GND 设置缓冲吸收电路可以吸收 Phase 波形中的高频噪声, 降低电压过冲和电磁辐射<sup>[9]</sup>。使用缓冲电路延缓开关速度, 同样能够起到抑制 Phase 点电压过冲的作用<sup>[10]</sup>。

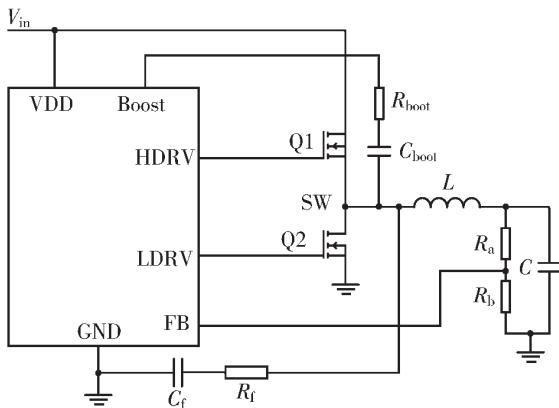

#### 1.1 Buck 开关电源原理

Buck 开关电源的基本原理如图 1 所示。控制 IC 分别控制 Q1、Q2 两个 MOSFET 的开关, 当 Q1 导通 Q2 断开时,  $V_{in}$  通过导通的 Q1 将能量传输到输出电感 L, 输出电容 C 和负载。当 Q1 断开 Q2 导通时, 因为电感和电

\* 基金项目: 国家重点研发计划项目(2017YFB1001700)

图 1 Buck 型变换器原理示意图

容当中储存了能量,且因为电感的惯性不能允许电流的突变,会维持向负载端供电的状态,将电感中储存的能量传递到负载,Q2 此时起到续流通路的作用<sup>[11]</sup>。

图 1 中共有两处应用了缓冲电路,SW 点(即 Phase 点)到 BOOST 的 RC,和 SW 点到 GND 的 RC。

## 1.2 SW-GND 缓冲电路设计

Buck 开关电源的 Phase 波形出现过冲和震荡的直接原因是寄生参数,如 ESL(寄生电感)、等效电阻、电容等,这些参数无法避免。

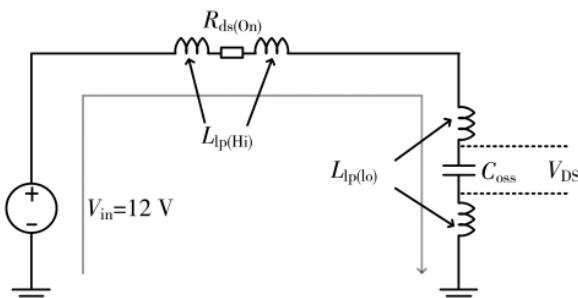

图 2 中  $L_{lp(Hi)}$  是上管 MOSFET Q1 的引线电感, $R_{ds(on)}$  是上管 Q1 导通时的电阻值。 $L_{lp(lo)}$  是下管 MOSFET Q2 引线电感, $C_{oss}$  是下管 Q2 的 DS 两级之间的等效电容,当  $C_{oss}$  被充电,其上的电压为  $V_{DS}$ <sup>[12]</sup>。

图 2 等效寄生参数电路

当上管导通时,等效于  $V_{in}$  通过图 2 的通路对下管 Q2 的寄生电容  $C_{oss}$  充电从而产生  $V_{DS}$  的波形, $V_{DS}$  就是 Phase 点的波形。

由于图 2 的通路中存在电感电容和电阻,因此当上管导通时,即便  $C_{oss}$  已经上升至  $V_{in}$ ,电感因为惯性还会继续给  $C_{oss}$  充电,形成过冲。

研究上管导通下管断开的瞬间,此时由于 Q1 突然的导通,导致回路上寄生电感储存了能量,根据能量守恒定理,电感中储存的能量转移到电容中,得到:

$$\frac{1}{2}L_{lp(Hi)}i_{qrr}^2 = \frac{1}{2}C_{oss}v_p^2 \quad (1)$$

式(1)中  $i_{qrr}$  是通过下管 MOSFET 的最大电流, $v_p$  是

下管 MOSFET 上的最大波动电压,求  $v_p$  的表达式叠加基准输入电压得到:

$$V_{PK} = V_{in} + \sqrt{\frac{L_{lp(Hi)}i_{qrr}^2}{C_{oss}}} \quad (2)$$

其中  $V_{PK}$  是过冲电压的最大值, $V_{in}$  是输入电压的大小,输入电压叠加最大波动电压得到最大过冲电压。 $i_{qrr}$  是 MOSFET 体二极管的反向恢复电流,这个电流是下管 MOSFET 寄生二极管反转过程中的最大值电流,由此确定了 SW 点波形的最大过冲。

式(2)中的寄生电感  $L_{lp(Hi)}$  和电流  $i_{qrr}$  通常在芯片内进行补偿。芯片外,可以在 SW 点和 GND 之间加入一个电容  $C_f$ ,该电容  $C_f$  和  $C_{oss}$  形成并联的关系,能够等效地增加  $C_{oss}$  的大小,从而也能够抑制最大过冲的峰值。由此确定,SW 到 GND 加入电容  $C_f$  的做法能够优化过冲电压。

被吸收的能量不会损耗在抗性元件上,而是耗散在电阻上,为了将电容吸收的过冲能量耗散,并且易于控制缓冲器的整体阻抗,则在  $C_f$  通路上再串联一个  $R_f$ ,最终的做法是在 SW 和 GND 之间加入一个  $RC$  串联电路。

站在频域的角度分析  $C_f$  电容的选型,电容滤波的本质基于电容的频域阻抗曲线,常在某一频率达到低至  $10\text{ m}\Omega \sim 100\text{ m}\Omega$  的阻抗,这样的低阻抗能够用于吸收特定频段的噪声<sup>[13]</sup>。

根据电容频域阻抗公式结合  $R_f$  得到缓冲电路阻抗:

$$Z_f = \sqrt{\left(\frac{1}{2\pi f C_f}\right)^2 + R_f^2} \quad (3)$$

其中  $Z_f$  是整个缓冲电路的频域阻抗, $f$  是频率。

去除所有的缓冲设计,测试 phase 波形中的噪声振荡频率  $f$ ,为滤除该噪声令该频段下电容阻抗小于  $100\text{ m}\Omega$ ,可供选择的电容容值即可计算得到:

$$C_f = \frac{10}{2\pi f} \quad (4)$$

联系式(4)知,足够大的  $C_f$  能够有效滤除噪声,但是不能太过偏离上式所计算出的电容值,否则滤波的频段会产生偏差。

虽然使用缓冲电路能够滤除噪声降低过冲,但本质上是在消耗功率,SW-GND 缓冲电路必然会在一定程度上影响开关电源的效率,这在对于开关电源效率要求甚高的应用场合提出了挑战,研发人员需要既达到缓冲性能的要求,又不对效率造成明显的损失。

$V_{in}$  通过输入点到 SW 点的电感  $L_{lp(Hi)}$  对下管 MOSFET 的 DS 电容  $C_{oss}$  充电,后级电路是与之并联的缓冲电路  $R_f$  和  $C_f$ 。面对上管 MOSFET 的突然打开,上述电路会产生阶跃响应, $C_f$  上的电压  $U_{cf}$  将会产生变化,通过  $R_f$  的部分将会产生功耗损失:

$$Q = \int_0^t (C_f \frac{dU_{cf}}{dt})^2 R_f dt \quad (5)$$

其中  $Q$  是缓冲电路产生的功耗, $t$  是计时时间,该缓冲电路产生的功率损失与  $C_f$ 、 $R_f$  的大小正相关。

### 1.3 BOOST 缓冲电路设计

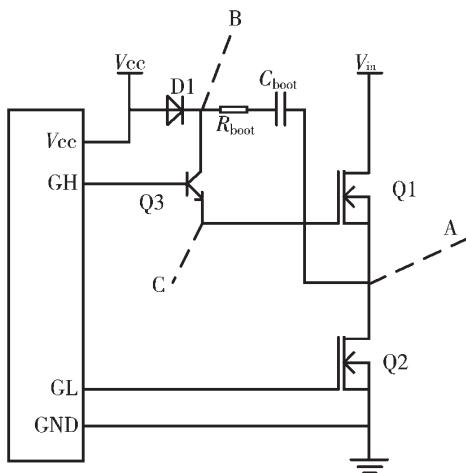

Buck 芯片驱动原理如图 3 所示。

图 3 Buck 芯片驱动电路简图

GH 和 GL 发出的驱动信号分别驱动 Q1 和 Q2，输出信号 GH 经过射极跟随器后驱动 Q1。射极跟随器的工作电源由自举电路  $RC$  提供，当下部开关 Q2 导通时，通过 D1 给  $C_{boot}$  充上电压  $V_{cc}$ 。当上部开关 Q1 导通时，B 点和 A 点的电压都上升，但是压差  $V_{BA}$  保持不变，被抬升的 B 点电压将成为射极跟随器的工作电压<sup>[14-15]</sup>。

射极跟随器导通后，相当于  $C_{boot}$  对 Q1 的 GS 之间的寄生电容  $C_{gsh}$  充电，其上的电压为  $v_{gsh}$ ，用  $V_{boot}$  表示  $C_{boot}$  上的电压，则 Q1 导通的过程相当于  $C_{boot}$  中的初始电压  $V_{boot}$  经过  $R_{boot}$  向  $C_{gsh}$  充电的过程，使得  $v_{gsh}$  达到  $U_{GS(th)}$  之后 MOSFET 即可导通。

当  $C_{boot}$  远大于  $C_{gsh}$  时， $C_{gsh}$  的充电方程满足：

$$v_{gsh} = V_{boot} \left(1 - e^{-\frac{t}{C_{gsh}R_{boot}}}\right) \quad (6)$$

MOSFET 的漏极电流  $i_D$  和 GS 之间电压  $v_{gsh}$  的关系式如下：

$$i_D = I_{D0} \left(\frac{v_{gsh}}{U_{GS(th)}} - 1\right)^2 \quad (7)$$

其中  $I_{D0}$  是  $v_{gsh}=2U_{GS(th)}$  时的  $i_D$ ，该方程可以体现一个 MOSFET 开启快慢，Phase 波形的最大波动  $v_p$  和  $i_D$  的关系是：

$$v_p = L_{ip(Hi)} \frac{d \left[ \frac{I_{D0}V_{boot}(1 - e^{-\frac{t}{C_{gsh}R_{boot}}})}{U_{GS(th)}} - 1 \right]^2}{dt} \quad (8)$$

所以更改  $R_{boot}$  可以通过改变 MOSFET 的开启速度达到限制过冲的效果。

当不满足  $C_{boot}$  远大于  $C_{gsh}$  时， $v_{gsh}$  最终稳定电压是：

$$v_{gsh} = \frac{C_{boot}V_{boot}}{C_{boot} + C_{gsh}} \quad (9)$$

只有当  $C_{boot}$  远大于  $C_{gsh}$  时，式(9)才成立，此时  $V_{boot}$  近似于不变， $C_{boot}$  可近似为理想电压源。增大  $C_{boot}$  放电的时

间常数，可以保证上管导通时间内  $V_{boot}$  只有较小的波动，但在实际应用中， $V_{boot}$  总会产生一定的跌落，为了确保电压跌落不影响 MOSFET 正常导通，工程上认为  $V_{boot}$  波动不可超过 5%。根据式(10)：

$$i_{BST} = C_{boot} \frac{V_{boot(D)}}{t_{on}} \quad (10)$$

式中  $i_{BST}$  是  $C_{boot}$  的放电电流，芯片数据手册中可以查找到其最大值； $V_{boot(D)}$  是在上管导通时间内  $V_{boot}$  的变化； $t_{on}$  是指上管导通的时间。若已知 Buck 电源的占空比  $D$ ，初始驱动电压  $V_{cc}$ ，开关频率  $f$ ，则可以计算出  $C_{boot}$  的最小值：

$$C_{boot_{min}} = i_{BST} \frac{20D}{fV_{cc}} \quad (11)$$

为了保证当上管断开，下管导通时， $V_{cc}$  能够快速完成对  $C_{boot}$  的充电， $R_{boot}C_{boot}$  的时间常数  $\tau$  不宜过大，工程上认为至少要使  $C_{boot}$  在下管导通的 10% 时间内完成充电，利用式(12)可以求出  $C_{boot}$  的最大值：

$$3\tau \leq \frac{1-D}{10f} \quad (12)$$

MOSFET 在开关过程中会产生开关损耗，其根本在于每次 MOSFET 的开关变换都不可避免地存在 V-I 交叠。MOSFET 的每个极间电容在每个开关过程中需要充放电，以完成整个开关过程，所以 V-I 交叠会持续一定的时间。当电容越大，充电时间就会增大，MOSFET 开启速度更慢，V-I 交叠时间越长，结果导致开关损耗变大，可以计算 MOSFET 开启至 V-I 交叠完成之前的时间<sup>[16]</sup>表示如下：

$$T_x = V_{in} \frac{R_{boot}C_{gsh}}{V_{boot} - (U_{GS(th)} + \frac{I_0}{g})} \quad (13)$$

其中， $C_{gsh}$  是 MOSFET 的 GD 两极之间的电容， $I_0$  是负载电流， $g$  是 MOSFET 的跨导。在其他条件保持一致的情况下，当增大  $R_{boot}$  以减缓 MOSFET 导通速度时，则必然增加 V-I 交叠的时间，从而导致功率损耗的增加。

### 2 Buck 芯片缓冲电路的仿真

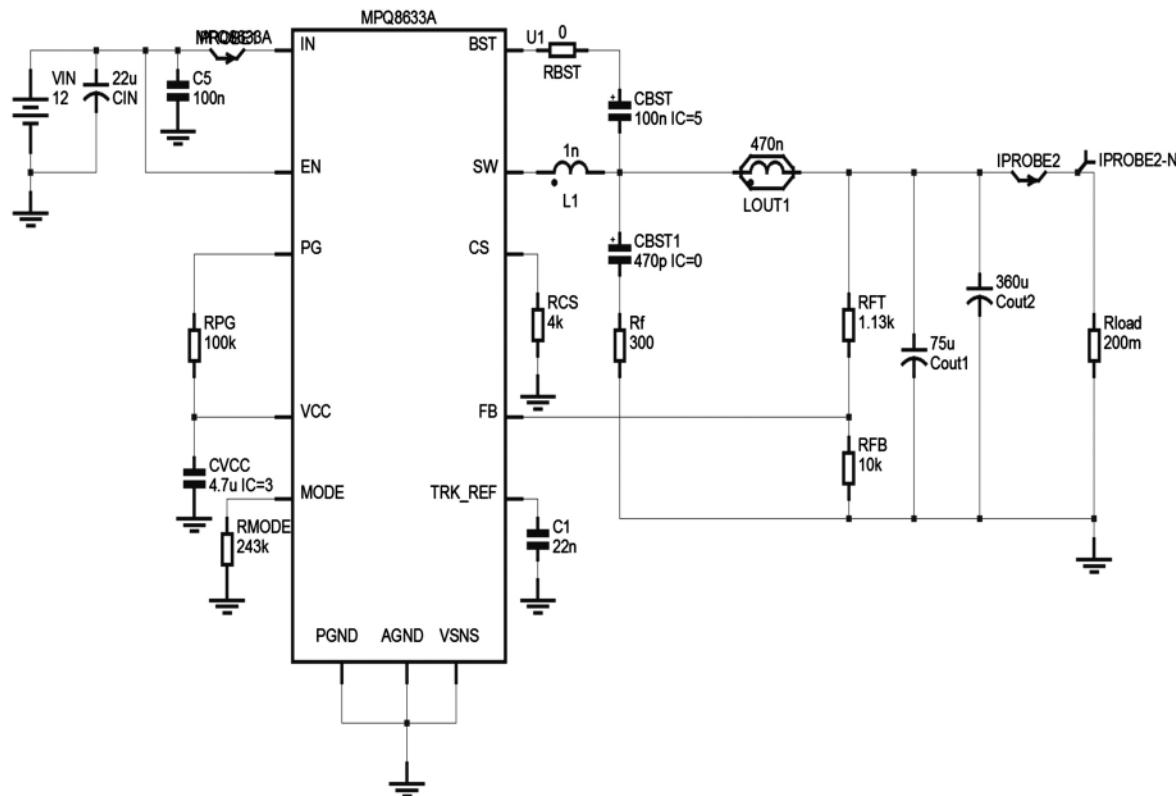

以常用系统电供电为例，Buck 变换器由控制器 MPQ8633A 和外围元件组成，输入电压  $V_{in}$  为 12 V，输出电压  $U_0=0.6$  V。Buck 型变换器仿真原理如图 4 所示，原理图中的  $R_f$  和  $C_f$  即所述 SW-GND 缓冲电路， $R_{BST}$  和  $C_{BST}$  即所述 BOOST 缓冲电路中的  $R_{boot}$  和  $C_{boot}$ 。

#### 2.1 Buck 芯片 SW-GND 缓冲电路仿真

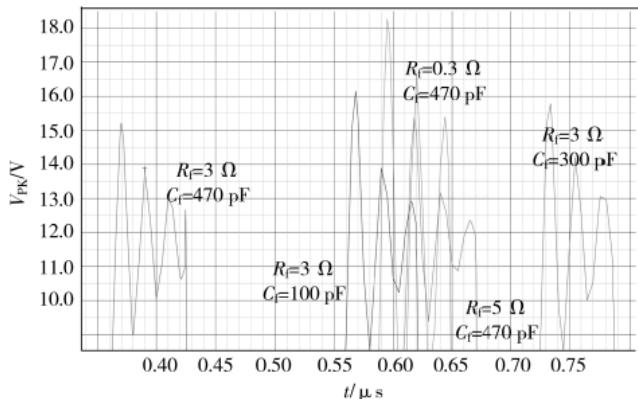

不调整  $C_{BST}$  和  $R_{BST}$ ，仿真观察不同  $R_f$  和  $C_f$  对于 Phase 波形的影响结果如图 5 所示。

将仿真波形的最大过冲电压值进行统计，列表比较不同  $R_f$  和  $C_f$  对于 Phase 波形的影响，如表 1 所示。其中， $V_{PK}$  是指过冲最高电压值，eff 是指电源芯片的转换效率。

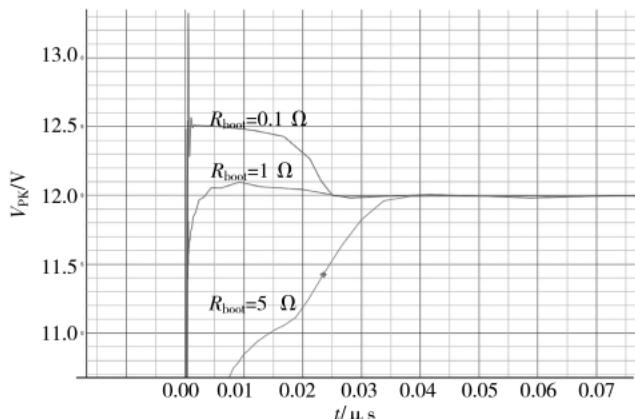

#### 2.2 Buck 芯片 BOOST 缓冲电路仿真

不调整  $R_f$  和  $C_f$ ，仿真观察不同  $R_{BST}$  对于 phase 波形过冲的影响，结果如图 6 所示。

图 4 Buck 型变换器仿真原理图

图 5 SW-GND 缓冲电路仿真波形

表 1 SW-GND 缓冲电路仿真

| 参数       | $R_f/\Omega$ | $C_f/pF$ | $V_{pk}/V$ | eff/% |

|----------|--------------|----------|------------|-------|

| 固定 $R_f$ | 3            | 100      | 16.144     | 87.7  |

|          | 3            | 300      | 15.778     | 86.4  |

|          | 3            | 470      | 15.219     | 85.6  |

| 固定 $C_f$ | 0.3          | 470      | 18.256     | 85    |

|          | 3            | 470      | 15.219     | 85.6  |

|          | 5            | 470      | 15.371     | 85.65 |

将仿真波形的最大过冲电压值进行统计,列表比较不同 RBST 对于 Phase 波形的影响,如表 2 所示。

仿真数据说明,针对 SW-GND 缓冲电路,  $C_f$  越大,越能够抑制波形的震荡过冲。 $R_f$  过小会使缓冲电路处于

图 6 BOOST 缓冲电路仿真波形

表 2 BOOST 缓冲电路仿真

| 参数           | $R_{bst}/\Omega$ | $C_{bst}/nF$ | $V_{pk}/V$ | eff/% |

|--------------|------------------|--------------|------------|-------|

| 固定 $C_{bst}$ | 0.1              | 100          | 13.247 5   | 84.8  |

|              | 1                | 100          | 12.512 5   | 82.1  |

|              | 6                | 100          | 12.071 1   | 79.7  |

欠阻尼状态,延长震荡时间,增大过冲; $R_f$  过大会增大滤波频域阻抗,降低滤波效果,也会增大过冲。缓冲电路能够影响电源的输出效率,由于  $C_f$  的变化决定了滤波频段,因此在更大程度上影响了效率,而  $R_f$  决定了针对目标频段的滤波效果。针对 BOOST 缓冲电路,增大  $R_{bst}$  的阻值能够延缓 MOSFET 的驱动电压上升速率,从而影响

MOSFET 的导通快慢,进而有效优化 Phase 电压过冲。

总的来看,BOOST 缓冲电路能够更好地降低电压过冲,但却产生了不可接受的效率损失。

### 3 Buck 芯片缓冲电路的实验

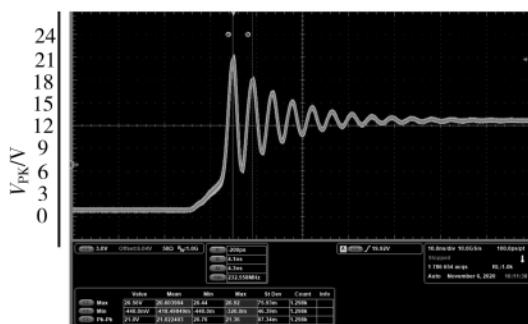

在上述仿真电路参数完全对应的实际 PCB 电路板上进行电源测试,根据仿真和前述理论计算,调整 Buck 电源中的对应器件,测试不同条件下的 Phase 波形。

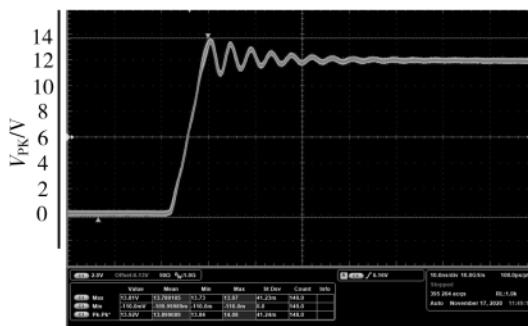

首先测试没有外部缓冲设计的 Phase 波形,并测得效率  $P_1$ ,如图 7 所示。

图 7 无外部缓冲的 Phase 波形

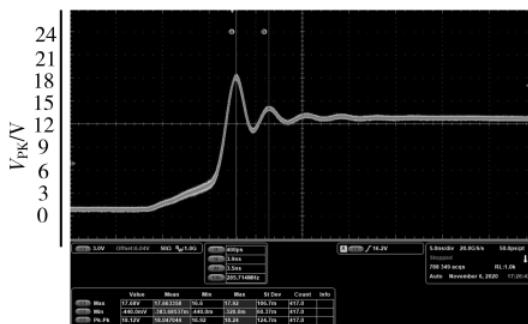

加入 SW-GND 缓冲电路,  $C_f=470 \text{ pF}$ ,  $R_f=3 \Omega$ , 测得波形,并测得效率  $P_2$ ,如图 8 所示。

图 8 SW-GND 缓冲的 Phase 波形

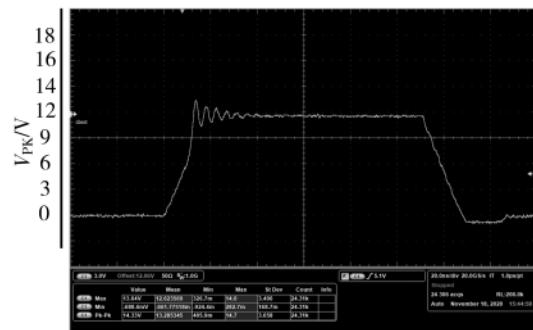

使用 BOOST 缓冲电路,  $R_{\text{BST}}=1 \Omega$ ,  $C_{\text{BST}}=0.1 \mu\text{F}$ , 测得波形,并测得效率  $P_3$ ,如图 9 所示。

图 9 BOOST 缓冲的 Phase 波形 1

更换为  $R_{\text{BST}}=6 \Omega$ ,  $C_{\text{BST}}=0.1 \mu\text{F}$ , 测得效率  $P_4$ ,如图 10 所示。

图 10 BOOST 缓冲的 Phase 波形 2

将实测结果的电压过冲值和不同负载下的电源转换效率  $P_1$ 、 $P_2$ 、 $P_3$ 、 $P_4$  列表,如表 3 所示。

表 3 实际电路板实测

|       | 电流/A  |       |       |       |       | 最大过冲/V |

|-------|-------|-------|-------|-------|-------|--------|

|       | 3     | 6     | 9     | 12    | 15    |        |

| $P_1$ | 94.84 | 92.31 | 89.73 | 87.20 | 84.65 | 20.56  |

| $P_2$ | 94.79 | 92.26 | 89.72 | 87.14 | 84.61 | 17.68  |

| $P_3$ | 93.31 | 90.15 | 87.22 | 85.14 | 83.37 | 13.81  |

| $P_4$ | 91.15 | 88.17 | 85.31 | 82.31 | 79.28 | 13.64  |

根据实测结果分析,SW-GND 缓冲电路的能够在一定程度上削弱过冲,BOOST 缓冲电路抑制过冲的能力更强,但是缓冲电路势必造成效率的损失,如果 MOSFET 在降额设计下过冲仍然可接受,尽量不要增加任何的缓冲电路以获得最高的效率。当过冲不满足 MOSFET 的降额设计时,将增加 SW-GND 缓冲电路作为首选,BOOST 缓冲电路作为次选,这与仿真结论是相符的。

### 4 结论

本文在理论上推导出两种缓冲电路的有效性和设计需求,并指出了每种缓冲电路的设计方法,基于缓冲电路对 Buck 芯片的效率损失进行仿真分析,综合比较缓冲性能和效率之间的关系,最后通过实验证明仿真分析的可行性。

运用此方法的理论计算,以仿真作为参考依据权衡缓冲效果和效率损失之间的关系,可用于指导 Buck 芯片的缓冲电路设计。

### 参考文献

- [1] BASSO P.开关电源 SPICE 仿真与实用设计[M].吕章德,译.北京:电子工业出版社,2009:23~33.

- [2] 王少斌,苏淑婧,任婷.宽输入全桥 Buck-Boost 变换器控制策略研究[J].电子技术应用,2019,45(12):110~114.

- [3] 王武军,路广,李鹏翀,等.Buck 变换器近远端反馈的仿真分析与应用[J].电子技术应用,2018,44(2):120~123.

- [4] 王其轩,王振宇,陈北辰,等.一种新型高性能开关电源的设计与实现[J].电测与仪表,2019,56(4):27~31,61.

- [5] 沈华,甄昊涵,童涛,等.MOSFET 寄生参数对 LLC 谐振变

(下转第 123 页)

效率。

利用单级变换器可实现升压、降压，且功率因数很高，开关管的反向电压与输入、输出电压中的较大者相同，因此开关管在较低的反向电压下工作，提高电路的稳定性，特别适合于高压输出的场合。

#### 参考文献

- [1] 韩京慧.基于自耦型电感和分段控制模式的特种信号灯研制[D].延吉:延边大学,2018.

- [2] 金永镐,张庆博.浮地模式 AC 宽工作电压范围的爆闪式信号灯设计[J].延边大学学报(自然科学版),2016,42(3):227–230.

- [3] 万其明,蔡教武.一种 LED 灯驱动电源功率因数校正变换器的设计[J].照明工程学报,2019,30(5):119–125.

- [4] 孙富康,解建侠,窦秋,等.交流发光二极管灯具频闪特性研究[J].灯与照明,2017,41(4):32–37.

- [5] 张潇文.电容降压桥式整流 LED 恒流电源仿真与实验[J].电子制作,2018(17):67–69.

- [6] 孙毓璞,徐玉珍,金涛.一种改进二次型高增益 Boost-Sepic 变换器[J].电源学报:1–9[2021-01-08].

- [7] 丁杰,赵世伟,文楚强.单开关低电压应力的高增益 Boost 变换器[J].电子技术应用,2019,45(12):125–128.

- [8] 丁杰,尹华杰,赵世伟.反激式隔离型高增益 DC/DC 变换器[J].电源学报:1–12[2021-03-23].

- [9] 林豪,石启元,洪峰.反激变换器平面变压器研究与设计[J].

电子器件,2020,43(5):1016–1020.

- [10] 郑玢鑫,黄煜,余小莉,等.一种适用于 SEPIC 变换器的可拓展电压增益单元电路[J].电力自动化设备,2021(4):56–63.

- [11] 刘怡宁.基于 SEPIC 电路的高频高升压比 DC/DC 变换器研究[D].哈尔滨:哈尔滨工业大学,2020.

- [12] 高珊珊,王懿杰,徐殿国.一种高频高升压比改进型 Sepic 变换器[J].电工技术学报,2019,34(16):3366–3372.

- [13] 毛兴武.高压驱动器 NCP5181 及其应用[J].电子世界,2009(4):16–17.

- [14] 王贤江,石玉,王金川.基于 SG2525 及 NCP5181 的半桥变换器[J].磁性材料及器件,2013,44(3):59–63.

- [15] 金楠.基于谐振技术及 MK 单片机的多路升压器研究设计[D].延吉:延边大学,2013.

(收稿日期:2021-03-01)

#### 作者简介:

王志凯(1997-),男,硕士研究生,主要研究方向:智能开关技术及智能变换。

张源(1998-),女,硕士研究生,主要研究方向:智能开关技术及智能变换。

金永镐(1964-),通信作者,男,博士,教授,主要研究方向:智能开关技术及智能变换,E-mail:331835200@qq.com。

扫码下载电子文档

(上接第 117 页)

- 换器性能影响研究[J].电子技术应用,2021,47(1):41–45.

- [6] 刘婷,闻心怡,陈刚,等.LLC 串联谐振式开关电源 MOSFET 故障诊断研究[J].电测与仪表,2019,57(2):147–152.

- [7] 孟茜倩,程加力,高建军.基于 MESFET 非线性模型的 MOSFET DC 建模技术[J].电子器件,2012,35(3):263–266.

- [8] 刘平,宋慧娜,刘晓芳,等.MOSFET 输出电容的非线性对振荡谐波的影响[J].微计算机信息,2007(32):283–285.

- [9] 杨伟,金华标,魏柳新,等.船用电子设备中开关电源的电磁辐射[J].中国航海,2016,39(4):34–37.

- [10] 焦堂沛,樊经纬,陈鹏,等.一种新型软开关同步 Buck 变换器的研究[J].电力电子技术,2020,54(3):108–109.

- [11] 堵国樑,吴建辉,樊兆雯,等.模拟电子电路基础[M].北京:机械工业出版社,2014.

- [12] 夏逸骁,陶雪慧.碳化硅 MOSFET 结电容模型[J].电力电子技术,2020,54(10):13–16.

- [13] 汪泉弟,安宗裕,郑亚利,等.电动汽车开关电源电磁兼

容优化设计方法[J].电工技术学报,2014,29(9):225–231.

- [14] 李冬超,戴庆元,林刚磊,等.一种应用于 DC/DC 转换器的自举电路设计[J].电子器件,2009,32(1):87–87,92.

- [15] 邓扬扬,冯全源,杨林才,等.适用于轻载高效 BUCK 转换器的自举电路设计[J].微电子学,2014,44(5):592–596.

- [16] 罗四海,娄本超,唐君,等.MOSFET 的损耗分析与工程近似计算[J].电子设计工程,2011,19(21):136–138,145.

(收稿日期:2021-02-23)

#### 作者简介:

叶丰华(1982-),男,本科,工程师,主要研究方向:服务器及关键应用主机硬件系统研发。

刘昊(1997-),通信作者,男,本科,主要研究方向:服务器电源架构设计研发,E-mail:LEOHJN@foxmail.com。

康磊(1989-),男,本科,主要研究方向:服务器电源架构设计研发。

扫码下载电子文档

## 版权声明

经作者授权，本论文版权和信息网络传播权归属于《电子技术应用》杂志，凡未经本刊书面同意任何机构、组织和个人不得擅自复印、汇编、翻译和进行信息网络传播。未经本刊书面同意，禁止一切互联网论文资源平台非法上传、收录本论文。

截至目前，本论文已经授权被中国期刊全文数据库（CNKI）、万方数据知识服务平台、中文科技期刊数据库（维普网）、DOAJ、美国《乌利希期刊指南》、JST 日本科技技术振兴机构数据库等数据库全文收录。

对于违反上述禁止行为并违法使用本论文的机构、组织和个人，本刊将采取一切必要法律行动来维护正当权益。

特此声明！

《电子技术应用》编辑部

中国电子信息产业集团有限公司第六研究所