# 基于 MIPI 规范的从端 D-PHY 数字电路设计 \*

张自豪<sup>1,2</sup>, 赵建中<sup>1</sup>, 周玉梅<sup>1,2</sup>

(1. 中国科学院微电子研究所, 北京 100029; 2. 中国科学院大学, 北京 100049)

**摘要:** 基于 MIPI D-PHY v1.1 规范, 提出了一种从端 D-PHY 数字电路设计, 该从端 D-PHY 采用 4 通道实现。高速模式下, 单通道数据传输速率最高支持 1.5 Gb/s; 低功耗模式下, 通道 0 数据传输速率最高支持 10 Mb/s。高速模式下, 串行数据流的解串由模拟电路实现, 解串后数据的帧头同步检测由数字电路实现; D-PHY 引导码的检测以及低功耗模式下数据传输为异步通信, 提出了一种异步时钟实现方式; 采用 SMIC 0.18 μm CMOS 工艺库进行综合, 典型工艺角下, 整体电路的面积为 95.061 μm<sup>2</sup>; 整体功耗为 4.291 mW, 其中低功耗模式下功耗为 231.3 μW。

**关键词:** MIPI; D-PHY; 高速模式; 低功耗模式; 异步时钟

中图分类号: TN492

文献标识码: A

DOI: 10.16157/j.issn.0258-7998.211418

中文引用格式: 张自豪, 赵建中, 周玉梅. 基于 MIPI 规范的从端 D-PHY 数字电路设计[J]. 电子技术应用, 2021, 47(11): 33-38.

英文引用格式: Zhang Zihao, Zhao Jianzhong, Zhou Yumei. Design of slave D-PHY digital circuit based on MIPI specification[J]. Application of Electronic Technique, 2021, 47(11): 33-38.

## Design of slave D-PHY digital circuit based on MIPI specification

Zhang Zihao<sup>1,2</sup>, Zhao Jianzhong<sup>1</sup>, Zhou Yumei<sup>1,2</sup>

(1. Institute of Microelectronics, Chinese Academy of Science, Beijing 100029, China;

2. University of Chinese Academy of Sciences, Beijing 100049, China)

**Abstract:** Based on the MIPI D-PHY version 1.1 specification, a design of slave D-PHY digital circuit is proposed, which is implemented with 4 lanes. In the high-speed mode, the data transfer rate of a single lane supports up to 1.5 Gb/s; in the low-power mode, the data transfer rate of lane 0 is up to 10 Mb/s. In the high-speed mode, the deserialization of the serial data stream is implemented by the analog circuit, and the synchronization detection of the data frame header after deserialization is realized by the digital circuit; the detection of the D-PHY entry code and the data transmission in the low-power mode are asynchronous communication and a kind of asynchronous clock implementation is proposed; SMIC 0.18 μm CMOS process library is used for synthesis, and at the typical process corner, the overall circuit area is 95.061 μm<sup>2</sup>; the overall power consumption is 4.291 mW, and the power consumption in low power mode is 231.3 μW.

**Key words:** MIPI; D-PHY; high speed mode; low-power mode; asynchronous clock

## 0 引言

早在 2003 年, ARM、诺基亚、德州仪器和意法半导体四家公司就预见了智能、多媒体手机的广阔市场前景, 成立了移动产业处理器接口(Mobile Industry Processor Interface, MIPI)联盟<sup>[1]</sup>。目前, 所有主要的芯片厂商使用 MIPI 规范, 所有智能手机都至少使用一种 MIPI 规范。串行显示接口(Display Serial Interface, DSI)协议是 MIPI 联盟推出的针对高速显示接口的规范<sup>[2]</sup>, 多用于移动终端系统<sup>[3]</sup>, 其特点是高速、灵活和低功耗<sup>[4]</sup>。DSI 协议架构的最低层是物理层(Physical Layer, PHY), 规范了发送端(主端)和接收端(从端)通道的电学特性和通道建立时的

时序要求<sup>[5]</sup>。D-PHY 规范是一种常用的兼容 DSI 协议的物理层规范<sup>[6]</sup>。

D-PHY 一般包含一个时钟通道, 一到四个数据通道, 主要的工作模式有高速(High Speed, HS)模式、低功耗(Low-Power, LP)模式<sup>[7]</sup>。高速模式下, D-PHY 通道采用差分点对点传输, 提供源同步时钟, 数据传输采用突发式(Burst)传输, 单通道数据传输速率最高支持 1.5 Gb/s(D-PHY v1.1 规范), 主要用于传输高速的图像、视频数据流。低功耗模式下, D-PHY 只有通道 0 工作, 通道无端接, 数据传输低速且可间断, 是一种异步通信模式<sup>[8]</sup>, 通道数据传输速率最高支持 10 Mb/s(D-PHY v1.1 规范), 主要用于传输控制和状态信号事务。

本设计主要关注以下问题的研究:(1)低功耗模

\* 基金项目: 国家科技重大专项 02 专项(2016ZX02301)

式下,是异步通信模式,如何实现数据的采样以及满足低功耗要求;(2)高速模式下,D-PHY 时钟最高达到 1.5 GHz,如何满足电路时序要求和四通道之间数据的对齐。

## 1 从端 D-PHY 规范

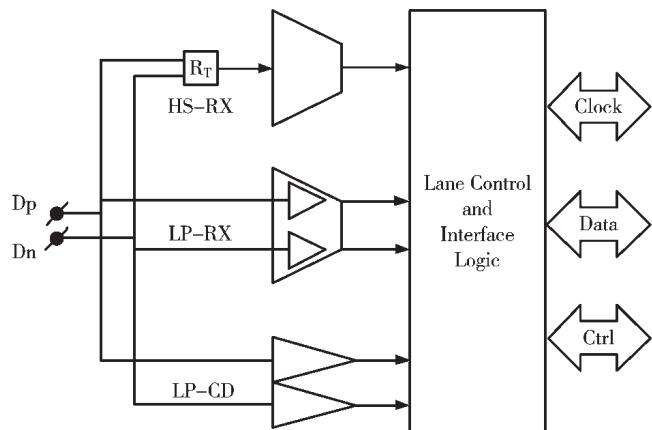

D-PHY 是 DSI 协议的最低层次,有主端和从端之分,图 1 所示为从端 D-PHY 单通道架构图,包含高速接收功能模块(HS-RX)、低功耗功能模块(LP-RX)和冲突检测功能模块(LP-CD)。本设计的从端 D-PHY 包含一个时钟通道和四个数据通道,其中时钟通道只工作在高速模式和超低功耗模式;数据通道只有通道 0 支持所有的模式,其他三个通道只有高速模式和超低功耗模式。

图 1 从端 D-PHY 单通道架构图

传输线 Dp、Dn 在高速模式下为差分小信号,在低功耗模式下为单端全摆幅信号<sup>[9-10]</sup>。D-PHY 规范将 Dp、Dn 编码成不同的通道状态,如表 1 所示。

表 1 D-PHY 通道状态

| 状态码   | 高速模式 |         | 低功耗模式  |  |

|-------|------|---------|--------|--|

|       | 突发模式 | 控制模式    | 低速模式   |  |

| HS-0  | 差分 0 | N/A     | N/A    |  |

| HS-1  | 差分 1 | N/A     | N/A    |  |

| LP-00 | N/A  | Bridge  | Space  |  |

| LP-01 | N/A  | HS-Rqst | Mark-0 |  |

| LP-10 | N/A  | LP-Rqst | Mark-1 |  |

| LP-11 | N/A  | Stop    | N/A    |  |

### 1.1 从端 D-PHY 低功耗模式

低功耗模式主要传输 DSI 协议规定的控制命令和状态信息。D-PHY 复位之后处于低功耗模式,并且在 D-PHY 进入高速模式之前,需要低功耗电路提前工作,将高速驱动电路使能以及端接电路使能打开,才能建立稳定可靠的高速传输连接。低功耗模式电路主要功能为:模拟前端进行模拟单端信号 Dp 和 Dn 的有效接收,并输出正确的逻辑电平给数字电路。数字电路通过 Dp

和 Dn 的逻辑电平值,进行不同的时序控制和逻辑组合。

通过检测 Dp、Dn 线路上的逻辑电平,D-PHY 首先通过一段引导码(Entry Code)进入低功耗模式,D-PHY 规范规定的低功耗模式引导码为:LP11→LP10→LP00→LP01→LP00。之后,D-PHY 根据不同的 8 bit 进入命令码(Entry Command)进入到不同的低功耗模式,低功耗模式可细分为三种模式:低功耗传输模式(Low-Power Data Transmission, LPDT)、超低功耗模式(Ultra-Low Power State, ULPS)和复位模式(Reset-Trigger)。对应关系如表 2 所示。

表 2 进入命令码

| 命令类型    | 进入命令码          |

|---------|----------------|

| LPDT    | mode 1110_0001 |

| ULPS    | mode 0001_1110 |

| Trigger | Trigger others |

低功耗模式下的 8 bit 进入命令码和 8 bit 低速数据是通过对 Dp、Dn 逻辑电平进行空格-独热码(Spaced-One\_Hot)解码得到的。空格独热码是一种特殊的编码方式,它使用 2 组 LP 状态值来表示数据“0”和数据“1”,每个 Mark 状态紧邻一个 Space 状态,即 Mark1(LP10)和 Space(LP00)表示数据“1”,Mark0(LP01)和 Space(LP00)则表示数据“0”。

### 1.2 从端 D-PHY 高速模式

D-PHY 在高速模式下主要传输高速的图像和视频数据流,数据传输采用 Burst 传输方式,D-PHY 规范规定一次 Burst 传输的最低有效数据为 1 Byte。为了协助从端进行高速数据流的同步,D-PHY 规范规定主端在传输有效数据之前,必须先发送 8 位的帧头同步码(Sync 码),有效数据传输结束后再发送一段尾流码(Trailer 码)。规范规定的 8 位 Sync 码为 0001\_1101,Trailer 码为最后一位有效数据的反相,为全“0”或者全“1”。

在 Burst 高速数据传输时,通过检测 Dp、Dn 线路上的逻辑电平,D-PHY 首先通过一段引导码进入高速模式,D-PHY 规范规定的高速模式引导码为:LP11→LP01→LP00,进入到高速模式之后,Dp、Dn 线路电压的摆幅降低,以差分形式工作,此时线路的端接并不能保证能稳定工作,所以 D-PHY 规范规定发送端在进入高速模式以后先发一段时间( $T_{hs-zero}$ )的 HS-0 数据,再接着发送 Sync 码、有效 Burst 载荷数据和 trailer 码。不传输 burst 高速数据时,Dp、Dn 维持在 STOP 通道状态。

### 2 从端 D-PHY 电路实现

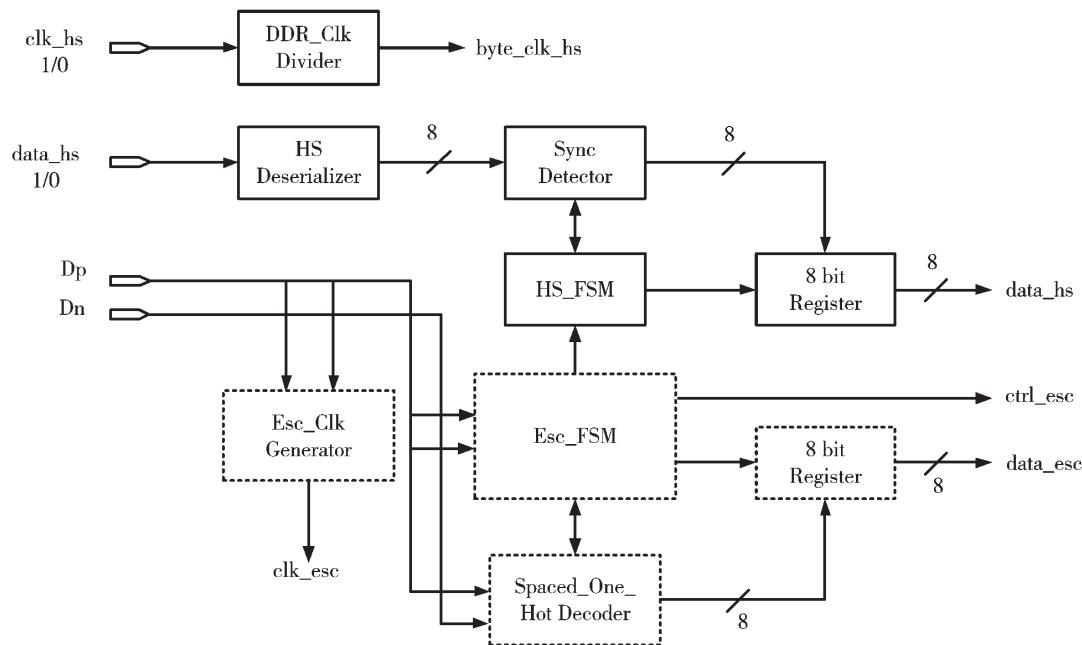

从端 D-PHY 是一个数模混合电路,主要功能是通过差分 Dp、Dn 通道线路,接收从主端发送来的串行比特流(bit)数据,将模拟信号转换为数字信号,解串出并行有效数据,并进行数据帧头同步检测,再将帧同步后的数据以字节(Byte)的形式传给协议上层。从端 D-PHY 电路架构图如图 2 所示。

图 2 从端 D-PHY 电路架构图

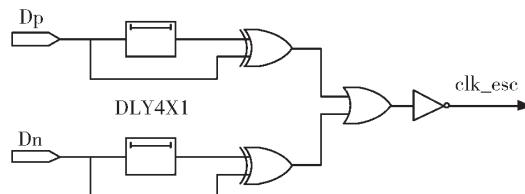

### 2.1 低功耗模式下异步时钟

D-PHY 在低功耗模式下是一种异步通信模式, 数据通道的传输不依赖于时钟通道。对于异步信号的采样, 一般来说要满足采样时钟频率至少是异步信号变化速率的 1.5 倍<sup>[1]</sup>。文献[1]采用外挂 40 MHz 本地时钟对 Dp、Dn 通道状态进行过采样。低功耗模式下, 数据传输是低速、可间断的, 外挂一个过采样时钟显然会增加电路的动态功耗, 并且额外消耗了系统资源。引导码和 Spaced-One-Hot 的编码特点是: 两次通道状态传输之间会发送一次 Bridge 状态或者 Space 状态, 其值都为 LP00, 本设计根据这一特点提出了一种低功耗模式下异步时钟生成电路, 可实现异步数据的有效采样。此异步时钟只在 Dp、Dn 变化时才会跳变。实现方式如下: 通过调用工艺库里的标准延时单元 DLY4X1, 分别将 Dp、Dn 延时

后的信号 Dp'、Dn' 和 Dp、Dn 相或或得到 clk\_p 和 clk\_n, 再将 clk\_p 和 clk\_n 相或再反相得到异步时钟 clk\_esc。电路设计如图 3 所示。

图 3 异步时钟生成

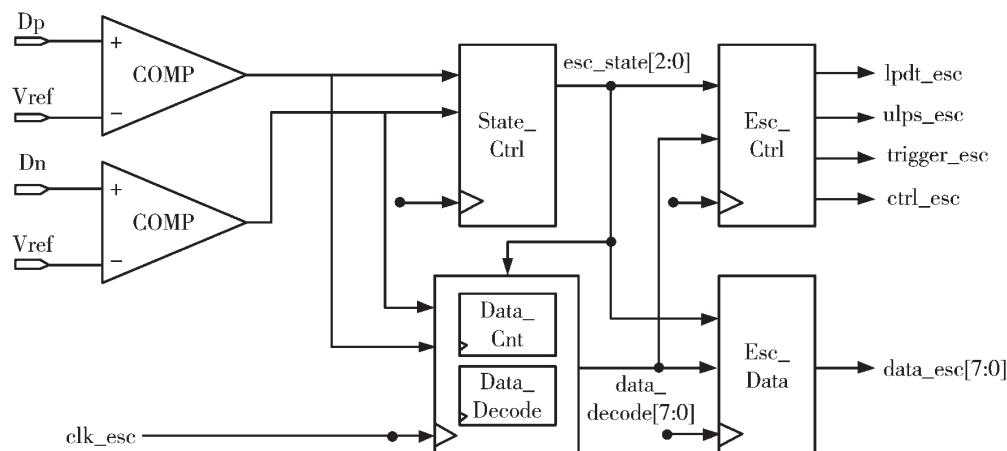

### 2.2 低功耗模式电路实现

低功耗模式电路如图 4 所示。低功耗模式控制通路的主要功能是保证从端 D-PHY 通过异步时钟 clk\_esc 能够采样到正确且对应的引导码, 进入正确的工作模式,

图 4 低功耗模式电路图

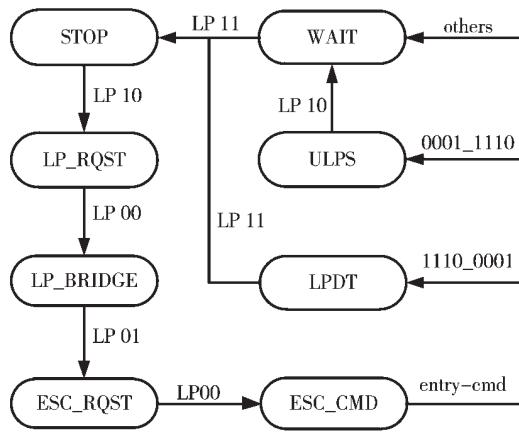

由 D-PHY 一个状态机 (Finite State Machine, FSM) 来控制, 通过检测不同的线路电平进入不同的状态, 状态转移图如图 5 所示。

图 5 低功耗模式状态转移图

D-PHY 复位结束之后, 处于 STOP 状态, 打开低功耗接收机进入线路电平检测模式, 之后根据不同的引导码进行状态跳转, 其中 ESC\_CMD 为进入命令码判断状态, 8 bit 进入命令码由数据通路给出; 低功耗模式下, 当再次检测线路电平为 LP11 时, D-PHY 回到 STOP 状态, 等待下一次低功耗传输。

数据通道进行 Spaced-One-Hot 的解码, 输出进入命令码, 并且在 LPDT 模式下输出 8 bit 的低速数据。数据通道的实现电路如图 5 所示, State\_Ctrl 为状态机控制模块, 在 ESC\_CMD 和 LPDT 状态下进行计数和 Spaced-One-Hot 解码, 分别由 Data\_Cnt 和 Data\_Decode 模块实现, 其中 Data\_Cnt 是一个 4 位二进制计数器, 控制 Data\_Decode 模块, 实现 8 比特的数据输出。

### 2.3 高速模式电路实现

D-PHY 在高速模式下采用同步通信机制, 提供源同步的时钟通道和数据通道。高速模式下的时钟是一种 DDR 时钟。本设计采用四个数据通道实现, 由于工艺角偏差和路径延时, 四通道之间的数据偏差必须进行精确的测算, 在设计过程中采取一定的预估考量方式。

本设计根据以往的数模混合电路设计经验, 将高速模式数模电路的功能划分如图所示。DDR 时钟的分频以及四通道数据的串并转换由模拟电路实现, 模拟电路使用分频时钟将四通道 8 bit 并行数据打出。数字电路实现高速模式的进入退出时序控制以及各个通道的有效数据 Sync 码检测。采用此功能架构划分, 模拟电路通过后仿真可以十分精确地得到四通道之间的数据偏差, 通过搭建模拟电路 Verilog 模型, 将通道之间的偏差信息反标进去, 供数字电路进行仿真验证分析。另外, 时钟分频和串并转换功能由模拟电路实现, 则不用将 4 通道高速时钟全部输出给数字部分, 只需输出一路分频后的低速时钟即可, 降低了数字电路的时序约束。

### 2.3.1 时钟通道高速模式实现

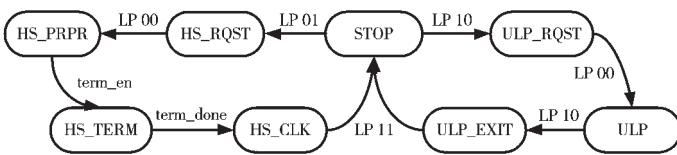

D-PHY 时钟通道只在需要进行高速 Burst 数据传输时才使能, 为了节省功耗, 其他时间都只工作在超低功耗模式。所以相较于数据通道, 时钟通道的具体实现电路相对简单。时钟通道的时序控制由一个状态机控制, 通过检测单端 Dp、Dn 线路电平, 时钟通道通过引导码 LP11→LP01→LP00 进入高速模式, 此时需打开时钟通道的高速端接使能, 端接建立完成后, Dp、Dn 为高速差分信号, 接收高速 DDR 时钟, 高速传输结束后, D-PHY 断开端接, 单端 Dp、Dn 信号维持 LP11 状态, 时钟通道回到 STOP 状态。非高速传输模式下, 时钟通道通过引导码 LP11→LP10→LP00→LP01→LP11 进入和退出超低功耗模式。时钟通道状态机如图 6 所示。

图 6 时钟通道状态转移图

### 2.3.2 数据通道高速模式实现

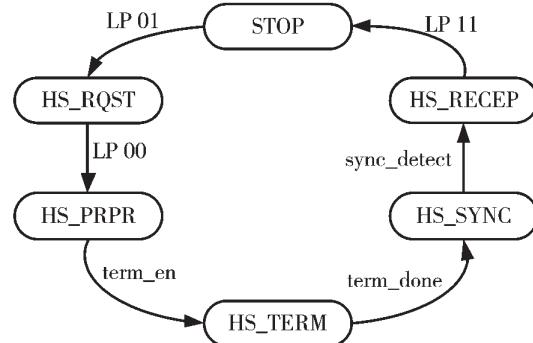

对于数据通道, 时序控制由一个状态机实现, 如图 7 所示。通过检测单端 Dp、Dn 线路电平, D-PHY 通过引导码 LP11→LP01→LP00 进入高速模式, 此时需打开数据通道的高速端接使能, 端接建立完成后, Dp、Dn 为高速差分信号, 接收高速差分数据。模拟电路将差分串行数据解串成 8 bit 并行数据, 数字电路进行并行数据的 Sync 码帧头检测, 检测到并行数据的帧头以后, 接下来的才是有效的载荷数据。高速传输结束后, D-PHY 断开端接, 单端 Dp、Dn 信号维持 LP11 状态, 数据通道回到 STOP 状态。

图 7 数据通道高速模式状态转移图

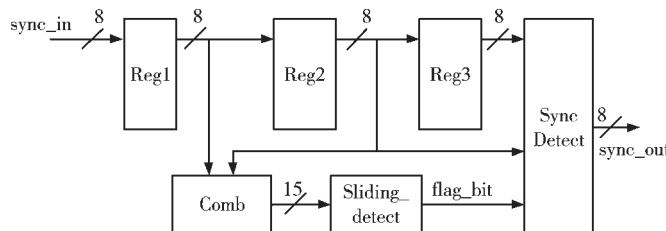

同步 Sync 码的检测由 Sync\_Detector 电路实现, 电路示意图如图 8 所示, sync\_in 是模拟电路串并转换输出的未对齐的 8 bit 并行数据, 其中, 8 位 Sync 码可能刚好存在于 1 byte 的数据中或者连续 2 byte 数据之间。Reg1~3 是级联的 8 位 D 触发器, 采用“滑动窗口”检测的方式判断 Reg1 和 Reg2 连续 2 byte 数据中 Sync 码的位置, 检

图 8 Sync 码检测电路图

测成功后生成位置标记信号,再将 Reg2 和 Reg3 对应位置的数据做一次拼接,得到帧同步后的 8 bit 对齐数据 sync out。

### 3 电路仿真与逻辑综合

### 3.1 从端口 PHY 仿真验证

本设计搭建 Testbench 平台对从端 D-PHY 进行仿真验证。模拟主端 D-PHY 行为，搭建了主端 D-PHY Verilog 模型，该模型可以产生 D-PHY 低功耗模式、高速模式和超低功耗模式仿真激励源。DUT(Design Under Test) 从端 D-PHY 由模拟电路 Verilog 模型和数字电路组成。

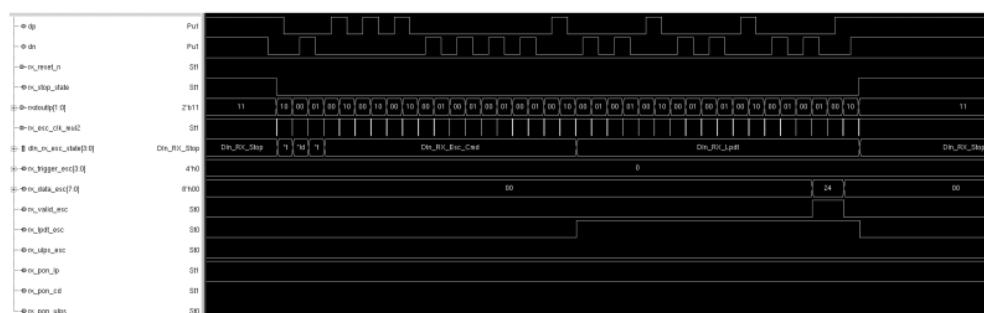

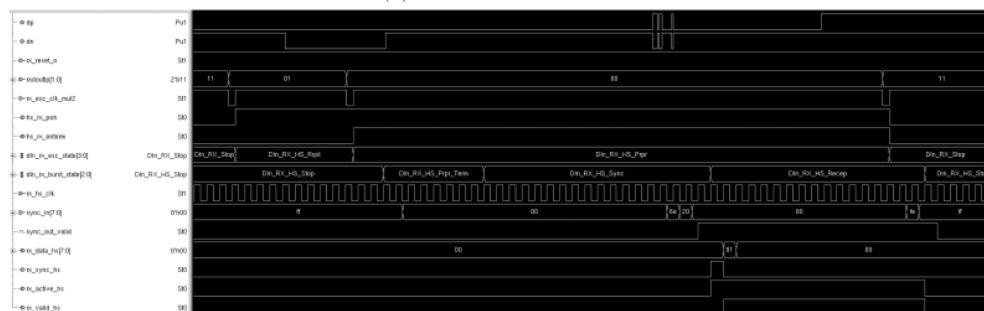

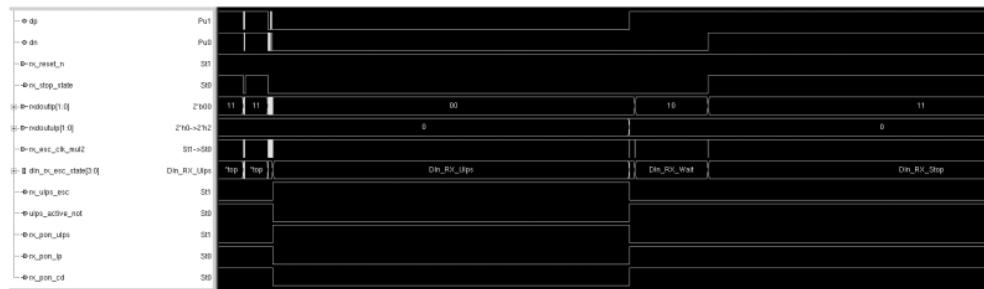

使用 VCS 工具进行编译仿真, 仿真结果如图 9 所示。

图 9(a)、(b)、(c) 分别为低功耗模式、高速模式和超低功耗模式仿真波形,结果显示,采用本设计提出的异步时钟,D-PHY 可以正确检测到低功耗模式进入引导码,并且能正确进行 Spaced-One-Hot 解码,输出 LPDT 数据和低功耗模式下的控制使能信号;D-PHY 可以正确检测到高速模式进入引导码,模拟模型的分频以及串并转换逻辑正确,数字电路部分可以正确检测到 Sync 码,有效载荷数据输出正确;D-PHY 可以正确检测到超低功耗模式进入引导码,超低功耗模式退出逻辑正确。

### 3.2 从端 D-PHY 逻辑综合

基于 SMIC 0.18  $\mu\text{m}$  工艺库, 使用 Synopsys Design Compiler(DC) 工具对本设计从端 D-PHY 进行逻辑综合。典型(tt)工艺角下, 从端 D-PHY 整体面积为 95 061  $\mu\text{m}^2$ , 整体功耗为 4.291 mW, 其中, 低功耗模式下功耗为 231.3  $\mu\text{W}$ 。

4 结论

本文提出了一种符合 MIPI D-PHY v1.1 规范的从端 D-PHY 数字电路设计，提出了一种异步时钟生成电路，该

(a) 低功耗模式仿真波形

(b) 高速模式仿真波形

## 超低功耗模式仿真

异步时钟可以准确地进行 D-PHY 各个模式下进入引导码的检测。根据数模功能架构划分,搭建了模拟电路模型,供数字电路进行仿真验证。仿真和综合结果表明,D-PHY 在各个模式下功能和时序正确,满足 D-PHY v1.1 高速模式下 1.5 Gb/s 和低功耗模式下 10 Mb/s 的带宽要求。

#### 参考文献

- [1] 李先友,赵曙光,段永成,等.基于 FPGA 的实时 MIPI CSI-2 图像采集与处理系统[J].电子技术应用,2019,45(1):97-100.

- [2] SHIN G W,LEE C K,LEE Y H.Hardware design of an interface supporting both camera and display for mobile devices[C]//2015 4th International Conference on Modeling and Simulation(MAS),2015:17-20.

- [3] KIM H S,LEE P H,HAN J W,et al.A 10 Gbps D-PHY transmitter bridge chip for FPGA-based frame generator supporting MIPI DSI of mobile display[J].IEICE Transactions on Electronics,2017,E100.C(11):1035-1038.

- [4] KIM D H,KIM B D,CHO K.Design of D-PHY chip for mobile display interface supporting MIPI standard[J].Microelectronics Journal,2012,43(12):949-955.

- [5] MIPI Alliance, MIPI alliance specification for display serial interface[S].Version 1.1,2011.

- [6] MIPI Alliance, MIPI alliance specification for D-PHY[S].Version 1.1,2011.

- [7] LEE P H,JANG Y C.A 20-Gb/s receiver bridge chip with

(上接第 32 页)

#### 参考文献

- [1] 张烨晨,刘有耀,崔盼.基于 FPGA 的 USB PD 控制器设计与实现[J].信息技术,2019,21(2):26-29.

- [2] 李生晖.基于 Type-C 接口的 USB\_PD 协议的设计与实现[D].西安:西安电子科技大学,2017.

- [3] 朱雪帅.应用于移动终端充电器的快充接口电路设计[D].南京:东南大学,2018.

- [4] 王玲玉.USB PD 3.0 协议中发送端物理层的设计与实现[D].沈阳:辽宁大学,2018.

- [5] SIAMAK D,LEO L.A Type-C USB power delivery chip faced catastrophic failure[C]//IEEE 11th Latin American Symposium on Circuits & Systems(LASCAS) 2020,2020.

- [6] 伍毅夫.基于 QuickCharge2.0 的快充控制芯片研究[D].西安:西安电子科技大学,2016.

- [7] 黄腾.USB Type-C 及 PD 设计验证面面观[J].中国集成电路,2016(9):47-51.

- [8] 席旭.基于 USB PD 协议的数控电源芯片设计[D].兰州:兰州大学,2019.

- [9] 方侃飞,蔺智挺,赵建中.面向 USB PD 3.0 协议的新型 BMC 解码电路设计[J].信息技术,2020,25(3):14-17.

- [10] 苗伟根.智能快充技术的研究及电路设计[D].杭州:杭州电子科技大学,2019.

auto-skew calibration for MIPI D-PHY interface[J].IEEE Trans. Consumer Electronics,2019,65(4):484-492.

- [8] KIM H S,LEE P H,HAN J W,et al.A 10 Gbps D-PHY transmitter bridge chip for FPGA-based frame generator supporting MIPI DSI of mobile display[J].IEICE Transactions on Electronics,2017,E100.C(11):1035-1038.

- [9] KIM T J,HWANG J I,LEE S,et al.A 14 Gb/s dual mode receiver with MIPI D-PHY and C-PHY interfaces for mobile display drivers[J].Journal of the Society for Information Display,2020,28(6):535-547.

- [10] PANDEY A K,JANGALE A,NARAYAN S.Signal integrity and compliance test of DSI and CSI2 serial interface over MIPI D-PHY[C]//2020 IEEE 24th Workshop on Signal and Power Integrity(SPI),2020:1-4.

- [11] CUMMINGS C E.Clock Domain Crossing(CDC) Design & Verification Techniques Using SystemVerilog[Z].2008:1-56.

(收稿日期:2021-02-22)

#### 作者简介:

张自豪(1995-),男,硕士研究生,主要研究方向:集成电路设计技术。

赵建中(1983-),男,博士,副研究员,主要研究方向:高速 Serdes 接口电路设计。

周玉梅(1962-),女,学士,研究员,主要研究方向:高性能低功耗专用集成电路设计和高性能低功耗混合信号电路设计。

扫码下载电子文档

- [11] 李建成.大功率电源电池组能量管理系统设计与应用[D].长沙:湖南大学,2013.

- [12] 赵旺.一种 BMC 码自适应解码系统 CN 208768080 U[P].2019-04-19.

- [13] 赵毅.数字滤波的滑动平均法和低通滤波法[J].仪表技术,2001,5(1):40-41.

- [14] HASHEMI S T,KIA M S S.Variability effects on full adders utilized at finite impulse response(FIR) filter implementation[J].Journal of Economic & Management Perspectives,2017,11(2):933-945.

- [15] ESCOTT R.VLSI implementation in multiple-valued logic of an FIR digital filter using residue number system arithmetic[J].IEEE Transactions on Circuits and Systems,1986,33(1):5-25.

- [16] SIAMAK D,XU Z.A BMC analog and digital PHY for USB Type-C power delivery[J].Canadian Journal of Electrical and Computer Engineering,2020,43(3):195-202.

(收稿日期:2021-03-11)

#### 作者简介:

张万荣(1964-),男,博士,教授,主要研究方向:芯片设计。

王飞虎(1995-),男,硕士,主要研究方向:芯片设计。

扫码下载电子文档

## 版权声明

经作者授权，本论文版权和信息网络传播权归属于《电子技术应用》杂志，凡未经本刊书面同意任何机构、组织和个人不得擅自复印、汇编、翻译和进行信息网络传播。未经本刊书面同意，禁止一切互联网论文资源平台非法上传、收录本论文。

截至目前，本论文已经授权被中国期刊全文数据库（CNKI）、万方数据知识服务平台、中文科技期刊数据库（维普网）、DOAJ、美国《乌利希期刊指南》、JST 日本科技技术振兴机构数据库等数据库全文收录。

对于违反上述禁止行为并违法使用本论文的机构、组织和个人，本刊将采取一切必要法律行动来维护正当权益。

特此声明！

《电子技术应用》编辑部

中国电子信息产业集团有限公司第六研究所