# 一种新型高精度电流检测电路的设计 \*

杨朝龙<sup>1</sup>, 刘斌<sup>2</sup>, 张志浩<sup>1,3</sup>, 章国豪<sup>1,3</sup>

(1. 广东工业大学 信息工程学院, 广东 广州 510006;

2. 佛山臻智微芯科技有限公司, 广东 广州 510006; 3. 河源广工大协同创新研究院, 广东 河源 517000)

**摘要:** 针对待检测的负载电阻在实际电路中存在偏差问题, 提出新型轨到轨跨导运放电路, 将输入电压转化成电流, 通过两级运放组成的负反馈电路, 将电流输出。该电流检测电路增加了输入电压范围, 也没有了传统串联电阻检测结构的采样保持支路, 并且对待检测电阻进行步进设计来减小误差, 进一步提高检测电路的精度。该电路采用 GLOBALFOUNDRIES 0.13  $\mu\text{m}$  RF SOI-CMOS 工艺实现, 工作电压为 5 V, 启动时间为 27 ns, 静态功耗为 1.17 mW, 电流检测电路检测精度高达 99.43%。

**关键词:** 电流检测; 检测电阻; 轨到轨跨导运放; 高精度

中图分类号: TN432

文献标识码: A

DOI: 10.16157/j.issn.0258-7998.211542

中文引用格式: 杨朝龙, 刘斌, 张志浩, 等. 一种新型高精度电流检测电路的设计[J]. 电子技术应用, 2021, 47(11): 39–43, 46.

英文引用格式: Yang Chaolong, Liu Bin, Zhang Zhihao, et al. Design of a new high-accuracy current sense circuit[J]. Application of Electronic Technique, 2021, 47(11): 39–43, 46.

## Design of a new high-accuracy current sense circuit

Yang Chaolong<sup>1</sup>, Liu Bin<sup>2</sup>, Zhang Zhihao<sup>1,3</sup>, Zhang Guohao<sup>1,3</sup>

(1. School of Information Engineering, Guangdong University of Technology, Guangzhou 510006, China;

2. Foshan Zhenzhi Micro Chip Technology Company, Guangzhou 510006, China;

3. Heyuan Synergy Innovation Institute of GDUT, Heyuan 517000, China)

**Abstract:** This paper presents a novel rail-to-rail current-sensing circuit to solve the deviation of the load resistance. The input voltage is converted into current by a symmetrical rail-to-rail transconductance operational amplifier, while the output is generated by a negative feedback circuit composed of two stages operational amplifier. The current-sensing circuit increases the input voltage range without the employment of the sampler holding branch in the traditional series resistance sensing structure. The step-control design of the sensing-resistor is carried out to reduce the deviation and further improve the accuracy. The presented current-sensing circuit implemented in the GLOBALFOUNDRIES 0.13  $\mu\text{m}$  RF SOI-CMOS technology, exhibits the start-up time of 27 ns, the static consumption of 1.17 mW, and the sensing accuracy of 99.43% under an operating voltage of 5 V.

**Key words:** current sense; sensing resistor; rail-to-rail transconductance amplifier; high accuracy

## 0 引言

电流检测技术广泛应用于现代工业的各个领域, 譬如电源管理系统、过流保护电路、可编程电流源、线性及开关模式电源和电池充电器等。常用的电流检测方式有串联电阻、功率管导通电阻、功率管镜像拷贝等方式<sup>[1-3]</sup>。串联电阻造成功率损耗, 对于串联电阻检测电路来说, 其待检测电阻在实际电路中通常存在 20% 的阻值偏差, 假定是 1 k $\Omega$  的电阻在流过 1 mA 电流时, 就会导致输出功率变化  $\pm 0.2$  mW, 但是其检测精度较高; 功率管导通电阻可以进行过流保护, 但是其受工艺、温度、电源等因素的影响较大, 很难应用于高精度的电流检测; 功率管镜像拷贝的检测管电流小, 降低了功耗, 但是检测精度不高。这些方法在功耗、速度和精度上都存在缺陷, 对于高精度的需求, 选择串联电阻检测电路。

针对以上存在的问题, 本文提出一种新型轨到轨电流检测电路架构, 先对待检测电阻两端的电压值进行步进调节, 减小了电阻偏差的影响, 提高了检测精度, 通过轨到轨跨导运放结构, 将输入电压转化为输出电流, 由于该跨导恒定, 因此该检测电路可以获得很高精度的电流, 再通过两级运放组成的负反馈回路, 将电流输出。

\* 基金项目: 广东省重点领域研发计划(2018B010115001); 国家自然科学基金(61974035); 广东省“珠江人才计划”本土创新科研团队(2017BT01X168)

测电阻串的偏差,也就是 $V_1$ 的步进值大小,步进值越小,电阻串的偏差就越精确;另一个是轨到轨跨导运放的跨导 $G_M$ ,跨导 $G_M$ 保持一个恒定值时,当输入电压 $V_1$ 变化一次,对应 $I_1$ 变化的值会是一个定值,增大了电流检测电路的精度;最后一个是 $I_1$ 和 $I_2$ 的差值大小,也就是运放OP的精度,运放的增益影响着它的精度,高增益的运放有更好的钳位作用,精度也高。

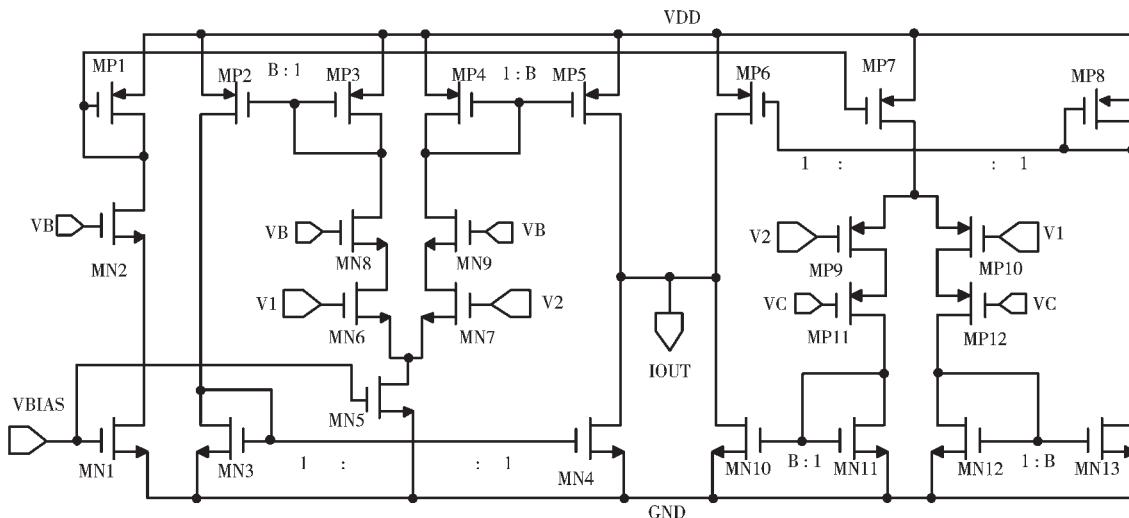

### 2.2.1 轨到轨跨导放大电路

图3为所电流检测电路中的轨到轨跨导运放电路。该轨到轨跨导运放是简单的双输入级结构,一个是N型输入对,一个是P型输入对,实现了输入轨到轨,两个输入对的输出以简单的方式结合在一个输出节点上,实现输出轨到轨<sup>[10]</sup>。若N型输入管和P型输入管的宽长比 $(W/L)_N=(W/L)_P$ ,则该运放跨导一定。 $V_{BIAS}$ 、 $V_B$ 和 $V_C$ 是三个偏置电压,由管 $MN_1$ 、 $MN_2$ 和 $MP_1$ 组成偏置电路,上电后,偏置电路通过电流镜 $MP_{10}$ 和管子 $MN_5$ 向各自差分对管提供偏置电流,输出晶体管对 $MP_5$ 、 $MN_4$ 和 $MP_6$ 、 $MN_{10}$ 的漏极相连,输出电流进行叠加。

单边N型跨导放大器的输入电压为:

$$V_{IN\ MAX}=V_{DD}-|V_{GS\ MP4}|-V_{DS\ MN9}+V_{TH\ MN7} \quad (11)$$

$$V_{IN\ MIN}=V_{DS\ MNS}+V_{GS\ MN7} \quad (12)$$

单边P型跨导放大器的输入电压为:

$$V_{IN\ MAX}=V_{DD}-|V_{DS\ MP7}|-|V_{GS\ MP9}| \quad (13)$$

$$V_{IN\ MIN}=V_{TH\ MP9}+|V_{DS\ MP11}|+V_{GS\ MN11} \quad (14)$$

利用N型和P型跨导放大器混合电路时,该电路有效地增加了共模输入电压范围。

如图3所示,单边N型跨导放大器电路包含一个输入差分对、三个电流镜和一个电流源:共源共栅差分对管 $MN_6$ 、 $MN_8$ 和 $MN_7$ 、 $MN_9$ ;一样的电流镜 $MP_2$ 、 $MP_3$ 和 $MP_4$ 、 $MP_5$ ,比值为 $1:B$ ,电流镜 $MP_5$ 、 $MN_{10}$ ,比值为 $1:1$ ;电流源 $MN_5$ 提供偏置电流。

只考虑沟道长度调制,不考虑体效应,单边N型跨

导放大器的增益为:

$$A_V=g_{mn7}\times[(g_{mn9}\cdot r_{0s9}\cdot r_{0n7})||\frac{1}{g_{mp4}}]\times g_{mp5}\times(r_{0p5}||r_{0n4}) \quad (15)$$

由于共源共栅管的输出阻抗 $g_{mn9}\cdot r_{0s9}\cdot r_{0n7}$ 远大于管子 $MP_4$ 的阻抗 $1/g_{mp4}$ ,式(15)化简为:

$$A_V=g_{mn7}\times\frac{1}{g_{mp4}}\times g_{mp5}\times(r_{0p5}||r_{0n4})=g_{mn7}\times B\times(r_{0p5}||r_{0n4}) \quad (16)$$

该电路的带宽为:

$$BW=1/[2\pi\times(r_{0p5}||r_{0n4})\times C_L] \quad (17)$$

其中, $C_L$ 为电路输出管子的寄生电容。

该轨对轨跨导运放电路总增益没有两级运放电路高,但是功率消耗会比两级运放电路低很多,此电路也不需要密勒补偿,也有着很宽的带宽。

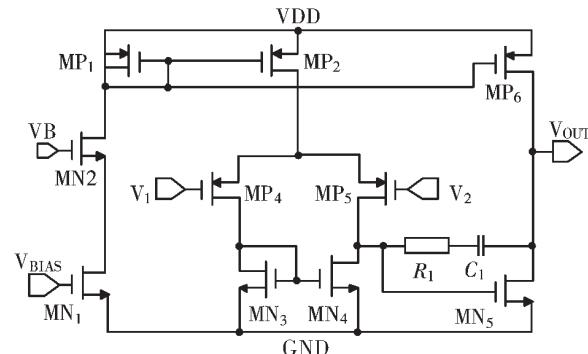

### 2.2.2 运算放大电路OP

图4为所提出的轨到轨电流检测电路中的运算放大电路。该结构为单端输出的两级运放,第一级为传统的五管OTA结构,输入是一个差分对管 $MP_4$ 、 $MP_5$ ,负载是一个电流镜 $MN_3$ 、 $MN_4$ ,比例为 $1:1$ ,来提供高增益,并将差分输入电压转化为电流;第二级为一个跨阻放大器,一个简单的共源极,来提供高输出摆幅,并将第一级输出电流转换为输出电压。 $V_{BIAS}$ 和 $V_B$ 为偏置电压, $MN_1$

图4 运算放大电路

图3 轨到轨跨导放大电路

管、 $MN_2$  管和  $MP_1$  管构成的偏置电路, 上电后, 偏置电路给管子  $MP_2$  提供偏置, 产生电流,  $C_1$  是密勒电容,  $R_1$  是密勒电阻, 来消除零点的影响, 提高电路的稳定性。

在只考虑沟道长度调制、不考虑体效应条件下, 第一级增益为:

$$A_{V1} = g_{mp5}(r_{0s5} \parallel r_{0s4}) \quad (18)$$

第二级增益为:

$$A_{V2} = g_{mn5}(r_{0s5} \parallel r_{0s6}) \quad (19)$$

电路的带宽为:

$$BW = (r_{0s5} \parallel r_{0s4}) / (2\pi \cdot A_{V2} \cdot C_1) \quad (20)$$

该电路结构简单, 运用两级运放可提高环路增益, 加入密勒电容、密勒电阻可提高电路的稳定性。

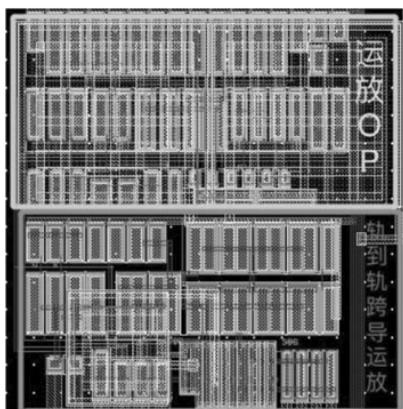

### 3 仿真结果分析

基于 GLOBALFOUNDRIES 0.13  $\mu\text{m}$  RF SOI-CMOS 工艺设计了一款新型电流检测电路。通过 Cadence virtuoso 软件对电路进行仿真与验证, 在温度 25  $^{\circ}\text{C}$ ,  $tt$  典型情况下, 电流检测电路的版图如图 5 所示, 其芯片面积为 400  $\mu\text{m} \times 550 \mu\text{m}$ 。

图 5 电流检测模块版图

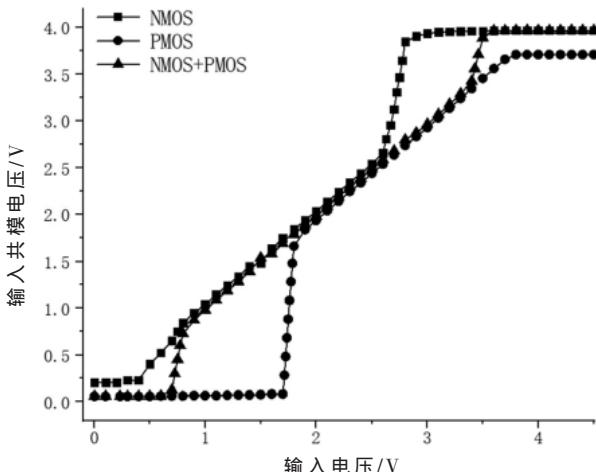

输入共模范围的仿真如图 6 所示, 单独的 NMOS 差动对的输入共模电压范围为 0.4~2.6 V; 单独的 PMOS

图 6 电路输入共模电压范围

差动对的输入共模电压范围为 1.8~3.8 V; 本文使用的 NMOS、PMOS 混合差动对的输入共模电压范围为 0.8~3.6 V, NMOS、PMOS 混合差动对有效地增大了输入共模电压范围。

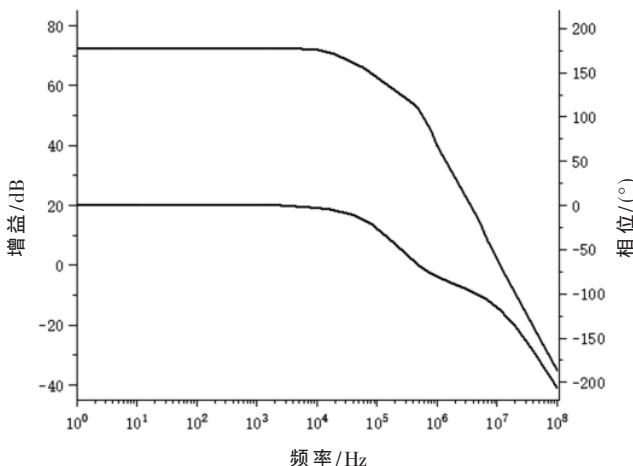

轨到轨跨到运放的增益和相位曲线如图 7 所示, 在低频时, 轨到轨跨导运放的低频增益可达 72.3 dB, 在增益为 0 dB 的时候, 相位达到了  $-117.9^{\circ}$ , 相位裕度也达到了  $62.1^{\circ}$ , 其单位增益带宽为 11.2 MHz, 该轨到轨跨导运放的稳定性良好并且有很宽的带宽。

图 7 轨到轨跨到运放的增益和相位曲线

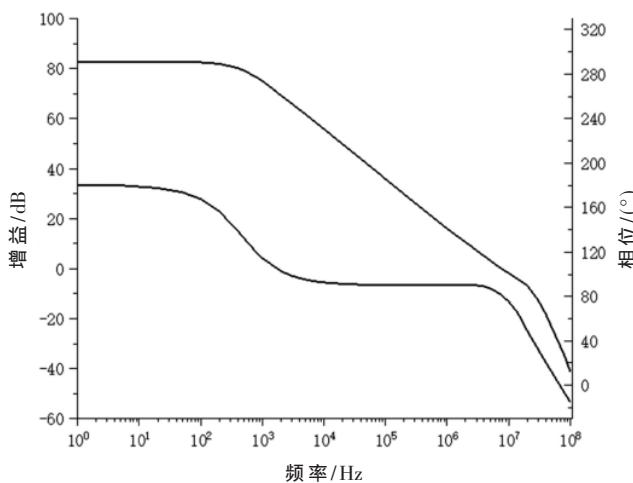

两级运放的增益和相位曲线如图 8 所示, 两级运放的低频增益可达 82.67 dB, 在增益为 0 dB 的时候, 相位也达到了  $81.49^{\circ}$ , 带宽为 7.6 MHz, 表明该两级运放满足环路增益的同时, 反馈环路稳定性良好。

图 8 两级运放的增益和相位曲线

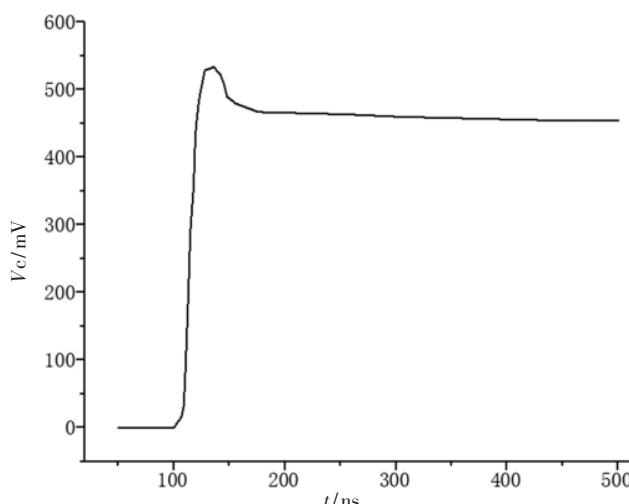

输出电压  $V_C$  的瞬态响应如图 9 所示, 在 100 ns 时,  $V_{DD}$  上电, 约 127 ns 时, 运放输出电压值达到稳定值的 90%, 得出该电路的启动时间为 27 ns, 仿真显示本文的新型电流检测电路有很快的瞬态响应。

图 9 输出电压  $V_c$  的瞬态响应

瞬态响应特性如表 2 所示, 输入电压  $V_1$  每次变化幅度为  $\pm 5$  mV, 相应轨到轨跨导运放的输出电流  $|I_1|$  变化  $\pm 0.7$   $\mu$ A, 误差在  $\pm 0.004$   $\mu$ A, 误差不足 0.57%, 表明轨到轨跨导运放的跨导变化幅度小, 与本文设计之初恒跨导相符合, 该电路有很高的精度, 精度为 99.43%; 运放输出电流  $I_2$  与  $|I_1|$  差值为  $\pm 0.08$   $\mu$ A, 误差不足 0.19%, 该两级运放的精度很高, 稳定性很好。

表 2 瞬态响应特性

| $V_1$ /V | $ I_1 $ / $\mu$ A | $ I_1 $ 差值/ $\mu$ A | $I_2$ / $\mu$ A | $(I_2 -  I_1 )$ / $\mu$ A |

|----------|-------------------|---------------------|-----------------|---------------------------|

| 2.431    | 41.918            | -0.703              | 41.840          | -0.078                    |

| 2.436    | 42.621            | -0.702              | 42.542          | -0.079                    |

| 2.441    | 43.383            | /                   | 43.304          | -0.079                    |

| 2.446    | 44.086            | +0.703              | 44.011          | -0.075                    |

| 2.451    | 44.790            | +0.704              | 44.713          | -0.077                    |

表 3 给出了本文与相关文献的电流检测电路的性能比较, 由表可见本文设计的电路结构简单并且不需要传统的电流采样保持电路, 该电路有快速的瞬态响应, 其检测精度高, 芯片面积小。

表 3 本文与其他参考文献的性能比较

| 性能指标                | 文献[1]    | 文献[2]     | 文献[4] | 文献[5] | 本文        |

|---------------------|----------|-----------|-------|-------|-----------|

| 检测方法                | 并联检测管    | 串联电阻      | 串联电阻  | 串联电阻  | 串联电阻      |

| 工艺/ $\mu$ m         | 0.35     | 1.5       | 0.35  | 0.35  | 0.13      |

| 工作电压/V              | 3.3~13.5 | 1.5~28    | 3~4.2 | 2~30  | 1.8~5.5   |

| 瞬态特性                | 较快       | -         | 较快    | -     | 快         |

| 精度/%                | 93.00    | 99.00     | 98.00 | 99.30 | 99.43     |

| 芯片面积/ $\text{mm}^2$ | -        | 2.33×1.73 | -     | -     | 0.40×0.55 |

#### 4 结论

本文基于传统检测电阻的电流检测结构, 设计分析了新型轨到轨电流检测电路, 利用对称的轨到轨跨导运放结构, 没有采样保持电路, 加上对待检测电阻的步进调节, 减小了电阻偏差带来的影响, 并且提高了检测电

路的精度。电路仿真表明, 本文电路增大了共模输入电压范围, 该电路的启动时间为 27 ns, 功耗为 1.17 mW, 运放带宽为 11.2 MHz, 电流检测电路的精度高达 99.43%。该电路具有高精度检测功能, 并且有较快的瞬态响应、较低的功耗和较宽的带宽, 可广泛应用于电源系统以及高精度芯片内部。

#### 参考文献

- [1] 刘满雀, 姚若河. 一种高精度电流检测电路的设计[J]. 中国集成电路, 2009, 18(3): 53~57.

- [2] 杨旸, 吴晓波. 一种用于高端电流检测的高精度放大器的设计[J]. 电路与系统学报, 2011, 16(2): 1~6.

- [3] 毕立强, 蔡小五, 谭守标, 等. 高边智能功率芯片的高精度电流检测电路[J]. 安徽大学学报(自然科学版), 2020, 44(6): 65~71.

- [4] Chi Yuan, Lai Xinquan, Du Hanxiao. Fast transient response high-accuracy current-sensing technique for step-up DC-DC converter[J]. Electronics Letters, 2015, 51(7): 577~579.

- [5] 王泽宇, 来新泉. 增益可调通用高精度负载电流检测电路[J]. 华中科技大学学报(自然科学版), 2016, 44(9): 6~10.

- [6] PUS CASU R, BRÎNZOI P, CREOS TEANU L, et al. High accuracy current sense amplifier with extended input common mode range[C]//2014 10th Conference on Ph.D. Research in Microelectronics and Electronics(PRIME), 2014.

- [7] LI H, XIE P, LI C, et al. A high accuracy and wide input voltage range current sensor with adaptive amplification and temperature compensation[C]//2019 IEEE International Conference on Electron Devices and Solid-State Circuits(EDSSC), 2019.

- [8] 毕查德·拉扎维. 模拟 CMOS 集成电路设计[M]. 西安: 西安交通大学出版社, 2003.

- [9] 曹正州, 孙佩. 一种低电压恒定跨导轨到轨运算放大器的设计[J]. 电子与封装, 2019, 19(11): 22~25.

- [10] 高瑜宏, 李俊龙. 一种低电压恒跨导轨对轨 CMOS 运算放大器设计[J]. 电子技术应用, 2020, 46(1): 48~51, 56.

- [11] 谢海情, 陈玉辉, 王振宇. 一种低压低功耗恒跨导轨到轨运算放大器设计[J]. 电子元件与材料, 2020, 39(10): 65~69.

- [12] 李有慧. 一种输入输出轨到轨 CMOS 运算放大器的设计[J]. 电子科技, 2015, 28(6): 165~169.

- [13] LI H, XIE P, LI C, et al. A high accuracy and wide input voltage range current sensor with adaptive amplification and temperature compensation[C]//2019 IEEE International Conference on Electron Devices and Solid-State Circuits(EDSSC), 2019.

- [14] 王健, 朱明魁. 一种恒跨导输入级轨到轨运算放大器的设计[J]. 电子世界, 2020(17): 189~190.

(下转第 46 页)

时会顾及所有工艺角、模式的影响,可以有效减少各场景间的相互影响<sup>[16]</sup>。通过使用“fix\_eco\_timing –type hold –method {size\_cell insert\_buffer} –buffer\_list \$buf\_list”命令和“fix\_eco\_timing –type setup –method {size\_cell}”命令进行时序违规的自动修复,经过第三次迭代后,所有场景中时序违规全部修复完成。表1是时序修复后通过“report\_constraints”得到的所有时序和设计规则检查(Design Rule Check)违规,因为macro端口后面没有连接负载,所以出现最小电容(Min\_Capacitance)违规,此违规可以忽略。

表1 时序与设计规则检查违规

| 引脚         | 场景           | 需要电容   | 实际电容   | 余量      |

|------------|--------------|--------|--------|---------|

| Sram0/i[0] | func_lt_cmax | 0.1000 | 0.0300 | -0.0700 |

| Sram0/i[1] | func_lt_cmax | 0.1000 | 0.0300 | -0.0700 |

| Sram0/i[2] | func_lt_cmax | 0.1000 | 0.0300 | -0.0700 |

| Sram1/i[3] | func_lt_cmax | 0.1000 | 0.0300 | -0.0700 |

| Sram1/i[4] | func_lt_cmax | 0.1000 | 0.0300 | -0.0700 |

## 4 结论

本文介绍了DMSA技术在MCMM物理设计中时序签核的应用,并利用Cxdp13芯片设计实例阐述DMSA技术的实现过程。实践结果表明,DMSA模式下时序分析与修复可以并行进行,时序修复过程中也会考虑其他场景的需要并且不需要进行多窗口切换,提高了时序分析的效率,也大大缩减了时序修复的时间。另外,随着科技的发展,普通计算机的硬件条件也足以支撑DMSA技术的实现。因此,在如今的MCMM物理设计中,DMSA技术在时序签核中得到了广泛的应用。

## 参考文献

- [1] 刘峰.CMOS集成电路后端设计与实战[M].北京:机械工业出版社,2015.

- [2] Design compiler user guide[M].Synopsys, 2012.

- [3] EWETZ R, KOH C K. Construction of reconfigurable clock trees for MCMM designs using mode separation and scenario compression[J]. ACM Transactions on Design Automation of Electronic Systems(TODAES), 2016, 21(4): 1–27.

- [4] 邱进超.40 纳米 3G 手机基带芯片的物理实现[D].西安:西安电子科技大学,2012.

- [5] BHATNAGAR H. Advanced ASIC chip synthesis[M]. New York, USA: Kluwer Academic Publishers, 2002.

- [6] 刘峰.集成电路静态时序分析与建模[M].北京:机械工业出版社,2016.

- [7] 虞希清.专用集成电路设计实用教程[M].杭州:浙江大学出版社,2018.

- [8] 吕宗伟,林争辉,张镭.数字集成电路的时序分析[J].微电子学,2001(2): 126–129.

- [9] 李珈.基于TQ时序分析器的时序分析和约束[J].电子测试,2013(11): 27–28.

- [10] FORZAN C, PANDINI D. Why we need statistical static timing analysis[C]//International Conference on Computer Design. IEEE, 2007: 91–96.

- [11] 杨晓东.基于 55nm 嵌入式闪存工艺的智能卡芯片数字后端设计与实现[D].北京:中国科学院大学,2017.

- [12] 叶将.基于DMSA的快速 hold 修复[J].硅谷,2012(4): 33, 6.

- [13] SHANTHALA L, JAYAGOWRI R. Efficient timing closure in SOC through timing quality checks and engineering change order[J]. International Journal of Advance Research, Ideas and Innovations in Technology, 2017, 3(3): 699–705.

- [14] 许立明,李沛杰,杨堃,等.ASIC中时钟 MUX 电路结构时序约束的方法分析[J].集成电路应用,2019,36(11): 12–15.

- [15] 裴武龙.纳米工艺物理设计中DMSA的研究与实现[D].北京:北京工业大学,2014.

- [16] Primetime commands[M].Synopsys, 2010.

(收稿日期:2021-03-17)

## 作者简介:

孙恒(1994-),男,硕士,主要研究方向:数字集成电路设计。

王仁平(1972-),通信作者,男,硕士,副教授,主要研究方向:数字集成电路设计,E-mail:838180112@qq.com。

蔡沅坤(1995-),男,硕士,主要研究方向:数字集成电路设计。

扫码下载电子文档

(上接第 43 页)

- [15] 马玉杰,高俊丽,后永奇,等.3.3V/0.18μm 恒跨导轨对轨 CMOS 运算放大器的设计[J].电子技术应用,2012, 38(11): 48–50, 54.

- [16] 刘浩男.一种轨到轨恒定增益差分运算放大器设计[J].电子技术与软件工程,2017(13): 93.

(收稿日期:2021-03-22)

## 作者简介:

杨朝龙(1998-),通信作者,男,硕士研究生,主要研究方向:模拟集成电路设计,E-mail:2549353907@qq.com。

刘斌(1987-),男,硕士,工程师,主要研究方向:模拟集成电路设计。

张志浩(1989-),男,博士,讲师,主要研究方向:射频与模拟集成电路设计。

扫码下载电子文档

## 版权声明

经作者授权，本论文版权和信息网络传播权归属于《电子技术应用》杂志，凡未经本刊书面同意任何机构、组织和个人不得擅自复印、汇编、翻译和进行信息网络传播。未经本刊书面同意，禁止一切互联网论文资源平台非法上传、收录本论文。

截至目前，本论文已经授权被中国期刊全文数据库（CNKI）、万方数据知识服务平台、中文科技期刊数据库（维普网）、DOAJ、美国《乌利希期刊指南》、JST 日本科技技术振兴机构数据库等数据库全文收录。

对于违反上述禁止行为并违法使用本论文的机构、组织和个人，本刊将采取一切必要法律行动来维护正当权益。

特此声明！

《电子技术应用》编辑部

中国电子信息产业集团有限公司第六研究所