# DMSA 在时序签核中的应用 \*

孙 恒,王仁平,蔡沅坤

(福州大学 物理与信息工程学院,福建 福州 350000)

**摘要:**在芯片的设计过程中,静态时序分析(Static Timing Analysis,STA)无疑是整个设计中最重要的一环。如今纳米级工艺下的芯片设计往往属于多工艺角多模式(MultiCorner-MultiMode,MCM)物理设计,工艺角和工作模式的特定组合称之为场景,多场景的物理设计会给芯片带来更加稳定的性能,但也会使静态时序分析变得更为复杂。介绍了分布式多场景时序分析(Distribute Multi\_Scenario Analysis,DMSA)技术在多工艺角多模式物理设计中的应用。经过基于Smic 90 nm 工艺的多场景数字芯片 Cxdp13 设计实践分析表明,在一定硬件条件支撑下,分布式多场景时序分析技术在多工艺角多模式的物理设计中可以达到快速时序签核的目的。

**关键词:**分布式多场景时序分析;静态时序分析;多工艺角多模式;时序签核;时序工程改变命令

中图分类号: TN431.2

文献标识码: A

DOI:10.16157/j.issn.0258-7998.211529

中文引用格式: 孙恒,王仁平,蔡沅坤. DMSA 在时序签核中的应用[J]. 电子技术应用, 2021, 47(11): 44–46.

英文引用格式: Sun Heng, Wang Renping, Cai Yuankun. Application of DMSA in timing sign-off[J]. Application of Electronic Technique, 2021, 47(11): 44–46.

## Application of DMSA in timing sign-off

Sun Heng, Wang Renping, Cai Yuankun

(Fuzhou University, University of Physics and Information Engineering, Fuzhou 350000, China)

**Abstract:** In the process of chip design, static timing analysis is undoubtedly the most important part of the entire design, and it is a priority and problem to be solved in chip design. Nowadays, chip design under nano-scale technology often belongs to multi-corner-multimode physical design. The specific combination of process angle and working mode is called scenario. Multi-scenario physical design will bring more stable performance to the chip, but it will also make static timing analysis becomes more complicated. This paper introduces the application of distribute multi-scenario analysis technology in multicorner-multimode physical design. The design practice analysis of the multi-scenario digital chip Cxdp13 based on the Smic 90 nm process shows that under certain hardware conditions, the distribute multi\_scenario analysis technology can achieve the purpose of rapid timing sign-off in the physical design of multicorner-multimode.

**Key words:** distribute multi-scenario analysis; static timing analysis; multicorner-multimode; timing sign-off; timing engineer change order

## 0 引言

随着集成电路产业不断发展,芯片制造早已进入深亚微米时代,一直以来,时序签核一直是检验芯片设计是否合格的重要标准之一,在综合工具(Design Compiler, DC)、布局布线工具(Integrated Circuit Compiler, ICC)、时序分析工具(Prime Time, PT)中都嵌入了不同的时序分析引擎。当工艺节点达到 90 nm 及以下时,为了使芯片在不同的极端环境下可以正常工作,就需要采用多工艺角多模式的物理设计方案来确保芯片在不同环境下稳定工作<sup>[1-3]</sup>。在对多场景物理设计进行时序分析时,传统 PT 需要打开多个窗口反复切换场景以达到遍历每一个

场景的目的,随后逐个场景进行时序分析,这样会使设计过程变得过于繁琐,而且,对于同一路径,不同场景下的时序违规可能会重复出现,对时序分析带来不必要的麻烦<sup>[4]</sup>,工艺角或模式的合并,也会带来各种各样的问题,DMSA 的使用可以很好地解决这些问题。

## 1 静态时序分析原理

DMSA 是 STA 的一种特殊模式,其原理和 STA 原理如出一辙。STA 是通过“穷举法”抽取整个电路的时序路径,计算时序路径的传播延时,检查信号是否满足时序约束要求,其目的是保证所有路径满足内部时序对建立时间(Setup time)和保持时间(Hold time)的要求,从而实现时序签核<sup>[5]</sup>。

STA 的实现主要分为三个步骤:(1)时序路径的划分,

\* 基金项目:福建省自然科学基金(2018J01803)

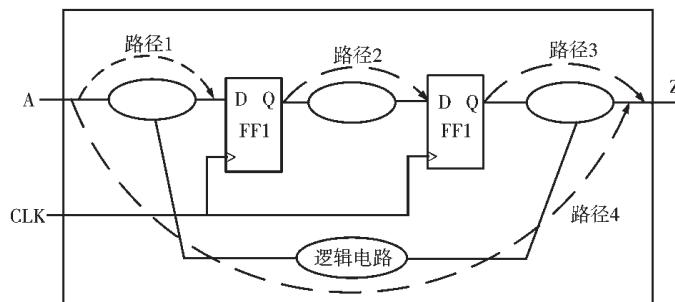

如图 1 所示,STA 在时序分析时一般将电路分为四种时序路径<sup>[6]</sup>。(2)路径延时的计算,静态时序分析的路径延时(Path delay)分为单元延时(Cell delay)和线延时(Net delay)。单元延迟多采用非线性延时模型(Nonlinear delay model),即用二维查找表进行单元延时计算,两输入变量分别为输入转换时间(Input transition time)和输出负载(Output load),同样,线延时的计算通过 ICC 中实际绕线情况,由 Start-RC 抽取寄生参数值,根据特定的线延时模型进行估算<sup>[7]</sup>。(3)路径时序的检测,就时序路径而言,需要通过延时计算得到路径的数据要求时间(Data required time)和数据到达时间(Data arrival time),然后通过比较数据要求时间和数据到达时间来判断路径是否存在时序违规问题<sup>[8-10]</sup>。

图 1 物理设计中时序路径划分

## 2 DMSA 的应用

DMSA 是静态时序分析的一种特殊模式,通过启动主进程(Master)来充当所有场景的管理者角色,主进程是运行在 DMSA 模式里的特殊进程,可以向从进程(Slave)远程分配服务器资源和任务,实现通过单个端口对所有的场景进行时序分析的目的<sup>[11-12]</sup>。

### 2.1 DMSA 使用过程

在 DMSA 的使用过程中,需要对三个关键变量进行设置,确保时序分析准确、高效的进行。

(1)许可证数目。在 DMSA 模式下进行时序分析时,主服务器(Master)需要分配一定数量的许可证(license)给从服务器(Slave)使用,没有许可证的从进程不能进行工作,使用“set\_multi\_scenario\_license\_limit”命令可以对许可证的数量进行设置,默认情况下,主服务器会最大程度地分配许可证给从进程,如果设置的从进程的数量多于许可证的数量时,没有许可证的从进程需要等其他从进程任务完成后,分配到许可证才可以进行工作。

(2)从进程的数量。根据场景的数量,在主服务器通过“set\_host\_option -max\_core -num\_processes”命令对 core 数目、启动进程数目进行设置,一般情况下,场景的数目要小于等于从进程的数目,确保每一个场景都有一个专用的从进程,保证 DMSA 顺利进行。

(3)场景的定义。DMSA 中场景的定义分为两种:(1)每一个场景都由一个脚本定义,通过命令“create\_

scenario-name \${mode}\_\${corner} -specific\_variables {mode corner} -specific\_data {pt\_setup.tcl}”主服务器将变量工作模式、工艺角组合分配到从服务器并执行带有变量工作模式、工艺角的脚本 pt\_setup.tcl。(2)时序分析使用“save\_session”命令后,可通过“create\_scenario -name -image”指定之前保存过的场景。许可证、从进程、场景三个变量的设置是 DMSA 设计方法能否并行运行的关键,需根据待分析芯片的物理设计进行正确的配置<sup>[13]</sup>。

### 2.2 DMSA 时序修复流程

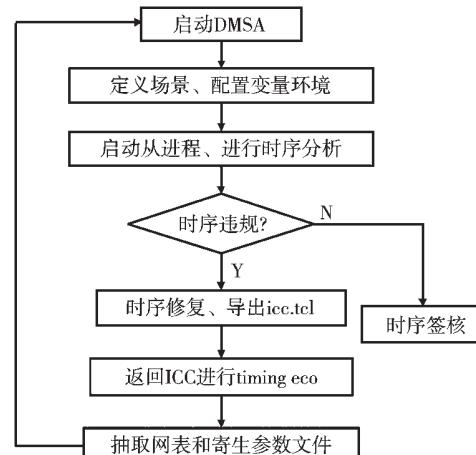

芯片在流片(Tapeout)之前,要满足时序约束和物理规则等要求,为了进行更精确的时序分析,需要将 ICC 生成的网表以及提取的寄生参数文件导入 PT 进行时序分析<sup>[14]</sup>,对于多场景的物理设计,采用 DMSA 设计方法,通过在 terminal 中输入“pt\_shell -multi\_scenario”便可进入 DMSA 模式。然后配置好相关路径和服务器资源,通过“create\_scenario”命令进行场景创建,并将数据传递到每一个从进程中,使用“start\_hosts”命令来启动所有从进程,完成环境配置之后“report\_constraints -all\_violators”命令可以查看合并后各场景下的时序违规,然后使用“fix\_eco\_timing”命令进行时序修复,待时序修复完成,用命令“write\_changes -format icctcl -output icc.tcl”生成时序修复后的工具命令语言(Tool Command Language, TCL)脚本,返回到 ICC 中进行时序修复,再提取优化后网表和寄生参数文件重新到 DMSA 中进行时序分析,循环往复,直到实现时序签核<sup>[15]</sup>。DMSA 时序修复流程如图 2 所示。

图 2 DMSA 时序修复流程

## 3 DMSA 在 Cxdp13 芯片上的实现

本次实验基于 Smic 90 nm 工艺库,待测试芯片 Cxdp13 设有 2 种模式,8 个工艺角,共有 16 个场景。在硬件配置方面共设置 16 个进程,对应 16 个场景。时序分析时,主进程将所有从进程中的时序信息整合筛选写入到一个文档报告中,自动过滤掉过多的重复路径,而不需要针对每一个场景进行时序分析,这样 PT 在做时序修复

时会顾及所有工艺角、模式的影响,可以有效减少各场景间的相互影响<sup>[16]</sup>。通过使用“fix\_eco\_timing –type hold –method {size\_cell insert\_buffer} –buffer\_list \$buf\_list”命令和“fix\_eco\_timing –type setup –method {size\_cell}”命令进行时序违规的自动修复,经过第三次迭代后,所有场景中时序违规全部修复完成。表1是时序修复后通过“report\_constraints”得到的所有时序和设计规则检查(Design Rule Check)违规,因为macro端口后面没有连接负载,所以出现最小电容(Min\_Capacitance)违规,此违规可以忽略。

表1 时序与设计规则检查违规

| 引脚         | 场景           | 需要电容   | 实际电容   | (pF) | 余量      |

|------------|--------------|--------|--------|------|---------|

| Sram0/i[0] | func_lt_cmax | 0.1000 | 0.0300 |      | -0.0700 |

| Sram0/i[1] | func_lt_cmax | 0.1000 | 0.0300 |      | -0.0700 |

| Sram0/i[2] | func_lt_cmax | 0.1000 | 0.0300 |      | -0.0700 |

| Sram1/i[3] | func_lt_cmax | 0.1000 | 0.0300 |      | -0.0700 |

| Sram1/i[4] | func_lt_cmax | 0.1000 | 0.0300 |      | -0.0700 |

## 4 结论

本文介绍了DMSA技术在MCMM物理设计中时序签核的应用,并利用Cxdp13芯片设计实例阐述DMSA技术的实现过程。实践结果表明,DMSA模式下时序分析与修复可以并行进行,时序修复过程中也会考虑其他场景的需要并且不需要进行多窗口切换,提高了时序分析的效率,也大大缩减了时序修复的时间。另外,随着科技的发展,普通计算机的硬件条件也足以支撑DMSA技术的实现。因此,在如今的MCMM物理设计中,DMSA技术在时序签核中得到了广泛的应用。

## 参考文献

- [1] 刘峰.CMOS集成电路后端设计与实战[M].北京:机械工业出版社,2015.

- [2] Design compiler user guide[M].Synopsys, 2012.

- [3] EWETZ R, KOH C K. Construction of reconfigurable clock trees for MCMM designs using mode separation and scenario compression[J]. ACM Transactions on Design Automation of Electronic Systems(TODAES), 2016, 21(4): 1–27.

- [4] 邱进超.40 纳米 3G 手机基带芯片的物理实现[D].西安:西安电子科技大学,2012.

- [5] BHATNAGAR H. Advanced ASIC chip synthesis[M]. New York, USA : Kluwer Academic Publishers , 2002.

- [6] 刘峰.集成电路静态时序分析与建模[M].北京:机械工业出版社,2016.

- [7] 虞希清.专用集成电路设计实用教程[M].杭州:浙江大学出版社,2018.

- [8] 吕宗伟,林争辉,张镭.数字集成电路的时序分析[J].微电子学,2001(2): 126–129.

- [9] 李珈.基于TQ时序分析器的时序分析和约束[J].电子测试,2013(11): 27–28.

- [10] FORZAN C, PANDINI D. Why we need statistical static timing analysis[C]//International Conference on Computer Design.IEEE, 2007: 91–96.

- [11] 杨晓东.基于 55nm 嵌入式闪存工艺的智能卡芯片数字后端设计与实现[D].北京:中国科学院大学,2017.

- [12] 叶将.基于DMSA的快速hold修复[J].硅谷,2012(4): 33,6.

- [13] SHANTHALA L, JAYAGOWRI R. Efficient timing closure in SOC through timing quality checks and engineering change order[J]. International Journal of Advance Research, Ideas and Innovations in Technology, 2017, 3(3): 699–705.

- [14] 许立明,李沛杰,杨堃,等.ASIC 中时钟 MUX 电路结构时序约束的方法分析[J].集成电路应用,2019,36(11): 12–15.

- [15] 裴武龙.纳米工艺物理设计中DMSA的研究与实现[D].北京:北京工业大学,2014.

- [16] Primetime commands[M].Synopsys, 2010.

(收稿日期:2021-03-17)

## 作者简介:

孙恒(1994-),男,硕士,主要研究方向:数字集成电路设计。

王仁平(1972-),通信作者,男,硕士,副教授,主要研究方向:数字集成电路设计,E-mail:838180112@qq.com。

蔡沅坤(1995-),男,硕士,主要研究方向:数字集成电路设计。

扫码下载电子文档

(上接第 43 页)

- [15] 马玉杰,高俊丽,后永奇,等.3.3V/0.18μm 恒跨导轨对轨 CMOS 运算放大器的设计[J].电子技术应用,2012, 38(11): 48–50, 54.

- [16] 刘浩男.一种轨到轨恒定增益差分运算放大器设计[J].电子技术与软件工程,2017(13): 93.

(收稿日期:2021-03-22)

## 作者简介:

杨朝龙(1998-),通信作者,男,硕士研究生,主要研究方向:模拟集成电路设计,E-mail:2549353907@qq.com。

刘斌(1987-),男,硕士,工程师,主要研究方向:模拟集成电路设计。

张志浩(1989-),男,博士,讲师,主要研究方向:射频与模拟集成电路设计。

扫码下载电子文档

## 版权声明

经作者授权，本论文版权和信息网络传播权归属于《电子技术应用》杂志，凡未经本刊书面同意任何机构、组织和个人不得擅自复印、汇编、翻译和进行信息网络传播。未经本刊书面同意，禁止一切互联网论文资源平台非法上传、收录本论文。

截至目前，本论文已经授权被中国期刊全文数据库（CNKI）、万方数据知识服务平台、中文科技期刊数据库（维普网）、DOAJ、美国《乌利希期刊指南》、JST 日本科技技术振兴机构数据库等数据库全文收录。

对于违反上述禁止行为并违法使用本论文的机构、组织和个人，本刊将采取一切必要法律行动来维护正当权益。

特此声明！

《电子技术应用》编辑部

中国电子信息产业集团有限公司第六研究所