# 高速大容量 DDR 微系统过孔串扰研究

张景辉,曾燕萍,王梦雅,周倩蓉,闫传荣

(中国电子科技集团公司第五十八研究所,江苏 无锡 214072)

**摘要:** 随着高速数字微系统中 DDR 总线信号传输速率与系统集成度的不断提高,过孔串扰问题成为影响系统信号完整性的不可忽视的因素之一。基于电磁耦合理论,通过建模仿真方法量化分析了过孔串扰的主要影响因素以及串扰噪声对信号质量的影响,在此基础上提出了过孔设计的主要原则以及减小串扰噪声的优化设计方法;介绍了一种正反面腔体结构系统级封装的信号处理微系统基板,结合 JEDEC 标准对 DDR3 总线进行了仿真分析与评估,通过以上方法优化过孔串扰大大改善了 DDR 总线的信号完整性,验证了该方法的正确性与有效性。

**关键词:** 过孔串扰;微系统;DDR;信号完整性

中图分类号: TN405.97

文献标识码: A

DOI:10.16157/j.issn.0258-7998.211356

中文引用格式: 张景辉,曾燕萍,王梦雅,等. 高速大容量 DDR 微系统过孔串扰研究[J]. 电子技术应用, 2021, 47(11): 100–104.

英文引用格式: Zhang Jinghui, Zeng Yanping, Wang Mengya, et al. Research on via crosstalk in high speed and large capacity DDR microsystems[J]. Application of Electronic Technique, 2021, 47(11): 100–104.

## Research on via crosstalk in high speed and large capacity DDR microsystems

Zhang Jinghui, Zeng Yanping, Wang Mengya, Zhou Qianrong, Yan Chuanrong

(China Electronics Technology Group Corporation No.58 Research Institute, Wuxi 214072, China)

**Abstract:** With the rapid increase of signal transmission rate and integration in high speed and large capacity digital microsystems, the influence of via crosstalk on signal integrity is becoming more and more prominent. Based on electromagnetic coupling theory, factors on via crosstalk and the influence of crosstalk noise on signal integrity are simulated and analyzed quantitatively by establishing simulation models. And some principles of via design and measures to decrease crosstalk noise are proposed. DDR3 bus in a microsystem in SiP(System in Package) technology, in which DDR units are mounted on both faces, is simulated and analyzed based on JEDEC DDR3 standard. Signal integrity of DDR bus is improved distinctly by reducing via crosstalk in a proper and effective measure proposed in this paper.

**Key words:** via crosstalk; microsystem; DDR; signal integrity

## 0 引言

采用并行传输技术的双倍速率同步动态随机存储器(Double Data Rate Synchronous Dynamic Random Access Memory, DDR SDRAM)是现代高速数字系统的主流应用,主控芯片与 DDR 存储器之间互联结构的信号完整性是保证整个系统运行的关键。DDR 拓扑的走线方式、阻抗匹配、端接方式、传输线的反射与串扰等问题是决定 DDRx 并行总线信号完整性的关键因素,也是系统设计研究的重点<sup>[1-3]</sup>。

随着现代数字系统数据传输速率越来越高,系统布线越来越密集,信号之间的串扰问题越来越突出<sup>[1]</sup>。对于信号串扰的研究主要集中在连接器、芯片封装与近间距的平行走线之间,过孔间的串扰问题是容易被忽略的因素。然而,对于采用系统级封装(System in Package, SiP)<sup>[4-5]</sup>的高速大容量 DDR 微系统来说,系统集成度进一步提高,

高速多层过孔普遍存在,造成过孔 Z 方向长度远大于水平方向的间距,过孔串扰成为不可忽视的问题。

本文简要分析了过孔串扰形成的基本原理与影响因素;利用频域、时域仿真平台建立过孔仿真模型,量化分析了系统中影响过孔串扰的主要指标以及串扰噪声对系统信号质量的影响,并且给出了完整的系统优化方案与仿真设计方法;结合实际项目案例验证了该方法的正确性与可行性,对以后高速数字系统互连结构设计具有一定的借鉴意义。

## 1 串扰理论

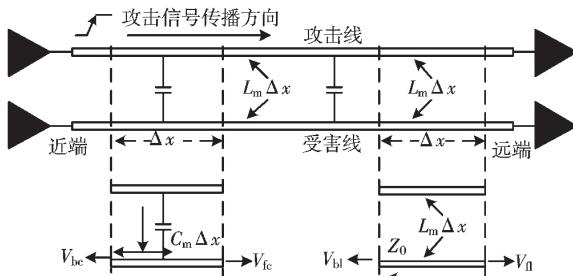

串扰源于耦合,导体间通过电场和磁场发生耦合,把信号的一部分能量传递到邻近的导体上,从而形成噪声。通常把产生干扰的信号称为攻击线,被干扰的信号称为受害线。串扰又分为容性串扰和感性串扰,容性串扰与感性串扰是同时发生的<sup>[6-8]</sup>。如图 1 所示:容性耦合

图 1 信号串扰集总参数模型

源于攻击线上的电压变化,变化的电压在受害线上引起感应电流;感性耦合源于攻击线上的电流变化,变化的电流在受害线上引起感应电压,从而导致电磁干扰。

将受害线上与攻击信号传播方向相反的一端称为近端,与攻击信号传播方向相同的一端称为远端;在受害线近端产生的容性、感性串扰分别为  $V_{nc}$ 、 $V_{nl}$ ,远端产生的容性、感性串扰分别为  $V_{fc}$ 、 $V_{fl}$ ,得到发生容性、感性耦合的远、近端串扰计算公式<sup>[9-10]</sup>:

$$\left\{ \begin{array}{l} V_{nc} = \frac{1}{4} \frac{C_m}{C} V_0 \\ V_{fc} = \frac{1}{2} \frac{Z_0 C_m l}{T_r} V_0 \end{array} \right. \quad (1)$$

$$\left\{ \begin{array}{l} V_{nl} = \frac{1}{4} \frac{L_m}{L} V_0 \\ V_{fl} = -\frac{1}{2} \frac{L_m l}{T_r Z_0} V_0 \end{array} \right. \quad (2)$$

其中,  $C$  与  $L$  分别代表导体单位长度的电容和电感,  $C_m$  与  $L_m$  分别代表单位长度的互容和互感,  $l$  代表耦合线的长度,  $Z_0$  为信号特征阻抗,  $T_r$  为干扰源的上升时间。

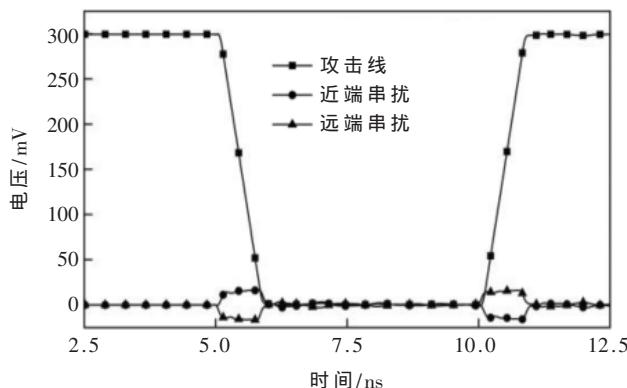

图 2 所示为攻击线上的波形与受害线上的远、近端串扰波形,受害线上同时包含了容性耦合电流与感性耦合电流。

图 2 远/近端串扰波形

以上分析可知,影响串扰的主要因素包括耦合长度、耦合线间距、传输线阻抗、干扰源信号速率等,而串扰对信号则会造成边沿的抖动与幅度上的噪声<sup>[11]</sup>,下面将搭建过孔仿真模型,对以上因素对信号串扰的影响做量化的仿真分析。

## 2 过孔串扰量化仿真分析

### 2.1 仿真模型搭建与仿真

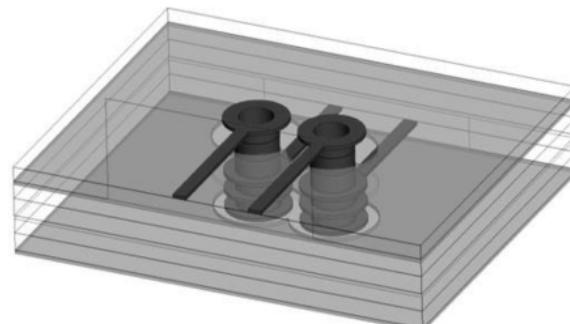

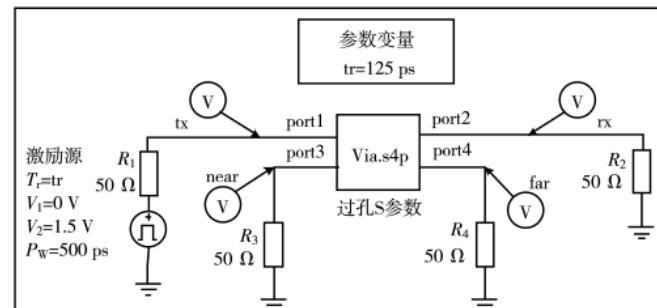

搭建仿真模型,分别对过孔间距  $S$ (孔间距与孔径比值)、过孔高度  $H_{via}$ (耦合长度)、攻击线数量  $N_A$  与信号上升时间  $T_r$  四个影响过孔串扰的因素进行定量仿真分析。利用 HFSS 仿真平台建立过孔三维仿真模型,提取不同条件下的过孔 S 参数,分析过孔之间的串扰;并且搭建时域仿真模型,仿真评估不同参数时串扰噪声幅值的大小<sup>[12-14]</sup>,如图 3 所示。

(a) 过孔 3D 模型

(b) 时域仿真模型

图 3 三维过孔模型与时域仿真拓扑

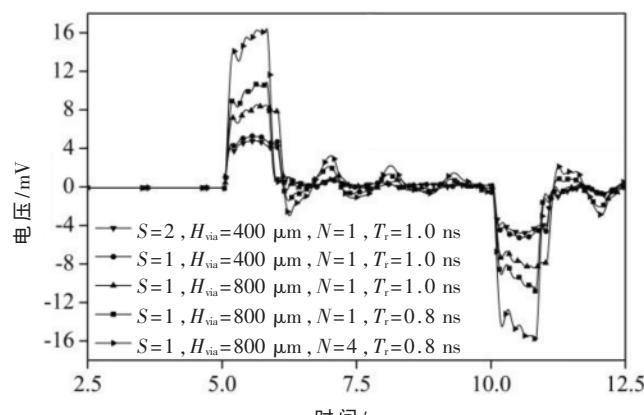

图 4 所示为不同参数时受害线上串扰噪声幅值曲线,可以看到当攻击线上的信号发生跳变时,在受害线上产生了串扰噪声。当过孔间距为 2 倍孔径、孔高为 400 μm,1 个攻击线,串扰源的上升时间为 1.0 ns 时,串

图 4 不同参数时的信号噪声波形对比

扰噪声为 4.78 mV;在此基础上,调节过孔的间距为 1,串扰噪声增加到 5.28 mV;当过孔高度由 400 μm 调节到 800 μm 时,噪声增加到 8.49 mV;接着,调节串扰源的上升时间为 0.8 ns,串扰噪声增加到 10.63 mV;而当攻击线的数量为 4 个时,串扰噪声增加到了 16.42 mV。

噪声的幅值大小变化趋势幅值结果与理论分析结果一致,以下对噪声幅值的变化进行定量分析,供优化设计做参考。

## 2.2 影响串扰因素定量分析

### 2.2.1 过孔间距的影响

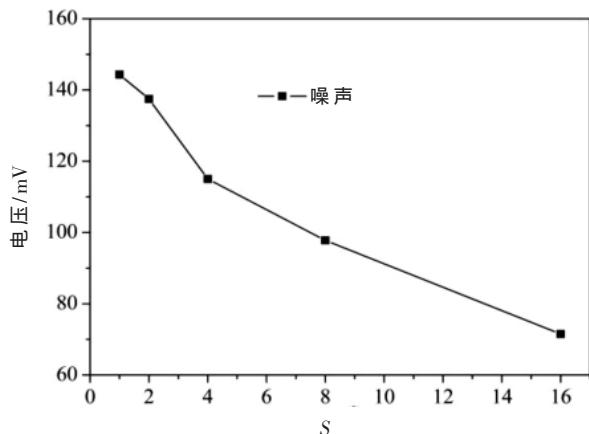

过孔间距决定耦合线单位长度互感  $L_m$  与互容  $C_m$  的大小,过孔间距越大,单位长度的互感与互容越小;式(1)、式(2)表明,近端串扰的大小与互感互容成正比;因此,随着过孔间距增加,串扰噪声则随之减小。如图 5 所示,当过孔间距  $S$  由 1 增加到 16 倍孔径时,互感互容随之减小,造成噪声幅值由 144.34 mV 减小到 71.49 mV;因此,在布线空间允许的条件下,应尽量增加过孔之间的间距,以达到减小串扰噪声的目的。

图 5 噪声幅值随过孔间距变化曲线

### 2.2.2 过孔高度的影响

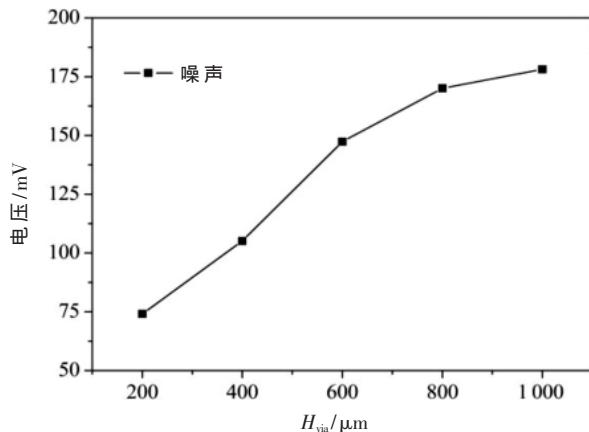

过孔高度  $H_{via}$ (耦合长度  $l$ )与串扰噪声的大小成正比。如图 6 所示,当过孔高度  $H_{via}$  由 200 μm 增加到 1 000 μm 时,噪声幅值由 74.12 mV 增加到 178.12 mV;因此,版图设计时,在满足传输线阻抗控制的条件下,应尽量减小过孔的高度,减少多层通孔设计,以减小过孔对串扰噪声以及对传输线阻抗匹配的影响。

### 2.2.3 信号上升时间的影响

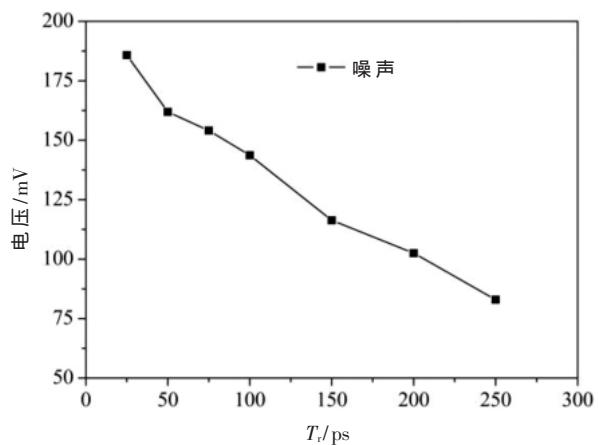

由以上分析可知,串扰噪声的大小与信号上升时间  $T_r$  成反比。仿真结果如图 7 所示:信号上升时间  $T_r$  由 25 ns 增加到 250 ns 时,噪声幅值由 185.83 mV 减小到 82.94 mV;因此,对于传输速率越高的信号,对于信号过孔的设计要求越严格。

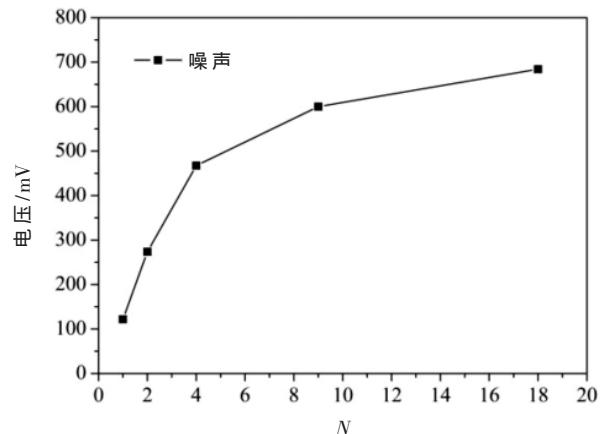

### 2.2.4 攻击线数量的影响

对于一个线性无源的系统,多个攻击线产生的串扰噪声也满足叠加定理,噪声幅值随攻击线数量变化的仿

图 6 噪声幅值随过孔高度变化曲线

图 7 噪声幅值随信号上升时间变化曲线

真结果如图 8 所示:当攻击线数量  $N_A$  由 1 个增加到 18 个时,噪声幅值由 121.91 mV 增加到 684.03 mV;由于攻击线数量越多,外层的攻击线距离受害线距离越远,耦合也就越弱,因此攻击线数量增加到一定程度后串扰量增加幅度越来越小,最终趋近于饱和。

图 8 噪声幅值随攻击线数量变化曲线

## 3 实例分析与仿真优化

### 3.1 基板设计

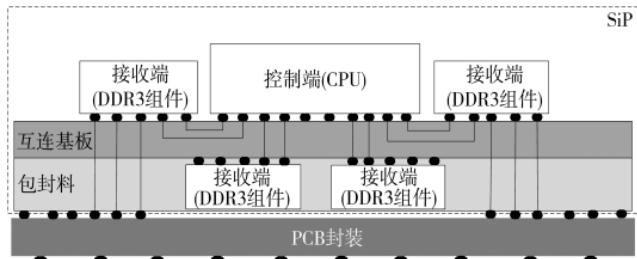

本项目 DDR 总线数据信号传输速率为 1.60 Gb/s,

由集成 4 个 DDR3 SDRAM 存储控制器的 CPU 控制 4 个 DDR3 总线通道, 每个通道由 9 个 DRAM 颗粒构成一个 72 位宽的 DRAM 接口, 单个 DRAM 颗粒的容量为 8 Gb; 如图 9 所示, SiP 基板采用正反面腔体结构, BGA 封装的控制端(CPU)贴装在基板正面, 而 4 个接收端(DDR3 组件)则排布在互连基板正反两面, 基板面积为 40 mm×60 mm, 采用 16 层堆叠结构, 其中芯板(Core)与 PP 层(Prepreg)厚度分别为 820  $\mu\text{m}$  与 30  $\mu\text{m}$ , 金属层厚度为 15  $\mu\text{m}$ 。

图 9 SiP 基板结构示意图

### 3.2 仿真结果

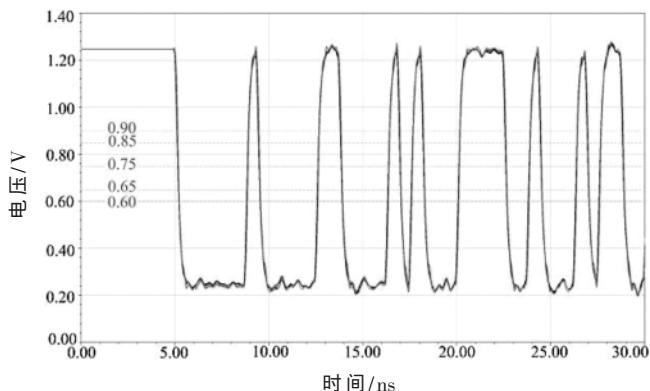

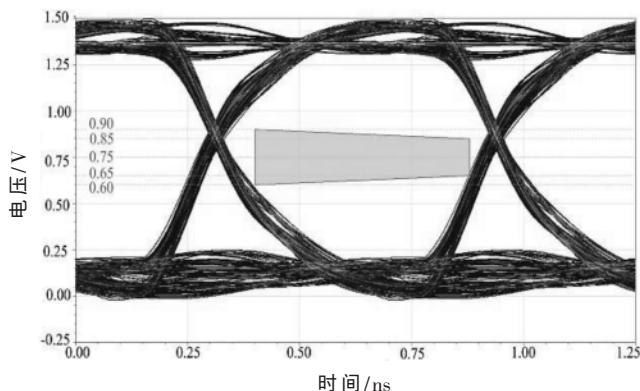

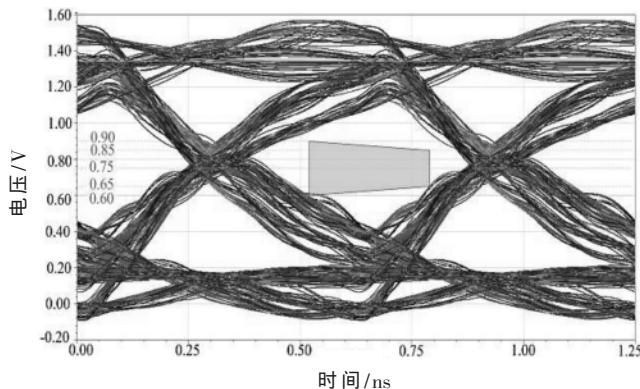

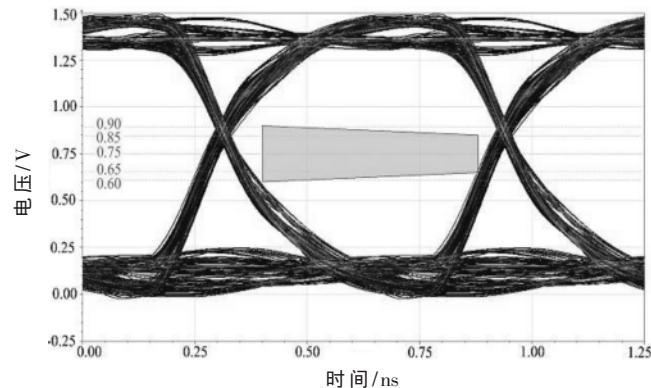

对 4 个 DDR3 组件的数据信号进行时域仿真, 得到波形与眼图仿真结果如图 10 所示。从仿真结果可以看出, 正面组件的数据信号质量明显优于反面组件的信号质量: 正面组件的眼高、眼宽分别为 944.1 mV、551.8 ps, 而反面组件的眼高、眼宽分别为 362.4 mV、165.2 ps, 根据

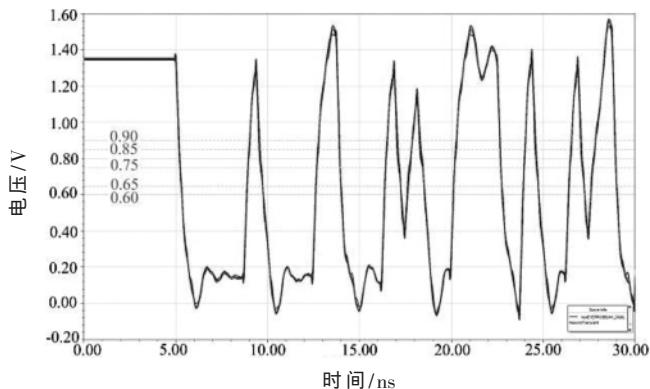

JEDEC DDR3 标准不满足眼图质量和时序裕量要求<sup>[15]</sup>。

结合基板结构与仿真结果分析可知: 正面组件与反面组件传输线的长度、阻抗控制与平面走线间距均一致, 单根数据线的波形、眼图质量一致, 而正、反面组件的区别是控制端到反面组件的数据走线存在大尺寸(位于 Core 层)、密集分布的过孔, 可初步判断过孔间的串扰造成信号上升/下降沿变缓, 使眼图质量恶化; 因此, 需要对过孔间串扰进行优化设计。

### 3.3 优化设计

由以上分析可知, 通过增大过孔间距、减小过孔高度或减小信号上升时间等可有效减小过孔之间的串扰噪声; 然而, 由于布线空间与工艺的限制, 以上优化方法难以实现。因此, 提出了信号过孔间添加回流地过孔的方案, 这种方法既可以提高信号过孔之间的隔离度, 有效抑制信号之间的串扰, 又可改善回流路径上的信号干扰。

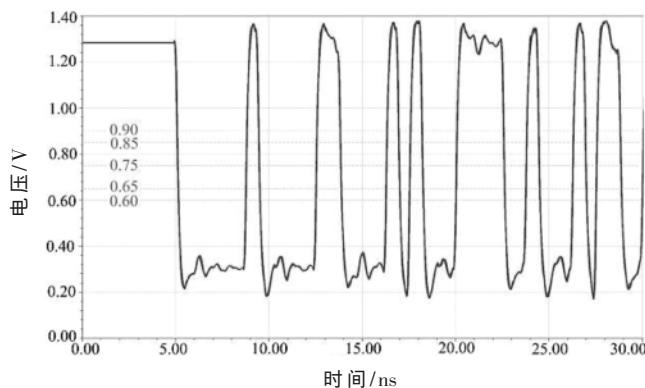

对优化后的系统结构进行时域仿真, 得到如图 11 所示的波形眼图结果。可以看出, 优化后的信号眼高由 362.4 mV 提高到 758.5 mV, 眼宽由 165.2 ps 增加到 560.2 ps, 可满足时序裕量要求。

### 4 结论

本文对系统级封装的 DDR 微系统中的信号完整性进行了研究, 通过理论研究与建模仿真分析的方法对过孔串扰问题进行了分析与研究, 量化分析了过孔间距、

(a) 正面组件数据信号波形

(c) 反面组件数据信号波形

(b) 正面组件数据信号眼图

(d) 反面组件数据信号眼图

图 10 DDR3 数据信号波形眼图结果

(a)优化后信号波形

(b)优化后信号眼图

图 11 优化后反面组件数据信号波形与眼图

过孔高度、过孔数量与信号上升时间对串扰噪声的影响以及串扰噪声对信号完整性的影响，在此基础上提出了过孔设计的基本原则与过孔串扰优化的方法；结合实际项目案例，通过增加回流地过孔的方法改善了过孔之间的串扰，得到了符合要求的信号波形与眼图仿真结果，对高速大容量信号过孔设计与串扰噪声优化设计有一定的借鉴意义。

#### 参考文献

- [1] JOHNSON H.高速数字设计[M].沈立,朱来文,陈宏伟,等译.北京:电子工业出版社,2004:203–206.

- [2] 周润景,苏良碧.Cadence 高速电路板设计与仿真(第四版)[M].北京:电子工业出版社,2011:377–386.

- [3] 侯斌,杨祎,巩稼民,等.高速大容量存储电路板的信号性能分析研究[J].现代电子技术,2015,38(13):137–140.

- [4] RIKO R.More-than-Moore 2.5D and 3D SiP Integration[M].West Berlin:Springer Publishing Company,2017.

- [5] LI Y, GOYAL D.3D microelectronic packaging (from fundamentals to applications)[M].West Berlin:Springer Publishing Company,2017.

- [6] BOGATIN E.信号完整性与电源完整性分析[M].李玉山,刘洋,初秀琴,等译.北京:电子工业出版社,2019:254–260.

- [7] 孟辰.高速电路中反射、串扰及 SSN 的分析与研究[D].西安:西安电子科技大学,2013.

- [8] QIAN L B,ZHU Z M,XIA Y S,et al.Through-silicon-via crosstalk model and optimization design for three-dimensional integrated circuits[J].Chinese Physics,2014,23(3):1–11.

- (上接第 94 页)

- [15] DANIELYAN A,FOI A,KATKOVNIK V,et al.Image upsampling via spatially adaptive block-matching filtering[C]//2008 16th European Signal Processing Conference,Lausanne,2008:1–5.

- [16] ZHAN Y,LI S J,LI M.Local and nonlocal regularization to image interpolation[J].Mathematical Problems in Engineering,2014(1):1–8.

0903002.

- [9] 刘烨铭,曹跃胜.高速多层板过孔分析与仿真[J].计算机工程与设计,2008,29(3):713–715.

- [10] 董辉,马祖杰.基于 Cadence 的 DDR2 串扰研究与仿真[J].浙江工业大学学报,2016,44(3):266–269.

- [11] 高振斌,郝晓雪,王蒙军,等.高速 BGA 封装与 PCB 差分互连结构的设计与优化[J].现代电子技术,2017,40(22):137–141.

- [12] 白金.基于高速数字信号电路的完整性设计[D].西安:西安电子科技大学,2014.

- [13] 曾燕萍,张景辉,王梦雅,等.DDR3 堆叠键合组件的信号完整性分析与优化[J].电子与封装,2020,20(12):120201.

- [14] 刘明阳,李勇量.三维电磁仿真在 25Gbps 串行收发通道设计中的应用方法[J].电子技术应用,2018,44(8):23–27.

- [15] JEDEC.DDR3 SDRAM specification :JESD 79–3F[S].Arlington:JEDEC,Jul 2012.

(收稿日期:2021-02-01)

#### 作者简介:

张景辉(1994–),男,硕士研究生,工程师,主要研究方向:信号完整性与电源完整性仿真。

曾燕萍(1987–),女,博士研究生,高级工程师,主要研究方向:三维集成系统级设计和仿真技术。

王梦雅(1992–),女,硕士研究生,工程师,主要研究方向:信号完整性与电源完整性仿真。

扫码下载电子文档

- [17] 海涛,席志红.基于改进复扩散耦合非局部均值滤波器的图像放大[J].系统工程与电子技术,2016,38(5):1182–1188.

(收稿日期:2020-07-21)

#### 作者简介:

海涛(1974–),通信作者,男,博士,讲师,主要研究方向:图像分辨增强、非线性信号处理,E-mail:nytcht@163.com。

扫码下载电子文档

## 版权声明

经作者授权，本论文版权和信息网络传播权归属于《电子技术应用》杂志，凡未经本刊书面同意任何机构、组织和个人不得擅自复印、汇编、翻译和进行信息网络传播。未经本刊书面同意，禁止一切互联网论文资源平台非法上传、收录本论文。

截至目前，本论文已经授权被中国期刊全文数据库（CNKI）、万方数据知识服务平台、中文科技期刊数据库（维普网）、DOAJ、美国《乌利希期刊指南》、JST 日本科技技术振兴机构数据库等数据库全文收录。

对于违反上述禁止行为并违法使用本论文的机构、组织和个人，本刊将采取一切必要法律行动来维护正当权益。

特此声明！

《电子技术应用》编辑部

中国电子信息产业集团有限公司第六研究所