# 龙芯 3A4000 主板 VGA 接口电路设计及研究 \*

籍明慧<sup>1,2</sup>,裴焕斗<sup>1,2</sup>,宫健<sup>1,2</sup>,张川川<sup>2</sup>,庄杰<sup>2</sup>

(1.中北大学 仪器与电子学院,山西 太原 030051;2.山西百信信息技术有限公司,山西 太原 030006)

**摘要:** VGA 接口以其良好的兼容性、成熟的技术优势、较低的成本等优点成为电子设备显示应用中最为广泛的接口类型。基于龙芯 3A4000 主板功能性要求,利用高性能视频数模转换芯片 ADV7125 将 DVO 总线数字信号转换为模拟信号通过 VGA 接口实现视频输出。对 VGA 接口及实现原理做了基本介绍,并对 VGA 视频输出功能拓扑结构以及 VGA 接口电路设计做了详细的描述。测试结果表明,对于不同显示模式的视频信号,该接口电路设计均符合功能性和可靠性要求,视频显示功能正常且性能良好。

**关键词:** 龙芯 3A4000; VGA 接口; ADV7125; 电路设计

中图分类号: TN919

文献标识码: A

DOI:10.16157/j.issn.0258-7998.211483

中文引用格式: 翟明慧,裴焕斗,宫健,等. 龙芯 3A4000 主板 VGA 接口电路设计及研究[J]. 电子技术应用, 2021, 47(11): 105–109, 115.

英文引用格式: Ji Minghui, Pei Huandou, Gong Jian, et al. Design and research on VGA interface circuit of Loongson 3A4000 motherboard[J]. Application of Electronic Technique, 2021, 47(11): 105–109, 115.

## Design and research on VGA interface circuit of Loongson 3A4000 motherboard

Ji Minghui<sup>1,2</sup>, Pei Huandou<sup>1,2</sup>, Gong Jian<sup>1,2</sup>, Zhang Chuanchuan<sup>2</sup>, Zhuang Jie<sup>2</sup>

(1.School of Instrument and Electronics, North University of China, Taiyuan 030051, China;

2.Shanxi 100 Trust Information Technology Co., Ltd., Taiyuan 030006, China)

**Abstract:** Video Graphics Array(VGA) interface has become the most widely interface type in the display application of electronic devices with its good compatibility, mature technical advantages and low cost. Based on the functional requirements of Loongson 3A4000 motherboard, DVO bus signal is converted to analog signal by using the ADV7125, a high-performance video digital-to-analog converter(DAC), and video signal is exported through VGA interface. The VGA interface and implementation principle are introduced, the VGA video output function topology and the circuit design of VGA interface are described in detail. The results show that the interface circuit design meets the requirements of functionality and reliability for video signals of different display modes, and the video display is normal with good performance.

**Key words:** Loongson 3A4000; VGA interface; ADV7125; circuit design

## 0 引言

随着电子产业的快速发展,视频接口技术也从早期的 BNC、S-端子、VGA 等接口发展到如今的 DVI、HDMI 以及 DP 等数字视频接口<sup>[1]</sup>,有了长足的进步。但是在视频数字化的潮流中,VGA 仍以成熟的技术优势、良好的兼容性和通用性以及相比之下较低的成本被广泛应用,是主板、嵌入式设备及高端显示器等设备上最主要的接口。同时 VGA 接口对于那些需要模拟信号进行显示的机器是不可替代的,在技术产品革新替代中有着重要的作用。在针对国产化 CPU 龙芯 3A4000 进行主板开发时,面向国产机器替代,逐步实现国产化的要求,VGA 接口的设计成为其中重要的一环。陈锴然<sup>[2]</sup>对不同视频传

输标准的传输方式与优劣进行了分析对比,简要介绍了各种视频传输标准的应用场景;陈桂、朱丽婷、付宗宝及郑佃好<sup>[3-6]</sup>等人基于几种 ARM 芯片控制 ADV7120、ADV7125 和 THS8134B 等高性能视频 D/A 转换芯片将 LCD 扫描式接口转换为了 VGA 接口,具体介绍了其电路设计。笔者在开发基于龙芯 3A4000(MIPS 架构)的通用主板的过程中,提出一种利用高性能视频 D/A 转换芯片 ADV7125 将 DVO 总线数字信号转换为模拟信号通过 VGA 接口实现视频输出的电路设计方法,该设计电路简单可靠,且有较好的防护性和信号质量。本文将详细介绍设计中的结构思路、电路设计及测试结果。

## 1 VGA 接口

### 1.1 简介及原理

VGA 是 IBM 于 1987 年提出的一个使用模拟信号的

\* 基金项目: 山西省科学技术厅安全可信计算机主板研发和产业化项目

(201903D111003)

电脑显示标准<sup>[7]</sup>, 标准定义了VGA信号外部接口互连的电气特性标称值、机械配接要求以及其信号传输原理(时序规范)。顾名思义,VGA接口就是用来专门针对于VGA标准输出数据的接口, 具有多分辨率模式、模拟信号输出、数据传输速度快等优点, 以其良好的兼容性、成熟性、可靠性被广泛应用于视频显示领域。

在进行视频显示时, 第一步系统内部首先将视频信息解码为数字型图像信息缓冲至显存芯片中, 然后高性能视频D/A芯片调用数字视频信号经过模拟调制成为R、G、B三原色模拟数据信号和行(HSYNC)、场(VSYNC)同步控制信号, 最后信号遵循VGA时序通过VGA接口传输到显示设备中, 其中行、场同步信号的作用是处理输入模拟信号以及联合起来控制VGA的显示时序。由VGA显示工业标准可知, VGA的显示时序在不同显示模式和刷新频率下, 各个模式行、场时序图轮廓基本一致, 都由同步脉冲、显示后沿、显示时序段和显示前沿组成, 只是每一段时序的状态持续时间不同。

## 1.2 VGA接口引脚定义

VGA接口的物理外形是一个15针孔的插座, 分为三排, 每排五个针孔。其传输信号主要有以下几种类型:

- (1) 模拟数据信号: 红、绿、蓝3基色RGB信号;

- (2) 同步控制信号: 行/场同步信号(H/VSYNC);

- (3) 电源、地: 1个通用地, 3个对应彩色分量信号地, 一个对应控制信号地, 一个+5 V电源。

其中行场同步信号(HSYNC、VSYNC)用来处理3根RGB彩色分量信号, 同时配合起来控制VGA的显示时序, 当工作在不同模式时, 行同步信号和场同步信号的波形也各不相同。VGA接口引脚定义见表1。

表1 VGA接口引脚定义

| 引脚   | 描述             | 引脚 | 描述                |

|------|----------------|----|-------------------|

| 1    | RED(红基色分量信号)   | 8  | BGND(蓝基色分量地线)     |

| 2    | GREEN(绿基色分量信号) | 9  | +5 V              |

| 3    | BLUE(蓝基色分量信号)  | 10 | SGND(地线)          |

| 4,11 | NC(未使用)        | 12 | DDC_DATA(DDC数据信号) |

| 5    | GND(地线)        | 13 | HSYNC(行同步信号)      |

| 6    | RGND(红基色分量地线)  | 14 | VSYNC(场同步信号)      |

| 7    | GGND(绿基色分量地线)  | 15 | DDC_CLK(DDC时钟信号)  |

## 1.3 VGA接口时序要求

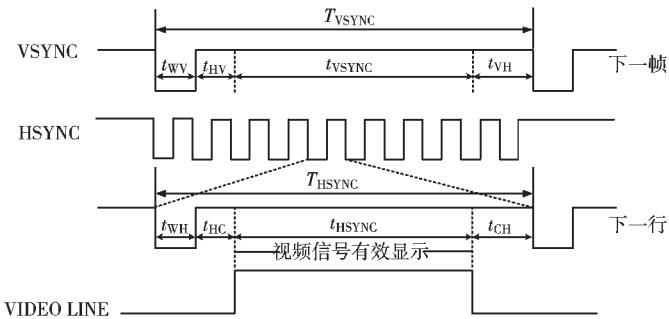

前文提到, VGA的显示时序是由行、场同步信号配合控制的。针对不同显示模式和刷新频率, VGA接口的时序也有不同表现方式, 但是其行场时序结构都是一致的, 均由同步脉冲、显示后沿、显示时序段和显示前沿组成, 只是其不同状态占用时间不同。图1为VGA的信号时序图。

如图1所示, 行、场同步信号在每行/帧开始的时候均产生一个的低脉冲信号, 且对应的同步脉冲均为负脉冲, 在难以分辨不同模式下同步脉冲的周期时, 会将

图1 VGA信号时序

其反相处理到达区分效果<sup>[8]</sup>。

VGA时序包括行、场扫描时序两个部分, 其时序参数有四个部分: 行(场)同步脉冲( $t_{WH}, t_{HV}$ )、显示后沿( $t_{HC}, t_{VH}$ )、有效显示区宽度( $t_{Hsync}, t_{Vsync}$ )、显示前沿( $t_{CH}, t_{VH}$ )。开始扫描时, 第一步进行的是行同步操作, 同步操作完成后开始真正的数据扫描工作<sup>[9]</sup>。VSYNC是完成一帧扫描所需要的时间, 称为场扫描周期, 其倒数被称为场频, 又称刷新频率; 行扫描时序与场扫描时序的结构是一致的, 此处不再细说。其中各个状态所占用时间可通过刷新频率即场频得出, 场扫描周期即为场频的倒数, 行扫描周期则通过场扫描周期和所扫描行数计算得知。

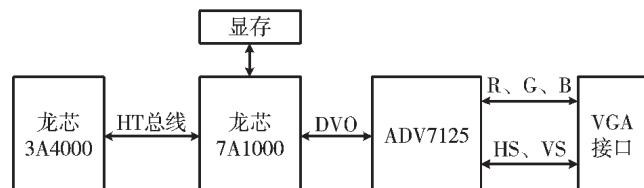

## 2 接口功能实现整体结构

本文基于龙芯3A4000 CPU的开发背景下进行VGA接口设计, 整体采用龙芯3A4000+7A1000的架构, 通过龙芯7A1000桥片(后文简称桥片)扩展显存以及VGA接口, 利用高性能视频D/A转换芯片ADV7125将DVO数字信号转换为模拟信号进行视频显示。整体结构如图2所示。

图2 整体结构框图

龙芯3A4000是龙芯3号系列处理器中首款基于GS464v微架构的四核处理器, 采用28 nm FD-SOI工艺, 主频稳定工作在1.5 GHz~2.0 GHz, 其性能与龙芯3A3000相比提升达一倍左右<sup>[10]</sup>。桥片与龙芯3A4000之间通过HT高速总线相连, 内部集成2D/3D GPU(100~500 MHz)、显示控制器以及显存接口, 同时集成PCIE以及USB、I2C、SPI等多个高低速接口。

本次设计主要依托于桥片内部集成的显示控制器接口, 桥片显示控制器支持双路DVO显示, 每路最大支持1920×1080@60Hz, 支持RGB444、RGB555、RGB565、RGB888四种色深。桥片显示控制器提供了数据传输引脚和时序控制引脚, 包括行场同步信号DVO\_HSYNC/VSYNC以及

24位数字数据信号DVO\_D[23:0],其主要负责图像数据处理、VGA接口时序实现以及配置芯片ADV7125的工作模式,并把处理后的帧数据以点为单位送SDRAM显示存储器。进行视频显示时,调用显存中图像数据经桥片处理后传输至D/A芯片ADV7125进行模数转换,最后模拟图像信号遵循VGA时序通过VGA接口传输到显示设备中。此次设计采用单片2Gb×16bit的SUMSUNG公司的DDR3 SDRAM芯片K4B2G1646Q-BCK0作为显示存储器,可以满足高速数据收发存储的功能需求。

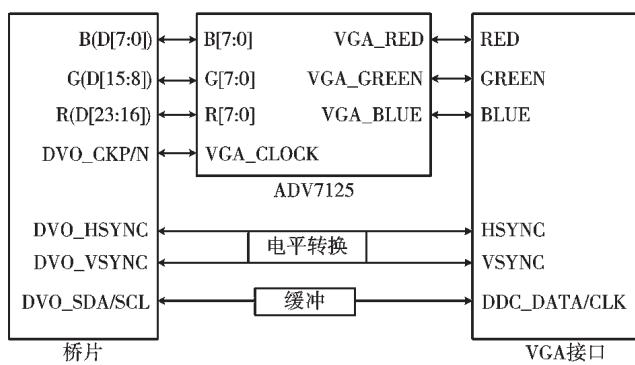

根据桥片设计手册规定,VGA接口的同步信号需要由桥片显示控制器提供,故利用ADV7125可以方便地将桥片的DVO接口转换成VGA接口。DVO接口的数据位DVO\_D[23:0]分别对应RGB888,即:DVO\_D[23:16]对应RGB信号的R[7:0],DVO\_D[15:8]对应RGB信号的G[7:0],DVO\_D[7:0]对应RGB信号的B[7:0]。在本系统中ADV7125工作在RGB888模式,故在设计中分别将DVO接口数据信号DVO\_D[7:0]、DVO\_D[15:8]、DVO\_D[23:16]分别与ADV7125芯片的VGA\_B[7:0]信号、VGA\_G[7:0]信号和VGA\_R[7:0]信号相连接。ADV7125芯片的时钟信号由桥片差分时钟提供,DVO接口中的同步扫描信号HSYNC和VSYNC以及I2C总线控制信号直接接到VGA接口。同时为了支持显示器热插拔功能,使用SPI\_CSn2(复用为GPIO功能)作为DVO通道的显示器热插拔检测引脚。信号走向如图3所示。

图3 整体信号流向图

### 3 电路设计

由于同步控制信号由桥片直接提供且VGA时序已经确定,故利用ADV7125将DVO数据信号转换成VGA接口电路并不复杂,在设计时严格考虑到芯片的基本特性和信号输入要求即可。整体电路可分为桥片到ADV7125芯片数据传输转换以及转换后信号处理并输出两个部分,下面就ADV7125芯片特性、桥片到芯片ADV7125电路连接、VGA接口设计以及关键信号的处理做详细介绍。

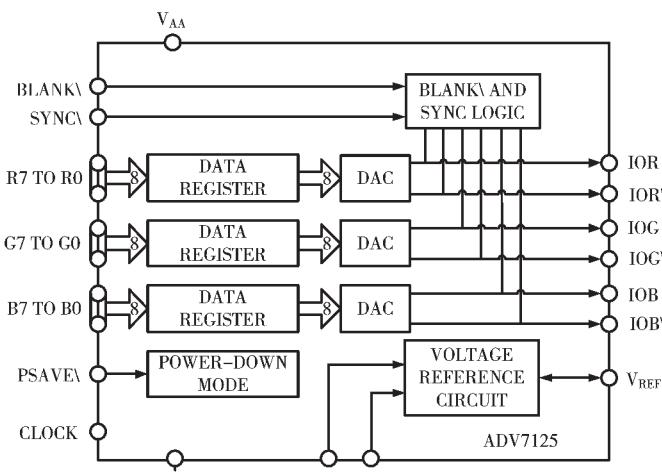

#### 3.1 ADV7125

ADV7125是一个单芯片高速数模转换器,吞吐量达330MS/s,内置着三个独立的8位高速分段式架构互补

输出高速DAC,分别对应三个具有8位寄存器的输入通道,用来接收数字信号并对视频数据做对应处理,24位像素数据(颜色信息)在每个时钟周期的上升沿锁存至器件内,之后被提供给三个8位DAC,然后转换为三个模拟(RGB)输出波形<sup>[11]</sup>。ADV7125还有两个附加的控制信号BLANK和SYNC,以与像素数据相似的方式锁存至模拟视频输出,分别在CLOCK的上升沿锁存,以便与像素数据流保持同步,共同作为ADV7125的输出信号。

ADV7125采用单芯片设计,使用相同的电流源保证了单调性和低毛刺,片内运算放大器保证了满量程输出电流在面对温度和电源变动时的稳定性<sup>[12]</sup>。采用可以进行调节的+5V/+3.3V电源供电,可配置省电模式,多应用于数字视频系统、高分辨率彩色图形、图像处理等方面。其功能框图如图4所示。

图4 ADV7125 功能框图

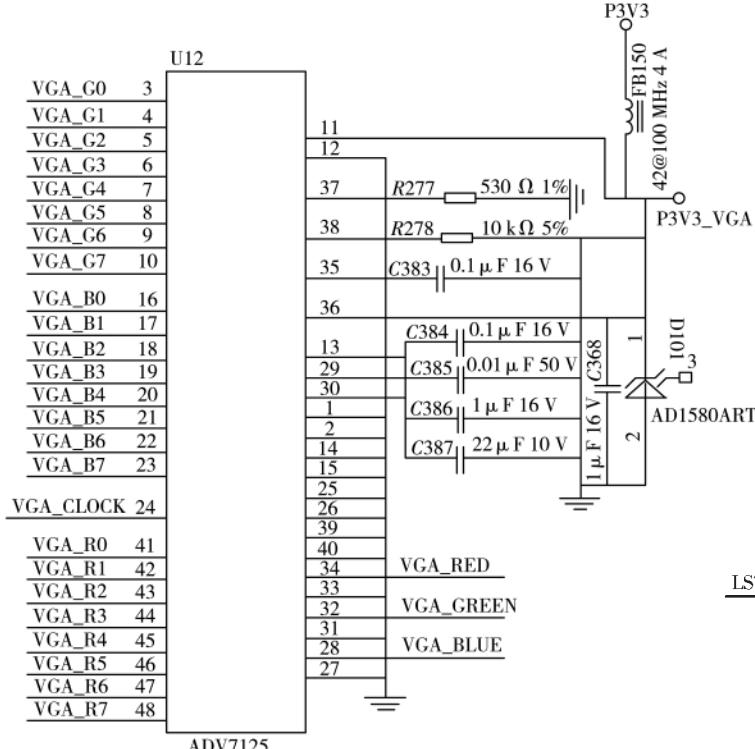

#### 3.2 桥片与ADV7125连接电路设计

由于VGA接口的同步信号由显示控制器提供,故只要将DVO接口数据的DVO\_D[7:0]、DVO\_D[15:8]和DVO\_D[23:16]分别与ADV7125芯片的VGA\_B[7:0]、VGA\_G[7:0]和VGA\_R[7:0]直接连接进行数字信号传输,ADV7125芯片的时钟信号由显示控制器内部时钟源产生的差分时钟提供。详细电路设计图如图5所示。

图5中VGA\_B[7:0]、VGA\_G[7:0]、VGA\_R[7:0]、VGA\_CLK为桥片的输出端。COMP端达到补偿内部参考运放的功能,通过在COMP引脚与P3V3\_VGA之间连接一个0.1μF的电容来实现。ADV7125是高精度DAC芯片,对于参考电平的要求很高,如果以电阻分压的方式得到参考电压的话效果并不好,根据ADV7125设计手册在电路设计时采用1.235V电压基准芯片AD1580来产生参考电压,可以得到稳定的参考电平。ADV7125的REST引脚专门用来控制视频信号幅度,考虑到阻值要求,固定的530Ω用2个200Ω和1个130Ω的电阻来代替,便于后期调节。同时ADV7125的SYNC引脚用来控制单一复合同步输入,由于桥片的图形处理器可以生

图 5 ADV7125 与桥片连接电路

成水平同步(HSYNC)、垂直同步(VSYNC)和复合 SYNC 信号,不需要 ADV7125 产生同步信号,故将 SYNC 拉到地,使其永久低电平。省电控制引脚 PASVE 为低有效,此处同样将其接地,实现功耗降低。另外在布局设计时使用了尽可能短的电容引线,尽可能将电容靠近器件放置,将每个 VAA 引脚单独去耦至地,最大程度地降低了引线电感。

### 3.3 VGA 接口设计以及关键信号的处理

考虑桥片 VGA 接口设计要求、信号保护、信号缓冲等方面因素，设计 VGA 接口电路如下，分以下三方面进行介绍，并在最后给出 VGA 接口原理图。

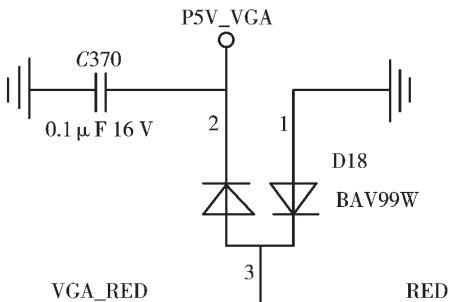

输出模拟视频信号的处理:(1)在三个模拟输出的引脚上分别搭配一个 $75\Omega$ 的端接电阻到地,以达到最佳性能,并且在PCB布局时尽可能地靠近了转换芯片去削弱信号反射。(2)在信号抵达接口之前,通过LC滤波电路对模拟信号进行一级滤波优化处理;(3)使用快速开关二极管BAV99W进行电路保护,BAV99W相当于两个二极管,其开关速度快于一般二极管,其接法如图6所示。

VGA\_RED/GREEN/BLUE、LS7A\_DVO\_HSYNC/NSYNC 均经过此电路处理。公共端接所需要保护的信号，另两端一个接电源，一个接地，可以实现泄放超额电压从而稳定电压的作用。

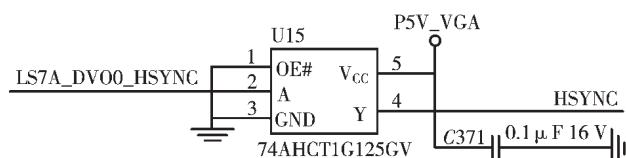

同步信号缓冲处理：视频同步信号由桥片显示控制器产生，由设计要求直接输出至 VGA 接口，故需要对信号 LS7A DVO HSYNC/N 做缓冲处理。本次设计使用

图 6 BAV99W 连接方式

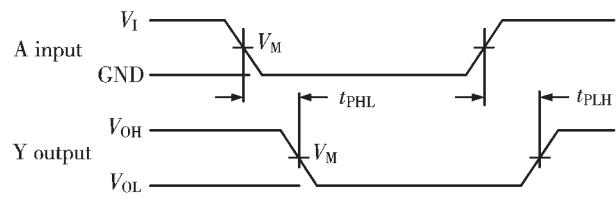

74AHCT1G125GV 非逆变缓冲器实现信号缓冲，电路连接以及输入(A)到输出(Y)传播延迟如图 7、图 8 所示。

图 7 74AHCT1G125GV 连接方式

图 8 输入(A)到输出(Y)传播延迟

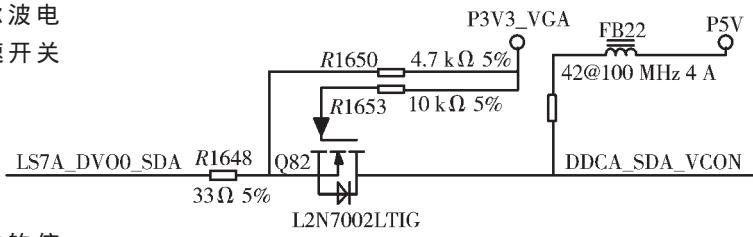

I<sup>2</sup>C 控制信号的电平转换：桥片的每个 DVO 接口都自带了一组 I<sup>2</sup>C 信号(使用 GPIO 模拟), 连接 DVO 接口的转换 PHY 芯片和显示器, 专门用于显示器检测。根据桥片设计要求, 必须使用该组 I<sup>2</sup>C 信号连接显示器接口, 而不使用 PHY 芯片输出的 I<sup>2</sup>C 引脚。桥片输出 I<sup>2</sup>C 信号电平为 TTL 电平, 而 VGA 接口需要电平为 5 V, 故需要对 SDA/SCL 信号进行电平转换, 此处设计使用常规的 MOS 管实现电平转换, 电平转换电路如图 9 所示。

图 9 电平转换电路

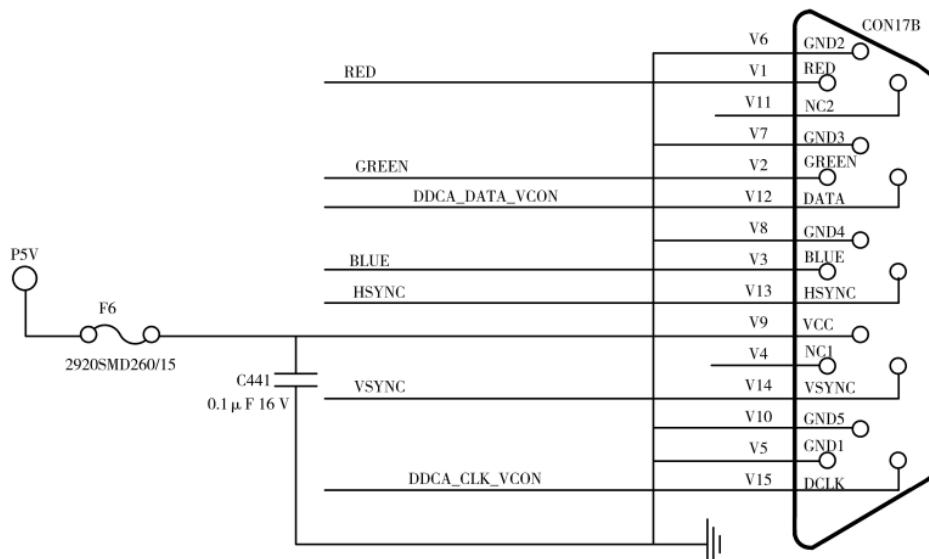

视频信号、同步信号以及 I<sup>2</sup>C 信号经过处理后连接至 VGA 接口即可实现视频输出功能。除此之外，还使用了保险丝对 VGA 接口进行了保护。VGA 接口及信号如图 10 所示。

图 10 VGA 接口及信号

#### 4 测试结果

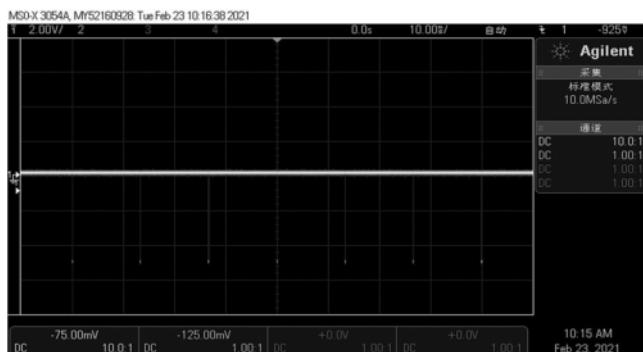

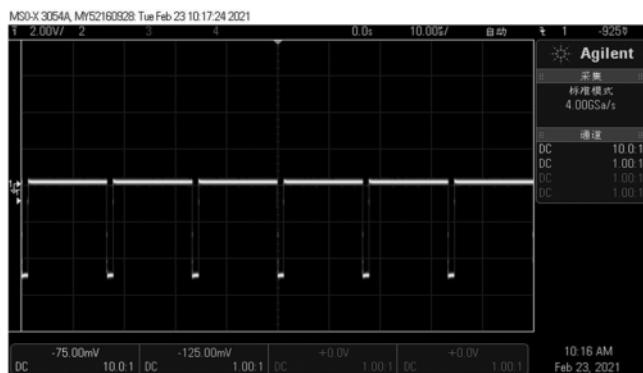

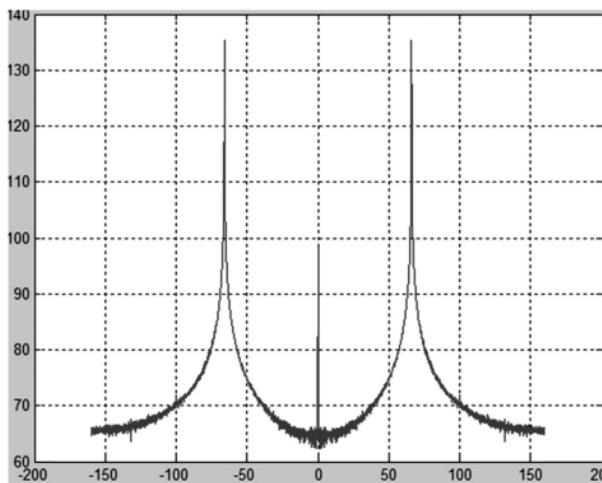

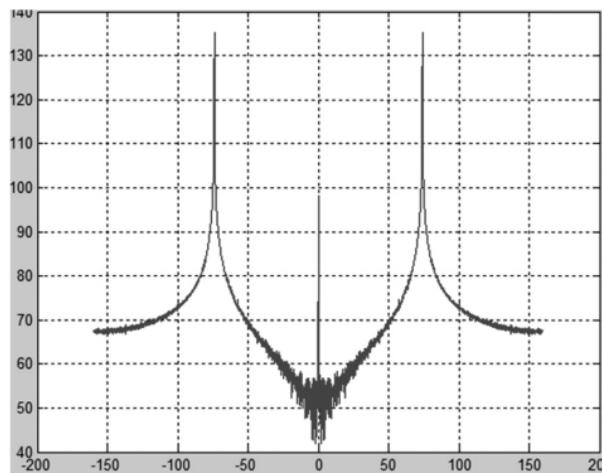

硬件调试后,针对 VGA 接口标准进行测试,分辨率设定为 1024\*768@60Hz,利用 MSO-X 3054A 示波器对行场同步信号 HSYNC、VSYNC 进行测试,结果如图 11、图 12 所示。

图 11 HSYNC 波形图

图 12 VSYNC 波形图

由图中分析可知:HSYNC 的周期为 20.68 μs,VSYNC 的周期为 16.67 ms,与 1024×768@60Hz 模式下的 VGA 接口时序要求一致,效果达到设计要求。同时,由模拟信号波形图可得知其输出电压在 0~0.7 V 之间,均符合 VESA

标准及增强型数据显示通道标准。利用 VGA 适配器将主板 VGA 接口与显示器接口连接,显示器画面可正常显示,且无明显抖动,显示性能良好。

#### 5 结论

本文在龙芯 3A4000 的开发背景下进行了 VGA 接口的设计,通过高性能 D/A 视频转换芯片 ADV7125 将桥片输出 DVO 数字信号转换为模拟信号,并将模拟信号传输至 VGA 接口,实现视频显示的功能。根据 VGA 时序要求以及桥片设计要求进行电路设计,并考虑了信号质量以及接口防护方面的要求。经过测试,通过 VGA 接口实现视频输出功能正常,性能良好,目前已成功应用于龙芯 3A4000 主板,满足功能性、可靠性要求,同时达到了产品级别的要求。

#### 参考文献

- [1] 范科峰,赵新华,张素兵,等.数字音视频接口技术标准分析[J].信息技术与标准化,2007(6):22~26.

- [2] 陈锴然.多种视频传输方式的应用研究[J].网络安全技术与应用,2018(5):75,80.

- [3] 陈桂,田学隆,陈南西.ARM 嵌入式平台的 VGA 接口设计[J].单片机与嵌入式系统应用,2007(4):25~28.

- [4] 朱丽婷,赵哲.S3C2440 的嵌入式 VGA 接口设计[J].杭州电子科技大学学报,2010,30(5):45~48.

- [5] 付宗宝,刘向阳,夏林根.基于 ADV7120 的嵌入式 VGA 接口设计与实现[J].自动化技术与应用,2012,31(6):42~46.

- [6] 郑佃好,张红雨,张洪斌.基于 ADV7125 的嵌入式系统 VGA 接口设计[J].单片机与嵌入式系统应用,2011,11(8):37~

- [7] 李荣翠.基于 FPGA 的图像压缩感知算法研究[D].贵阳:贵州大学,2018.

- [8] 王跃霖.基于 FPGA 的动态目标检测与跟踪系统的研究[D].

(下转第 115 页)

图 14 66 MHz 带频响应

图 15 74 MHz 带频响应

## 参考文献

- [1] 杨小牛.从软件无线电到认知无线电,走向终极无线电——无线通信发展展望[J].中国电子科学研究院学报,2008(1):1-7.

- [2] 张飞,伍小保.广义多相滤波及其应用[J].雷达科学与技术,2014(3):262-266.

- [3] 朱小华,王建新,于雷.多相滤波法实现的数字正交相干检波器[J].南京理工大学学报,2001(6):642-645.

- [4] 吴兵,张飞,伍小保.宽带数字波形产生中的广义多相滤

(上接第 109 页)

- 兰州:兰州交通大学,2018.

- [9] 王涌,肖顺文,罗春梅.基于 Verilog 的 VGA 显示控制电路设计[J].数字技术与应用,2019,37(4):150-151,153.

- [10] 龙芯中科技术有限公司.Loongson\_3A4000\_user.pdf[DB/OL].[2020-08-13].[http://www.loongson.cn/uploadfile/cpu/3A40\\_00user.pdf](http://www.loongson.cn/uploadfile/cpu/3A40_00user.pdf).

- [11] ADV7125 芯片数据手册[DB/OL].[2020-09-05].[https://www.analog.com/media/cn/technical-documentation/data-sheets/ADV7125\\_cn.pdf](https://www.analog.com/media/cn/technical-documentation/data-sheets/ADV7125_cn.pdf).

波[J].雷达科学与技术,2016(4):422-426.

- [5] 江春燕,周胜源,陈星.基于软件无线电多相滤波的数字正交变换技术[J].电子设计工程,2010(6):89-92.

- [6] 罗星华,苏涛.基于多相滤波原理的数字正交采样技术[J].现代电子技术,2008(3):27-30.

- [7] 徐荣华,胡修林.基于多相滤波结构的宽带接收机数字下变频研究[J].计算机与数字工程,2007(4):50-54.

- [8] 支蔚秋.基于多相滤波的星上数字波束形成网络中关键技术的研究[D].西安:西安电子科技大学,2008.

- [9] 周沿海.基于多相滤波的信道化发射机研究[J].通信技术,2012(4):27-30.

- [10] 曾斌,龙慧敏.基于多相滤波的宽带数字接收机二次变频设计[J].电讯技术,2008(9):43-46.

- [11] 谢裕进.基于多相滤波的宽带数字接收机的研究与 FPGA 实现[D].南京:南京航空航天大学,2009.

- [12] A·V·奥本海默.信号与系统(第二版)[M].刘树棠,译.西安:西安交通大学出版社,2001.

- [13] A·V·奥本海默.离散时间信号处理(第二版)[M].刘树棠,等译.西安:西安交通大学出版社,2001.

- [14] 杜勇.数字滤波器的 MATLAB 与 FPGA 实现[M].北京:电子工业出版社,2012.3

- [15] INGLE V K.数字信号处理及其 MATLAB 实现[M].陈怀琛,等译.北京:电子工业出版社,1998.

- [16] 程佩青.数字信号处理教程[M].北京:清华大学出版社,2001.

- [17] 周耀华,汪凯仁.数字信号处理[M].上海:复旦大学出版社,1992.

- [18] 陈亚勇.MATLAB 信号处理详解[M].北京:人民邮电出版社,2001.

- [19] 陈桂明,张月照.应用 MATLAB 语言处理数字信号与数字图像[M].北京:科学出版社,2000.

- [20] Xilinx.Kintex-7 datasheet[DB/OL].<http://china.Xilinx.com/products/silicon-devices/fpga-ultrascale.html>.

(收稿日期:2021-03-07)

## 作者简介:

徐波(1982-),男,硕士研究生,工程师,主要研究方向:数字微系统集成技术、ASIC 设计。

扫码下载电子文档

- [12] 刘盼.基于 CMOS 的 VGA 接口的工业相机的设计[D].保定:河北大学,2014:37-38.

(收稿日期:2021-03-09)

## 作者简介:

籍明慧(1997-),男,硕士研究生,主要研究方向:主板设计。

裴焕斗(1973-),男,博士,副教授,主要研究方向:测试计量技术及仪器。

宫健(1997-),男,硕士研究生,主要研究方向:嵌入式系统。

扫码下载电子文档

## 版权声明

经作者授权，本论文版权和信息网络传播权归属于《电子技术应用》杂志，凡未经本刊书面同意任何机构、组织和个人不得擅自复印、汇编、翻译和进行信息网络传播。未经本刊书面同意，禁止一切互联网论文资源平台非法上传、收录本论文。

截至目前，本论文已经授权被中国期刊全文数据库（CNKI）、万方数据知识服务平台、中文科技期刊数据库（维普网）、DOAJ、美国《乌利希期刊指南》、JST 日本科技技术振兴机构数据库等数据库全文收录。

对于违反上述禁止行为并违法使用本论文的机构、组织和个人，本刊将采取一切必要法律行动来维护正当权益。

特此声明！

《电子技术应用》编辑部

中国电子信息产业集团有限公司第六研究所