# 一种实时频谱仪中帧检波器的 FPGA 实现

郭 静, 何 鹏

(中国电子科技集团公司第四十一研究所, 山东 青岛 266555)

**摘要:** 针对实时频谱仪中无缝频谱数据量巨大导致难以进行传输和显示的问题, 基于 FPGA 的 FIFO 资源设计了一种适用于实时频谱仪的帧检波器, 在保留信号特征的条件下将多帧频谱数据合并为一帧进行传输与刷新。仿真与实际测试结果表明该检波器具有正峰值、负峰值、平均值和实时刷新四种检波方式, 能够在检波的同时实现对分析带宽外频谱数据的截断。相比于传统基于 RAM 实现的帧检波器, 该检波器不需要控制 RAM 读写地址, 易于实现, 占用逻辑资源较少, 已在实时频谱仪中得到应用。

**关键词:** 实时频谱分析仪; 检波器; 帧检波; FPGA

中图分类号: TN47

文献标识码: A

DOI: 10.16157/j.issn.0258-7998.212124

中文引用格式: 郭静, 何鹏. 一种实时频谱仪中帧检波器的 FPGA 实现[J]. 电子技术应用, 2021, 47(12): 35–38.

英文引用格式: Guo Jing, He Peng. A realization of frame detector in real-time spectrum analyzer based on FPGA[J]. Application of Electronic Technique, 2021, 47(12): 35–38.

## A realization of frame detector in real-time spectrum analyzer based on FPGA

Guo Jing, He Peng

(The 41st Institute of CETC, Qingdao 266555, China)

**Abstract:** For coping with transmission and display problem caused by the huge amount of seamless spectrum data in real-time spectrum analyzer, this article designed a FIFO-based frame detector of real-time spectrum analyzer in FPGA. It combines multiple frames of spectrum data into one frame for transmission and refresh while retaining signal characteristics. By simulation and actual testing, results show that the detector has four types of detection: peak value, negative value, mean value and real-time sample value. It also can cut off the spectrum data outside the analysis bandwidth while detecting. Compared with the traditional RAM-based frame detector, the detector does not need to control RAM read and write addresses, is easy to implement, occupies less logic resources, and has been applied in real-time spectrum analyzers.

**Key words:** real-time spectrum analyzer; detector; frame detect; FPGA

## 0 引言

随着无线电技术的快速发展, 信号越来越呈现出复杂性、瞬变性、传输快、高带宽等特点, 对射频信号的测试和检测要求越来越高, 信号测量分析技术的发展也面临着很大的挑战和机遇<sup>[1-3]</sup>。传统的频谱仪由于不能进行实时数据处理, 容易导致突发瞬变信号的遗漏, 已经无法满足复杂信号对频谱分析和测试的需求。为满足复杂电磁环境下的信号测试工作需要, 实时频谱分析仪应运而生并得到了快速发展<sup>[4-5]</sup>。

实时频谱分析仪具有无缝数据处理能力<sup>[6-7]</sup>, 实时处理 FFT 模块完成时域数据到频域数据的转换, 得到每秒数十万甚至上百万数量级的频谱帧, 如此庞大的数据量不仅难以进行数据传输, 而且更无法实时显示<sup>[8]</sup>, 因此需要实时检波技术来解决传输和刷新的瓶颈。传统实时频谱仪中的帧检波器通常采用 RAM 资源进行实现<sup>[9-10]</sup>, 在检波过程中需要对 RAM 进行读、写地址的控制, 控制

方法较为繁琐且占用逻辑资源。本文提出了一种基于 FPGA FIFO 资源实现的实时检波器, 不需要控制读写地址, 只需控制新来的频谱数据与 FIFO 中存储的数据一一比较或累加后重新写入 FIFO, 实现方式简单且占用逻辑资源较少。

实时频谱仪具有可变分析带宽功能, 可变分析带宽滤波器通带外的频谱数据不需要进行显示, 在检波运算前剔除分析带宽外的数据, 可以减小后续信号处理和数据传输的压力, 因此本文在检波运算前增加了是否为分析带宽内显示点的判断。

## 1 实时检波器原理

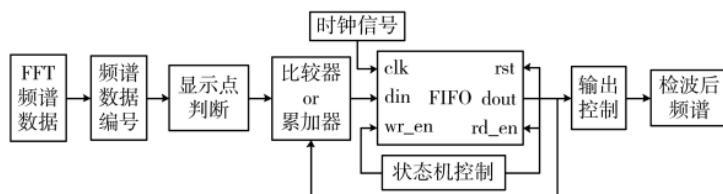

实时频谱仪数据处理组成框图如图 1 所示。中频输

图 1 实时频谱仪数据处理框图

入信号通过 ADC 采样,采样后的数据经过下变频与可变分析带宽数字滤波后无缝进行实时 FFT 频谱计算<sup>[11-12]</sup>,实时检波器将多帧 FFT 频谱数据根据不同检波方式保留不同信号特征,压缩成 1 帧频谱数据传输至上位机进行刷新显示。本系统中 ADC 采样率为 204.8 MHz,最大分析带宽下变频滤波经过 2 倍抽取形成 102.4 MHz 速率的 IQ 数据,若进行 1 024 点数的 FFT 运算,每秒可形成 10 万帧频谱数据。为了适应人眼可识别的数据刷新频率,需要进行实时帧检波处理,即每 4 000 帧频谱检波输出 1 帧频谱,形成每秒 25 帧的刷新频率<sup>[13]</sup>。

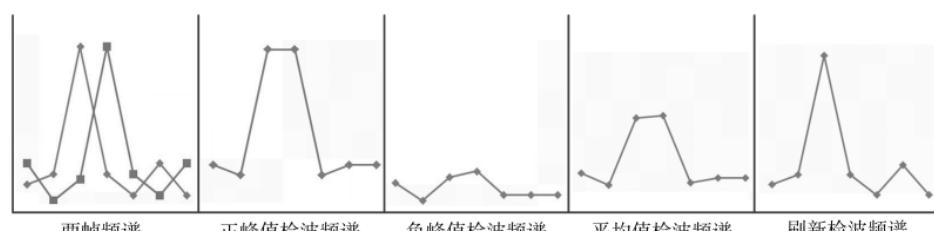

实时频谱分析仪参考传统频谱仪中的视频检波算法,同时考虑到数据处理的实时性,引入了正峰值、负峰值、平均值和实时刷新四种检波方式<sup>[14-15]</sup>。图 2 为对两帧频谱经过不同检波方式输出的频谱图,正峰值检波画出了所有频点的最大值包络,负峰值检波选取每个频点最小值的信号进行显示,平均值检波对每个频点的值求平均值,实时刷新检波则仅选择输出一帧频谱数据。不同的检波方式有利于观察不同特征的信号,正峰值检波有利于保留突发信号的信息,负峰值检波有利于消除突发信号的影响,平均值检波有利于提高小信号的测量能力,实时刷新检波有利于观察检波前原始信号的频谱。

## 2 实时检波器设计与实现

### 2.1 分析带宽内显示点计算

实时频谱仪具有可变分析带宽功能,显示的频谱数据为分析带宽内的数据,因此原始的频谱数据需要根据用户设定的频点间步长、分析带宽和 FFT 点数来进行截断,剔除分析带宽外的数据。显示点数计算公式如式(1)所示:

$$\text{ShowNum} = \frac{\text{BW}}{\text{Step}} + 1 \quad (1)$$

式中,ShowNum 为显示点数;BW 为分析带宽,Hz;Step 为频点间步长,Hz。

以 60 MHz 分析带宽、100K 步长为例,该参数设置下上位机软件自动关联的 FFT 点数为 1 024 点,通过式(1)计算出显示点数为 601 点,需要选取 1 024 点频谱数据中间的 601 点数据进行后续的处理与显示,前后两端共 423 个点应该被剔除。在本文中对输入的每一帧频谱数据进行点数计数编号,通过该点对应计数器的值即可判断该点是否位于显示点的位置,从而在该频谱帧到达检

波器时判断每一个频点为显示点还是截断点,若为显示点则参与检波运算,若为截断点则舍去跳转到下一流程。

### 2.2 实时检波器的实现

本文使用 Xilinx Kintex UltraScale 系列的 FPGA 进行数字中频信号处理,通过 FIFO 对检波过程数据进行暂存,设置 FIFO 读数模式为 First Word Fall Through,以便在新频谱数据到来时及时与 FIFO 的输出数据做比较,宽度为平均值检波模式下所需累加器产生最大数据的宽度,深度为可容纳最大显示点的数据量。

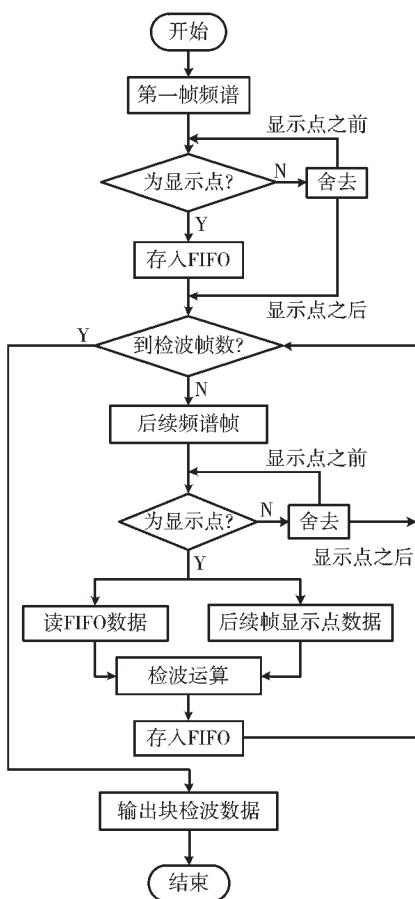

图 3 所示为基于 FIFO 结构实现的检波器逻辑控制框图,上位机软件设置检波帧数、检波类型和显示点数后,经过 FFT 变换后的频谱数据输入至实时帧检波器进行检波,不同时间内无缝捕获的许多相邻帧组成块<sup>[6]</sup>,具体块内检波实现流程如图 4 所示。

图 3 基于 FIFO 结构实现的检波器逻辑控制

(1)频谱数据编号:对每一帧到来的频谱数据进行编号,对于长度为 NFFT 的频谱数据,编号应为 1~NFFT。

(2)存储数据:第一帧频谱数据的显示点暂存至 FIFO 中。

(3)读取数据并回写数据:后续帧频谱数据的显示点到达的同时读取 FIFO 数据,新的频谱数据依次与 FIFO 输出的频谱数据进行比较或累加,根据不同的检波方式将得到的数据写入至 FIFO(正峰值检波使用比较器写入较大的值,负峰值检波使用比较器写入较小的值,平均值检波使用累加器写入累加值,实时刷新检波直接写入输入的频谱数据),等待下一帧频谱数据的显示点到来时再进行比较或累加。

(4)输出数据:处理的频谱数据帧数达到软件设置的检波帧数后输出检波频谱数据,其中均值检波需要将 FIFO 输出的累加值除以检波帧数进行平均运算,其他检波方式则直接输出 FIFO 的存储数据。

(5)重置参数:清零检波帧数计数器,准备进行下一个块的检波。

图 2 不同检波方式输出的频谱图

图 4 块内检波流程图

由于本系统中 FPGA 的处理时钟为 204.8 MHz, FFT 频谱数据速率为 102.4 MHz, 在输出检波数据帧的过程中不会被新的频谱数据所覆盖, 因此只需要单路检波器即可满足要求。若存在输入频谱数据覆盖输出频谱数据的风险, 可将该结构扩展为采用两个相同的 FIFO 进行乒乓操作。

### 3 实验测试

#### 3.1 仿真测试

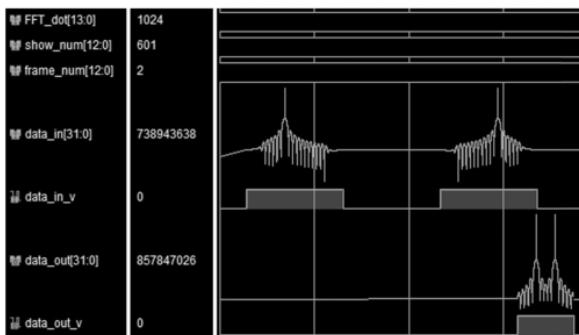

使用 Vivado 自带仿真器对实时检波器程序进行仿真, 以正峰值检波为例。设置 FFT 点数为 1 024 点, 显示点数为 601 点, 块检波帧数为 2 帧, 检波模式选择正峰值检波。图 5 为检波器仿真波形图, data\_in 为输入 1 024

图 5 检波器仿真输出正峰值检波频谱

点数的频谱, 第一帧信号频率为 143.6 MHz, 第二帧信号频率为 163.6 MHz, data\_out 为经过检波输出后的 601 个点的显示频谱, 可以看出输出频谱同时保留了 143.6 MHz 和 163.6 MHz 两个信号, 实现了正峰值检波与分析带宽外数据的截断。

#### 3.2 实际测试

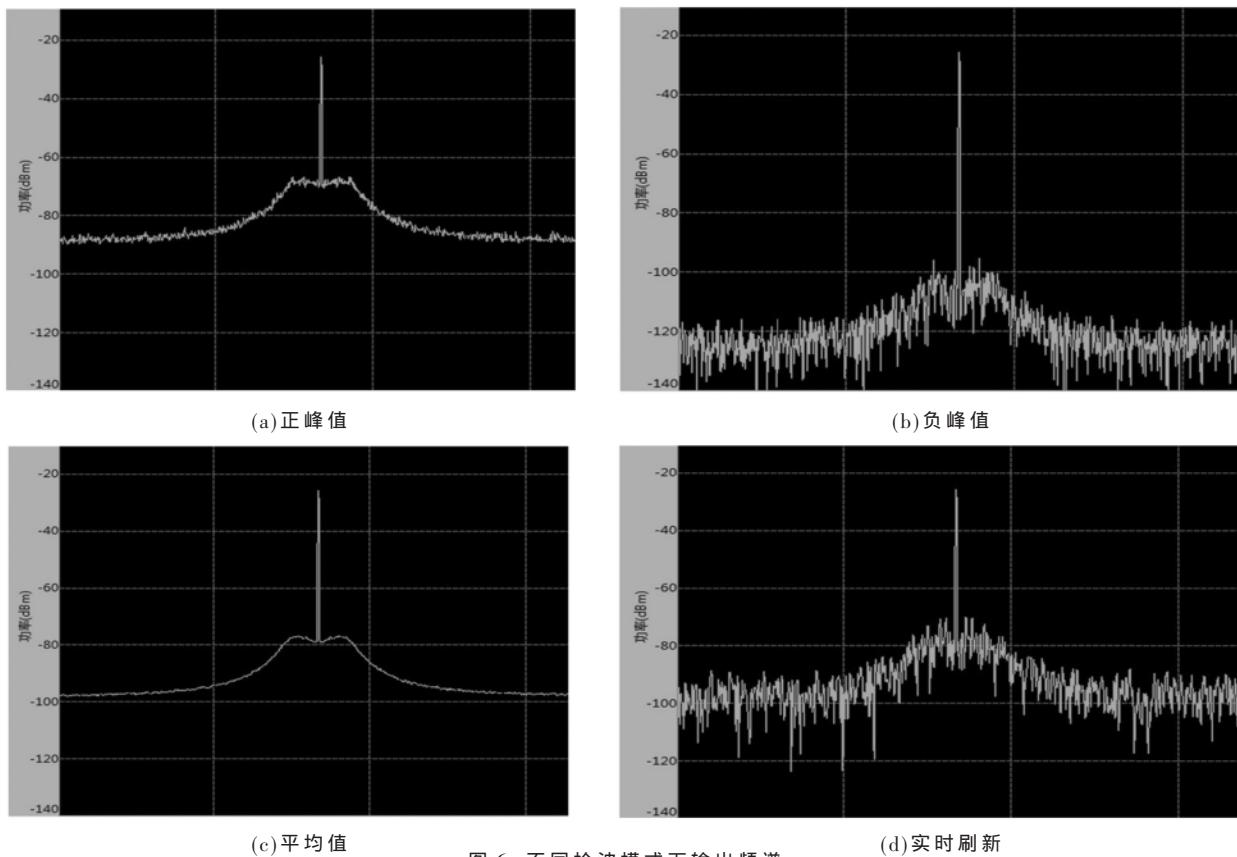

连接信号源输出端和实时频谱仪输入端, 设置信号源输出频率为 6 GHz, 实时频谱仪分析带宽为 60 MHz, 步长为 25 kHz, 块检波帧数为 4 000 帧, 分别设置实时频谱仪的检波方式为正峰值、负峰值、平均值和实时刷新, 得到不同检波模式的输出频谱图如图 6 所示。由实验测试结果可以得出, 该实时检波器可以满足实时频谱仪的检波需求。

### 4 结论

本文利用 FPGA 的 FIFO 资源设计了一种可应用于实时频谱仪的帧检波器, 实验证明该检波器可实现正峰值、负峰值、平均值和实时刷新四种检波功能, 能够根据需要灵活设置检波帧数与检波模式, 满足实时频谱仪的检波需求。在参与检波运算前对分析带宽外数据进行剔除, 减轻了后续数据的处理压力。基于 FIFO 资源实现的检波器结构简单, 占用逻辑资源较少, 可在实时频谱仪中广泛推广使用。

#### 参考文献

- [1] 陈曾平, 吴巨红, 宿绍莹, 等. 宽带实时频谱分析技术及其应用[J]. 信号处理, 2012(2): 151–157.

- [2] 张亚军. 实时频谱仪的数字中频处理设计与实现[D]. 成都: 电子科技大学, 2017.

- [3] 陈弘扬, 王心尘. 浅谈基于实时频谱仪的信号识别[J]. 中国无线电, 2020(7): 41–43.

- [4] IGLESIAS V, GRAJAL J, SANCHEZ M A, et al. Implementation of a real-time spectrum analyzer on FPGA platforms[J]. IEEE Transactions on Instrumentation and Measurement, 2015, 64(2): 338–355.

- [5] 泰克公司. 实时频谱分析基础知识[Z]. 2019.

- [6] 钱永. 实时频谱仪原理及应用案例集汇编[M]. 泰克科技中国有限公司, 2007: 102–104.

- [7] 郭仕剑, 李波, 胡昆明. 实时频谱分析技术在雷达信号侦查中的应用[J]. 信号处理, 2011, 27(8): 1229–1234.

- [8] 胡健. 基于软件无线电的实时频谱分析技术的研究与实现[D]. 上海: 复旦大学, 2011.

- [9] 李鹏飞. 一种并行架构的数字信号频域处理电路设计[D]. 成都: 电子科技大学, 2019.

- [10] 刘聪. 基于信道化的并行数字频谱处理模块设计[D]. 成都: 电子科技大学, 2020.

- [11] 陈昱, 刘平. 频谱分析仪检波方式的分析与研究[J]. 现代电子技术, 2010, 33(1): 97–99, 102.

- [12] 陈仁北, 陈爽. 数字视频检波器设计[J]. 国外电子测量技术, 2006, 25(1): 45–47.

图 6 不同检波模式下输出频谱

[13] 李根.宽带实时谱仪重叠帧及频谱三维压缩技术研究与实现[D].成都:电子科技大学,2017.

[14] 张亚洲,张超,王保锐.实时频谱分析仪中并行 FFT 算法的 FPGA 设计[J].单片机与嵌入式系统应用,2016(5):23-26.

[15] 梁琦.实时频谱仪中关键算法的研究与 FPGA 实现[D].重庆:重庆邮电大学,2017.

(收稿日期:2021-09-04)

## 作者简介:

郭静(1990-),女,硕士,工程师,主要研究方向:数字信号处理与 FPGA 工程实现。

何鹏(1981-),男,硕士,高级工程师,主要研究方向:宽带数字信号处理技术。

扫码下载电子文档

(上接第 34 页)

[8] 郭希铮,袁佳琦,游小杰,等.电力电子实时仿真建模的 FPGA 资源优化方法研究[J].检测技术与数据处理,2020,24(7):12-19.

[9] 王毅,邓子乔,马郭亮,等.基于 FPGA 的多节点电力线信道仿真器的设计与实现[J].电力系统保护与控制,2018,46(17):145-151.

[10] 于飞,朱炯.数字 IGBT 驱动保护电路设计[J].电测与仪表,2014,51(10):116-119.

[11] 李姝萱,卜刚.基于 FPGA 的 PIE 编码与 UVM 验证平台的设计[J].电子技术应用,2021,47(6):110-114.

[12] 李锦明,刘梦欣,成乃朋.RS 编码算法的优化与 FPGA 实现[J].电子技术应用,2020,46(2):76-79,83.

[13] 杜蜀薇,赵兵,孔令达,等.基于 FPGA 仿真模拟技术的

智能电能表软件可靠性测试系统设计[J].电测与仪表,2017,54(22):83-87,122.

[14] 黄建尧,刘升华,李琨.适于底层协议栈开发的数据采集与仿真系统[J].电子技术应用,2010,36(2):129-132.

[15] 王虹现,全英汇,邢孟道,等.基于 FPGA 的 SAR 回波仿真快速实现方法[J].系统工程与电子技术,2010,32(11):2284-2289.

(收稿日期:2021-08-13)

## 作者简介:

朱炯(1989-),男,硕士,工程师,主要研究方向:控制理论与控制工程。

李康(1969-),男,博士,主任医师,主要研究方向:神经及心血管影像学。

徐亦飞(1986-),男,博士,主要研究方向:自动曝光控制算法。

扫码下载电子文档

## 版权声明

经作者授权，本论文版权和信息网络传播权归属于《电子技术应用》杂志，凡未经本刊书面同意任何机构、组织和个人不得擅自复印、汇编、翻译和进行信息网络传播。未经本刊书面同意，禁止一切互联网论文资源平台非法上传、收录本论文。

截至目前，本论文已经授权被中国期刊全文数据库（CNKI）、万方数据知识服务平台、中文科技期刊数据库（维普网）、DOAJ、美国《乌利希期刊指南》、JST 日本科技技术振兴机构数据库等数据库全文收录。

对于违反上述禁止行为并违法使用本论文的机构、组织和个人，本刊将采取一切必要法律行动来维护正当权益。

特此声明！

《电子技术应用》编辑部

中国电子信息产业集团有限公司第六研究所