# 基于 0.35 μm CMOS 工艺的高温高压 LDO 芯片设计 \*

吴 霞 , 鲍言锋 , 邓婉玲 , 黄君凯

(暨南大学 信息科学技术学院 电子工程系, 广东 广州 510632)

**摘要:** 基于 X-FAB xa 0.35 μm CMOS 工艺,首先采用 Cascode 电流镜和高压管,设计了一种具有高电源抑制比且无需额外提供偏置模块的高温高压基准电路,在输入电压为 5.5 V~30 V、工作温度为 -55 ℃~175 ℃时,可获得稳定的 0.9 V 基准电压。接着针对负反馈环路的稳定性问题,根据动态零点补偿原理设计了一种新的动态零点补偿电路,使系统在全负载变化范围内保持稳定。同时配合其他过温保护、过压保护、过流保护和逻辑控制等电路模块,完成一款面积为 2.822 3 mm<sup>2</sup> 的高温高压低压差线性稳压器(LDO)芯片的设计。

**关键词:** LDO ; CMOS ; 高温高压 ; 0.35 μm 工艺

中图分类号: TN402

文献标识码: A

DOI: 10.16157/j.issn.0258-7998.201109

中文引用格式: 吴霞, 鲍言锋, 邓婉玲, 等. 基于 0.35 μm CMOS 工艺的高温高压 LDO 芯片设计[J]. 电子技术应用, 2021, 47(12): 120–125.

英文引用格式: Wu Xia, Bao Yanfeng, Deng Wanling, et al. Design of high temperature and high voltage LDO using 0.35 μm CMOS process[J]. Application of Electronic Technique, 2021, 47(12): 120–125.

## Design of high temperature and high voltage LDO using 0.35 μm CMOS process

Wu Xia , Bao Yanfeng , Deng Wanling , Huang Junkai

(College of Information Science and Technology, Jinan University, Guangzhou 510632, China)

**Abstract:** In this paper, based on X-FAB xa 0.35 μm CMOS process, a cascode current mirror and high voltage MOS transistors are used to design a high temperature and high voltage reference circuit with high power supply rejection ratio without additional bias circuit module, and thus, a stable 0.9 V reference voltage can be obtained when the input voltage is in the range of 5.5 V~30 V and the operating temperature is in the range of -55 ℃~175 ℃. Then, according to the principle of dynamic zero compensation, a new dynamic zero compensation circuit is designed to make the system to maintain stability in the full load voltage range. At the same time, with the design of other circuit modules such as over-temperature protection, over-voltage protection, over-current protection and logic control circuit modules, a low-dropout linear regulator(LDO) chip with high temperature and high voltage is finally designed, the area of which is 2.822 3 mm<sup>2</sup>.

**Key words:** LDO ; CMOS ; high temperature and voltage ; 0.35 μm process

## 0 引言

随着嵌入式电子产品在日常生活的广泛应用,对电源的充电速度、续航能力及转换效率等技术指标的要求越来越高,因此对电源管理芯片提出了更高的要求。不但需要电源芯片具有精度高、功耗低和体积小等特点,在一些应用场景中,还要求芯片能在高温高压的恶劣环境中稳定地工作<sup>[1]</sup>。例如,混合动力汽车的引擎装置和控制系统通常工作于高达 150 ℃以上的高温环境,石油和天然气油井的井底传感系统和监测设施的工作温度也超过 150 ℃,探月工程电子设备需要在 -153 ℃~127 ℃的大温差环境下工作。但目前普通的电源管理芯片的最大工作温度通常在 150 ℃以下,因此不能直接应用在这

种高温和大温差的环境中。

LDO 作为电源管理芯片中占据市场较大份额的产品,由于具有体积小、功耗低和输出纹波小等优点,已广泛应用于片上集成系统<sup>[2~7]</sup>。但是,目前市场上 LDO 芯片的输入电压范围通常在 2 V~5 V,当输入高于 5 V 时,典型应用中的大多数 LDO 芯片将会被烧毁<sup>[8]</sup>,从而限制了 LDO 在高温高压环境下的应用,因此设计一款面积小、输入电压范围大且能在高温环境中长期稳定工作的 LDO 芯片便显得十分必要<sup>[9~12]</sup>。

本文针对这一需要,基于 X-FAB xa 0.35 μm CMOS 工艺,设计了一款高温高压 LDO 芯片,该芯片可以实现在输入电压为 5.5 V~30 V,工作温度为 -55 ℃~175 ℃的情况下,输出电压为 5 V 且输出误差小于 ±5% 的设计目标,可应用于航空航天和混合动力汽车等苛刻环境。

\* 基金项目: 广东省自然科学基金(2020A1515010567)

## 1 LDO 的基本工作原理

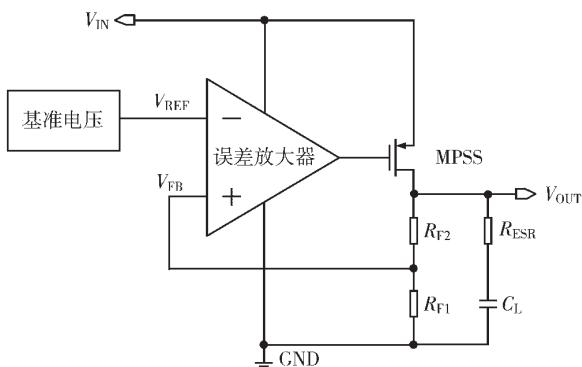

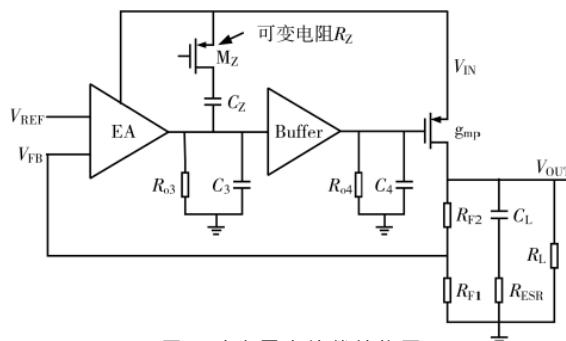

典型 LDO 的电路结构<sup>[13]</sup>如图 1 所示,包含基准电路<sup>[14]</sup>、误差放大器、P 型功率管 MPSS<sup>[15-17]</sup>、电阻  $R_{F2}$  和  $R_{F1}$  组成的反馈网络、大电容  $C_L$  和等效串联电阻  $R_{ESR}$ 。当电源输入电压  $V_{IN}$  上电时,启动电路使基准电路摆脱简并点开始工作;稳定后的基准模块为后续的电路提供基准电流和基准电压,同时关闭了启动电路,产生的基准电压  $V_{REF}$  作用于误差放大器负端。开始时,由于整个反馈网络还没有建立,输出电压  $V_{OUT}$  为低电平,基准电压  $V_{REF}$  和反馈电压  $V_{FB}$  的差值增加,信号经过误差放大器使其输出减小,导致功率管的驱动电压增加,流过电阻  $R_{F1}$  和  $R_{F2}$  的电流增加,输出电压也增大;最终,建立的负反馈系统使基准电压  $V_{REF}$  和反馈电压  $V_{FB}$  相等,输出电压保持不变。

图 1 典型 LDO 的电路框图

## 2 LDO 芯片系统结构

本文设计的高温高压 LDO 芯片的系统框图如图 2 所示,该系统主要由基准电路模块、过温保护模块、过流保护模块、过压保护模块、逻辑控制模块和误差放大器

图 2 LDO 的系统框图

模块组成。其中,基准电路模块采用高压管和增大负反馈环路,在高温高压情况下为误差放大器模块的反相输入端提供一个稳定的基准电压  $V_{REF}$ ,同时也为其他模块提供稳定的偏置电压和偏置电流;误差放大器模块主要用于反馈信号  $V_{FB}$  和基准电压  $V_{REF}$  的比较,通过控制功率管栅极保证输出电压的稳定,同时采用动态零点补偿方法,以提高系统在负载变化时的稳定性。考虑到系统输入电压变化范围较大,输出高压功率管两端的压差导致芯片内部发热严重,长时间工作时将加速芯片老化甚至烧坏芯片,因此需要采用过温、过压、过流等保护模块以及逻辑控制模块来控制系统的工作状态,实现对芯片的有效保护。

## 3 LDO 芯片核心电路模块设计与验证

下面基于 X-FAB xa 0.35  $\mu\text{m}$  CMOS 工艺,给出所研制的高温高压 LDO 芯片中基准电路和误差放大器两个核心模块的具体设计。

### 3.1 高温高压基准电路设计及其验证

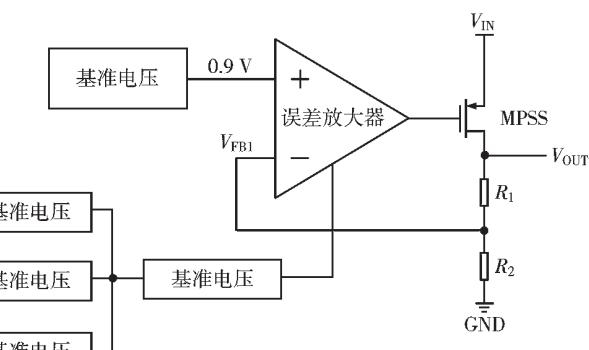

本文设计的高温高压基准电路的结构如图 3 所示,其中电阻  $R_1$  与晶体管 MN15、MN16 经分压,为晶体管 MN17 的栅极提供偏置电压,使 MN17 工作在饱和区;电

图 3 高温高压基准电路的结构图

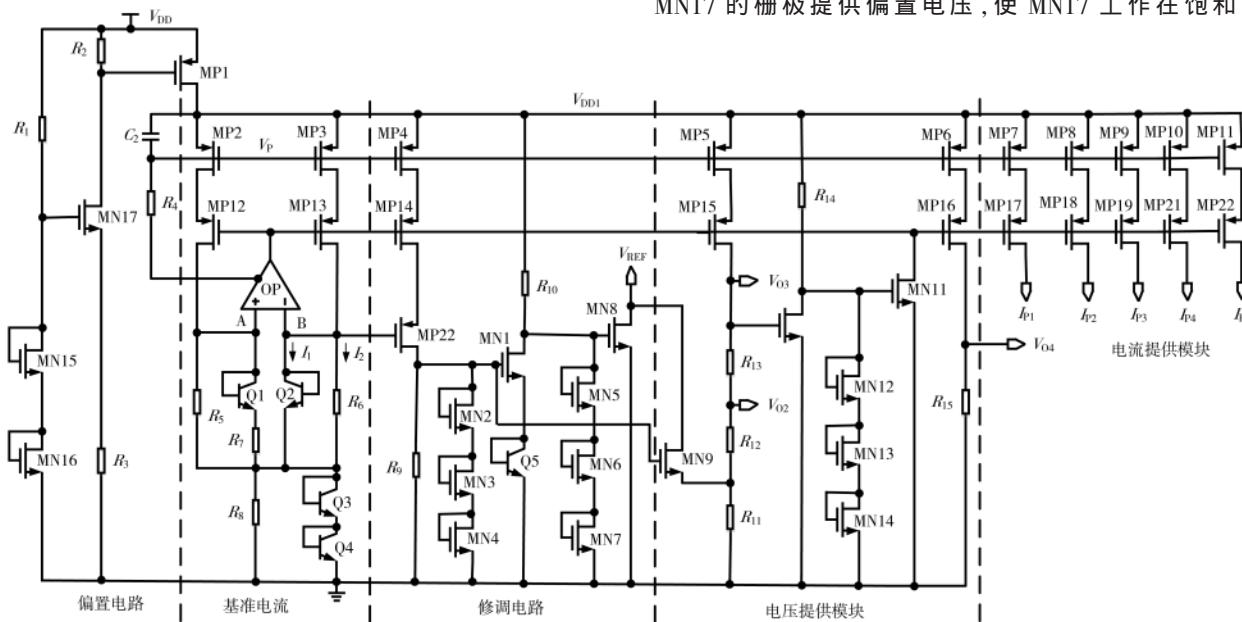

阻  $R_2$  与晶体管 MN17、电阻  $R_3$  经分压，为高压管 MP1 提供偏置电压。通过合理设计电阻  $R_1$ 、 $R_2$ 、 $R_3$  的阻值和晶体管 MN15、MN16、MN17 的尺寸，使高压管 MP1 在整个输入电压范围内一直处于线性区，确保了后续各个模块在整个输入电压范围内正常工作。晶体管 MP2、MP3、MP12、MP13，运算放大器 OP、Q1、Q2 以及电阻  $R_5$ 、 $R_6$ 、 $R_7$  构成了基准电流源电路，基准电流  $I_3$  由正温度系数的电流  $I_1$  与负温度系数的电流  $I_2$  相加得到。通过合理设置晶体管 Q1 和 Q2 发射极的面积之比  $N$ 、电阻  $R_6$  和  $R_7$  的值，可以得到一个与温度无关的基准电流  $I_3$ ，并通过晶体管 MP2、MP3 镜像给晶体管 MP7–MP11，为其他模块提供偏置电流。基准电流  $I_3$  通过 MP5、MP6 镜像到输出端，为后续模块提供偏置电压  $V_{02}$ 、 $V_{03}$  和  $V_{04}$ ，同时由于电阻  $R_{11}$  的温度系数很小，工作在线性区的晶体管 MN9 的源–漏压降也很小，因此电阻  $R_{11}$  两端的电压即是与温度无关的基准电压。

需要指出，第一，考虑到电源电压在实际高压应用中，由于晶体管之间的不匹配将导致偏置电流产生偏差，因此本文采用 Cascode 电流镜和高压管 MP12–MP21 的设计，用于解决偏置电流的稳定性问题。第二，注意到在基准电路包含有运放的情况下，不同模块可以通过基准连线产生“串扰”，导致运放放大器无法保持  $V_p$  恒定，从而使 MP7–MP11 的偏置电流出现较大的瞬态变化，因此本文通过加入大电容  $C_1$  旁路到地来抑制外界的干扰，并添加电阻  $R_4$  来进一步提高运放的稳定性。

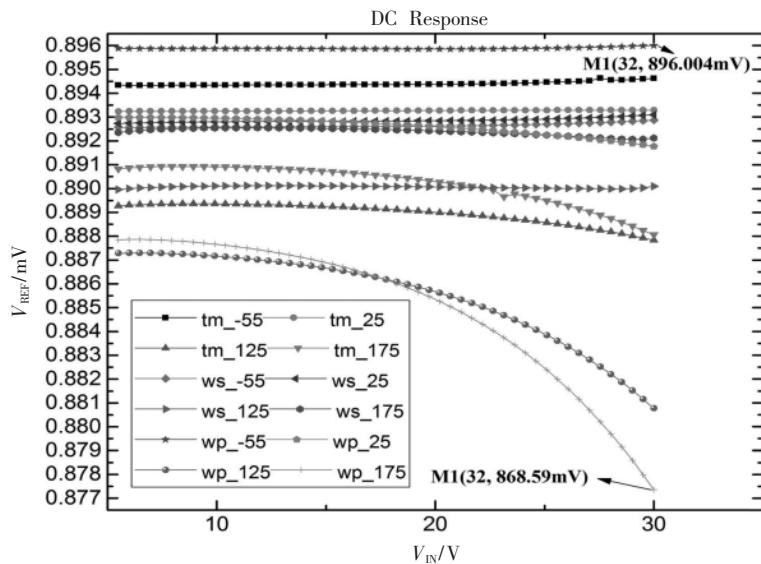

图 4 给出了在 tm、wp、ws 三种工艺角，温度在  $-55^{\circ}\text{C}$ 、 $25^{\circ}\text{C}$ 、 $125^{\circ}\text{C}$ 、 $175^{\circ}\text{C}$ ，共 12 种组合情况下图 3 基准电路的线性调整率。可以看到，输入电压从 5.5 V~30 V 变化时，基准电压的输出保持稳定，因此可满足本设计需要的高温高压以及宽输入电压的要求。此外，在最差工艺角的情况下，基准电压只偏离理论值 31.5 mV，满足了

图 4 基准电路的线性调整率

对高电源抑制比的设计需要。

### 3.2 误差放大器设计及其验证

由于误差放大器的增益、单位增益带宽和闭环稳定性等主要性能指标对整个 LDO 芯片的质量产生重要影响<sup>[2-3]</sup>，针对高温时误差放大器的增益和带宽下降将严重影响 LDO 芯片稳定性的问题，本文在缓冲级隔离补偿的基础上，基于动态零点补偿原理<sup>[18]</sup>，设计了一种新的动态零点补偿电路结构，如图 5 所示。通过在误差放大器输出端口加入补偿电容  $C_Z$  和工作在线性区的晶体管  $M_Z$ ，当输出电流变化时，晶体管的阻值也随之改变来补偿输出极点的变化，从而确保在整个负载变化范围内系统保持稳定。

图 5 动态零点补偿结构图

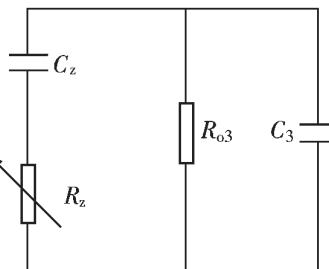

本文设计的带有用于提高系统带宽的缓冲级电路的误差放大器，采用了可提高运放增益的 PMOS 折叠共源共栅结构，其等效输出阻抗电路如图 6 所示，这里  $R_Z$  是工作在线性区晶体管的等效电阻， $R_{o3}$  和  $C_3$  分别是运放的输出电阻和输出电容，因此，等效的交流输出阻抗  $Z$  可表示为：

$$Z(s) = \frac{1+sR_zC_z}{1+s(R_zC_z+R_{o3}C_z+R_{o3}C_3)+s^2R_zC_zR_{o3}C_3} \quad (1)$$

令上式分子分母等于零，可得到两个极点和一个零点，分别为：

$$P_3 \approx \frac{1}{R_zC_z+R_{o3}C_z+R_{o3}C_3} \quad (2)$$

$$P_4 \approx \frac{R_zC_z+R_{o3}C_z+R_{o3}C_3}{R_zC_zR_{o3}C_3} \quad (3)$$

$$Z_c \approx \frac{1}{2\pi R_zC_z} \quad (4)$$

通过动态零点补偿后，误差放大器的输出端

图 6 误差放大器输出端的等效电路图

变为两个极点  $P_3, P_4$  和零点  $Z_c$ , 通过优化寄生参数以及合理设计  $R_z$  和  $C_z$ , 使  $P_3$  成为系统的主极点, 极点  $P_4$  在增益带宽积之外, 动态零点  $Z_c$  补偿了输出端极点  $P_0$ ; 同时, 通过缓冲器降低了功率管栅极间电阻, 使该处极点也在增益带宽积之外。通过这样的补偿方式, 使电路的主极点基本不变, 从而保证了系统的稳定性。

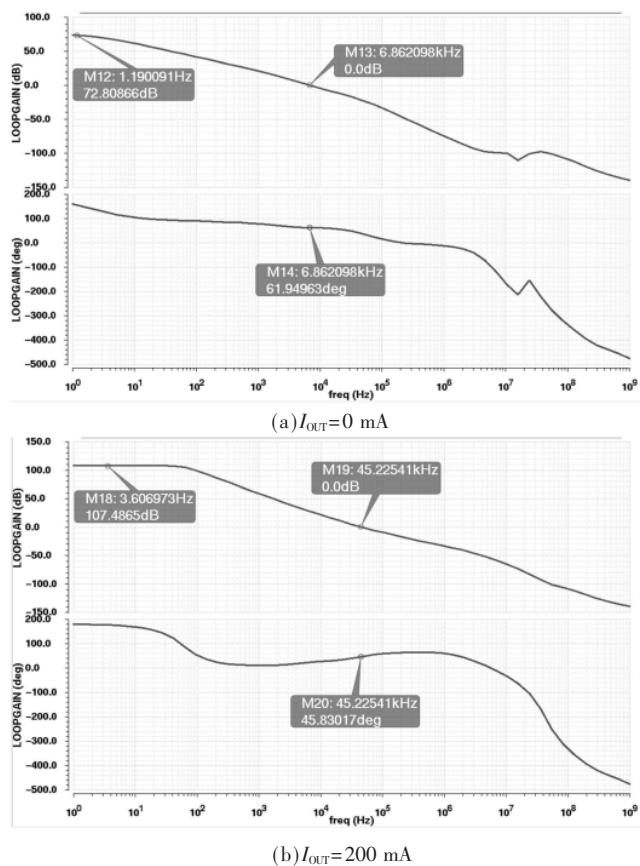

在电源电压 10 V, 温度 25 °C, 负载电容  $C_L$  为 4.7 μF, 串联电阻  $R_{ESR}$  为 0.1 Ω 的条件下, 图 7 分别给出了负载电流为 0 mA 和 200 mA 情况下, 环路增益和相位裕度的仿真结果, 可以看到系统的环路增益在全负载范围内最低在 72 dB 以上, 相位裕度最小为 45.83°; 在不同的负载条件下, 通过合理设计, 使动态零点跟随输出极点变化, 从而在单位增益带宽积内仅有一个极点, 其他零点和极点都在高频处。因此, 本文的设计可以保证动态零点补偿结果满足 LDO 要求。

图 7 负载电流分别为 0 mA 和 200 mA 的环路增益和相位裕度

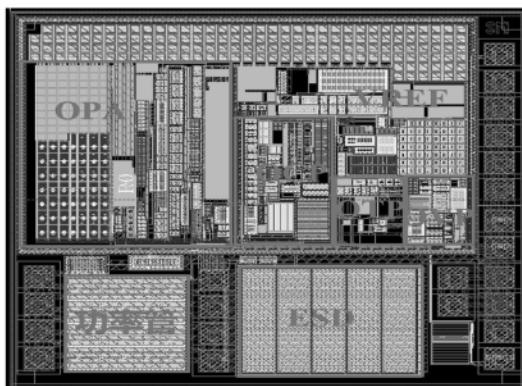

#### 4 LDO 芯片的整体布局及其版图设计

图 8 给出所设计的 LDO 芯片的整体布局及其版图, 其中已经嵌入为 LDO 芯片提供保护机制和增加使用寿命所设计的过温模块、过压模块、过流模块及逻辑控制模块。这里, 考虑到 LDO 芯片功率管的尺寸比较大, 在芯片中的发热也较严重, 基准电压易受到温度的影响, 因此在图 8 中将基准电路模块远离功率管布置, 保证了基准电路的偏置电压和偏置电流的稳定。同时, 本文还

图 8 LDO 芯片的版图

在芯片端口之间加入了 ESD 保护电路, 以避免人体放电对 LDO 芯片的影响; 这里, ESD 保护电路采用厂家提供的 IP 核。此外, 图 8 中也将过温保护模块、过流保护模块和过压保护模块靠近驱动管设计, 以避免驱动管发热影响到芯片正常工作。最后, 通过各个模块的布局布线, 采用 Cadence Virtusuo 软件工具, 并经过 DRC 和 LVS 规则检查, 完成了 LDO 芯片的版图设计和验证, 最终芯片的面积为 2.8223 mm<sup>2</sup>。

#### 5 LDO 芯片的整体性能仿真及其验证

前面已经对 LDO 的基准电路模块和误差放大器模块进行设计和仿真验证, 为了保证所设计的 LDO 芯片达到预期的指标和功能, 下面使用 Cadence spectre 软件工具对 LDO 芯片的整体性能进行仿真, 并对仿真结果进行分析和验证。

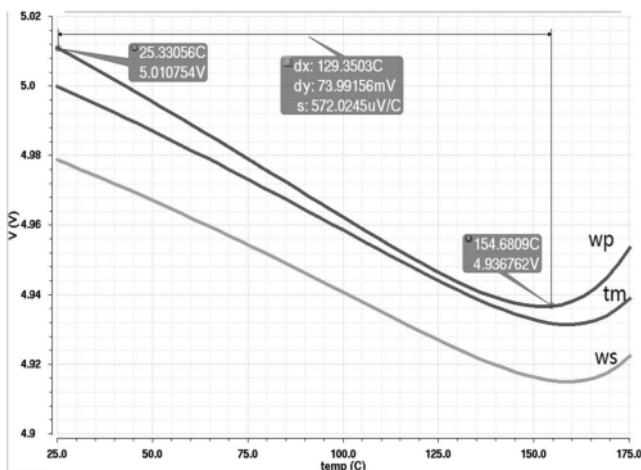

在输入电压  $V_{IN}=10 \text{ V}$ , 温度范围为 25 °C~175 °C 的空载情况下, 图 9 给出了 LDO 在不同工艺角下的输出电压温度漂移。从图中结果可以看到, 当温度从 25 °C~175 °C 变化时, 输出电压在 wp 工艺角下从 5.01 V 变化到 4.93 V, 因此输出电压的变化率为 1.6%, 输出电压的温度系数约为 108 ppm/°C, 可满足本文设计对输出电压精度的要求。

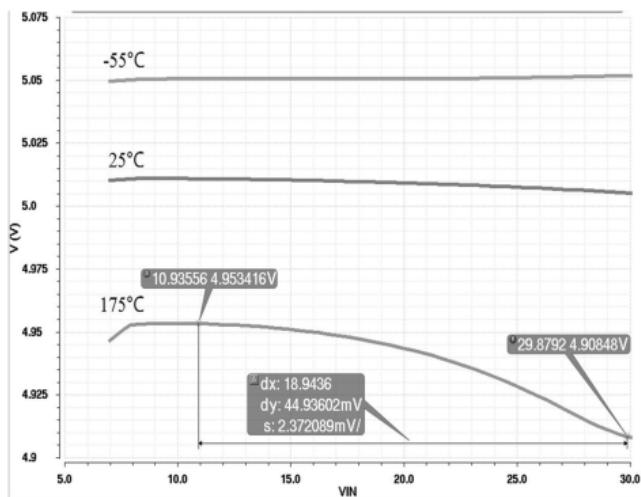

在空载条件下, 输入电压  $V_{IN}$  在 5.5 V~30 V 范围内,

图 9 不同工艺角下的输出电压温度漂移

温度为-55 °C、25 °C 和 175 °C 情况下,LDO 在 wp 工艺角下的线性调整率如图 10 所示。从图中结果可以得到,在温度为 175 °C 时,线性调整率为 1.95 mV/V。注意到高温情况下误差放大器的直流增益会发生改变,将导致 LDO 在不同工艺角具有不同的线性调整率。与上面类似的仿真结果表明,在 tm 工艺角下,温度为 175 °C 时的线性调整率为 0.64 mV/V;在 ws 工艺角下,温度为 175 °C 时的线性调整率为 2.18 mV/V。

图 10 wp 工艺角下的线性调整率

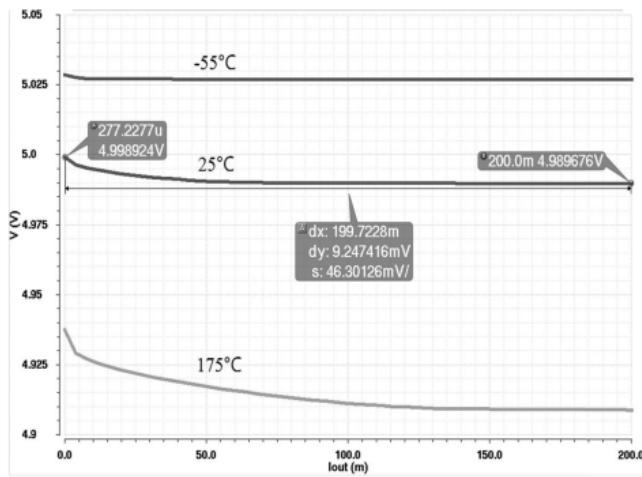

在输入电压  $V_{IN}=7.4$  V, 负载电流从 0 mA 变化到 200 mA 时, 温度为-55 °C、25 °C 和 175 °C 情况下, 在典型工艺角 tm 下 LDO 的负载调整率如图 11 所示。从图中结果可以得到, 在温度为 25 °C 时, 负载调整率为 46 μV/mA。相应

图 11 输入电压为 7.4 V 时的负载调整率

地, 在输入电压  $V_{IN}=30$  V, 温度在 175 °C 时, 由于晶体管的泄漏电流增大导致误差放大器的直流增益下降, 输出电压的变化也增大, 与上面类似的仿真结果表明, 这时的负载调整率为 164 μV/mA。

表 1 是本文设计的 LDO 芯片与其他同类 LDO 芯片的主要技术指标对比。可以看到, 本文设计的 LDO 芯片比文献[4]具有更高的输出电流, 比文献[5]、[6]具有更宽的输入电压范围, 并可在更高的电压下稳定工作。同时, 本文设计的 LDO 芯片, 其工作温度范围也具有明显的优势, 不仅工作温度范围比文献[4-6]的结果更宽, 并且可以在高达 175 °C 的温度下正常工作。因此, 本文设计的 LDO 芯片的主要技术指标可满足实际应用的要求。

## 6 结论

本文设计了一款基于 0.35 μm CMOS 工艺的高温高压 LDO 芯片, 其最小的线性调整率和负载调整率分别为 2.18 mV/V 和 46 μV/mA, 芯片面积为 2.822 3 mm<sup>2</sup>。使用 Cadence spectre 工具对所研制的 LDO 芯片进行仿真验证, 结果表明该 LDO 芯片能工作在-55 °C~175 °C 的环境中, 输入电压范围在 5.5 V~30 V, 其输出最大电流为 200 mA, 并可以稳定地输出 5 V 电压, 且输出电压误差不超过 5%。因此, 可适用于汽车、宇航空间和井下系统等恶劣环境中的嵌入式电子产品。

## 参考文献

- [1] 刘彦松.SOI 高温器件及其在汽车电子等领域中的应用[J].物理, 1999(7): 412~412.

- [2] SIMPSON C. A user's guide to compensating low-dropout regulators[C]//Wescon'97 Conference Proceedings.IEEE, 1997: 270~275.

- [3] SIMPSON C. Linear regulators : theory of operation and compensation[J]. Sensor Letters, 2012, 10(5): 1099~1103.

- [4] 冯肖雄. 应用于智能电池中的宽输入电压范围的 LDO 线性变换器设计[D]. 哈尔滨: 哈尔滨工业大学, 2011.

- [5] YIN J, HUANG S, DUAN Q, et al. An 800 mA load current LDO with wide input voltage range[C]//International Conference on Circuits.IEEE, 2017: 174~178.

- [6] 卢璐. 一种基于 0.35 μm BCD 工艺的低压差线性稳压器的研究与设计[D]. 成都: 电子科技大学, 2017.

- [7] 陈迪平, 应韬, 董刚. 一种适用于移动芯片的低功耗低温漂 LDO 电路[J]. 西安电子科技大学学报(自然科学版), 2018, 45(6): 57~62.

- [8] DU H, LAI X, CHI Y. A high voltage LDO with dynamic compensation network [J]. Analog Integrated Circuits and

表 1 LDO 芯片的系统指标及其对比

| 参数    | 工艺           | 输入电压范围/V | 输出电压/V | 输出电流/mA | 工作温度/°C | 线性调整率/(mV/V) | 负载调整率/(μV/mA) |

|-------|--------------|----------|--------|---------|---------|--------------|---------------|

| 本文指标  | 0.35 μm CMOS | 5.5~30   | 5      | 200     | -55~175 | 0.65         | 46            |

| 文献[4] | 0.5 μm CMOS  | 4.5~28   | 1.8    | 20      | -40~85  | 0.0085       | 2.6           |

| 文献[5] | 0.25 μm CMOS | 3.9~20   | 2.5    | 800     | <160    | 0.509        | 45.8          |

| 文献[6] | 0.35 μm CMOS | 5.2~16   | 5      | 400     | -55~125 | 1.1          | 29            |

- Signal Processing , 2014 , 80(2) : 233–241.

- [9] WANG Y,ZHU Z,YAO J, et al.A 0.45-V, 14.6-nW CMOS subthreshold voltage reference with no resistors and no BJTs[J]. IEEE Transactions on Circuits and Systems II: Express Briefs , 2015 , 62(7) : 621–625.

- [10] 辛晓宁,张雷.一种宽输入电压范围高 PSRR 线性稳压器[J].电子设计工程 , 2016 , 24(17) : 185–187.

- [11] LU T,ZHANG J,ZONG Y.A Low-quiescent current low-dropout regulator with wide input range[J]. International Journal of Electronics and Electrical Engineering , 2015 , 3 (3) : 182–186.

- [12] HENG S,PHAM C K.A low-power high-PSRR low-dropout regulator with bulk-gate controlled circuit[J].IEEE Transactions on Circuits and Systems II: Express Briefs , 2010 , 57(4) : 245–249.

- [13] LEUNG K N,MOK P K T,KI W H.A novel frequency compensation technique for low-voltage low-dropout regulator[C]//IEEE International Symposium on Circuits and Systems , IEEE , 1999 : 102–105.

- [14] RAZAVI B.The bandgap reference a circuit for all seasons[J]. IEEE Solid-State Circuits Magazine , 2016 , 8(3) : 9–12.

- [15] CHONG S S,CHAN P K.A 0.9-μA a quiescent current output-capacitorless LDO regulator with adaptive power transistors in 65-nm CMOS[J].IEEE Transactions on Circuits and Systems I: Regular Papers , 2013 , 60(4) : 1072–1081.

- [16] HENG S,PHAM C K.A low-power high-PSRR low-dropout regulator with bulk-gate controlled circuit[J].IEEE Transactions on Circuits and Systems II: Express Briefs , 2010 , 57(4) : 245–249.

- [17] KEIKHOSRAVY K , MIRABBASI S.A 0.13 μm CMOS low-power capacitor-less LDO regulator using bulk-modulation technique[J].IEEE Transactions on Circuits and Systems I: Regular Papers , 2014 , 61(11) : 3105–3114.

- [18] KWOK K C,MOK P K T.Pole-zero tracking frequency compensation for low dropout regulator[C]//IEEE International Symposium on Circuits and Systems , 2002 , ISCAS 2002.IEEE , 2002 : 735–738.

(收稿日期:2020-11-12)

**作者简介:**

吴霞(1974-),女,硕士,实验师,主要研究方向:电子电路设计与应用。

鲍言锋(1992-),男,硕士研究生,主要研究方向:模拟集成电路设计。

邓婉玲(1980-),女,副教授,硕士生导师,主要研究方向:新型半导体器件与模拟集成电路设计。

扫码下载电子文档

(上接第 119 页)

- 日常活动监测[J].电工技术 , 2020(12) : 52–55.

- [3] 方轶,丛林虎,邓建球.基于国密算法的武器装备数据混合加密方案[J].探测与控制学报 , 2020 , 42(1) : 121–126.

- [4] 李晶,宋小明.密码技术在网络安全中的应用研究[J].内蒙古科技与经济 , 2020(1) : 58–59.

- [5] 赵磊.智能电网中电力用户隐私安全研究[D].长沙:长沙理工大学 , 2018.

- [6] 温伟强.网络攻击技术与网络安全探析[J].网络安全技术与应用 , 2015(1) : 79–81.

- [7] 李彬.浅谈非对称加密方式及其应用[J].信息记录材料 , 2021 , 22(1) : 214–215.

- [8] 姚华桢.一种基于 AES 算法的流媒体加密方法[J].中国有线电视 , 2006(2) : 153–157.

- [9] 鲍海燕,芦彩林.基于改进 RSA 算法的隐私数据集同态加密方法[J].太赫兹科学与电子信息学报 , 2020 , 18(5) : 929–933.

- [10] 张露.非侵入式负荷监测算法研究[D].广州:华南理工

大学 , 2019.

- [11] 李淑敬,李林国.RAS 算法在 VFP 中数字签名的实现[J].西安文理学院学报(自然科学版) , 2013 , 16(4) : 58–61.

- [12] 乐丁惕.基于 CTR 操作模式的 AES 算法加密组件的研究[J].长春工程学院学报(自然科学版) , 2012 , 13(4) : 117–118 , 122.

- [13] 张乐星.基于 AES 和 RSA 的网络数据加密方案[J].科技通报 , 2004(6) : 539–541.

- [14] 李学锋,陈丹.公开密钥密码体制与 RSA 算法[J].襄阳师专学报 , 1998 , 19(2) : 62–64.

- [15] 陈刚.基于数据加密算法的计算机通信安全技术[J].九江学院学报(自然科学版) , 2020 , 35(4) : 68–70 , 74.

(收稿日期:2020-11-14)

**作者简介:**

陈子秋(1997-),男,本科,主要研究方向:信息技术安全与应用。

冯瑞珏(1985-),通信作者,女,硕士,讲师,主要研究方向:信息技术安全与应用,E-mail:fengrj@gcu.edu.cn。

扫码下载电子文档

## 版权声明

经作者授权，本论文版权和信息网络传播权归属于《电子技术应用》杂志，凡未经本刊书面同意任何机构、组织和个人不得擅自复印、汇编、翻译和进行信息网络传播。未经本刊书面同意，禁止一切互联网论文资源平台非法上传、收录本论文。

截至目前，本论文已经授权被中国期刊全文数据库（CNKI）、万方数据知识服务平台、中文科技期刊数据库（维普网）、DOAJ、美国《乌利希期刊指南》、JST 日本科技技术振兴机构数据库等数据库全文收录。

对于违反上述禁止行为并违法使用本论文的机构、组织和个人，本刊将采取一切必要法律行动来维护正当权益。

特此声明！

《电子技术应用》编辑部

中国电子信息产业集团有限公司第六研究所