# 一种基于 130 nm CMOS 工艺的 K 波段上/下双向混频器 \*

赵玉楠, 潘俊仁, 彭尧, 何进, 王豪, 常胜, 黄启俊

(武汉大学 物理科学与技术学院, 湖北 武汉 430072)

**摘要:** 基于 130 nm RF CMOS 工艺, 提出了一种可实现上/下双向变频功能的 K 波段有源混频器。当收发机工作于接收模式时, 双向混频器执行下变频功能, 将低噪放大器放大后的射频信号转换为中频信号; 当收发机工作于发射模式时, 双向混频器则实现上变频功能, 将输入的基带信号转换为射频信号并输出至功率放大器。后仿真结果表明, 在 0 dBm 的本振驱动下, 混频器工作于上变频模式时的转换增益、噪声系数、输出 1 dB 压缩点在 23~25 GHz 范围内分别为 -1.1~−0.4 dB、12.9~3.3 dB、−8.2 dBm@24 GHz; 工作于下变频工作模式时的转换增益、噪声系数、输入 1 dB 压缩点在 23~25 GHz 范围内分别为 2.4~3.4 dB、15.2~15.6 dB、−3.6 dBm@24 GHz。混频器芯片面积为 0.6 mm<sup>2</sup>; 在 1.5 V 供电电压下, 消耗功率 12 mW。

**关键词:** 上/下双向混频器; K 波段; CMOS; 有源巴伦

中图分类号: TN432; TN773

文献标识码: A

DOI: 10.16157/j.issn.0258-7998.211716

中文引用格式: 赵玉楠, 潘俊仁, 彭尧, 等. 一种基于 130 nm CMOS 工艺的 K 波段上/下双向混频器[J]. 电子技术应用, 2022, 48(1): 94–99.

英文引用格式: Zhao Yunan, Pan Junren, Peng Yao, et al. A K-band up/down bidirectional mixer in 130 nm CMOS[J]. Application of Electronic Technique, 2022, 48(1): 94–99.

## A K-band up/down bidirectional mixer in 130 nm CMOS

Zhao Yunan, Pan Junren, Peng Yao, He Jin, Wang Hao, Chang Sheng, Huang Qijun

(School of Physics and Technology, Wuhan University, Wuhan 430072, China)

**Abstract:** An active bidirectional mixer performing the up/down conversion is proposed at K-band with a 130 nm CMOS in this paper. The mixer performs the down conversion in the Rx mode and converts the radio frequency(RF) signal amplified by low noise amplifier(LNA) into the intermediate frequency(IF) signal, whereas carries out the up conversion in the Tx mode and shifts the baseband(BB) signal up to the RF signal for the power amplifier(PA). Post-simulation results shows that with 0 dBm local oscillator(LO) drives, the mixer achieves the conversion gain(CG), noise figure(NF), and output 1 dB compression point(OP1dB) of −1.1~−0.4 dB, 12.9~13.3 dB from 23 to 25 GHz, and −8.2 dBm@24 GHz in up-conversion mode, respectively. In down-conversion mode, the mixer exhibits the CG, NF, and input 1 dB compression point(IP1dB) of 2.4~3.4 dB, 15.2~15.6 dB from 23 to 25 GHz, and −3.6 dBm@24 GHz, respectively. The chip area is 0.6 mm<sup>2</sup>, which consumes 12 mW from a supply of 1.5 V.

**Key words:** up/down bidirectional mixer; K-band; CMOS; active balun

## 0 引言

随着汽车工业快速地发展, 驾驶员迫切需要先进的驾驶辅助系统(Advanced Driver-Assistance System, ADAS)来提高道路交通的安全性<sup>[1-2]</sup>。毫米波雷达传感器作为先进驾驶辅助系统的重要模块, 具有高空间分辨率、低大气衰减等特点, 近年来受到了广泛的关注<sup>[3-7]</sup>。目前, 汽车雷达传感器主要采用两个毫米波段, 一个是 K 波段的 24 GHz, 用于盲点检测和防撞等短程应用; 另一个是 E 波段的 77 GHz, 用于自适应巡航控制等远程雷达通信。由于 CMOS 工艺具有开关速度快、成本低、集成度

高等优点, 为了满足日益增长的市场需求, 基于 CMOS 工艺的 K 波段收发机得到了广泛的研究和开发<sup>[8-13]</sup>。传统无线收发机的收发支路一般采用分开设计的方式。作为收发支路中的关键组成部分, 下变频混频器在接收支路中, 将低噪放大器放大后的射频信号下变频为中频信号; 而上变频混频器则在发射支路中, 将基带信号上变频为射频信号。相对来说, 这种收发支路分开设计的方式将占用更大的芯片面积, 消耗更多的功耗, 增加系统的复杂度, 对小型化、低功耗、低成本的芯片设计较为不利。虽然单个无源混频器可以实现上/下双向变频功能, 但是它们有转换损耗, 并且需要较高的本振驱动<sup>[14]</sup>, 从而导致系统功耗显著增加。

\* 基金项目: 国家自然科学基金(61774113, 61874079, 62074116, 81971702)

本文基于 130 nm RF CMOS 工艺, 设计了一种可实现上/下双向变频功能的 K 波段混频器。创新地通过同一核心电路实现了上变频与下变频的混频功能, 同时在保证混频器有较好性能的前提下, 节省了射频接收机芯片面积。

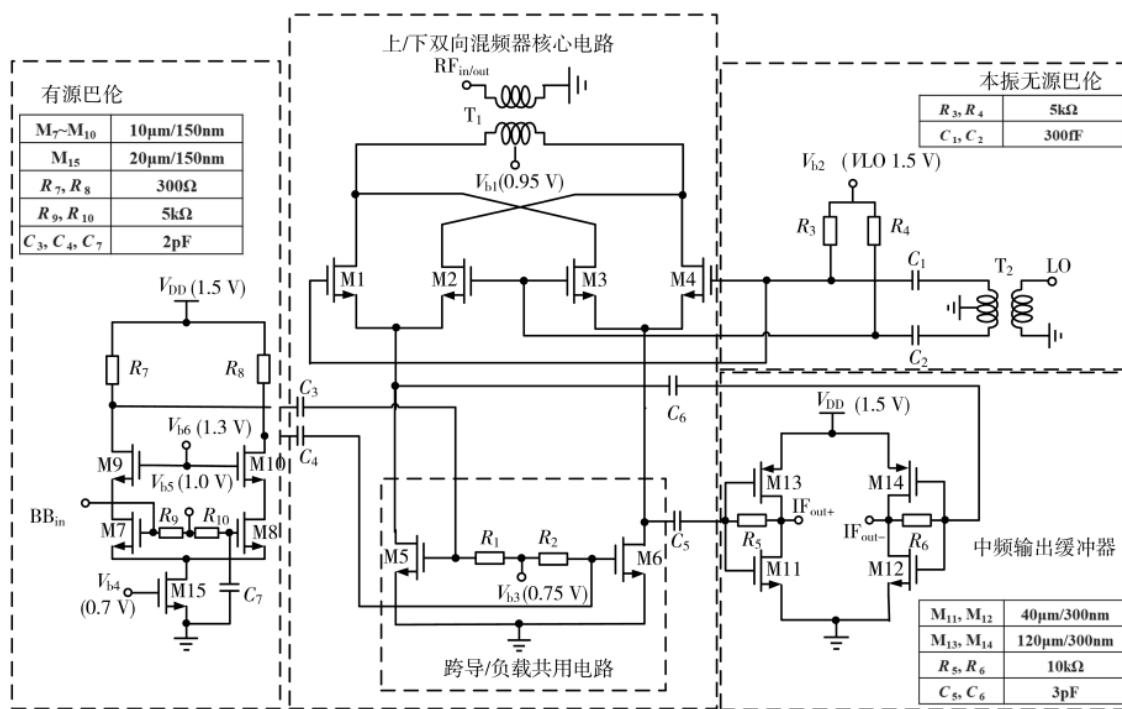

## 1 上/下双向混频器电路原理图及设计思路

K 波段上/下双向变频混频器的电路原理图如图 1 所示。该双向混频器由混频器核心电路、本振(Local Oscillator, LO)巴伦电路、基带(Baseband, BB)有源巴伦电路和中频(Intermediate Frequency, IF)输出缓冲电路组成。本振巴伦电路具有单端-差分转换和在本振端口 50 Ω 阻抗匹配的功能; 基带有源巴伦电路则对基带信号进行单端-差分转换和放大; 中频缓冲电路用于在中频差分输出端口  $IF_{out+}$  和  $IF_{out-}$  驱动 50 Ω 负载。

在图 1 中, 本文创新地采用了跨导/负载( $g_m$ /load)共用电路, 在以吉尔伯特(Gilbert)混频器为基础的核心电路上实现上/下双向变频功能。当混频器上变频时, 跨导/负载共用电路执行跨导( $g_m$ )功能, 将经过有源巴伦电路进行单端-差分变换后的基带差分电压信号转换为差分基带电流信号, 并输入至本振开关级电路, 进而被上变频为差分射频(Radio Frequency, RF)电流信号; 混频器下变频时, 将经过 RF 变压器  $T_1$  进行单端-差分变换后的射频差分电压信号转换为射频差分电流信号, 并输入至本振开关级电路, 进而被下变频为中频差分电流信号, 此时跨导/负载共用电路实现负载(load)功能, 将中频差分电流信号最终转换为中频差分电压信号。更为详细的工作原理将在第 2 节结合电路进行具

体分析。

## 2 双向混频器的电路设计和分析

### 2.1 上/下双向混频器核心电路

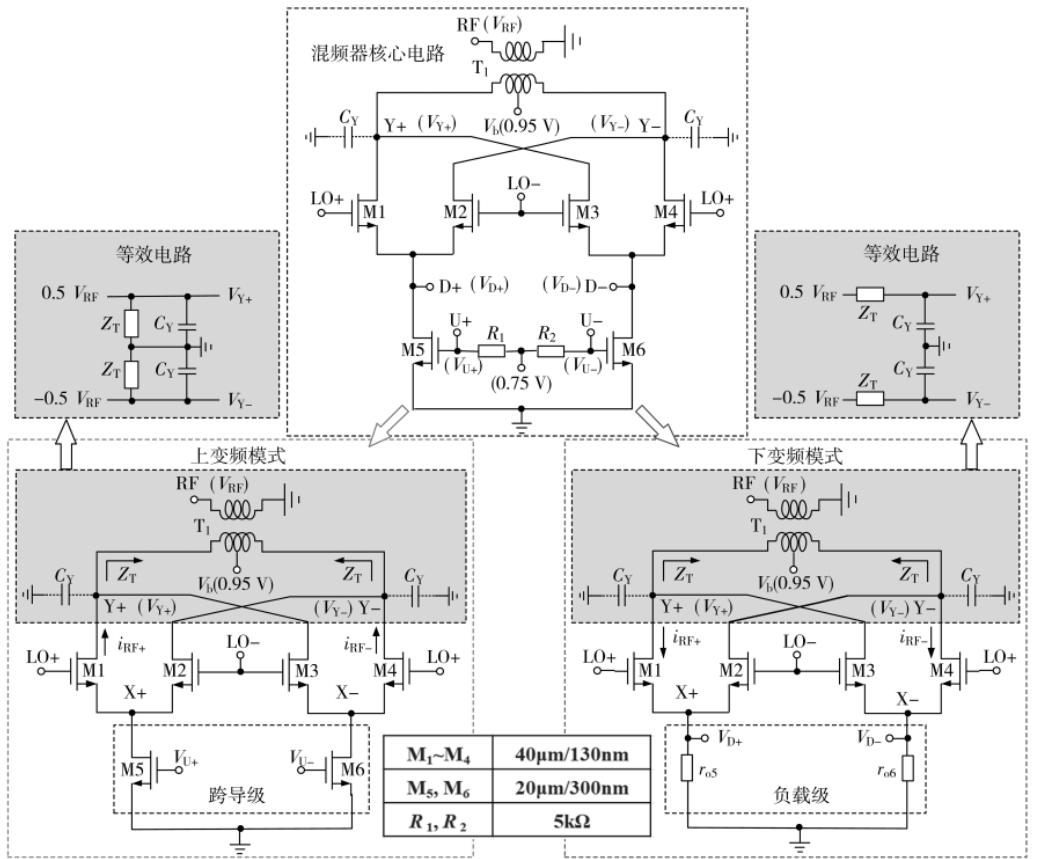

图 2 描述了混频器核心电路图及其上/下双向工作模式。晶体管  $M_1 \sim M_4$  组成由差分信号  $LO_+$  和  $LO_-$  驱动的本振开关级。

上变频模式: 有源巴伦电路产生的基带差分电压信号  $V_{U+}$  和  $V_{U-}$ , 经由晶体管  $M_5 \sim M_6$  构成的跨导( $g_{m5,6}$ )级传输到电路节点  $X_+$  和  $X_-$ , 再经由 LO 开关级, 上变频为 RF 差分电流信号  $i_{RF+}, i_{RF-}$ , 通过从电路节点  $Y_+$  和  $Y_-$  看进去的等效输入阻抗, 得到射频差分电压信号  $V_{Y+}, V_{Y-}$ , 最后由片上变压器巴伦  $T_1$  转变为单端射频输出信号  $V_{RF}$ , 并在 RF 端口完成 50 Ω 负载阻抗匹配。如图 2 中所示, 根据变压器巴伦  $T_1$  的自身阻抗  $Z_T$  和电路节点  $Y_+/Y_-$  处的寄生电容  $C_Y$ , 混频器核心电路在上变频模式的转换增益(up-conversion gain, up-CG)可以表示为:

$$A_{up-CG} = \frac{2}{\pi} g_{m5,6} \left| \frac{1}{1/Z_T + j\omega_{RF} C_Y} \right| \quad (1)$$

由此可知, 若要提高  $A_{up-CG}$ , 既可以通过增加  $g_{m5,6}$ , 也可以通过  $Z_T$  与  $C_Y$  在工作频率  $\omega_{RF}$  处谐振来实现。

下变频模式: 晶体管  $M_5 \sim M_6$  成为有源负载( $r_{o5,6}$ )级。 $T_1$  将单端射频输入信号  $V_{RF}$  差分为电压信号  $V_{Y+}, V_{Y-}$ , 通过电路节点  $Y_+$  和  $Y_-$  处  $Z_T$  与  $C_Y$  的等效阻抗, 转换为 RF 差分电流信号  $i_{RF+}, i_{RF-}$ , 再经过 LO 开关级, 下变频为 IF 差分电流信号, 最终经有源负载  $r_{o5,6}$  得到 IF 差分电压信号  $V_{D+}, V_{D-}$ 。同理, 混频器核心电路在下变频模式的转换增益(down-conversion gain, down-CG)可表示为:

图 1 K 波段上/下双向混频器电路原理图

图 2 混频器核心电路及上/下双向工作模式

$$A_{\text{down-CC}} = \frac{2}{\pi} \left| \frac{1/j\omega_{\text{RF}} C_Y}{1/Z_T + j\omega_{\text{RF}} C_Y} \right| \quad (2)$$

因此,混频器可工作在上/下双向变频模式。仿真结果显示,在栅源电压  $V_{GS,6}$  为 0.75 V 时,晶体管  $M_5 \sim M_6$  偏置在饱和区;当尺寸为  $20 \mu\text{m}/300 \text{ nm}$  时,  $M_5 \sim M_6$  获得较大的输出电阻  $r_{o5,6}$ ,为  $5 \text{ k}\Omega$ 。折衷考虑转换损耗、开关速度和寄生电容  $C_Y$  等性能参数,本振开关级晶体管  $M_1 \sim M_4$  的尺寸最终优化为  $40 \mu\text{m}/130 \text{ nm}$ 。偏置电压  $V_b$  被设置为 0.95 V 以平衡上/下变频的转换增益。

## 2.2 有源巴伦、本振巴伦和输出缓冲器电路

如图 1 所示,基带有源巴伦电路由差分共源共栅对 ( $M_7 \sim M_9 - R_7$  和  $M_8 \sim M_{10} - R_8$ ) 及电流源 ( $M_{15}$ ) 组成。差分共源共栅对的一个输入端口用于输入单端基带信号  $BB_{in}$ , 另一个端口则通过电容  $C_7$  直接接地。电路完成了对  $BB_{in}$  信号的差分转换和放大,其增益表示为:

$$A_V = g_{m7,8} R_{7,8} \quad (3)$$

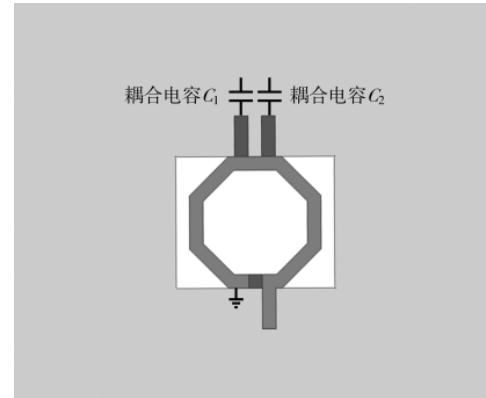

为了获得较强的驱动特性,采用了自偏置反相器型放大器作为 IF 输出缓冲器电路,包括晶体管  $M_{11} \sim M_{14}$  和反馈电阻  $R_5 \sim R_6$ 。此外,由于工作在高频段,本振巴伦电路同射频端口一样采用片上变压器巴伦来实现。 $T_1$  和  $T_2$  有着类似的如图 3 所示的结构。

为更好地与 LO 开关级晶体管  $M_1 \sim M_4$  的输入端进行匹配,将  $T_2$  的两个差分端口串联耦合电容  $C_1$  和  $C_2$ ,以

图 3 片上本振变压器巴伦  $T_2$

补偿其输入端的感性阻抗;同时  $C_1$  和  $C_2$  还能用于隔离  $M_1 \sim M_4$  的偏置电压与  $T_2$  中心接地抽头间的直流电平。

## 3 双向混频器版图及仿真结果

### 3.1 双向混频器版图

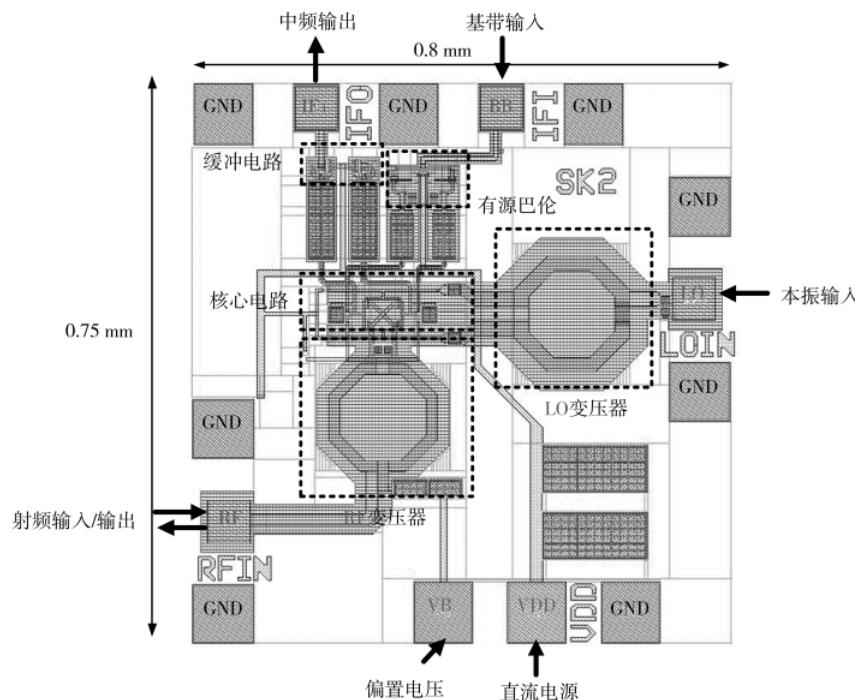

基于后端有 7 层金属层的 130 nm RF CMOS 工艺,本文设计了可实现上/下双向变频功能的 K 波段混频器。图 4 所示为 K 波段双向混频器版图,包括两个片上变压器巴伦  $T_1$ 、 $T_2$  和所有测试焊盘在内的整个芯片版图面积为  $0.75 \text{ mm} \times 0.8 \text{ mm}$ ,其中 G-S-G 焊盘的中心间距为  $150 \mu\text{m}$ 。

图 4 K 波段双向混频器版图

### 3.2 后仿真结果

为了得到更为精确的混频器性能,采用了全波三维电磁高频结构仿真器对混频器的无源元件(包括变压器、电容、金属连线和过孔等)进行了整体电磁仿真,最后将所生成的无源多端口 S 参数文件与晶圆厂提供 PDK 中的有源器件进行联合仿真,以获得整体混频器设计的最终性能。整体混频器优化后的最终仿真结果如图 5~图 7 所示。

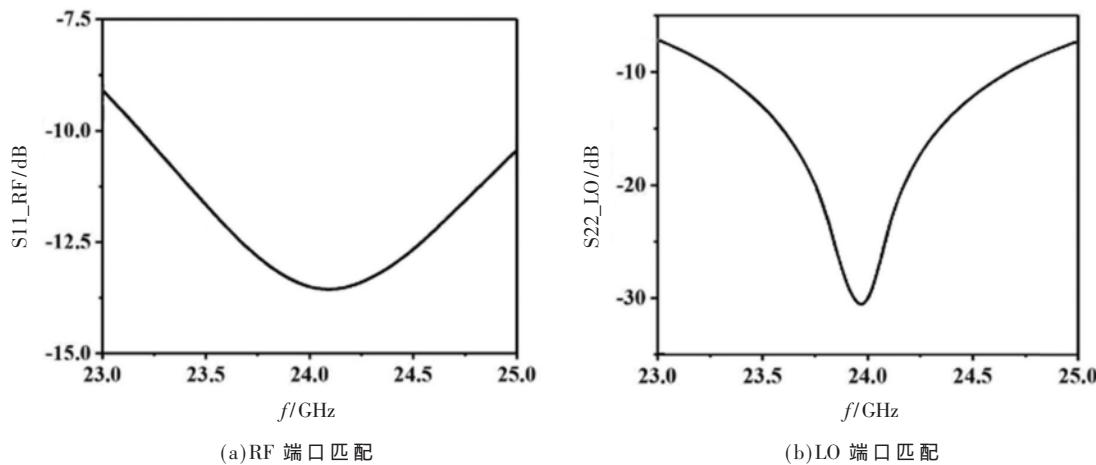

图 5 为射频端口和本振端口在 23~25 GHz 频段内的 50 Ω 阻抗匹配(回波损耗 S11\_RF 和 S22\_LO)仿真结果,可以看出在 23.3~25 GHz 频段内,混频器 S11\_RF 和 S22\_LO 都小于 -10 dB,具备良好的阻抗匹配度。

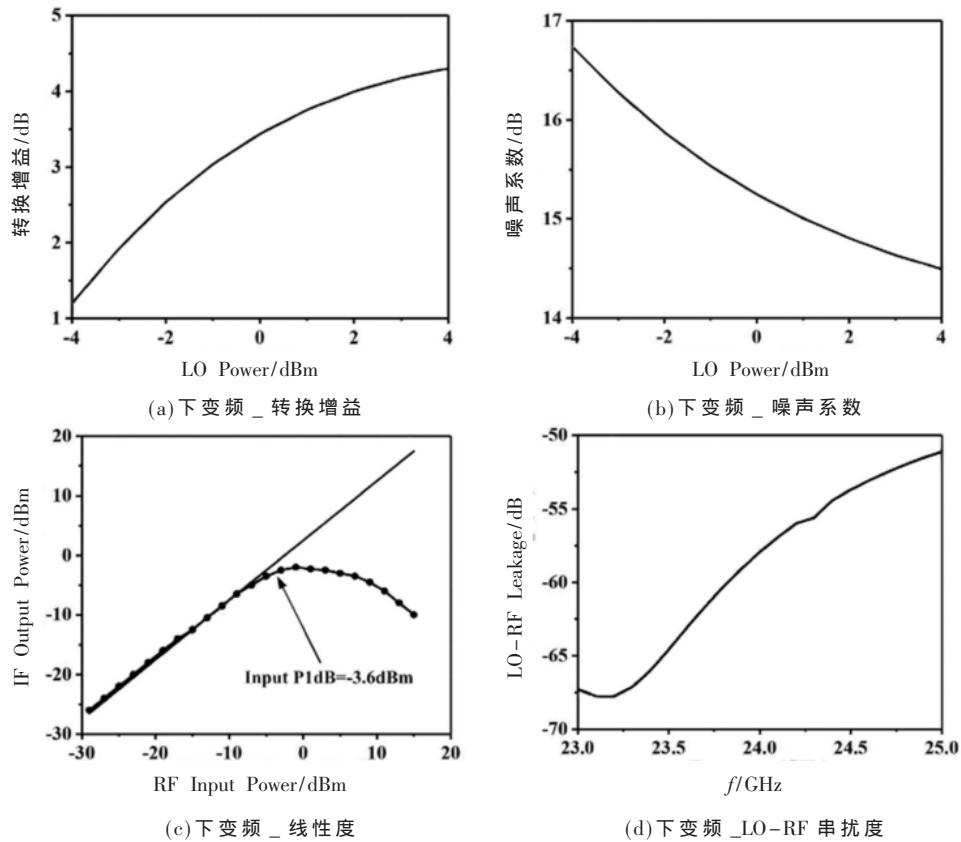

图 6 为混频器下变频模式性能仿真结果。图 6(a)和图 6(b)为电路工作在下变频模式时,在不同本振驱动功

率下的混频器转换增益和噪声系数(NF)。可以看到,混频器的下变频转换增益和噪声系数随着本振功率的增加(从 -4 dBm 变化至 4 dBm)而逐步地得到改善。但考虑到实际应用中本振驱动信号一般由压控振荡器或频率合成器产生,其功率不会太大,因此选定 0 dBm 为下变频模式下混频器的本振输入功率。此时,混频器的下变频转换增益和下变频噪声系数分别为 3.4 dB 和 15.2 dB。图 6(c)和图 6(d)为本振功率是 0 dBm 时,混频器的线性度(RF 端口输入 -IF 端口输出的输入 1 dB 压缩点 IP<sub>1dB</sub>)和本振 - 射频(LO-RF)端口的隔离度(ISO)仿真结果。可见在下变频模式下,电路在 24 GHz 频点时的线性度为 -3.6 dBm,隔离度为 -58 dB,端口隔离性能良好。

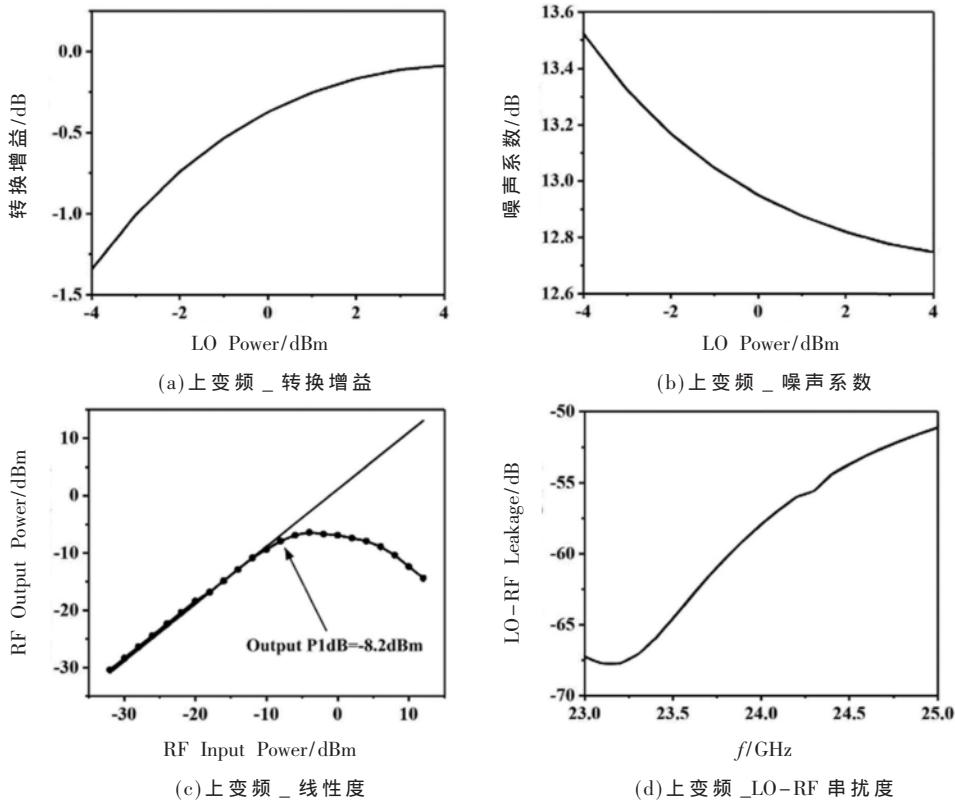

图 7 为混频器上变频模式性能仿真结果。图 7(a)和图 7(b)为电路工作在上变频模式时,在不同本振驱动功

图 5 射频/本振端口 50 Ω 阻抗匹配仿真

图 6 混频器下变频模式性能仿真

图 7 混频器上变频模式性能仿真

率下的混频器转换增益和噪声系数。对其的分析同图 6(a)

和图 6(b)类似,不再赘述。当本振驱动功率为 0 dBm 时,

表 1 本文电路性能总结与同类型设计性能比较

| 参考文献              | RF 频段/GHz | LO 功率/dBm | LO-RF 隔离/dB | 转换增益/dB   | 功耗/mW | 噪声系数/dB | 面积/mm <sup>2</sup> | 线性度/dBm |

|-------------------|-----------|-----------|-------------|-----------|-------|---------|--------------------|---------|

| [8] <sup>1</sup>  | 18~28     | 3         | >30         | -2~0.7    | 8     | N.A.    | 0.4                | -7~-5.2 |

| [9] <sup>1</sup>  | 23.4~29.2 | 4.7       | >28.9       | -1.9      | 22.8  | N.A.    | 0.86               | 0.3     |

| [10] <sup>2</sup> | 24        | N. A.     | N.A.        | 4.9       | 24    | 16.8    | 0.58               | -13.7   |

| [15] <sup>2</sup> | 21.7~24.2 | 3         | N.A.        | 10.7      | 23    | N.A.    | 0.51               | -13.6   |

| 本文 <sup>1</sup>   | 24        | 0         | >55         | -1.1~-0.4 | 12    | 12.9    | 0.6                | -8.2    |

| 本文 <sup>2</sup>   | 24        | 0         | >55         | 2.4~3.4   | 12    | 15.2    | 0.6                | -3.6    |

注：<sup>1</sup> 上变频电路；<sup>2</sup> 下变频电路；本文参数均为后仿真结果

混频器的上变频转换增益和上变频噪声系数分别为-0.4 dB 和 12.95 dB；在 24 GHz 频点时，混频器的线性度(IF 端口输入-RF 端口输出的输出1 dB 压缩点 OP<sub>1dB</sub>)为-8.2 dBm，本振-射频端口的隔离度为-58 dB。

版图的后仿真结果表明，在 0 dBm 的本振驱动功率下，混频器工作于上/下两种变频模式时均可获得较好的输入线性度、适宜的噪声系数和转换增益，本振和射频端口具备较强的隔离度，而且 50 Ω 阻抗匹配良好，整体电路直流功耗为 12 mW。

表 1 总结了所提出的上/下双向混频器的性能，并与最近报道的混频器进行了参数对比。可以看出，本设计不仅实现了上/下双向变频功能，且表现出具有竞争力的性能。

#### 4 结论

本文基于 130 nm RF CMOS 工艺，采用了跨导/负载共用电路，在以 Gilbert 混频器为基础的核心电路上，提出了一种可实现上/下双向变频功能的 K 波段有源混频器。整个芯片版图面积包括两个片上变压器巴伦 T<sub>1</sub>、T<sub>2</sub> 和所有测试焊盘在内为 0.75 mm×0.8 mm。在 1.5 V 供电电压下，整体混频器电路的直流功耗为 12 mW。与其他混频器相比较，本设计在面积、功耗、隔离度等方面表现出具有竞争力的性能。因此，该混频器在高集成度 K 波段 CMOS 收发机中具有潜在的应用前景。

#### 参考文献

- [1] GERÓNIMO D, LÓPEZ A M, SAPPA A D, et al. Survey of pedestrian detection for advanced driver assistance systems[J]. IEEE Transactions on Pattern Analysis and Machine Intelligence, 2010, 32(7): 1239~1258.

- [2] LI L, WEN D, ZHENG N, et al. Cognitive cars: a new frontier for ADAS research[J]. IEEE Transactions on Intelligent Transportation Systems, 2012, 13(1): 395~407.

- [3] TURK A S, KESKIN A K, UYSAL H, et al. Millimeter wave short range radar system design[C]//2016 IEEE Radar Methods and Systems Workshop(RMSW), 2016: 76~78.

- [4] KESKIN A K, SENTURK M D, DEMIREL S, et al. Front-end design for Ka band mm-wave radar[C]//2016 17th International Radar Symposium(IRS), 2016: 1~4.

- [5] 李骏, 王健安, 赖凡. 毫米波片上雷达技术研究进展[J]. 微电子学, 2019, 49(4): 545~550.

- [6] 李洋, 李浩, 王占平, 等. 一种应用于汽车安全系统的LFMCW 雷达[J]. 火控雷达技术, 2014, 43(4): 26~29, 37.

- [7] 鲍迎. 小型化 24GHz FMCW 汽车防撞雷达[D]. 杭州: 浙江大学, 2011.

- [8] VERMA A, O K K, LIN J A. low-power up-conversion CMOS mixer for 22~29-GHz ultra-wideband applications[J]. IEEE Transactions on Microwave Theory and Techniques, 2006, 54(8): 3295~3300.

- [9] WON Y S, KIM C H, LEE S G A. 24 GHz highly linear up-conversion mixer in CMOS 0.13 μm technology[J]. IEEE Microwave and Wireless Components Letters, 2015, 25(6): 400~402.

- [10] WANG S, LIN W J A. 10/24-GHz CMOS/IPD monopulse receiver for angle-discrimination radars[J]. IEEE Trans. Circuit Syst. I, Reg. Papers, 2014, 61(10): 2999~3006.

- [11] LIN H H, LIN Y H, WANG H A. high linearity 24-GHz down-conversion mixer using distributedderivative superposition technique in 0.18 μm CMOS process[J]. IEEE Microwave and Wireless Components Letters, 2018, 28(1): 49~51.

- [12] JAIN V, SUNDARAMAN S, HEYDARI P A. 22~29-GHz pulse-radar receiver front-end in 0.18 μm CMOS[J]. IEEE Trans. Microw. Theory Techn., 2009, 57(8): 1903~1914.

- [13] 刘智卿. 硅基毫米波接收前端中放大器和混频器集成电路研究[D]. 成都: 电子科技大学, 2018.

- [14] 李垚, 朱晓维. 一种 2.8~6GHz 单片双平衡无源混频器[J]. 微波学报, 2019, 35(6): 26~30.

- [15] LIN D R, KAO K Y, LIN K Y A. K-band high-gain linear CMOS mixer with current-bleeding neutralization technique[C]//2018 Asia-Pacific Microwave Conference (APMC). Kyoto, Japan: IEEE, 2018: 267~269.

(收稿日期: 2021-05-06)

#### 作者简介:

赵玉楠(1998-), 女, 硕士研究生, 主要研究方向: 射频集成电路设计。

潘俊仁(1997-), 男, 硕士研究生, 主要研究方向: 射频集成电路设计。

彭尧(1994-), 男, 硕士研究生, 主要研究方向: 模拟、射频、毫米波集成电路设计。

扫码下载电子文档

## 版权声明

经作者授权，本论文版权和信息网络传播权归属于《电子技术应用》杂志，凡未经本刊书面同意任何机构、组织和个人不得擅自复印、汇编、翻译和进行信息网络传播。未经本刊书面同意，禁止一切互联网论文资源平台非法上传、收录本论文。

截至目前，本论文已经授权被中国期刊全文数据库（CNKI）、万方数据知识服务平台、中文科技期刊数据库（维普网）、DOAJ、美国《乌利希期刊指南》、JST 日本科技技术振兴机构数据库等数据库全文收录。

对于违反上述禁止行为并违法使用本论文的机构、组织和个人，本刊将采取一切必要法律行动来维护正当权益。

特此声明！

《电子技术应用》编辑部

中国电子信息产业集团有限公司第六研究所