# 基于 LVDS 传输可靠性优化设计

杜凯旋<sup>1,2</sup>, 焦新泉<sup>1,2</sup>, 杨志文<sup>1</sup>, 李辉景<sup>1</sup>

(1. 中北大学 电子测试技术国家重点实验室, 山西 太原 030051;

2. 中北大学 仪器科学与动态测试教育部重点实验室, 山西 太原 030051)

**摘要:** 针对 LVDS 传输初始化建链过程中出现的首帧丢失和干扰导致的误建链问题, 对链路传输机理及稳定性进行分析, 并从硬件与软件两方面进行优化。软件上采取识别帧头和发送训练帧的方法, 改善建链过程; 硬件上选用性能更好的隔离芯片, 优化差分端阻抗, 减小干扰对数据传输的影响。经多次试验证明, 优化后的链路可实现 480 Mb/s 速率下的可靠传输, 该优化设计对提高 LVDS 链路传输稳定性和减少误码方面具有很好的参考价值。

**关键词:** LVDS; 链路建立; 训练帧; 电气隔离

中图分类号: TN919

文献标识码: A

DOI: 10.16157/j.issn.0258-7998.211811

中文引用格式: 杜凯旋, 焦新泉, 杨志文, 等. 基于 LVDS 传输可靠性优化设计[J]. 电子技术应用, 2022, 48(1): 105–108, 114.

英文引用格式: Du Kaixuan, Jiao Xinquan, Yang Zhiwen, et al. Optimized design based on LVDS transmission reliability[J]. Application of Electronic Technique, 2022, 48(1): 105–108, 114.

## Optimized design based on LVDS transmission reliability

Du Kaixuan<sup>1</sup>, Jiao Xinquan<sup>1,2</sup>, Yang Zhiwen<sup>1</sup>, Li Huijing<sup>1</sup>

(1. State Key Laboratory of Electronic Technology, North University of China, Taiyuan 030051, China;

2. Key Laboratory of Instrument Science and Dynamic Testing(Ministry of Education),

North University of China, Taiyuan 030051, China)

**Abstract:** Aiming at the problem of the first frame loss and the mis-establishment of the link caused by the interference during the initial link establishment of LVDS transmission, this paper analyzes the link transmission mechanism and stability, and optimizes it from both hardware and software aspects. The software adopts the method of identifying the frame header and sending the training frame to improve the link building process. The hardware chooses a better performance electrical isolation chip and optimizes the differential terminal impedance to reduce the impact of interference on data transmission. Many tests have proved that the optimized link can achieve reliable transmission at a rate of 480 Mb/s. This optimized design has a good reference value for improving the transmission stability of the LVDS link and reducing errors.

**Key words:** LVDS; link establishment; training frame; electrical isolation

## 0 引言

随着电子技术与通信技术的迅猛发展, 高速率高帧频的数据为并行传输带来巨大挑战, 面对高速并行传输带来的偏移和干扰问题<sup>[1]</sup>, 低电压差分信号(Low-Voltage Differential Signaling, LVDS)凭借高速率、低功耗以及抗共模干扰性好等优点, 广泛应用于军事、科研、工业等各领域的数据传输通信<sup>[2]</sup>。

针对 LVDS 通信建链过程中出现的丢帧及误码现象, 为了进一步提高 LVDS 传输链路的可靠性, 本文对 LVDS 传输链路硬件物理层和软件链路层进行研究, 提出相应的优化措施并加以验证<sup>[3]</sup>。实际测试链路传输稳定, 可有效解决丢帧和误码问题。

## 1 LVDS 链路概述

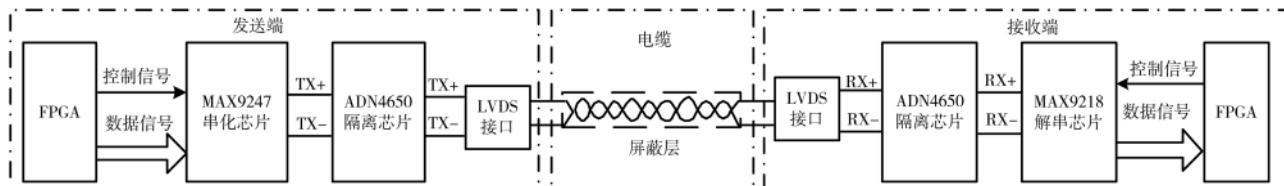

LVDS 链路原理框图如图 1 所示, 由发送端、接收端

图 1 LVDS 链路原理框图

和传输电缆组成,可实现480 Mb/s速率下图像数据的传输。串化解串芯片选用MAXIM公司研发的MAX9247和MAX9218,支持700 Mb/s传输速率。在接口处选用ADI公司的AND4650 LVDS缓冲芯片实现电气隔离,最大可支持600 Mb/s的开关速率。图1中图像数据信号和控制信号由FPGA发出,经MAX9247串化为一对差分信号,经过AND4650隔离后通过全信双绞电缆送至接收端。在接收端中,隔离后的差分信号进入MAX9218,通过时钟恢复技术解串,恢复为图像数据信号后由FPGA接收,整条链路由FPGA实现数据发送与接收的逻辑控制<sup>[4]</sup>。

## 2 故障定位

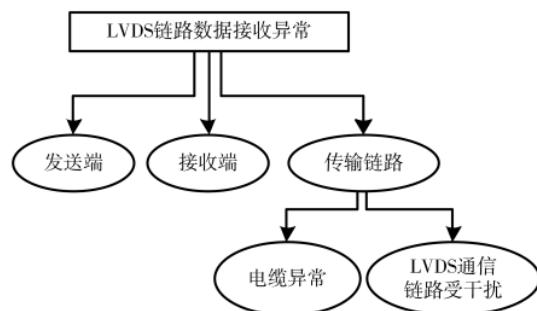

从“LVDS链路数据接收异常”事件出发,对故障产生的原因进行分析总结,绘制故障树如图2所示。故障产生的原因可分为3个分支,即:发送端异常、接收端异常和传输链路异常,传输链路异常又可分为电缆异常和LVDS通信链路受干扰<sup>[5]</sup>。

图2 故障树图

若发送端异常,可能出现数据未发送的故障情况。现采用FPGA开发软件的DEBUG模式监测发送端数据,当出现首帧丢失时,监测到发送端首帧数据已发送,因此该分支故障可能性较低<sup>[6]</sup>。

若接收端异常,可能出现第一帧未接收的故障现象。故障发生时,DEBUG模式监测到链路未建立,此时FPGA无法接收数据。同时也无法通过示波器对首帧的差分信号进行抓取和识别,可证明故障与接收端链路建立有关。

若电缆异常,可能由于电缆受损或工艺等原因导致的传输链路故障,经过核实用电缆传输链路阻抗与制作工艺均符合要求。传输电缆采用全性双绞带屏蔽线(LVDS信号传输专用线缆),连接器为高速连接器,最高传输速率可达1.6 Gb/s,远远满足数据传输的要求,该分支故障概率较低<sup>[7]</sup>。

若LVDS通信链路受干扰,可能由于干扰引发误码进一步导致误码和丢帧故障。为了模拟干扰环境,将设备放置在电磁干扰环境下,进行多次测试,误码现象出现,可证明误码与链路干扰有关。

综上所述,丢帧及误码问题极大可能与接收端链路建立及链路上的干扰有关,因此应针对软件链路层和硬件物理层进行进一步的研究与优化。

## 3 软件优化

上述故障定位表明,在首帧数据接收时MAX9218并未解出图像数据,同时恶劣环境及干扰等因素也会影响传输链路稳定性,因此软件方面的优化不可或缺。

### 3.1 LVDS建链机理分析

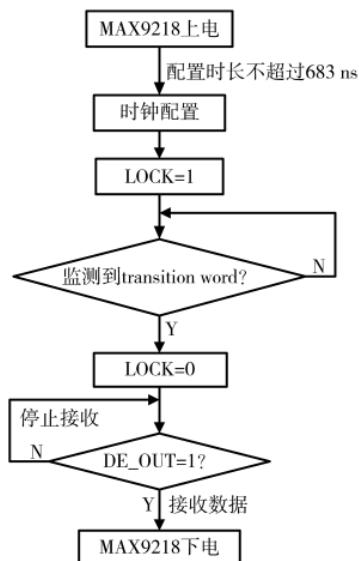

LVDS传输链路发送端和接收端采用的芯片分别为MAX9247和MAX9218,两端在数据传输的过程中需要建立连接,链路建立流程如图3所示。

图3 MAX9218 建链流程图

接收端MAX9218上电后,内部锁相环PLL与外部24 MHz参考时钟REFCLK进行锁定,锁定时间不超过683 ns,待锁定完成后LOCK信号由高阻态变为高电平<sup>[8]</sup>。LOCK信号为高时,监测差分输入端是否有transition word输入,监测到transition word后,LOCK信号变为低电平。当MAX9218解出数据信号后,DE\_OUT信号拉高,FPGA开始接收数据,当DE\_OUT信号拉低时停止接收数据。

### 3.2 故障原因总结

根据软件建立机理分析,以下两个方面可造成首帧丢失及误码现象。

一方面在链路实际传输过程中,接收端MAX9218上电后,若图像数据立即发送,此时LVDS传输线路时钟配置还未完成,LOCK信号处于高阻态,链路不具备接收数据条件,会错过首帧transition word,因此FPGA未正常启动数据接收。待下一帧开始时,时钟配置完成,可以正常建立链路连接,数据接收恢复正常。

另一方面当链路处于空闲状态时,若链路上的干扰被MAX9218解出,DE\_OUT拉高,FPGA开始接收数据,此时会导致出现误码情况。

### 3.3 软件优化设计

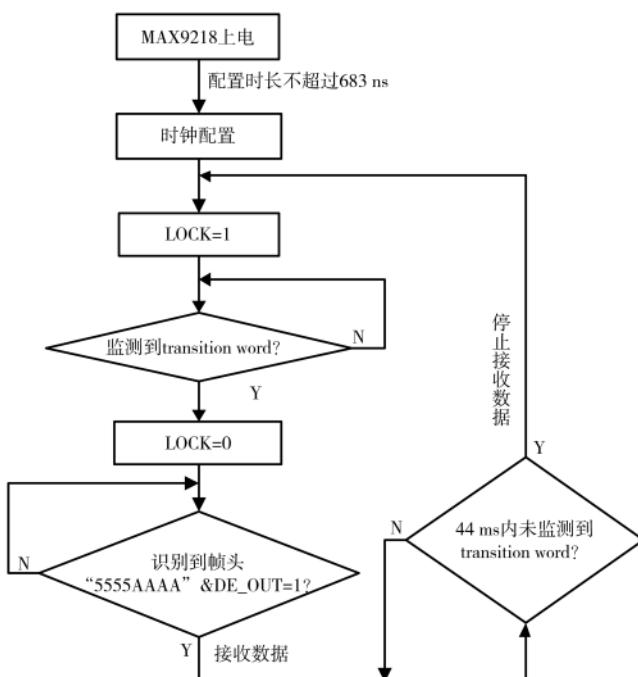

针对链路初始化建链过程中出现的丢帧和误码现象,现提出一种识别帧头来启动数据接收和发送训练帧的软件优化方法,优化后的链路建立流程如图4所示。

图 4 优化后 MAX9218 建链流程图

优化后的链路启动数据接收的条件为识别到帧头“5555AAAA”，控制信号 LOCK=‘0’，DE\_OUT=‘1’。同时

设置自动断链机制，当链路上 44 ms 内没有监测到 transition word 时，则停止数据接收，LOCK 信号由低变高。识别帧头及自动断链等措施可避免当链路空闲时由于干扰引发误建链而导致的误码的故障。

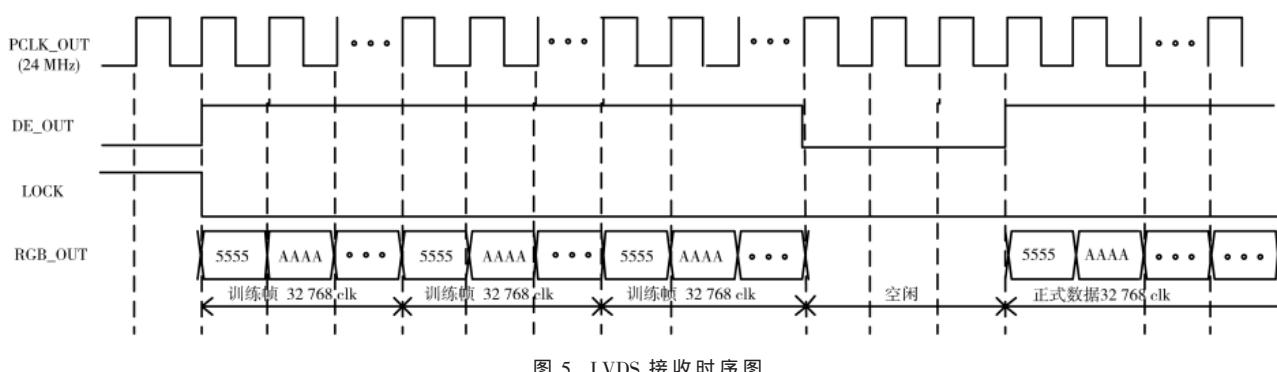

LVDS 接收时序图如图 5 所示，训练帧与正式数据帧结构相同，长度为 64 KB，解串后的宽度为 16 bit，但训练帧并不包含有用信息。发送端在发送正式数据前先发送 3 帧训练帧，每帧数据共耗时 32 768 个时钟周期，3 帧训练帧总耗时约 3 ms，远超最大链路时钟配置时长 683 ns，因此训练帧能使得 LVDS 传输链路在接收到正式数据之前 LOCK 信号就处于低电平的状态，确保接收端能够可靠稳定地接收正式数据，同时训练帧的丢失也不会对正式数据完整性产生影响<sup>[9]</sup>。

### 4 硬件优化

#### 4.1 电气隔离分析

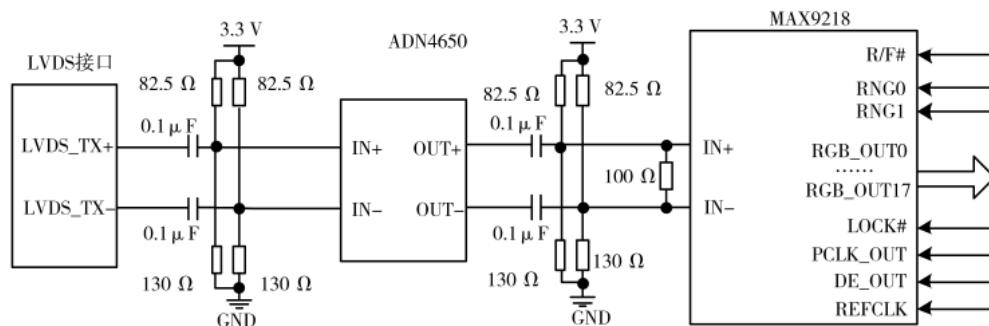

如图 6 接收端所用的隔离芯片为 ADN4650，根据芯片手册介绍，若差分输入端输入浮空(未连接，无端接电阻)，且差分输入电压  $V_{ID}$  介于  $\pm 100 \text{ mV}$  之间，此时 ADN4650 的差分输出端逻辑状态为不定<sup>[10]</sup>。为了避免这种状况，ADN4651 在 ADN4650 的基础上集成的故障安全接收器能够确保当差分输出电压  $V_{OD}$  介于  $\pm 100 \text{ mV}$  之间，差分输出电压  $V_{OD}$  为高电平，表 1 为两款芯片真值表。

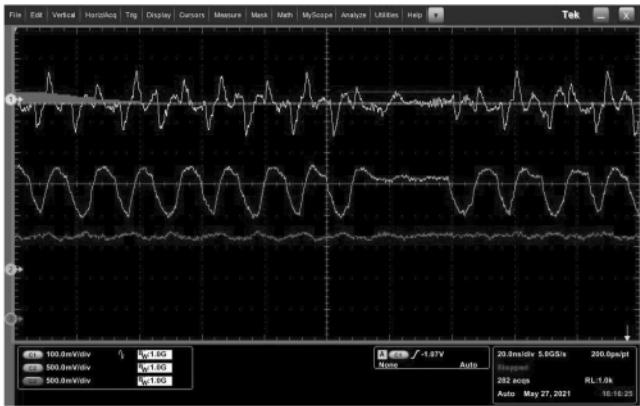

为了验证干扰对隔离输出信号的影响，利用信号源的噪声信号模拟链路干扰，将信号源产生的峰峰值 100 mV 的噪声信号接入链路中，并通过示波器抓取测试信号，图 7 所示波形从上至下分别对应信号源输入、ADN4650 差

图 5 LVDS 接收时序图

图 6 接收端电路原理图

表 1 ADN4650/4651 真值表

| 上电 | $V_{DD}/mV$            | ADN4650     |     | ADN4651     |     |

|----|------------------------|-------------|-----|-------------|-----|

|    |                        | $V_{OP}/mV$ | 逻辑  | $V_{OP}/mV$ | 逻辑  |

| 是  | $\geq 100$             | $\geq 250$  | 高电平 | $\geq 250$  | 高电平 |

| 是  | $\leq -100$            | $\leq -250$ | 低电平 | $\leq -250$ | 低电平 |

| 是  | $-100 < V_{ID} < +100$ | 不确定         | 不确定 | $\geq 250$  | 高电平 |

| 否  | 无关                     | $\geq 250$  | 高电平 | $\geq 250$  | 高电平 |

图 7 干扰模拟实验

分输出、AND4651 差分输出。

对比不同通道的波形，可以看出 ADN4650 差分输出

随噪声信号抖动，而 ADN4651 差分输出稳定维持在高电平不随噪声抖动。

#### 4.2 硬件电路优化设计

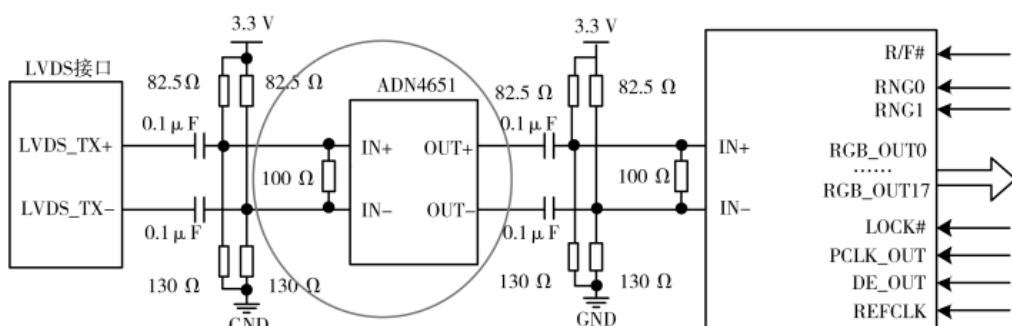

电路优化部分如图 8 更改后原理图中圈出部分所示。

隔离芯片由 AND4650 替换为 AND4651，当传输链路空闲时，AND4651 的故障安全机制可以拉高输出，确保链路  $DE\_OUT=0$  从而无法建立连接，链路不受输入端干扰的影响进入不确定的状态，从而增强链路的稳定性<sup>[11]</sup>。

差分输入端前并联  $100\Omega$  的端接电阻，可最大程度减少来自链路上的电磁干扰。并联的端接电阻可减小差分输入端间的阻抗，差分输入端间的阻抗的降低会影响差分输入信号的压差。经过测试验证，并联的  $100\Omega$  在不影响隔离芯片对图像数据信号识别的基础上，可有效降低干扰的幅值，使得干扰信号压差保持在 ADN4651 故障安全机制内，从而避免对后续链路的影响。

#### 5 测试结果

针对优化后的链路进行测试，图 9 为接收数据结果，图中前 3 帧为训练帧，后面为正式数据。数据帧结构完整，帧计数连续无丢帧情况。

经过 50 次的传输测试及数据分析，数据帧计数连续且无丢帧误码情况的出现，结果表明优化后的 LVDS 链路数据传输稳定可靠性强<sup>[12]</sup>。

图 8 优化后接收端电路原理图

| 00 | 01 | 02 | 03 | 04 | 05 | 06 | 07 | 08 | 09 | 0A | 0B | 0C | 0D | 0F | 10 | 12 | 13 | 14 | 15 | 16 | 17 |    |

|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|

| 55 | 55 | AA | AA | BB |    |

| BB |    |

| BB |    |

| BB |    |

| 55 | 55 | AA | AA | BB |    |

| BB |    |

| BB |    |

| BB |    |

| BB |    |

| 55 | 55 | AA | AA | BB |    |

| BB |    |

| BB |    |

| BB |    |

| 55 | 55 | AA | AA | BB |    |

| BB |    |

| BB |    |

| BB |    |

| 55 | 55 | AA | AA | 00 | 02 | 00 | 01 | 00 | 00 | 00 | 01 | 00 | 00 | 00 | 00 | 00 | 01 | A2 | 85 | 00 | 00 |    |

| 00 | 00 | 00 | 00 | 00 | 00 | 00 | 00 | 00 | 00 | 00 | 00 | 00 | 00 | 00 | 00 | 00 | 00 | 00 | 00 | 00 | 00 |    |

| 00 | 00 | 00 | 00 | 00 | 00 | 00 | 00 | 00 | 00 | 00 | 00 | 00 | 00 | 00 | 00 | 00 | 00 | 00 | 00 | 00 | 00 |    |

| 55 | 55 | AA | AA | 00 | 02 | 00 | 02 | 00 | 00 | 00 | 01 | 00 | 00 | 00 | 00 | 00 | 00 | 00 | 00 | 00 | 00 | 00 |

| 00 | 00 | 00 | 00 | 00 | 00 | 00 | 00 | 00 | 00 | 00 | 00 | 00 | 00 | 00 | 00 | 00 | 00 | 00 | 00 | 00 | 00 |    |

| 00 | 00 | 00 | 00 | 00 | 00 | 00 | 00 | 00 | 00 | 00 | 00 | 00 | 00 | 00 | 00 | 00 | 00 | 00 | 00 | 00 | 00 |    |

| 00 | 00 | 00 | 00 | 00 | 00 | 00 | 00 | 00 | 00 | 00 | 00 | 00 | 00 | 00 | 00 | 00 | 00 | 00 | 00 | 00 | 00 |    |

| 55 | 55 | AA | AA | 00 | 03 | 00 | 01 | 00 | 00 | 00 | 01 | 00 | 00 | 55 | 20 | 01 | 00 | 00 | 01 | A2 | 86 | 00 |

图 9 接收数据回放

(下转第 114 页)

- profile linkage[C]//Asia Information Retrieval Symposium.[S. 1.]: Springer International Publishing, 2014: 197–208.

- [5] 王正彬, 沈明玉, 赵皎. 基于节点重构的社交网络的隐私保护技术探讨[J]. 计算机工程与应用, 2017, 53(11): 131–136.

- [6] 仲兆满, 管燕, 胡云, 等. 基于背景和内容的微博用户兴趣挖掘[J]. 软件学报, 2017, 28(2): 278–291.

- [7] 何力, 贾焰, 韩伟红, 等. 基于用户主题模型的微博用户兴趣挖掘(英文)[J]. 中国通信, 2014, 11(8): 131–144.

- [8] 吕志泉, 李昊, 张宗福, 等. 基于主题模型的社交网络匿名用户重识别[J]. 计算机科学, 2019, 46(6): 143–147.

- [9] 金奕江, 孙晓明, 马少平. 因特网上的写作风格鉴别[J]. 广西师范大学学报(自然科学版), 2003, 21(1): 62–66.

- [10] 杨仁凤, 陈端兵, 谢文波. 微博用户兴趣主题抽取方法[J]. 电子科技大学学报, 2018, 47(4): 633–640.

- [11] ZHANG Y, EICK C F. Tracking events in Twitter by combining an LDA-based approach and a density-contour clustering approach[J]. International Journal of Semantic Computing,

- 2019, 13(1): 87–110.

- [12] 邢千里, 刘列, 刘奕群, 等. 微博中用户标签的研究[J]. 软件学报, 2015, 26(7): 1626–1637.

- [13] 格桑多吉, 乔少杰, 韩楠, 等. 基于 Single-Pass 的网络舆情热点发现算法[J]. 电子科技大学学报, 2015, 44(4): 599–604.

- [14] 陈得福. 基于监督学习的写作风格建模方法研究[D]. 杭州: 浙江大学, 2016.

- [15] 吴铮. 跨社交网络用户多重身份识别算法研究[D]. 郑州: 解放军信息工程大学, 2017.

(收稿日期: 2021-03-16)

**作者简介:**

沈佳琪(1995-), 男, 硕士, 主要研究方向: 社会关系网络分析。

周国民(1971-), 男, 硕士, 教授, 主要研究方向: 信息网络安全、信息智能处理、大数据公安信息化应用。

扫码下载电子文档

(上接第 108 页)

**6 结论**

本文设计的可靠性优化方案通过软硬件优化相结合, 解决了 LVDS 传输初始化建链过程中出现的首帧丢失和误建链问题。通过识别帧头、发送训练帧和电气隔离等措施, 能使链路对异常状况的适应性进一步增强。本优化方案中的具体措施对于其他 LVDS 链路具备良好的可移植性和实用性。

**参考文献**

- [1] 乔锐, 翟成瑞, 张彦军. 一种 LVDS 高速数据传输电路[J]. 电子器件, 2021, 44(2): 312–315.

- [2] 鄭玲玲, 文丰, 李辉景. 一种基于 LVDS 高速传输的接口优化设计[J]. 电测与仪表, 2016, 53(20): 80–83.

- [3] 张晋硕. 基于 Camera Link 的图像数据采集装置的研究与实现[D]. 太原: 中北大学, 2020.

- [4] 雷武伟, 文丰, 刘东海, 等. 基于 LVDS 的高可靠性远距离数据传输设计[J]. 电子技术应用, 2019, 45(6): 130–134.

- [5] 董静怡, 庞景月, 彭宇, 等. 集成 LSTM 的航天器遥测数据异常检测方法[J]. 仪器仪表学报, 2019, 40(7): 22–29.

- [6] 方炜, 任勇峰, 储成群, 等. 低电压差分信号远距离通信

电缆参数估计[J]. 科学技术与工程, 2018, 18(19): 209–212.

- [7] 李辉景, 王淑琴, 任勇峰, 等. 基于 CRC 校验的高速长线 LVDS 传输设计[J]. 电子器件, 2015, 38(6): 1346–1351.

- [8] 张波, 李杰, 张海鹏, 等. 基于 FPGA 的 LVDS 传输链路的可靠性设计[J]. 电子器件, 2018, 41(5): 1237–1241.

- [9] 朱泽珲, 任勇峰, 贾兴中. 基于 LVDS 长距离高可靠性传输的优化设计[J]. 电子测量技术, 2020, 43(20): 150–154.

- [10] 文丰, 张宇, 吴瑞华. 基于 4 bit-CRC 反馈网络的高速 LVDS 传输优化设计[J]. 兵器装备工程学报, 2019, 40(9): 108–113.

- [11] 陈晓敏, 薛志超, 张志龙, 等. 低电压差分信号长线传输的优化设计[J]. 电子技术应用, 2020, 46(11): 104–108.

- [12] 李晋涛, 任勇峰, 杨志文, 等. 基于 SATA3.0 的存储系统优化设计[J]. 电子技术应用, 2021, 47(1): 86–90.

(收稿日期: 2021-05-28)

**作者简介:**

杜凯旋(1997-), 男, 硕士研究生, 主要研究方向: 测试计量技术及仪器。

焦新泉(1978-), 男, 博士, 副教授, 主要研究方向: 微纳米器件及测试技术。

扫码下载电子文档

## 版权声明

经作者授权，本论文版权和信息网络传播权归属于《电子技术应用》杂志，凡未经本刊书面同意任何机构、组织和个人不得擅自复印、汇编、翻译和进行信息网络传播。未经本刊书面同意，禁止一切互联网论文资源平台非法上传、收录本论文。

截至目前，本论文已经授权被中国期刊全文数据库（CNKI）、万方数据知识服务平台、中文科技期刊数据库（维普网）、DOAJ、美国《乌利希期刊指南》、JST 日本科技技术振兴机构数据库等数据库全文收录。

对于违反上述禁止行为并违法使用本论文的机构、组织和个人，本刊将采取一切必要法律行动来维护正当权益。

特此声明！

《电子技术应用》编辑部

中国电子信息产业集团有限公司第六研究所