# 0.8~18 GHz 超宽带接收组件设计与实现

王 毅

(中国西南电子技术研究所,四川 成都 610036)

**摘要:**设计了一种应用于无线侦收系统的小型化超宽带接收组件,在有限的体积内集成了两路变频接收通道、两个本振源及一个校准源。采用毫米波高本振的超外差二次变频架构,降低了组合干扰抑制的难度。基于一系列多功能芯片进行电路的小型化设计,腔体正面微波电路和反面控制电路通过通孔进行互联,有效减小了组件厚度和横向尺寸。利用内部校准源产生信号,通过ADC采集DLVA电压进而调节数控衰减器的方式,可优化双通道增益及一致性等指标,基本可以做到免调试,提高了批生产效率。

**关键词:**超宽带;变频接收;小型化;自校准

中图分类号: TN851.4

文献标识码: A

DOI: 10.16157/j.issn.0258-7998.212007

中文引用格式: 王毅. 0.8~18 GHz 超宽带接收组件设计与实现[J]. 电子技术应用, 2022, 48(1): 146~151, 156.

英文引用格式: Wang Yi. Design and implementation of a 0.8~18 GHz ultra-wideband receiver module[J]. Application of Electronic Technique, 2022, 48(1): 146~151, 156.

## Design and implementation of a 0.8~18 GHz ultra-wideband receiver module

Wang Yi

(Southwest China Institute of Electronic Technology, Chengdu 610036, China)

**Abstract:** A miniaturized ultra-wideband receiver module is designed for electronic reconnaissance system in this paper. The receiver module contains two down-converter receiving channels, two LO synthesizers and a self-checking circuit in limited area. The module is of superheterodyne with twice frequency conversion by millimeter wave local oscillator, and the miniaturized circuits based on a series of multi-function MMICs are designed. To reduce the thickness and lateral dimensions, the through holes between microwave circuits and control circuits are adopted for interconnection. To realize self-calibration function, self-calibration synthesizer generates a signal, and then the ADC collects the voltage of DLVA, finally the gain and the consistence of two receiving channel are optimized based on adjusting the digital attenuators. Through above steps, the receiver module is easily manufactured, thus batch production efficiency is improved.

**Key words:** ultra-wideband; receiver; miniaturization; self-calibration

## 0 引言

超宽带接收机主要应用于电子对抗领域中,特别是雷达对抗领域<sup>[1]</sup>。为了能侦收敌方的信息,需要接收的频段尽可能宽,因此侦察雷达往往需要接收机能跨倍频程工作<sup>[2]</sup>。作为超宽带接收机的核心组成部分,超宽带接收组件需要将从天线接收到的射频信号变频至中频信号。随着系统复杂度的提高<sup>[3~4]</sup>,一方面超宽带接收组件需要具有超宽带、大动态、高灵敏度等性能<sup>[5~6]</sup>,另一方面还需要具备小型化、轻量化和通用化等特点<sup>[7~8]</sup>。

传统的超宽带组件在电路实现时将0.8 GHz~18 GHz的频带划分为若干个子频带(如0.8 GHz~6 GHz、6 GHz~18 GHz)来分别进行预选滤波和变频,滤波器组合占用面积大,频综种类多,不利于实现组件的小型化。目前超宽带组件实现小型化的方式主要有采用LTCC技术<sup>[9]</sup>、HTCC技术<sup>[10]</sup>及微波多层板技术<sup>[11]</sup>,前两者存在成本和

工艺问题,后者存在复杂的叠层设计和散热问题。本文在综合考虑性能、工艺和成本因素后,提出了一种超宽带接收组件小型化设计方案,并进行了加工验证。

### 1 超宽带接收组件技术要求

超宽带接收组件的典型技术指标如下文所示。

#### 1.1 通道指标

- (1)通道数:2路;

- (2)输入信号频率:0.8~18 GHz;

- (3)输出信号频率和带宽:1.8 GHz@1 GHz;

- (4)输入输出驻波比: $\leq 2$ ;

- (5)通道总增益: $60 \text{ dB} \pm 2 \text{ dB}$ ;

- (6)输出 $P_{-1}$ : $\geq 5 \text{ dBm}$ ;

- (7)功率调整范围: $\geq 75 \text{ dB}$ ;

- (8)噪声系数: $\leq 9 \text{ dB}$ ;

- (9)杂散抑制: $\geq 45 \text{ dBc}$ ;

(10)通道间幅度一致性： $\leq \pm 2$  dB。

## 1.2 频率源指标

频率源包括为接收通道提供本振信号的一、二本振及用于自校准的本振源，除输出频率不同外，其余技术指标均相同，如下所示：

- (1)控制步进：10 MHz；

- (2)频率误差： $\leq \pm 0.2$  MHz；

- (3)输出功率：0 dBm~5 dBm；

- (4)相位噪声：10 kHz、100 kHz 处不大于  $-80$  dBc/Hz；

- (5)杂散抑制： $\geq 50$  dBc；

- (6)跳频响应时间： $\leq 25$   $\mu$ s。

## 2 超宽带接收组件电路设计

### 2.1 电路方案设计

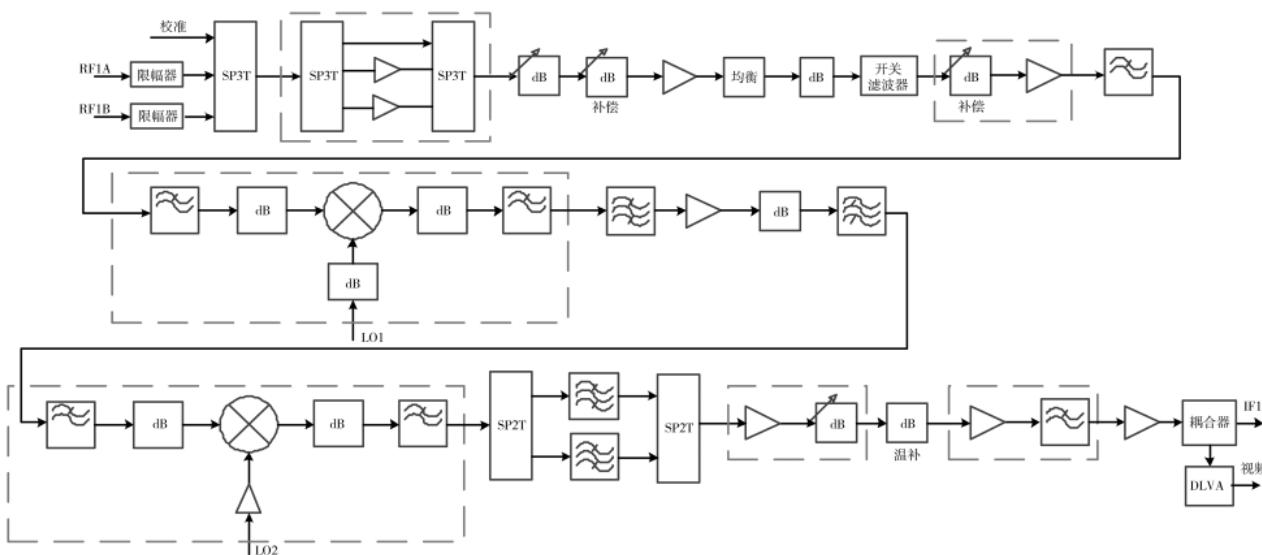

由于本设计中射频接收为超宽带接收，中频频率为1.8 GHz 的较低频率，要求增益高、杂散抑制高且噪声系数低，因而采用超外差式二次变频结构较易实现。传统的超宽带接收组件采用较低的本振信号与接收射频信号进行混频<sup>[12]</sup>，由于本振信号频率与射频信号频率间隔较近，低阶组合干扰容易混入中频带内而难以通过滤波器滤除。本设计采用毫米波高本振信号进行两次混频，单个接收通道的具体功能框图如图1所示。全频带射频信号统一与宽带一本振信号 22.8 GHz~40 GHz 进行第一次混频，电路结构相对简单，宽带设计压力较小。一中频信号 22 GHz $\pm 0.5$  GHz 与二本振信号 20.2 GHz 进行第二次混频，得到 1.8 GHz $\pm 0.5$  GHz 的中频信号然后输出至信号处理模块。

预选滤波器频段划分如表1 所示，每一段均为亚倍频程滤波，利于滤除自身谐波，从而减小组合干扰。传统的开关滤波器采用分离的滤波器单元组合而成，不利于实现组件的小型化。本文采用定制的开关滤波器单片电路来实现，其体积仅为 3.5 mm $\times$ 5 mm $\times$ 0.1 mm，带外抑制度为 25 dB，可采用两级开关滤波器来实现更好的抑制

效果。

### 2.2 关键指标分析

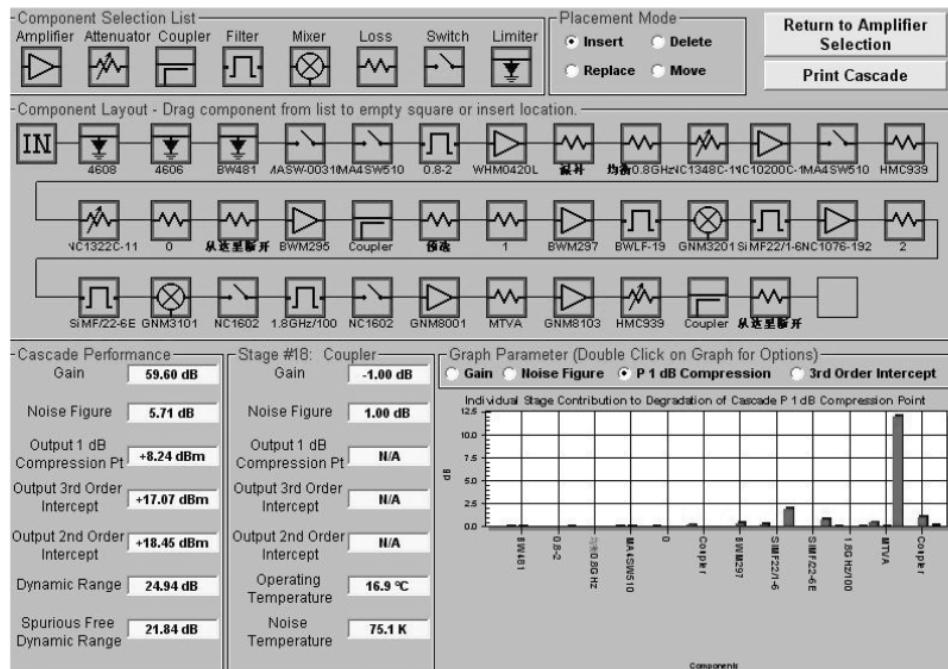

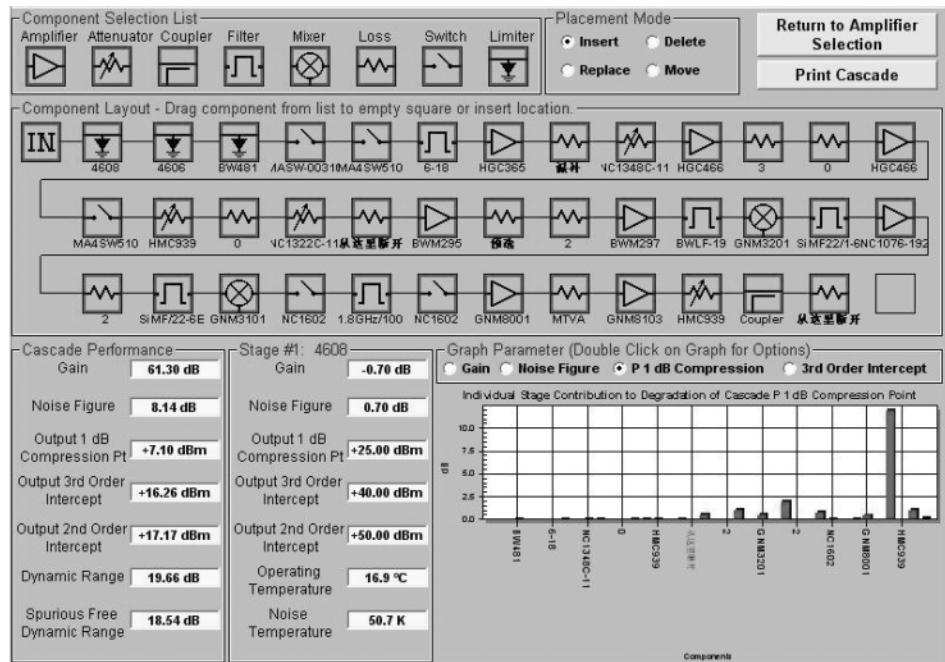

对于超宽带接收组件，全频带的增益平坦度、噪声系数和杂散抑制为最难实现的指标，直接影响系统的使用性能，因此需着重考虑。采用 Cascade 软件对链路进行仿真分析，选择射频信号范围的最低频率 0.8 GHz 和最高频率 18 GHz 为典型值

表 1 预选滤波器

频段划分

(GHz)

| 序号 | 预选滤波器频率 |

|----|---------|

| 1  | 0.8~1.4 |

| 2  | 1.2~2.2 |

| 3  | 2~3.5   |

| 4  | 3~5     |

| 5  | 4.5~7.5 |

| 6  | 7~11.5  |

| 7  | 11~18   |

来进行仿真，得到链路指标分别如图2 和图3 所示。图中左侧第一列数据为链路级联指标，第二列数据为选中的某一级器件指标。利用仿真结果可对链路的增益、噪声系数、输出  $P_{-1}$  等指标进行分析。

#### 2.2.1 噪声系数分析

由噪声系数级联公式可知，链路前几级器件的噪声特性决定了总的噪声系数。射频信号输入端除了必不可少的限幅器和开关，第三级器件为一开关低噪放多功能芯片，用来实现大动态范围和低噪声输出功能的灵活切换。大信号输入时，多功能芯片切换为直通通道工作；小信号输入时，切换为低噪放通道工作，从而保证了通道具有较低的噪声系数。由图2 和图3 的仿真结果可知，接收组件的噪声系数不大于 8.1 dB，满足指标要求。

#### 2.2.2 增益及增益调节分析

本设计选用具有良好宽带频响特性的限幅器、开关、低噪放和混频器等器件，同时在关键器件间放置可调衰减片、宽带均衡器和温补衰减器，来保证链路具有良好的增益平坦度和温度稳定性。由图2 和图3 的仿真结果可知，接收组件增益为 59.6 dB~61.3 dB，满足增益指标要求。

在射频链路上设置三级数控衰减器来实现不低于

图 1 单个接收通道功能框图

图 2 0.8 GHz 链路仿真结果

图 3 18 GHz 链路仿真结果

75 dB 的功率调整功能, 数控衰减量分别为 20 dB、31 dB、35 dB, 总衰减量为 86 dB, 满足增益调节指标要求。

### 2.2.3 杂散抑制分析

变频组件中最主要的杂散来源为组合干扰。第一次混频后的一中频为 22 GHz, 带宽为 1 GHz, 因此射频信号按 1 GHz 带宽逐次分析, 本振频率设置为射频频段中心频点对应的本振。根据链路混频关系, 可计算出每次混频时落入中频带内的组合干扰如表 2、表 3 所示。

由以上分析结果可知,第一次混频时,在 $f_{IF1} \pm 500$  MHz

带内有 $-2f_{RF}+f_{LO}$  和  $2f_{RF}$  的混频组合干扰信号, 第二次混频带内没有组合干扰信号出现。

混频器输出带内杂散无法通过滤波器滤除，只能靠混频器本身对组合信号产生抑制。第一次变频选用的混频器对  $-2f_{RF} + f_{LO}$ 、 $2f_{RF}$  组合干扰信号抑制达 50 dBc 以上，因此预计杂散抑制可以满足指标要求。

## 2.3 频率源设计

### 2.3.1 本振源设计

二本振为 20.2 GHz 固定本振,采用定制的微封装锁

表 2 第一次混频杂散信号

| 频段编号 | 射频频率/GHz | 本振频率/GHz | 杂散   |

|------|----------|----------|------|

| 1    | 0.8~1.4  | 23.1     | -2×1 |

| 2    | 1.2~2.2  | 23.7     | 无    |

| 3    | 2~3      | 24.5     | 无    |

|      | 3~3.5    | 25.25    | 无    |

| 4    | 3~4      | 25.5     | 无    |

|      | 4~5      | 26.5     | 无    |

|      | 4.5~5.5  | 27       | 无    |

| 5    | 5.5~6.5  | 28       | 无    |

|      | 6.5~7.5  | 29       | 无    |

|      | 7~8      | 29.5     | 无    |

|      | 8~9      | 30.5     | 无    |

| 6    | 9~10     | 31.5     | 无    |

|      | 10~11    | 32.5     | 2×0  |

|      | 11~11.5  | 33.25    | 2×0  |

|      | 11~12    | 33.5     | 2×0  |

|      | 12~13    | 34.5     | 无    |

|      | 13~14    | 35.5     | 无    |

| 7    | 14~15    | 36.5     | 无    |

|      | 15~16    | 37.5     | 无    |

|      | 16~17    | 38.5     | 无    |

|      | 17~18    | 39.5     | 无    |

注:x前为射频频率阶数,x后为本振频率阶数。

表 3 第二次混频杂散信号

| 射频频率/GHz | 本振频率/GHz | 杂散( $f_0 \pm 500$ MHz) |

|----------|----------|------------------------|

| 22±0.5   | 20.2     | 无                      |

相源,5 V 单电源供电,其外形尺寸仅为 15 mm×12 mm×3.1 mm。

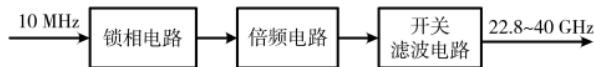

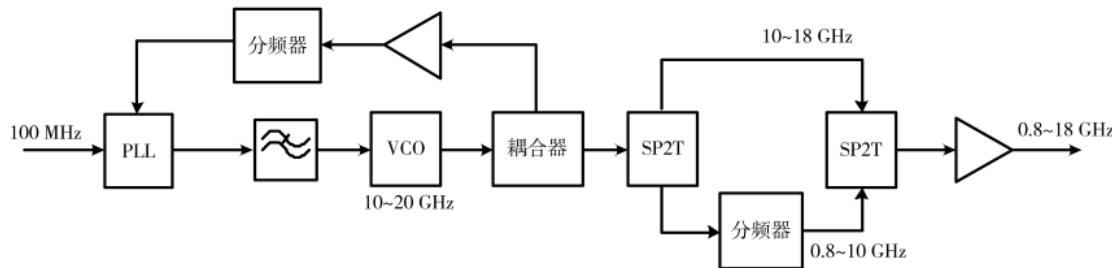

一本振为毫米波高本振,其原理框图如图 4 所示,采用锁相源+倍频电路+开关滤波放大电路的方式实现。

图 4 一本振原理框图

### 2.3.2 校准源设计

锁相环对 100 MHz 参考信号和 VCO 的分频信号进行鉴相,环路锁定后,VCO 可以输出稳定的 10 GHz~20 GHz 信号,然后通过开关进行直通输出或分频输出就可得到 0.8 GHz~18 GHz 的宽带校准信号,其原理框图如图 5

图 5 校准源原理框图

所示。

### 2.4 电路自校准功能设计

本设计利用 ADC 对末级处的 DLVA 输出电压进行采集,进而计算出不同频点处的链路增益,然后控制射频链路上预留的大步进和小步进数控衰减器,可有效改善增益平坦度以及两通道间的幅度一致性。

链路射频输入端设计了 SP3T 开关,可根据用户需求选择外置信号源或内置自检源进行自校准,校准完成后将数控衰减码值进行存储,每次上电进行调用即可。通过该功能的设计,接收组件基本可以做到免调试,具备良好的批生产性。

### 2.5 电路小型化设计

该超宽带接收组件需要在有限的体积内集成 2 通道接收电路、2 个本振源、自检源、100 MHz 晶振以及数字采集及控制电路等。组件的腔体正面为微波电路,腔体反面为两层控制电路。第一层控制电路包含开关驱动器、电源变换和分配、晶振功分等功能电路。该层电路通过腔体上的通孔与微波电路进行互联,实现控制和供电,摒弃了双面互联必需的玻璃绝缘子,可有效减小腔体的厚度及横向尺寸。第二层控制电路包含主控 FPGA 及其外围电路,与第一层控制电路采用柔性电路板进行连接。

射频连接器采用 SSMP,低频连接器采用 J55A 超小型矩形连接器;链路上采用了较多的多功能芯片,包括开关滤波器、数控衰减低噪放芯片、滤波衰减混频芯片等,混频后的中频滤波器均选用 MEMS 或 MMIC 滤波器,从而实现电路的高集成和小型化设计。

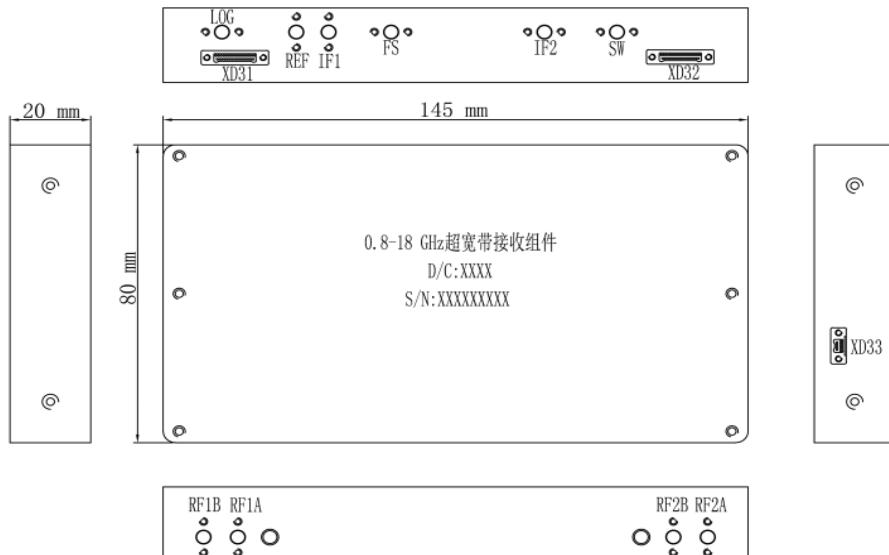

该组件外形如图 6 所示,组件尺寸为 145 mm×80 mm×20 mm。

### 3 实验结果与讨论

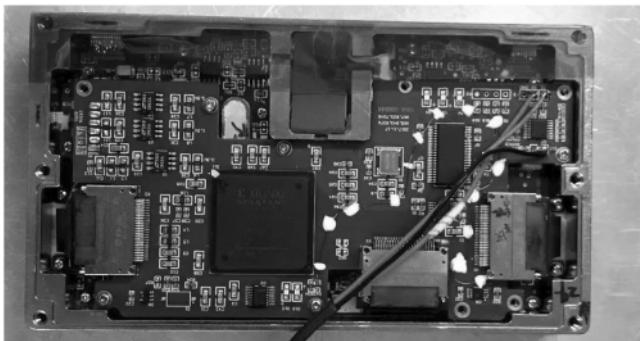

组装完成后的实物如图 7 所示。

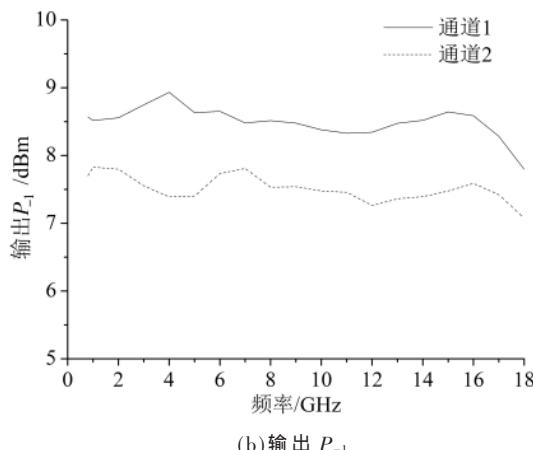

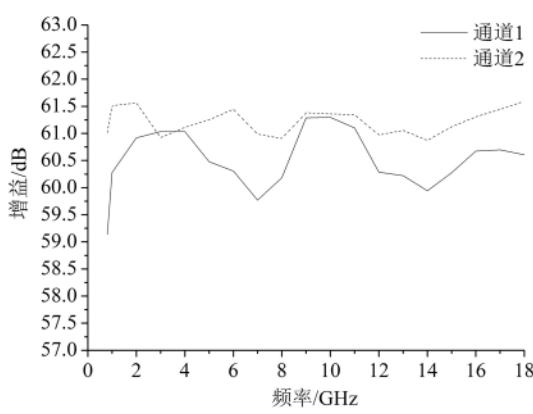

接收组件各频点增益和输出  $P_{-1}$  测试结果分别如图 8(a)和图 8(b)所示,增益范围为 59.1 dB~61.6 dB,输出  $P_{-1}$  范围为 7.1 dBm~8.9 dBm。

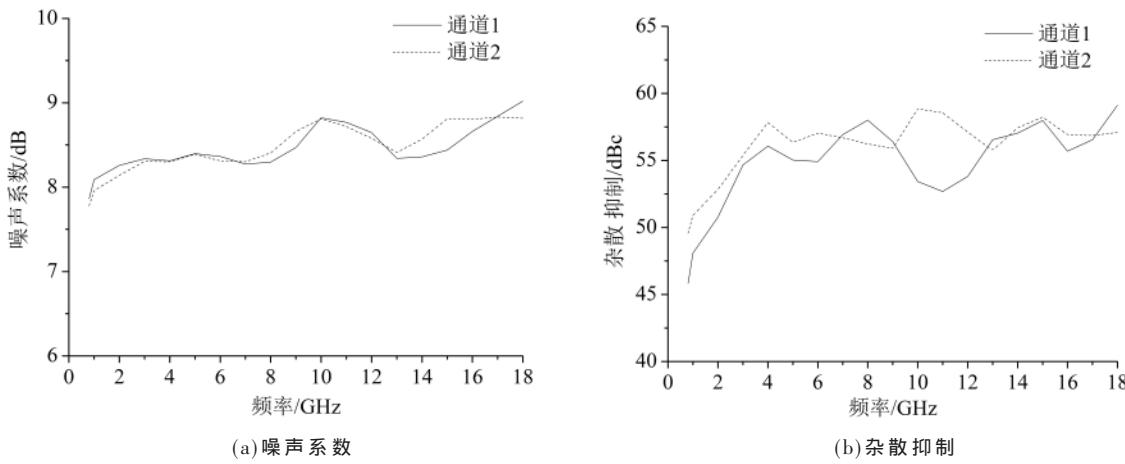

接收组件各频点噪声系数和杂散抑制测试结果分别如图 9(a)和图 9(b)所示,噪声系数不大于 8.9 dB,杂散抑制大于 46 dBc。

所有主要技术指标测试结果汇总于表 4,各项指标均达到了预定设计要求。

图 6 接收组件外形图

图 7 接收组件实物照片

#### 4 结论

本文讨论了超宽带接收组件进行小型化设计的问题,综合考虑性能和成本等因素,基于毫米波高本振的二次变频超外差架构,采用高集成度的开关滤波器等多功能芯片,实现了频率覆盖0.8 GHz~18 GHz的小型化超宽带接收组件,主要性能指标满足要求。

表 4 主要技术指标测试结果及符合性

| 指标项              | 要求值     | 实测值       | 符合性 |

|------------------|---------|-----------|-----|

| 通道数              | 2       | 2         | 满足  |

| 输入信号频率/GHz       | 0.8~18  | 0.8~18    | 满足  |

| 输出信号频率和带宽/GHz    | 1.8±0.5 | 1.8±0.5   | 满足  |

| 输入输出驻波比          | ≤2      | 1.85      | 满足  |

| 增益/dB            | 60±2    | 59.1~61.6 | 满足  |

| 输出 $P_{-1}$ /dBm | ≥5      | 7.1       | 满足  |

| 功率调整范围/dB        | ≥75     | 83        | 满足  |

| 噪声系数/dB          | ≤9      | 8.9       | 满足  |

| 杂散抑制/dBc         | ≥45     | 46        | 满足  |

| 通道间幅度一致性/dB      | ≤±2     | ±1.8      | 满足  |

该小型化超宽带接收组件与已发表的同类型组件相比,内部除了集成了两个独立接收通道,还包含变频所需的本振源、校准源和自校准采集电路。利用内部校准源产生信号,通过ADC采集DLVA电压进而调节数控衰减器的方式,优化双通道增益及一致性指标,基本可以做到免调试,提高了生产效率。

图 8 增益和输出  $P_{-1}$  测试结果

图 9 噪声系数和杂散抑制测试结果

## 参考文献

[1] 余高干.0.4~18 GHz 超宽带雷达接收前端小型化的研究[D].成都:电子科技大学,2015.

[2] 卢建平.超宽带大动态雷达接收机设计[D].西安:西安电

(上接第 141 页)

[7] 秦文奕.单馈点宽带圆极化微带天线设计[J].通信技术,2013(8):34~36.

[8] FU S, KONG Q, FA N S, et al. Broadband circularly polarized microstrip antenna with coplanar parasitic ring slot patch for L-band satellite system application[J]. IEEE Antennas & Wireless Propagation Letters, 2014, 13: 943~946.

[9] BABAKHANI B, SHARMA S K. Wideband circularly polarized fan-shaped antenna on a HIS structure[C]//2016 IEEE International Symposium on Antennas and Propagation & USNC/URSI National Radio Science Meeting. IEEE, 2016.

[10] Nasimuddin, QING X. A wideband high gain circularly polarized antenna for satellite applications[C]//2019 IEEE

(上接第 145 页)

[8] 戴新峰,郁元卫,贾世星,等.Ka 波段 Si 基微机械宽带垂直过渡[J].微纳电子技术,2008,45(12):712~715.

[9] 王辉.Ka 波段微带到带状线垂直互联技术研究[C]//全国天线年会论文集(上册),2017.中国电子学会,2017.

[10] 王勇,韦炜,杨栋,等.基于硅转接板工艺的宽带射频芯片三维异构集成[J].东南大学学报(英文版),2021,37(1):8~13.

[11] 罗江波.高性能硅转接板的系统设计及集成制造方法研究[D].上海:上海交通大学,2019.

[12] LIN Y J, KANG C, CHUA L, et al. Advanced 3D eWLB-PoP(embedded wafer level ball grid array-package on package) technology[C]//Proceedings of the 66th Electronic Components and Technology Conference. Las Vegas, NV, USA, 2016: 1772~1777.

子科技大学,2009.

[3] 刘民伟.10 MHz~12 GHz 超宽带接收机的设计与实现[D].成都:电子科技大学,2013.

(下转第 156 页)

Asia-Pacific Microwave Conference(APMC).IEEE, 2019.

[11] 许碧惠.超材料电磁特性分析及其在平面宽带天线中的应用[D].成都:电子科技大学,2020.

[12] 秦开元.宽带高增益圆极化天线设计[D].泉州:华侨大学,2018.

(收稿日期:2021-09-24)

## 作者简介:

隋涛(1994-),通信作者,男,硕士,工程师,主要研究方向:卫星数据传输无线系统设计,E-mail:suitao214@163.com。

邢斯瑞(1987-),男,硕士,研究员,主要研究方向:卫星通信系统设计。

孙伟(1989-),男,硕士,助理研究员,主要研究方向:卫星通信系统设计。

扫码下载电子文档

[13] LEE J Y, LEE S K, PARK J H. Fabrication of void-free copper filled through-glass-via for wafer-level RF MEMS packaging[J]. Electronics Letters, 2012, 48(17): 1076~1077.

[14] 王清源,吴洪江,赵宇,等.一种基于 MEMS 体硅工艺的三维集成 T/R 模块[J].半导体技术,2021,46(4):300~304,336.

(收稿日期:2021-06-30)

## 作者简介:

游月娟(1998-),女,硕士研究生,主要研究方向:射频微系统与先进封装技术。

刘德喜(1973-),男,硕士,研究员,主要研究方向:微波毫米波电路设计。

刘亚威(1986-),男,博士,高级工程师,主要研究方向:微波毫米波电路设计、微系统及先进工艺研发。

扫码下载电子文档

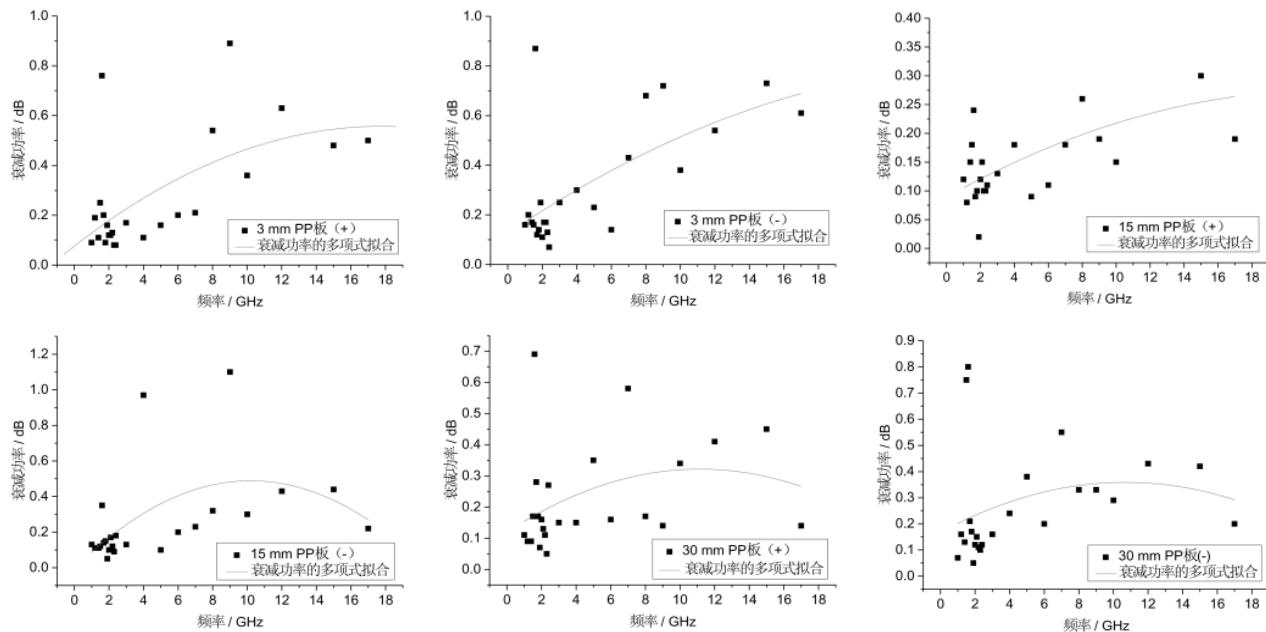

图 6 不同频率下 PP 板电磁波衰减量

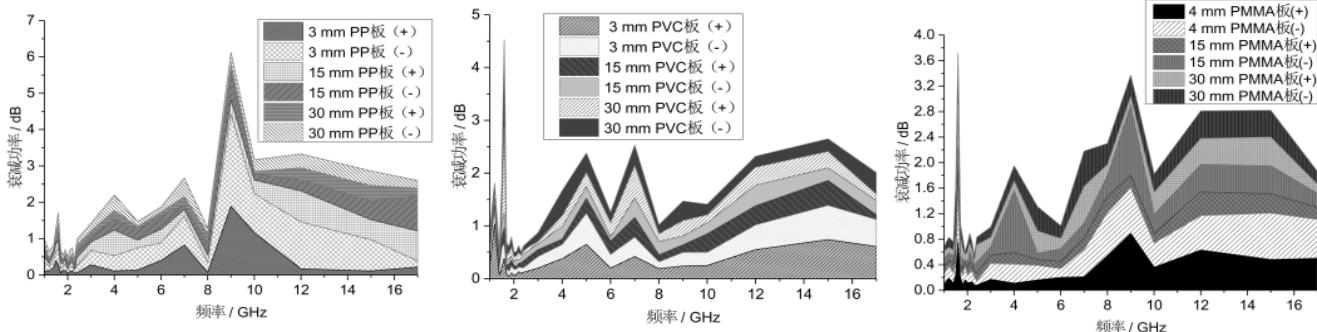

图 7 不同材料下带电介质板电磁波衰减量

[13] 法林, CASTAGNA J P, 董和风.一种计算反射/传输系数的快速精确算法[J].中国科学:G辑, 2008, 38(7): 873–895.

(收稿日期: 2021-06-16)

#### 作者简介:

张超(1988-), 通信作者, 男, 本科, 工程师, 主要研究方

(上接第 151 页)

- [4] 周泽伦, 李祎. 2~18 GHz 超宽带接收分系统的设计[J]. 微波学报, 2016, 39(14): 116–119.

- [5] 何俊岑, 候智鹏, 周俊. 基于 LTCC 的小型化宽带变频组件[J]. 电子信息对抗技术, 2015, 30(3): 59–62.

- [6] 周凤艳, 刘秉策. 一种 6~18 GHz 宽带接收前端的设计[J]. 雷达科学与技术, 2015, 13(1): 95–98.

- [7] 庞玉会. 一种 X 波段小型化上下变频组件的研制[J]. 现代电子技术, 2012, 35(23): 101–104.

- [8] 苟民. 超宽带接收前端的设计与实现[J]. 火控雷达技术, 2017, 46(3): 55–58.

- [9] 苏明慧, 杜二旺, 姜立伟. 基于 LTCC 的星载 S 频段上变

向: 电磁环境模拟与测试、电学热学测量,

E-mail: zhoushuafei@163.com。

孔晓玉(1987-), 女, 本科, 工程师, 主要研究方向: 电学热学测试。

郑丹丹(1990-), 女, 本科, 工程师, 主要研究方向: 电学热学测试。

扫码下载电子文档

- 频器[J]. 微波学报, 2016, 32(3): 93–96.

- [10] 傅显慧. 2~18 GHz 接收前端关键技术研究[D]. 北京: 中国运载火箭技术研究院, 2020.

- [11] 李镇, 杨燕, 吴国中, 等. 2~18 GHz 超宽带小型化下变频通道设计[J]. 微波学报, 2020, 36(4): 78–81.

- [12] 唐霆宇. 一种小型化超宽带接收前端的设计与实现[J]. 电子技术应用, 2019, 45(6): 11–14.

(收稿日期: 2021-08-04)

#### 作者简介:

王毅(1988-), 男, 硕士, 工程师, 主要研究方向: 射频微波电路与系统、航天测控系统中的信道设计。

扫码下载电子文档

## 版权声明

经作者授权，本论文版权和信息网络传播权归属于《电子技术应用》杂志，凡未经本刊书面同意任何机构、组织和个人不得擅自复印、汇编、翻译和进行信息网络传播。未经本刊书面同意，禁止一切互联网论文资源平台非法上传、收录本论文。

截至目前，本论文已经授权被中国期刊全文数据库（CNKI）、万方数据知识服务平台、中文科技期刊数据库（维普网）、DOAJ、美国《乌利希期刊指南》、JST 日本科技技术振兴机构数据库等数据库全文收录。

对于违反上述禁止行为并违法使用本论文的机构、组织和个人，本刊将采取一切必要法律行动来维护正当权益。

特此声明！

《电子技术应用》编辑部

中国电子信息产业集团有限公司第六研究所