# 一种高速施密特触发器的设计

孙建民<sup>1</sup>,闫江<sup>1,2</sup>,张龙<sup>3</sup>,赵以诚<sup>3</sup>

(1.贵州大学 大数据与信息工程学院,贵州 贵阳 550025;

2.北方工业大学 信息学院,北京 100144;3.北京中科格励微科技有限公司,北京 100089)

**摘要:**在数字隔离器系统中,因为存在电路寄生效应和随机噪声,数字信号的波形会发生严重畸变。针对该问题,提出了一种电压—电流模式高速施密特触发器,该电路能有效还原信号的波形。电路主体结构采用电流放大器和跨导运算放大器相结合,在输入高速数据时,电流放大器提供了快速的前馈通路来增加比较器的响应速度,实现施密特触发器的高速翻转。设计采用 GF\_0.18  $\mu$ m\_BCD 工艺,在电源电压 5 V 的条件下,可实现 500 MHz 高速信号的整形,信号的传输延时为 652 ps。

**关键词:**施密特触发器;跨导运算放大器;电流放大器

中图分类号: TN409

文献标识码: A

DOI:10.16157/j.issn.0258-7998.211856

中文引用格式: 孙建民,闫江,张龙,等. 一种高速施密特触发器的设计[J]. 电子技术应用, 2022, 48(2): 28-31.

英文引用格式: Sun Jianmin, Yan Jiang, Zhang Long, et al. Design of a high-speed Schmitt trigger[J]. Application of Electronic Technique, 2022, 48(2): 28-31.

## Design of a high-speed Schmitt trigger

Sun Jianmin<sup>1</sup>, Yan Jiang<sup>2</sup>, Zhang Long<sup>3</sup>, Zhao Yicheng<sup>3</sup>

(1.School of Big Data and Information Engineering, Guizhou University, Guiyang 550025, China;

2.School of Information, North China University of Technology, Beijing 100144, China;

3.Beijing Zhongke Greenway Technology Co., Ltd., Beijing 100089, China)

**Abstract:** In the digital isolator system, due to the existence of circuit parasitics and random noise, the waveform of the digital signal will be severely distorted. Aiming at this problem, a voltage-current mode high-speed Schmitt trigger is proposed, which can effectively restore the signal waveform. The main structure of the circuit uses a combination of a current amplifier and a transconductance operational amplifier. When inputting high-speed data, the current amplifier provides a fast feedforward path to increase the response speed of the comparator and realize the high-speed flip of the Schmitt trigger. This design adopts the GF\_0.18  $\mu$ m\_BCD process, under the condition of the power supply voltage of 5 V, it can realize the shaping of the 500 MHz high-speed signal, the transmission delay of the signal is 652 ps.

**Key words:** Schmitt trigger; transconductance operational amplifier; current amplifier

## 0 引言

在数字系统中,矩形脉冲信号经过传输后往往会发生畸变,因为信号在传输过程中会受到许多非理想因素的影响,如在 PCB 板的寄生效应、封装过程的寄生电容电感、传输线上的寄生电容、接收端的阻抗不匹配以及其他信号线的噪声干扰等。这些不利因素会使信号的上升下降沿明显变缓,有时还会在信号的上升下降沿附近产生振荡,所以在数字系统中通常需要给输入信号进行滤波整形,以还原信号的完整性。施密特触发器是脉冲波形变换最常使用的一种电路,因为其在性能上有两个重要的特点:一是输入信号上升和下降过程中电路状态转换的阈值不同;二是电路内部存在正反馈过程使输出波形边沿变得很陡。利用这两个特点不

仅可以加快信号边沿的变化,还可以有效地滤除叠加在脉冲信号上的噪声<sup>[1-2]</sup>。

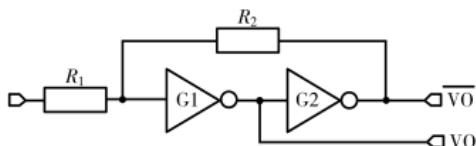

传统的施密特触发器如图 1<sup>[3]</sup>所示,由 CMOS 反向器和 TTL 门电路构成,基本结构是将两级反相器串接,通过电阻分压将输出端的电压反馈到输入端,通过改变分压电阻的比值可以调节阈值电压和滞回区间,电路结构简单,但是性能较差。

随着集成电路的发展,传统的施密特触发器不能满足数字系统高集成度、高可靠性、低延迟、低功耗的要求。文献[4]、文献[5]提出了基于电流模式的施密特触发器,采用差分跨导放大器模块,具有输入阻抗高、运算精度高的优点,适用于各种电流模式模拟信号处理应用,但不适用于大规模的数字系统。文献[4]提出了一种迟

图 1 传统施密特触发器

滞可调节的高速低压施密特触发器，通过体偏置电压的变化来调节阈值电压，与传统的结构相比，该结构具有可独立控制上升下降阈值电压的优点，但是该结构的传输延时受负载的影响较大，通用性较差<sup>[3-5]</sup>。

在数字隔离器系统中，信号与通道的匹配度和信号的传输延时是影响电路性能的重要因素，所以在电路设计时需要保证每个信号通道的翻转阈值完全一致，传输延时尽可能小，同时还需要考虑输入信号与供电电压的兼容性问题。基于以上考虑，本文提出一种电压—电流模式的高速比较器作为施密特触发器，以实现信号高速传输的功能。

## 1 高速施密特触发器的整体架构

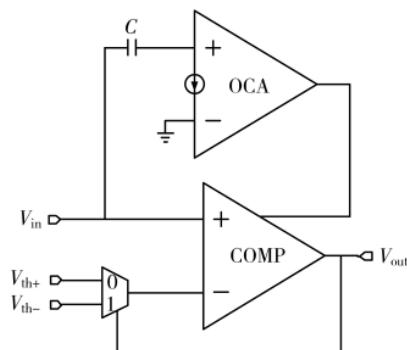

本文提出的高速施密特触发器整体结构如图 2 所示。 $V_{in}$  为输入信号， $V_{out}$  为输出信号， $V_{th+}$  和  $V_{th-}$  分别为上升和下降阈值电压基准。电流放大器(OCA)为比较器的翻转提供快速前馈通路以增加比较器的响应速度。电压比较器(COMP)采用差分式输入推挽式输出的跨导运算

图 2 高速施密特触发器结构框图

放大器(OTA)，这是一种能够将输入的微小电压差信号放大为较大输出电流信号的结构，这种结构内部没有高阻节点，有较快的响应速度<sup>[6-9]</sup>。

图 2 所示电路的具体工作过程如下：当输入电压变化时，电容  $C$  和电阻  $R$  将输入信号的变化转化为电流放大器的输入，即前馈电流。当输入电压从低到高变化时，前馈电路为比较器的翻转提供较大的灌电流，加速了比较器的翻转。比较器发生翻转后， $V_{out}$  将信号反馈给阈值基准端，阈值基准切换为下降阈值  $V_{th-}$ 。当输入信号从高到低变化时，前馈电路为比较器的翻转提供较大的拉电流，加速了比较器的翻转。比较器发生翻转后，阈值基准切换为上升阈值  $V_{th+}$ 。

## 2 高速施密特触发器的电路设计

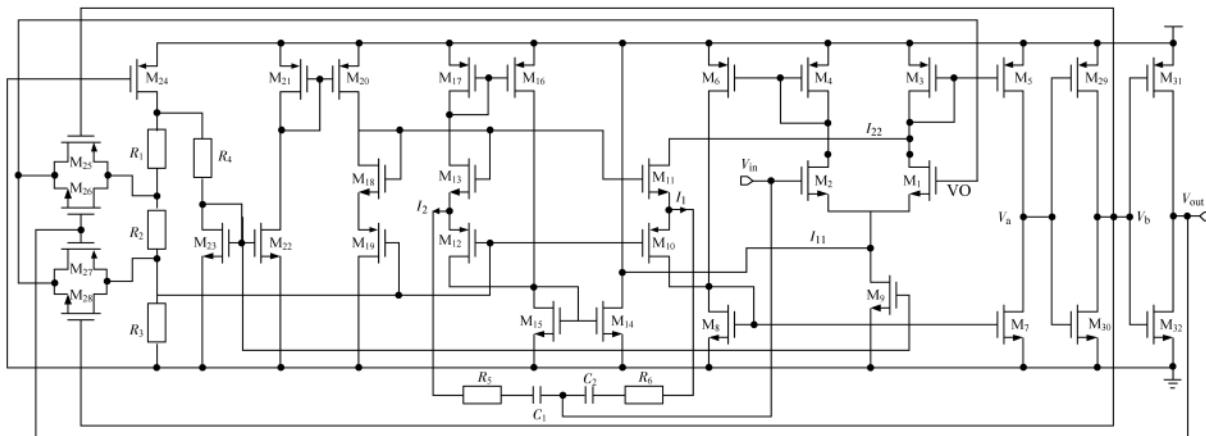

本文设计的高速施密特触发器如图 3 所示。具体工作原理如下。

当  $V_{in}$  信号为低电平时，电路输出  $V_{out}$  为高电平，M25、M26 组成的传输门电路导通，阈值电压基准电路的输出  $V_0$  为  $V_{th+}$ ，连接跨导运算放大器的同相输入端。当输入电压  $V_{in}$  从低到高变化时，电容  $C_1$ 、 $C_2$  将  $V_{in}$  的变化转化为 M10、M12 的源端电流，作为电流放大器的输入电流。当  $V_{in}$  上升到  $V_{th+}$  时，OCA 输出电流达到最大值，为比较器的翻转瞬间提供了较大的下拉电流，加速了比较器的翻转。当比较器发生翻转，M25、M26 构成的传输门关断，M27、M28 构成的传输门导通，此时阈值电压切换为  $V_{th-}$ ；同理当  $V_{in}$  从高到低变化时，发生与上述相反过程。

M1~M8 组成了跨导运算放大器(OTA)。与传统的电压比较器相比，跨导运算放大器具有结构简单、高频特性好的优点<sup>[8]</sup>。M1、M2 构成的差分输入端为电压电流转换级而非电压增压级，所以 OTA 没有大摆幅电压信号和米勒电容效应，因此在使用时不需要进行频率补偿就有较好的频率特性<sup>[8]</sup>。M3~M8 为电流镜结构，电流传输比值决定了电流的放大倍数，OTA 增益表达式为：

$$A_v = G_m \cdot R_{out} \quad (1)$$

其中  $G_m$  为 OTA 的等效跨导， $R_{out}$  为等效输出电阻。

图 3 高速施密特触发器电路结构

$$G_m = M \cdot g_m = \frac{MI_B}{(V_{GS2} - V_{THN})} \quad (2)$$

$$R_{out} = r_{o7} / r_{o8} = \frac{2}{MI_B(\lambda_7 + \lambda_8)} \quad (3)$$

其中  $M$  为电流镜 M3、M5 的电流传输比,  $I_B$  为流过 M9 的偏置尾电流,  $\lambda_i$  为第  $i$  个晶体管的沟道调制系数。增大电流传输比  $M$  和尾电流的大小  $I_B$  可以增大输出电流, 但是会降低电路的稳定性并增加电路的功耗。本文采用 OTA 与电流放大器相结合的结构, 在保持  $M$  不变的情况下增大电路的等效跨导, 以加快 OTA 输出的瞬态响应速度<sup>[7-9]</sup>。

M10~M13 和电容  $C_1 \sim C_2$ 、电阻  $R_5 \sim R_6$  构成电流放大器作为 OTA 的前馈通路。电容  $C_1$ 、 $C_2$  和电阻  $R_5$ 、 $R_6$  将输入电压的变化转化为电路放大器的输入电流  $I_1$ 、 $I_2$ , 经过 M3、M5 电流放大器的输出电流  $I_{11}$  流入比较器的尾电流, 为比较器的翻转提供尾电流, 加快比较速度。经过 M16、M17 电流放大器输出电流  $I_{22}$  流入比较器的输出级, 加快了比较器的翻转速度。

M25~M28 组成两组传输门, 通过电压  $V_{out}$ 、 $V_b$  来控制传输门的输出电压  $V_0$ , 当  $V_{out}$  为高电平,  $V_b$  为低电平时,  $V_0$  输出值为  $V_{th+}$ ;  $V_{out}$  为低电平,  $V_b$  为高电平时,  $V_0$  输出值为  $V_{th-}$ 。 $V_{th+}$  和  $V_{th-}$  通过电阻  $R_1$ 、 $R_2$ 、 $R_3$  分压产生, 通过调节电阻阻值可以改变电压阈值和滞回区间<sup>[10-15]</sup>。

$$V_{th+} = \frac{R_2 + R_3}{R_1 + R_2 + R_3} \cdot V_{DD} \quad (4)$$

$$V_{th-} = \frac{R_3}{R_1 + R_2 + R_3} \cdot V_{DD} \quad (5)$$

$$\Delta V = V_{th+} - V_{th-} = \frac{R_2}{R_1 + R_2 + R_3} \cdot V_{DD} \quad (6)$$

### 3 仿真结果

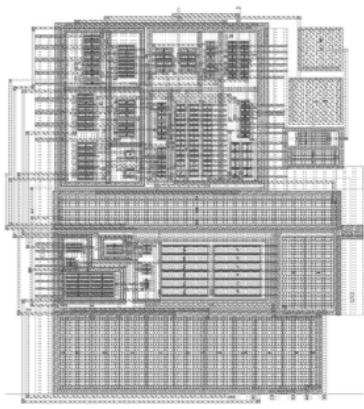

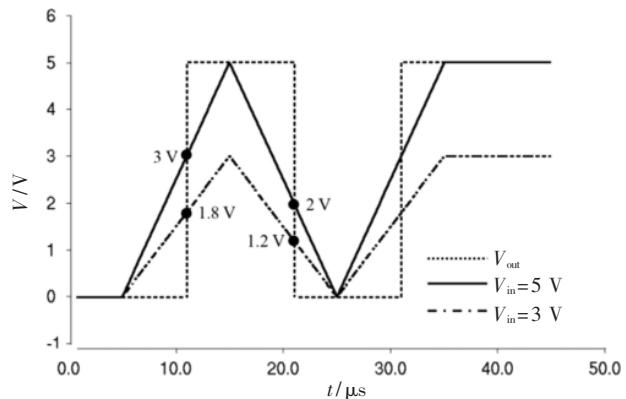

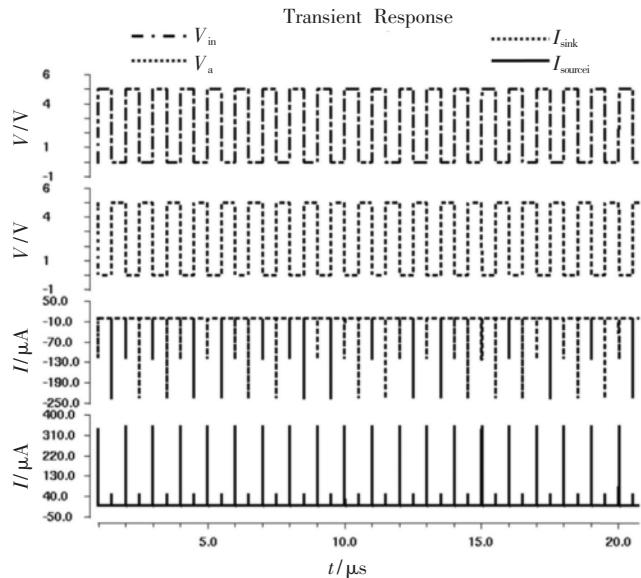

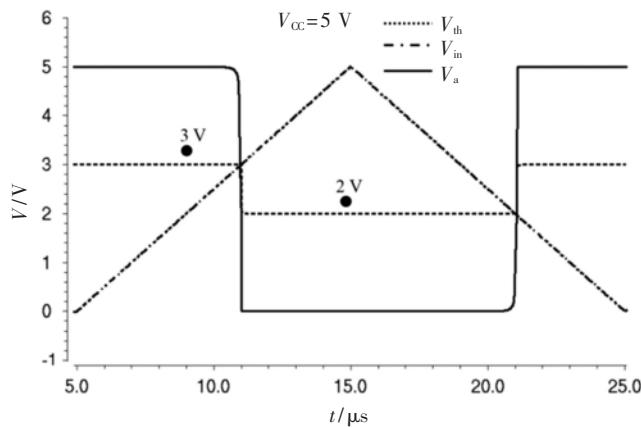

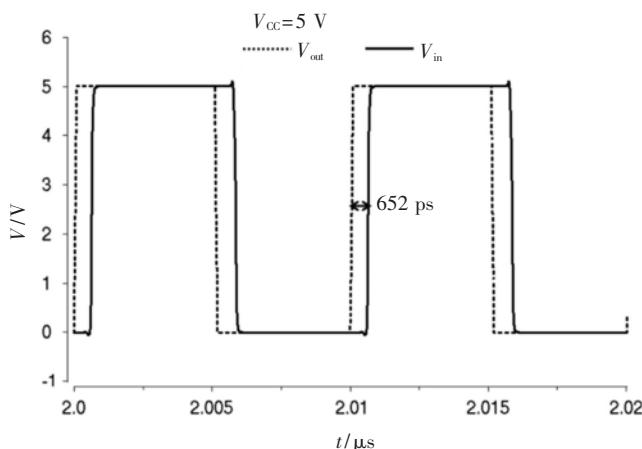

本设计采用 GF\_0.18  $\mu\text{m}$ \_BCD 工艺, 电路的整体版图如图 4 所示, 利用 Cadence ADE 仿真高速施密特触发器的动态特性, 结果如图 4 所示: 图 5 为阈值电压和滞回区间的仿真结果, 本文设计的阈值电压为 0.4 倍  $V_{CC}$  和 0.6 倍  $V_{CC}$ , 滞回区间为 0.2 倍  $V_{CC}$ , 电源电压为 3~5 V 时均能达到要求; 从图 6 中可以看出在比较器翻转瞬间, 前馈通路为比较器提供了较大的拉灌电流, 加速了比较器的翻转; 图 7 为比较器翻转时的阈值切换, 在比较器

图 4 电路整体版图结构

图 5 阈值电压仿真结果

图 6 比较器瞬态响应

图 7 阈值电压的切换

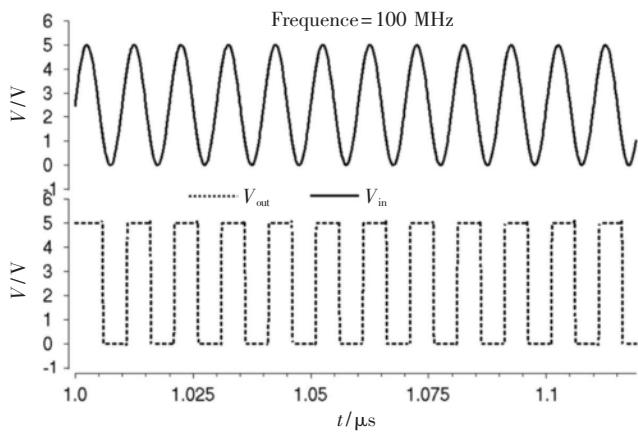

发生翻转瞬间,  $V_{th}$  阈值电压切换, 加速比较器恢复为稳定状态; 图 8 为高速施密特触发器工作在 100 MHz 高频输入信号下的仿真结果, 其电路延时为 652 ps, 信号的上升时间为 54 ps, 下降时间为 65 ps。电路的整体性能如表 1 所示。输入信号为 100 MHz 时的整形结果如图 9 所示, 与其他文献性能比较如表 2 所示。

图 8 传输延时仿真结果

表 1 高速施密特触发器的整体性能

| 参数             | 指标             |

|----------------|----------------|

| 工艺             | GF_0.18 μm_BCD |

| 电源电压/V         | 3~5            |

| 最大输入信号频率/MHz   | 500            |

| 传输延迟/ps        | 652            |

| $T_{rise}$ /ps | 54             |

| $T_{fall}$ /ps | 65             |

图 9 输入信号为 100 MHz 时的整形结果

表 2 施密特触发器的性能比较

| 参考文献 | 供电电压/V | 频率/MHz |

|------|--------|--------|

| [4]  | 3      | 0.001  |

| [5]  | 1      | 100    |

| [13] | 1.8    | 10     |

| [14] | 1.8    | 500    |

| 本文   | 3.3~5  | 500    |

## 4 结论

通过仿真,本文设计的高速施密特触发器能够工作在电源为3~5 V的系统中,输入信号和电源电压有较好的兼容性。同时电路本身的传输延时较小,能够对100 MHz的高速信号进整形滤波,当输入信号为100 MHz时,上升时间为54 ps,下降时间为65 ps,电路的传输延时为

652 ps,实现了高速度低传输延时的功能。

## 参考文献

- [1] 阎石.数字电子技术基础[M].北京:高等教育出版社,2006:457~467.

- [2] RAZAVI B.Design of analog COMS integrated circuits[M].陈贵灿,译.西安:西安交通大学出版社,2002:239~279.

- [3] 康裕荣,康向东.论施密特触发器[J].赣南师范学院学报,2007(3):65~67.

- [4] PARVEEN S A, RUKMINI M S S.Two new Schmitt trigger circuits based on current sink and current source inverters[C]//2015 International Conference on Signal Processing and Communication Engineering Systems,2015.

- [5] CHEN Z, CHEN S A high-speed low voltage CMOS Schmitt trigger with adjustable hysteresis[C]//2017 IEEE/ACIS 16th International Conference on Computer and Information Science(ICIS),2017.

- [6] SMITH M J S.On the circuit analysis of the Schmitt trigger[J].IEEE Journal of Solid-State Circuits,1988(10):293.

- [7] 吴锋霖,李思臻,余凯,等.一种增益提升和摆率增强的运算跨导放大器[J].电子技术应用,2020,46(7):65~69.

- [8] 高速施密特触发器[J].无线电工程译文,1973(2):112.

- [9] 王梦海,张春茗,严展科.一种增益和摆率提升的电流镜运算放大器[J].微电子学,2019,49(4):452~456.

- [10] 王坤,杨文荣,冉峰,等.一种新型电流运算放大器的设计[J].微计算机信息,2006(11):241~242.

- [11] 韩英.电流反馈放大器原理与应用[D].长沙:湖南师范大学,2006.

- [12] 王思远.施密特触发器电路优化与在 SRAM 中应用的研究[D].淮南:安徽理工大学,2019.

- [13] DEJHAN K, TOOPRAKAI P, RERKMANEEWAN T, et al. A high-speed direct bootstrapped CMOS Schmitt trigger circuit[C]//2004 IEEE International Conference on Semiconductor Electronics,2004.

- [14] HOSSEINNEJAD M, ERFANIAN A, KARAMI M A.On the design of low power CMOS Schmitt Trigger for biomedical application[C]//2019 27th Iranian Conference on Electrical Engineering(ICEE),2019.

- [15] YUAN F.A high-speed differential CMOS Schmitt trigger with regenerative current feedback and adjustable hysteresis[J].Analog Integrated Circuits and Signal Processing,2010,63:121~127.

(收稿日期:2021-06-13)

## 作者简介:

孙建民(1996-),通信作者,女,硕士研究生,主要研究方向:模拟集成电路设计,E-mail:13577556764@163.com。

闫江(1960-),男,博士,教授,主要研究方向:微电子与集成电路。

张龙(1989-),男,硕士,工程师,主要研究方向:模拟集成电路设计。

扫码下载电子文档

## 版权声明

经作者授权，本论文版权和信息网络传播权归属于《电子技术应用》杂志，凡未经本刊书面同意任何机构、组织和个人不得擅自复印、汇编、翻译和进行信息网络传播。未经本刊书面同意，禁止一切互联网论文资源平台非法上传、收录本论文。

截至目前，本论文已经授权被中国期刊全文数据库（CNKI）、万方数据知识服务平台、中文科技期刊数据库（维普网）、DOAJ、美国《乌利希期刊指南》、JST 日本科技技术振兴机构数据库等数据库全文收录。

对于违反上述禁止行为并违法使用本论文的机构、组织和个人，本刊将采取一切必要法律行动来维护正当权益。

特此声明！

《电子技术应用》编辑部

中国电子信息产业集团有限公司第六研究所